Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                              |

|----------------------------|----------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                     |

| Core Processor             | ARM9®                                                                                        |

| Core Size                  | 16/32-Bit                                                                                    |

| Speed                      | 96MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                                |

| Number of I/O              | 80                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                 |

| Program Memory Type        | FLASH                                                                                        |

| EEPROM Size                | -                                                                                            |

| RAM Size                   | 96K x 8                                                                                      |

| /oltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                                   |

| Data Converters            | A/D 8x10b                                                                                    |

| Oscillator Type            | Internal                                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                |

| Package / Case             | 128-LQFP                                                                                     |

| Supplier Device Package    | -                                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str912faw47x6                        |

Contents STR91xFAxxx

# **Contents**

| 1 | Desc | ription  |                                            | 10 |

|---|------|----------|--------------------------------------------|----|

| 2 | Devi | ce sumi  | mary                                       | 11 |

| 3 | Func | tional c | overview                                   | 12 |

|   | 3.1  | System   | n-in-a-package (SiP)                       | 12 |

|   | 3.2  | Packag   | ge choice                                  | 12 |

|   | 3.3  | ARM96    | 66E-S CPU core                             | 12 |

|   | 3.4  | Burst F  | Flash memory interface                     | 12 |

|   |      | 3.4.1    | Pre-fetch queue (PFQ)                      | 12 |

|   |      | 3.4.2    | Branch cache (BC)                          | 13 |

|   |      | 3.4.3    | Management of literals                     | 13 |

|   | 3.5  | SRAM     | (64 Kbytes or 96 Kbytes)                   | 15 |

|   |      | 3.5.1    | Arbitration                                | 15 |

|   |      | 3.5.2    | Battery backup                             | 15 |

|   | 3.6  | DMA d    | lata movement                              | 15 |

|   | 3.7  | Non-vo   | platile memories                           | 16 |

|   |      | 3.7.1    | Primary Flash memory                       | 16 |

|   |      | 3.7.2    | Secondary Flash memory                     | 16 |

|   | 3.8  | One-tir  | me-programmable (OTP) memory               | 17 |

|   |      | 3.8.1    | Product ID and revision level              | 17 |

|   | 3.9  | Vector   | ed interrupt controller (VIC)              | 18 |

|   |      | 3.9.1    | FIQ handling                               | 18 |

|   |      | 3.9.2    | IRQ handling                               | 18 |

|   |      | 3.9.3    | Interrupt sources                          | 18 |

|   | 3.10 | Clock    | control unit (CCU)                         | 20 |

|   |      | 3.10.1   | Master clock sources                       | 20 |

|   |      | 3.10.2   | Reference clock (RCLK)                     | 21 |

|   |      | 3.10.3   | AHB clock (HCLK)                           | 21 |

|   |      | 3.10.4   | APB clock (PCLK)                           | 21 |

|   |      | 3.10.5   | Flash memory interface clock (FMICLK)      | 22 |

|   |      | 3.10.6   | UART and SSP clock (BRCLK)                 | 22 |

|   |      | 3.10.7   | External memory interface bus clock (BCLK) | 22 |

STR91xFAxxx Contents

|      | 3.10.8   | USB interface clock                                    | . 22 |

|------|----------|--------------------------------------------------------|------|

|      | 3.10.9   | Ethernet MAC clock                                     | . 22 |

|      | 3.10.10  | External RTC calibration clock                         | . 22 |

|      | 3.10.11  | Operation example                                      | . 23 |

| 3.11 | Flexible | power management                                       | 23   |

|      | 3.11.1   | Run mode                                               | . 23 |

|      | 3.11.2   | Idle mode                                              | . 24 |

|      | 3.11.3   | Sleep mode                                             | . 24 |

| 3.12 | Voltage  | supplies                                               | 24   |

|      | 3.12.1   | Independent A/D converter supply and reference voltage | . 24 |

|      | 3.12.2   | Battery supply                                         | . 25 |

| 3.13 | System   | supervisor                                             | 25   |

|      | 3.13.1   | Supply voltage brownout                                | . 25 |

|      | 3.13.2   | Supply voltage dropout                                 | . 26 |

|      | 3.13.3   | Watchdog timer                                         | . 26 |

|      | 3.13.4   | External RESET_INn pin                                 | . 26 |

|      | 3.13.5   | Power-up                                               | . 26 |

|      | 3.13.6   | JTAG debug command                                     | . 26 |

|      | 3.13.7   | Tamper detection                                       | . 27 |

| 3.14 | Real-tim | ne clock (RTC)                                         | 27   |

| 3.15 | JTAG in  | iterface                                               | 27   |

|      | 3.15.1   | In-system-programming                                  | . 28 |

|      | 3.15.2   | Boundary scan                                          | . 29 |

|      | 3.15.3   | CPU debug                                              | . 29 |

|      | 3.15.4   | JTAG security bit                                      | . 29 |

| 3.16 | Embedo   | ded trace module (ARM ETM9, v. r2p2)                   | 30   |

| 3.17 | Etherne  | et MAC interface with DMA                              | 30   |

| 3.18 | USB 2.0  | Slave device interface with DMA                        | 31   |

|      | 3.18.1   | Packet buffer interface (PBI)                          | . 32 |

|      | 3.18.2   | DMA                                                    | . 32 |

|      | 3.18.3   | Suspend mode                                           | . 32 |

| 3.19 | CAN 2.0  | DB interface                                           | 32   |

| 3.20 | UART ir  | nterfaces with DMA                                     | 33   |

|      | 3.20.1   | DMA                                                    | . 33 |

| 3.21 | I2C inte | rfaces                                                 | 33   |

| 3.22 | SSP int  | erfaces (SPI, SSI, and MICROWIRE) with DMA             | 34   |

|      |          | , , ,                                                  |      |

| 9  | Package mechanical data     | 95 |

|----|-----------------------------|----|

|    | 9.1 ECOPACK 1               | 04 |

|    | 9.2 Thermal characteristics | 04 |

| 10 | Ordering information        | 05 |

| 11 | Revision history            | 06 |

# 3.5 SRAM (64 Kbytes or 96 Kbytes)

A 32-bit wide SRAM resides on the CPU's Data TCM (D-TCM) interface, providing single-cycle data accesses. As shown in *Figure 1*, the D-TCM shares SRAM access with the Advanced High-performance Bus (AHB). Sharing is controlled by simple arbitration logic to allow the DMA unit on the AHB to also access the SRAM.

#### 3.5.1 Arbitration

Zero-wait state access occurs for either the D-TCM or the AHB when only one of the two is requesting SRAM. When both request SRAM simultaneously, access is granted on an interleaved basis so neither requestor is starved, granting one 32-bit word transfer to each requestor before relinquishing SRAM to the other. When neither the D-TCM or the AHB are requesting SRAM, the arbiter leaves access granted to the most recent user (if D-TCM was last to use SRAM then the D-TCM will not have to arbitrate to get access next time).

The CPU may execute code from SRAM through the AHB. There are no wait states as long as the D-TCM is not contending for SRAM access and the AHB is not sharing bandwidth with peripheral traffic. The ARM966E-S CPU core has a small pre-fetch queue built into this instruction path through the AHB to look ahead and fetch instructions during idle bus cycles.

### 3.5.2 Battery backup

When a battery is connected to the designated battery backup pin (VBATT), SRAM contents are automatically preserved when the operating voltage on the main digital supplies (VDD and VDDQ are lost or sag below the LVD threshold. Automatic switchover to SRAM can be disabled by firmware if it is desired that the battery will power only the RTC and not the SRAM during standby.

#### 3.6 DMA data movement

DMA channels on the Advanced High-performance Bus (AHB) take full advantage of the separate data path provided by the Harvard architecture, moving data rapidly and largely independent of the instruction path. There are two DMA units, one is dedicated to move data between the Ethernet interface and SRAM, the other DMA unit has eight programmable channels with 14 request signals to service other peripherals and interfaces (USB, SSP, ADC, UART, Timers, EMI, and external request pins). Both single word and burst DMA transfers are supported. Memory-to-memory transfers are supported in addition to memory-peripheral transfers. DMA access to SRAM is shared with D-TCM accesses, and arbitration is described in *Section 3.5.1*. Efficient DMA transfers are managed by firmware using linked list descriptor tables. Of the 16 DMA request signals, two are assigned to external inputs. The DMA unit can move data between external devices and resources inside the STR91xFA through the EMI bus.

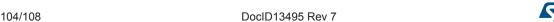

As an option, there are a number of peripherals that do not have to receive a clock sourced from the CCU. The USB interface can receive an external clock on pin P2.7, TIM timers TIM0/ TIM1 can receive an external clock on pin P2.4, and timers TIM2/TIM3 on pin P2.5.

Figure 2. Clock control

# 3.10.2 Reference clock (RCLK)

The main clock ( $f_{MSTR}$ ) can be divided to operate at a slower frequency reference clock (RCLK) for the ARM core and all the peripherals. The RCLK provides the divided clock for the ARM core, and feeds the dividers for the AHB, APB, External Memory Interface, and FMI units.

#### 3.10.3 AHB clock (HCLK)

The RCLK can be divided by 1, 2 or 4 to generate the AHB clock. The AHB clock is the bus clock for the AHB bus and all bus transfers are synchronized to this clock. The maximum HCLK frequency is 96 MHz.

### 3.10.4 APB clock (PCLK)

The RCLK can be divided by 1, 2, 4 or 8 to generate the APB clock. The APB clock is the bus clock for the APB bus and all bus transfers are synchronized to this clock. Many of the peripherals that are connected to the AHB bus also use the PCLK as the source for external bus data transfers. The maximum PCLK frequency is 48 MHz.

Functional overview STR91xFAxxx

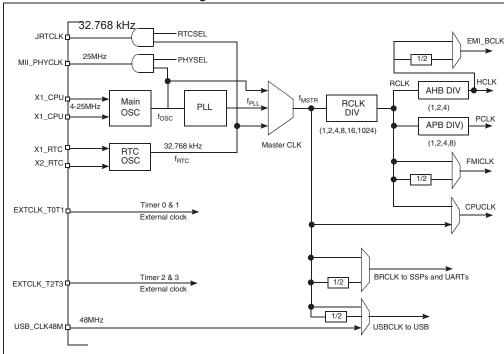

three TAPs are daisy-chained, only one TAP will converse on the JTAG bus at any given time while the other two TAPs are in BYPASS mode. The TAP positioning order within this JTAG chain is the boundary scan TAP first, followed by the ARM debug TAP, followed by the Flash TAP. All three TAP controllers are reset simultaneously by one of two methods:

- A chip-level global reset, caused only by a Power-On-Reset (POR) or a Low Voltage Detect (LVD).

- A reset command issued by the external JTAG test equipment. This can be the assertion of the JTAG JTRSTn input pin on the STR91xFA or a JTAG reset command shifted into the STR91xFA serially.

This means that chip-level system resets from watchdog time-out or the assertion of RESET\_INn pin do not affect the operation of any JTAG TAP controller. Only global resets effect the TAPs.

Figure 3. JTAG chaining inside the STR91xFA

# 3.15.1 In-system-programming

The JTAG interface is used to program or erase all memory areas of the STR91xFA device. The pin RESET\_INn must be asserted during ISP to prevent the CPU from fetching invalid instructions while the Flash memories are being programmed.

Note that the 32 bytes of OTP memory locations cannot be erased by any means once programmed by JTAG ISP or the CPU.

577

Functional overview STR91xFAxxx

# 3.16 Embedded trace module (ARM ETM9, v. r2p2)

The ETM9 interface provides greater visibility of instruction and data flow happening inside the CPU core by streaming compressed data at a very high rate from the STR91xFA though a small number of ETM9 pins to an external Trace Port Analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or other high-speed channel. Real-time instruction flow and data activity can be recorded and later formatted and displayed on the host computer running debugger software, and this software is typically integrated with the debug software used for EmbeddedICE-RT functions such as single-step, breakpoints, etc. Tracing may be triggered and filtered by many sources, such as instruction address comparators, data watchpoints, context ID comparators, and counters. State sequencing of up to three triggers is also provided. TPA hardware is commercially available and operates with debugging software tools.

The ETM9 interface is nine pins total, four of which are data lines, and all pins can be used for GPIO after tracing is no longer needed. The ETM9 interface is used in conjunction with the JTAG interface for trace configuration. When tracing begins, the ETM9 engine compresses the data by various means before broadcasting data at high speed to the TPA over the four data lines. The most common ETM9 compression technique is to only output address information when the CPU branches to a location that cannot be inferred from the source code. This means the host computer must have a static image of the code being executed for decompressing the ETM9 data. Because of this, self-modified code cannot be traced.

#### 3.17 Ethernet MAC interface with DMA

STR91xFA devices in 128-pin and 144-ball packages provide an IEEE-802.3-2002 compliant Media Access Controller (MAC) for Ethernet LAN communications through an industry standard Medium Independent Interface (MII). The STR91xFA requires an external Ethernet physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the STR91xFA MII port using as many as 18 signals (see pins which have signal names MII\_\* in *Table 8*).

The MAC corresponds to the OSI Data Link layer and the PHY corresponds to the OSI Physical layer. The STR91xFA MAC is responsible for:

- Data encapsulation, including frame assembly before transmission, and frame parsing/error detection during and after reception.

- Media access control, including initiation of frame transmission and recover from transmission failure.

577

The STR91xFA MAC includes the following features:

- Supports 10 and 100 Mbps rates

- Tagged MAC frame support (VLAN support)

- Half duplex (CSMA/CD) and full duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. Transmit FIFO depth is 4 words (32 bits each), and the receive FIFO is 16 words deep.

A 32-bit burst DMA channel residing on the AHB is dedicated to the Ethernet MAC for high-speed data transfers, side-stepping the CPU for minimal CPU impact during transfers. This DMA channel includes the following features:

- Direct SRAM to MAC transfers of transmit frames with the related status, by descriptor chain

- Direct MAC to SRAM transfers of receive frames with the related status, by descriptor chain

- Open and Closed descriptor chain management

#### 3.18 USB 2.0 slave device interface with DMA

The STR91xFA provides a USB slave controller that implements both the OSI Physical and Data Link layers for direct bus connection by an external USB host on pins USBDP and USBPN. The USB interface detects token packets, handles data transmission and reception, and processes handshake packets as required by the USB 2.0 standard.

The USB slave interface includes the following features:

- Supports USB low and full-speed transfers (12 Mbps), certified to comply with the USB 2.0 specification

- Supports isochronous, bulk, control, and interrupt endpoints

- Configurable number of endpoints allowing a mixture of up to 20 single-buffered monodirectional endpoints or up to 10 double-buffered bidirectional endpoints

- Dedicated, dual-port 2 Kbyte USB Packet Buffer SRAM. One port of the SRAM is connected by a Packet Buffer Interface (PBI) on the USB side, and the CPU connects to the other SRAM port.

- CRC generation and checking

- NRZI encoding-decoding and bit stuffing

- USB suspend resume operations

#### 3.22.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service each SSP channel for fast and direct transfers between the SSP bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive. Burst transfers require that FIFOs are enabled.

# 3.23 General purpose I/O

There are up to 80 GPIO pins available on 10 I/O ports for 128-pin and 144-ball devices, and up to 40 GPIO pins on 5 I/O ports for 80-pin devices. Each and every GPIO pin by default (during and just after a reset condition) is in high-impedance input mode, and some GPIO pins are additionally routed to certain peripheral function inputs. CPU firmware may initialize GPIO pins to have alternate input or output functions as listed in *Table 8*. At any time, the logic state of any GPIO pin may be read by firmware as a GPIO input, regardless of its reassigned input or output function.

Bit masking is available on each port, meaning firmware may selectively read or write individual port pins, without disturbing other pins on the same port during a write.

Firmware may designate each GPIO pin to have open-drain or push-pull characteristics.

All GPIO pins are 5 V tolerant, meaning they can drive a voltage level up to VDDQ, and can be safely driven by a voltage up to 5 V.

# 3.24 A/D converter (ADC) with DMA

The STR91xFA provides an eight-channel, 10-bit successive approximation analog-to-digital converter. The ADC input pins are multiplexed with other functions on Port 4 as shown in *Table 8*. Following are the major ADC features:

- Fast conversion time, as low as 0.7 usec

- Accuracy. Integral and differential non-linearity are typically within 4 conversion counts.

- 0 to 3.6 V input range. External reference voltage input pin (AVREF) available on 128pin packages for better accuracy on low-voltage inputs. See *Table 11: Operating* conditions, for restrictions to the relative voltage levels of VDDQ, AVDD, AVREF, and AVREF AVDD.

- CPU Firmware may convert one ADC input channel at a time, or it has the option to set the ADC to automatically scan and convert all eight ADC input channels sequentially before signalling an end-of-conversion

- Automatic continuous conversion mode is available for any number of designated ADC input channels

- Analog watchdog mode provides automatic monitoring of any ADC input, comparing it

against two programmable voltage threshold values. The ADC unit will set a flag or it

will interrupt the CPU if the input voltage rises above the higher threshold, or drops

below the lower threshold.

- The ADC unit goes to stand-by mode (very low-current consumption) after any reset event. CPU firmware may also command the ADC unit to stand-by mode at any time.

- ADC conversion can be started or triggered by software command as well as triggers from Timer/Counter (TIM), Motor Controller and input from external pin.

Pin description STR91xFAxxx

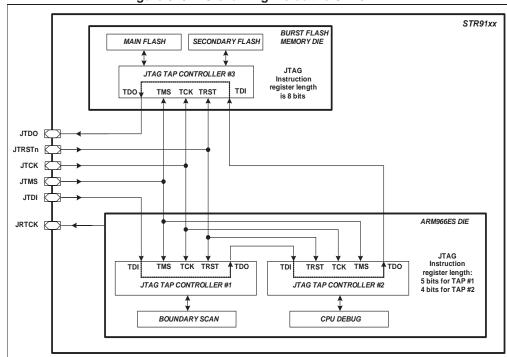

Figure 8. STR91xFAW 128-pin package pinout

- NU (Not Used) on STR910FAW devices. Pin 95 is not connected, pin 96 must be pulled up by a 1.5Kohm resistor to VDDQ.

- 2. No USBCLK function on STR910FAW devices.

- 3. No PHYCLK function on STR910FAW devices.

STR91xFAxxx Pin description

Table 8. Device pin description (continued)

| Package |         | age      |                 | a           |                            | •                                 | •                               | Alternate              | functions                      |                               |

|---------|---------|----------|-----------------|-------------|----------------------------|-----------------------------------|---------------------------------|------------------------|--------------------------------|-------------------------------|

| LQFP80  | LQFP128 | LFBGA144 | Pin<br>name     | Signal type | Default pin function       | Default<br>input<br>function      | Alternate input 1               | Alternate output 1     | Alternate<br>output 2          | Alternate output 3            |

| 12      | 18      | F6       | P5.1            | 1/0         | GPIO_5.1,<br>GP Input, HiZ | EXINT9,<br>External Intr          | UART0_RxD,<br>UART rcv data     | GPIO_5.1,<br>GP Output | CAN_TX,<br>CAN Tx data         | UART2_TX,<br>UART xmit data   |

| 17      | 25      | K1       | PHYCLK<br>_P5.2 | I/O         | GPIO_5.2,<br>GP Input, HiZ | EXINT10,<br>External Intr         | UART2_RxD,<br>UART rcv data     | GPIO_5.2,<br>GP Output | MII_PHYCLK,<br>25Mhz to PHY    | TIM3_OCMP1,<br>Out comp/PWM   |

| 18      | 27      | H2       | P5.3            | I/O         | GPIO_5.3,<br>GP Input, HiZ | EXINT11,<br>External Intr         | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_5.3,<br>GP Output | MII_TX_EN,<br>MAC xmit enbl    | TIM2_OCMP1,<br>Out comp/PWM   |

| 44      | 70      | J12      | P5.4            | I/O         | GPIO_5.4,<br>GP Input, HiZ | EXINT12,<br>External Intr         | SSP0_SCLK,<br>SSP slv clk in    | GPIO_5.4,<br>GP Output | SSP0_SCLK,<br>SSP mstr clk out | EMI_CS0n,<br>EMI Chip Select  |

| 47      | 77      | H11      | P5.5            | I/O         | GPIO_5.5,<br>GP Input, HiZ | EXINT13,<br>External Intr         | SSP0_MOSI,<br>SSP slv dat in    | GPIO_5.5,<br>GP Output | SSP0_MOSI,<br>SSP mstr dat out | EMI_CS1n,<br>EMI Chip Select  |

| 48      | 79      | Н9       | P5.6            | I/O         | GPIO_5.6,<br>GP Input, HiZ | EXINT14,<br>External Intr         | SSP0_MISO,<br>SSP mstr dat in   | GPIO_5.6,<br>GP Output | SSP0_MISO,<br>SSP slv data out | EMI_CS2n,<br>EMI Chip Select  |

| 49      | 80      | G12      | P5.7            | I/O         | GPIO_5.7,<br>GP Input, HiZ | EXINT15,<br>External Intr         | SSP0_NSS,<br>SSP slv select in  | GPIO_5.7,<br>GP Output | SSP0_NSS,<br>SSP mstr sel out  | EMI_CS3n,<br>EMI Chip Select  |

|         |         |          |                 |             |                            | •                                 |                                 |                        |                                |                               |

| 19      | 29      | H4       | P6.0            | I/O         | GPIO_6.0,<br>GP Input, HiZ | EXINT16,<br>External Intr         | TIM0_ICAP1,<br>Input Capture    | GPIO_6.0,<br>GP Output | TIM0_OCMP1,<br>Out comp/PWM    | MC_UH,<br>IMC phase U hi      |

| 20      | 31      | J3       | P6.1            | I/O         | GPIO_6.1,<br>GP Input, HiZ | EXINT17,<br>External Intr         | TIM0_ICAP2,<br>Input Capture    | GPIO_6.1,<br>GP Output | TIM0_OCMP2,<br>Out comp        | MC_UL,<br>IMC phase U lo      |

| 13      | 19      | G2       | P6.2            | I/O         | GPIO_6.2,<br>GP Input, HiZ | EXINT18,<br>External Intr         | TIM1_ICAP1,<br>Input Capture    | GPIO_6.2,<br>GP Output | TIM1_OCMP1,<br>Out comp/PWM    | MC_VH,<br>IMC phase V hi      |

| 14      | 20      | G3       | P6.3            | I/O         | GPIO_6.3,<br>GP Input, HiZ | EXINT19,<br>External Intr         | TIM1_ICAP2,<br>Input Capture    | GPIO_6.3,<br>GP Output | TIM1_OCMP2,<br>Out comp        | MC_VL,<br>IMC phase V lo      |

| 52      | 83      | G8       | P6.4            | I/O         | GPIO_6.4,<br>GP Input, HiZ | EXINT20,<br>External Intr         | TIM2_ICAP1,<br>Input Capture    | GPIO_6.4,<br>GP Output | TIM2_OCMP1,<br>Out comp/PWM    | MC_WH,<br>IMC phase W hi      |

| 53      | 84      | G7       | P6.5            | I/O         | GPIO_6.5,<br>GP Input, HiZ | EXINT21,<br>External Intr         | TIM2_ICAP2,<br>Input Capture    | GPIO_6.5,<br>GP Output | TIM2_OCMP2,<br>Out comp        | MC_WL,<br>IMC phase W lo      |

| 57      | 92      | E9       | P6.6            | I/O         | GPIO_6.6,<br>GP Input, HiZ | EXINT22_TRIG,<br>Ext Intr & Tach  | UART0_RxD,<br>UART rcv data     | GPIO_6.6,<br>GP Output | TIM3_OCMP1,<br>Out comp/PWM    | ETM_TRCLK,<br>ETM trace clock |

| 58      | 93      | D12      | P6.7            | I/O         | GPIO_6.7,<br>GP Input, HiZ | EXINT23_STOP,<br>Ext Intr & Estop | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_6.7,<br>GP Output | TIM3_OCMP2,<br>Out comp        | UART0_TX,<br>UART xmit data   |

|         |         |          |                 |             |                            |                                   |                                 |                        |                                |                               |

| -       | 5       | D1       | P7.0            | I/O         | GPIO_7.0,<br>GP Input, HiZ | EXINT24,<br>External Intr         | TIM0_ICAP1,<br>Input Capture    | GPIO_7.0,<br>GP Output | 8b) EMI_A0,<br>16b) EMI_A16    | ETM_PCK0,<br>ETM Packet       |

| -       | 6       | D2       | P7.1            | I/O         | GPIO_7.1,<br>GP Input, HiZ | EXINT25,<br>External Intr         | TIM0_ICAP2,<br>Input Capture    | GPIO_7.1,<br>GP Output | 8b) EMI_A1,<br>16b) EMI_A17    | ETM_PCK1,<br>ETM Packet       |

| -       | 7       | B1       | P7.2            | I/O         | GPIO_7.2,<br>GP Input, HiZ | EXINT26,<br>External Intr         | TIM2_ICAP1,<br>Input Capture    | GPIO_7.2,<br>GP Output | 8b) EMI_A2,<br>16b) EMI_A18    | ETM_PCK2,<br>ETM Packet       |

| -       | 13      | F1       | P7.3            | I/O         | GPIO_7.3,<br>GP Input, HiZ | EXINT27,<br>External Intr         | TIM2_ICAP2,<br>Input Capture    | GPIO_7.3,<br>GP Output | 8b) EMI_A3,<br>16b) EMI_A19    | ETM_PCK3,<br>ETM Packet       |

| -       | 14      | G1       | P7.4            | I/O         | GPIO_7.4,<br>GP Input, HiZ | EXINT28,<br>External Intr         | UART0_RxD,<br>UART rcv data     | GPIO_7.4,<br>GP Output | 8b) EMI_A4,<br>16b) EMI_A20    | EMI_CS3n,<br>EMI Chip Select  |

| -       | 15      | E5       | P7.5            | I/O         | GPIO_7.5,<br>GP Input, HiZ | EXINT29,<br>External Intr         | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_7.5,<br>GP Output | 8b) EMI_A5,<br>16b) EMI_A21    | EMI_CS2n,<br>EMI Chip Select  |

STR91xFAxxx Pin description

Table 8. Device pin description (continued)

| F      | Packa   | age      |                      | Ф           |                                                                                                                                                       | -                            | Alternate functions |                       |                       |                    |  |

|--------|---------|----------|----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|-----------------------|-----------------------|--------------------|--|

| LQFP80 | LQFP128 | LFBGA144 | Pin<br>name          | Signal type | Default pin function                                                                                                                                  | Default<br>input<br>function | Alternate input 1   | Alternate<br>output 1 | Alternate<br>output 2 | Alternate output 3 |  |

| -      | 21      | G4       | EMI_<br>BWR_<br>WRLn | 0           | EMI byte write<br>strobe (8 bit<br>mode) or low<br>byte write<br>strobe (16 bit<br>mode)<br>Can also be<br>configured as<br>EMI_LBn in<br>BGA package |                              |                     | N/A                   |                       |                    |  |

| -      | 22      | H1       | EMI_<br>WRHn         | 0           | EMI high byte<br>write strobe<br>(16-bit mode)<br>Can also be<br>configured as<br>EMI_UBn in<br>BGA package                                           |                              | N/A                 |                       |                       |                    |  |

| -      | 74      | J10      | EMI_ALE              | 0           | EMI address<br>latch enable<br>(mux mode)                                                                                                             |                              | N/A                 |                       |                       |                    |  |

| -      | 75      | J9       | EMI_<br>RDn          | 0           | EMI read strobe                                                                                                                                       |                              | N/A                 |                       |                       |                    |  |

| -      | -       | Н8       | EMI_<br>BAAn         | 0           | EMI Burst<br>address<br>advance                                                                                                                       |                              |                     | N/A                   |                       |                    |  |

| -      | -       | K8       | EMI_<br>WAITn        | I           | EMI Wait input for burst mode device                                                                                                                  |                              |                     | N/A                   |                       |                    |  |

| -      | -       | M8       | EMI_<br>BCLK         | 0           | EMI bus clock                                                                                                                                         |                              |                     | N/A                   |                       |                    |  |

| -      | -       | A12      | EMI_<br>WEn          | 0           | EMI write enable                                                                                                                                      |                              |                     | N/A                   |                       |                    |  |

| -      | 91      | E10      | TAMPER<br>_IN        | 1           | Tamper detection input                                                                                                                                |                              |                     | N/A                   |                       |                    |  |

| -      | 94      | D11      | MII_<br>MDIO         | I/O         | MAC/PHY<br>management<br>data line                                                                                                                    |                              |                     | N/A                   |                       |                    |  |

| 59     | 95      | D10      | USBDN                | I/O         | USB data (-)<br>bus connect                                                                                                                           |                              |                     | N/A                   |                       |                    |  |

| 60     | 96      | C11      | USBDP                | I/O         | USB data (+)<br>bus connect                                                                                                                           | N/A                          |                     |                       |                       |                    |  |

| 56     | 89      | C12      | RESET<br>_INn        | _           | External reset input                                                                                                                                  | N/A                          |                     |                       |                       |                    |  |

| 62     | 100     | A9       | RESET<br>_OUTn       | 0           | Global or<br>System reset<br>output                                                                                                                   | N/A                          |                     |                       |                       |                    |  |

| 65     | 104     | A10      | X1_CPU               | I           | CPU oscillator or crystal input                                                                                                                       | N/A                          |                     |                       |                       |                    |  |

| 64     | 103     | A11      | X2_CPU               | 0           | CPU crystal connection                                                                                                                                |                              |                     | N/A                   |                       |                    |  |

STR91xFAxxx Memory mapping

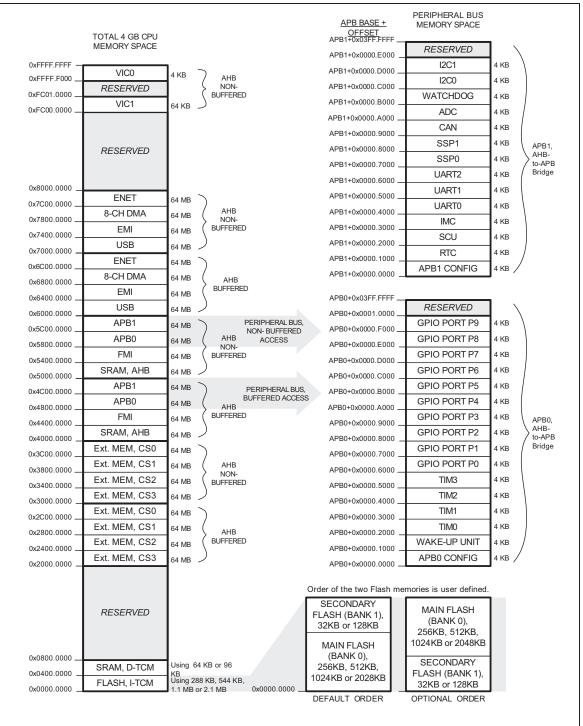

Figure 9. STR91xFA memory map

Electrical characteristics STR91xFAxxx

### 7.9.5 Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

#### 7.9.6 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

# 7.9.7 Electrical sensitivity

Table 30. Static latch-up data

| Symbol | Parameter             | Conditions                                    | Class <sup>(1)</sup> |

|--------|-----------------------|-----------------------------------------------|----------------------|

| LU     | Static latch-up class | T <sub>A</sub> = +25 °C conforming to JESD78A | II class A           |

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

Electrical characteristics STR91xFAxxx

# 7.12 Communication interface electrical characteristics

### 7.12.1 10/100 Ethernet MAC electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6 V,  $V_{DD}$  = 1.65 - 2 V,  $T_A$  = -40 / 85 °C unless otherwise specified.

### **Ethernet MII interface timings**

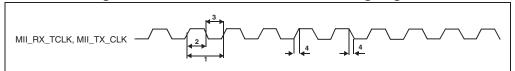

Figure 25. MII\_RX\_CLK and MII\_TX\_CLK timing diagram

Table 40. MII\_RX\_CLK and MII\_TX\_CLK timing table

| Symbol | Parameter           | Symbol                  | Va  | Unit |       |

|--------|---------------------|-------------------------|-----|------|-------|

|        | Farameter           | Symbol                  | Min | Max  | Offic |

| 1      | Cycle time          | t <sub>c</sub> (CLK)    | 40  |      | ns    |

| 2      | Pulse duration high | t <sub>HIGH</sub> (CLK) | 40% | 60%  |       |

| 3      | Pulse duration low  | t <sub>LOW</sub> (CLK)  | 40% | 60%  |       |

| 4      | Transition time     | t <sub>t</sub> (CLK)    |     | 1    | ns    |

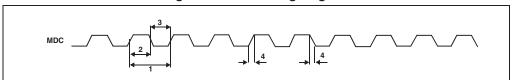

Figure 26. MDC timing diagram

Table 41. MDC timing table

| Symbol | Parameter           | Symbol                  | Va  | Unit |       |

|--------|---------------------|-------------------------|-----|------|-------|

|        | Farameter           | Syllibol                | Min | Max  | Oilit |

| 1      | Cycle time          | t <sub>c</sub> (MDC)    | 266 |      | ns    |

| 2      | Pulse duration high | t <sub>HIGH</sub> (MDC) | 40% | 60%  |       |

| 3      | Pulse duration low  | t <sub>LOW</sub> (MDC)  | 40% | 60%  |       |

| 4      | Transition time     | t <sub>t</sub> (MDC)    |     | 1    | ns    |

## **Ethernet MII management timings**

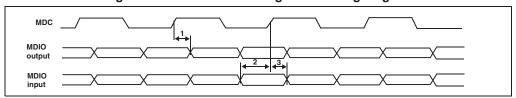

Figure 27. Ethernet MII management timing diagram

Table 42. Ethernet MII management timing table

| Symbol | Parameter                              | Symbol                 | Va    | Unit |       |

|--------|----------------------------------------|------------------------|-------|------|-------|

| Symbol | raiailletei                            | Symbol                 | Min   | Max  | Oille |

| 1      | MDIO delay from rising edge of MDC     | t <sub>c</sub> (MDIO)  |       | 2.83 | ns    |

| 2      | MDIO setup time to rising edge of MDC  | T <sub>su</sub> (MDIO) | 2.70  |      | ns    |

| 3      | MDIO hold time from rising edge of MDC | T <sub>h</sub> (MDIO)  | -2.03 |      | ns    |

## **Ethernet MII transmit timings**

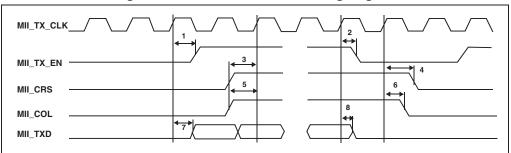

Figure 28. Ethernet MII transmit timing diagram

Electrical characteristics STR91xFAxxx

Symbol **Parameter** Symbol Unit Min Max MII\_TX\_CLK high to  $t_{VAL}(MII\_TX\_EN)$ 1 4.20 ns MII\_TX\_EN valid MII\_TX\_CLK high to  $T_{inval}(MII\_TX\_EN)$ 2 4.86 ns MII TX EN invalid MII CRS valid to 3 0.61  $T_{SU}(MII\_CRS)$ ns MII\_TX\_CLK high MII\_TX\_CLK high to 4 T<sub>h</sub>(MII\_CRS) 0.00 ns MII CRS invalid MII COL valid to 5  $T_{su}(MII\_COL)$ 0.81 ns MII\_TX\_CLK high MII\_TX\_CLK high to 6  $T_h(MII\_COL)$ 0.00 ns MII COL invalid MII\_TX\_CLK high to 7  $t_{VAL}(MII\_TXD)$ 5.02 ns MII\_TXD valid MII\_TXCLK high to 8  $T_{inval}(MII\_TXD$ 5.02 ns MII\_TXD invalid

Table 43. Ethernet MII transmit timing table

#### **Ethernet MII receive timings**

MII\_RX\_CLK

MII\_RXD

MII\_RX\_DV

MII\_RX\_ER

Figure 29. Ethernet MII receive timing diagram

Table 44. Ethernet MII receive timing table

| Symbol | Parameter                          | Symbol                    | Va   | Unit |      |

|--------|------------------------------------|---------------------------|------|------|------|

|        | raiametei                          | Symbol                    | Min  | Max  | Onit |

| 1      | MII_RXD valid to MII_RX_CLK high   | T <sub>su</sub> (MII_RXD) | 0.81 |      | ns   |

| 2      | MII_RX_CLK high to MII_RXD invalid | T <sub>h</sub> (MII_RXD)  | 0.00 |      | ns   |

#### 7.12.2 USB electrical interface characteristics

USB 2.0 Compliant in Full Speed Mode

#### 7.12.3 CAN interface electrical characteristics

Conforms to CAN 2.0B protocol specification

86/108 DocID13495 Rev 7

| Symbol               | Parameter <sup>(1) (2)</sup>                   | Test<br>conditions        | Value                 |                       |                       | l lm:4 |

|----------------------|------------------------------------------------|---------------------------|-----------------------|-----------------------|-----------------------|--------|

|                      |                                                |                           | Min                   | Тур                   | Max                   | Unit   |

| t <sub>CONV(S]</sub> | Single mode conversion time                    |                           | 2*16/f <sub>ADC</sub> |                       | 3*16/f <sub>ADC</sub> | μs     |

|                      |                                                | f <sub>ADC</sub> = 24 MHz | 1.33                  |                       | 2                     |        |

| TR(S)                | Single mode throughput rate (3)                | f <sub>ADC</sub> = 24 MHz |                       |                       | 500                   | ksps   |

| t <sub>CONV(C]</sub> | Continuous mode conversion time <sup>(4)</sup> |                           |                       | 1*16/f <sub>ADC</sub> |                       | μs     |

|                      |                                                | f <sub>ADC</sub> = 24 MHz |                       | 0.66                  |                       | μs     |

| TR(C)                | Continuous mode throughput rate                | f <sub>ADC</sub> = 24 MHz |                       | 1500                  |                       | ksps   |

Table 48. ADC conversion time (silicon Rev G)

- 3. Value obtained on conversions started by trigger in single mode

- 4. All sucessive conversions in continuous and scan modes.

Table 49. ADC conversion time (silicon Rev H and higher)

| Symbol                | Parameter <sup>(1)</sup> (2)                     | Test<br>conditions        | Value                 |                       |                       | I I a i t |

|-----------------------|--------------------------------------------------|---------------------------|-----------------------|-----------------------|-----------------------|-----------|

|                       |                                                  |                           | Min                   | Тур                   | Max                   | Unit      |

| t <sub>CONV(S]</sub>  | Single mode conversion time                      |                           | 1*16/f <sub>ADC</sub> |                       | 2*16/f <sub>ADC</sub> | μs        |

|                       |                                                  | f <sub>ADC</sub> = 24 MHz | 0.66                  |                       | 1.33                  |           |

| TR(S)                 | Single mode throughput rate (3)                  | f <sub>ADC</sub> = 24 MHz |                       |                       | 750                   | ksps      |

| t <sub>CONV(C]</sub>  | Continuous mode conversion time <sup>(4)</sup>   |                           |                       | 1*16/f <sub>ADC</sub> |                       | μs        |

|                       |                                                  | f <sub>ADC</sub> = 24 MHz |                       | 0.66                  |                       | μs        |

| TR(C)                 | Continuous mode throughput rate                  | f <sub>ADC</sub> = 24 MHz |                       | 1500                  |                       | ksps      |

| t <sub>CONV(FT]</sub> | Fast trigger mode conversion time <sup>(5)</sup> |                           |                       | 1*16/f <sub>ADC</sub> |                       | μs        |

|                       |                                                  | f <sub>ADC</sub> = 24 MHz |                       | 0.66                  |                       | μs        |

| TR(FT)                | Fast trigger mode throughput rate <sup>(6)</sup> | f <sub>ADC</sub> = 24 MHz | 100                   |                       | 1200                  | ksps      |

<sup>1.</sup> Guaranteed by design, not tested in production.

- 3. Value obtained from conversions started by trigger in single mode

- 4. All successive conversions in continuous and scan modes.

- Conversion started by trigger when automatic clock gated mode enabled. Fast trigger mode is available only in devices with silicon Rev H and higher.

- 6. Value obtained from conversions started by fast trigger in single mode

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Parameters in this table apply to devices with silicon Rev G. Refer to *Table 5* for device rev identification in OTP memory and to *Section 8: Device marking.*

<sup>2.</sup> Parameters in this table apply to devices with silicon Rev H and higher. Refer to *Table 5* for device rev identification in OTP memory and to *Section 8: Device marking*.

### Marking of engineering samples for LFBGA144

The following figure shows the engineering sample marking for the LFBGA package. Only the information field containing the engineering sample marking is shown.

Product identification<sup>(1)</sup>

STR910FAZ

Additional Information

Date code

MSv36551V1

Figure 46. LFBGA144 package top view

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

Dpad 0.37 mm

Dsm 0.52 mm typ. (depends on solder mask registration tolerance)

Solder paste 0.37 mm aperture diameter

Non solder mask defined pads are recommended

4 to 6 mils screen print

Figure 47. Recommended PCB design rules (0.80/0.75 mm pitch BGA)

### 9.1 ECOPACK

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions, and product status are available at <a href="https://www.st.com">www.st.com</a>.

### 9.2 Thermal characteristics

The average chip-junction temperature, T<sub>J</sub> must never exceed 125 °C.

The average chip-junction temperature, T<sub>J</sub>, in degrees Celsius, may be calculated using the following equation:

$$T_{,l} = T_A + (P_D \times \Theta_{,lA}) \tag{1}$$

Where:

- T<sub>A</sub> is the ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- $P_D$  is the sum of  $P_{INT}$  and  $P_{I/O}$  ( $P_D = P_{INT} + P_{I/O}$ ),

- P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the Chip Internal Power.

P<sub>I/O</sub> represents the power dissipation on input and output pins;

Most of the time for the applications  $P_{I/O}$  <  $P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant if the device is configured to drive continuously external modules and/or memories. The worst case  $P_{INT}$  of the STR91xFA is 500 mW ( $I_{DD}$  x  $V_{DD}$ , or 250 mA x 2.0 V).

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_D = K / (T_A + 273 \,^{\circ}C)$$

(2)

Therefore (solving equations 1 and 2):

$$K = P_D x (T_A + 273 °C) + \Theta_{IA} x P_D^2$$

(3)

Where:

K is a constant for the particular part, which may be determined from equation (3) by

measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub>

and T<sub>J</sub> may be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>.

**Table 53. Thermal characteristics**

| Symbol            | Parameter                                                                  | Value | Unit |

|-------------------|----------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$     | Thermal resistance junction-ambient<br>LQFP 80 - 12 x 12 mm / 0.5 mm pitch | 41.5  | °C/W |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient<br>LQFP128 - 14 x 14 mm / 0.4 mm pitch | 38    | °C/W |

| $\Theta_{JA}$     | Thermal resistance junction-ambient<br>LFBGA 144 - 10 x 10 x 1.7 mm        | 36.5  | °C/W |