Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                              |

|----------------------------|----------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                     |

| Core Processor             | ARM9®                                                                                        |

| Core Size                  | 16/32-Bit                                                                                    |

| Speed                      | 96MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                                |

| Number of I/O              | 80                                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                                             |

| Program Memory Type        | FLASH                                                                                        |

| EEPROM Size                | ·                                                                                            |

| RAM Size                   | 96K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                                   |

| Data Converters            | A/D 8x10b                                                                                    |

| Oscillator Type            | Internal                                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                |

| Package / Case             | 144-LFBGA                                                                                    |

| Supplier Device Package    | -                                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str912faz42h6                        |

|                            |                                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49. | ADC conversion time (silicon Rev H and higher)                          | 91 |

|-----------|-------------------------------------------------------------------------|----|

| Table 50. | LQFP80 12 x12 mm low-profile quad flat package                          |    |

|           | mechanical data                                                         | 96 |

| Table 51. | LQFP128 - 128-pin, 14 x 14 mm low-profile quad flat package             |    |

|           | mechanical data                                                         | 99 |

| Table 52. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |    |

|           | 0.8 mm pitch, package mechanical data 1                                 | 02 |

| Table 53. | Thermal characteristics                                                 | 04 |

| Table 54. | Ordering information scheme                                             | 05 |

| Table 55. | Document revision history 1                                             | 06 |

## 1 Description

STR91xFA is a series of ARM<sup>®</sup>-powered microcontrollers which combines a 16/32-bit ARM966E-S RISC processor core, dual-bank Flash memory, large SRAM for data or code, and a rich peripheral set to form an ideal embedded controller for a wide variety of applications such as point-of-sale terminals, industrial automation, security and surveillance, vending machines, communication gateways, serial protocol conversion, and medical equipment. The ARM966E-S core can perform single-cycle DSP instructions, good for speech processing, audio algorithms, and low-end imaging.

| Tuble 4. Occioning      | of secondary r lash mer | liony      |

|-------------------------|-------------------------|------------|

| Size of secondary Flash | 32 Kbytes               | 128 Kbytes |

| Number of sectors       | 4                       | 8          |

| Size of each sector     | 8 Kbytes                | 16 Kbytes  |

Table 4. Sectoring of secondary Flash memory

#### 3.8 One-time-programmable (OTP) memory

There are 32 bytes of OTP memory ideally suited for serial numbers, security keys, factory calibration constants, or other permanent data constants. These OTP data bytes can be programmed only one time through either the JTAG interface or by the CPU, and these bytes can never be altered afterwards. As an option, a "lock bit" can be set by the JTAG interface or the CPU which will block any further writing to the this OTP area. The "lock bit" itself is also OTP. If the OTP array is unlocked, it is always possible to go back and write to an OTP byte location that has not been previously written, but it is never possible to change an OTP bytes (bytes 31 and 30) are reserved for the STR91xFA product ID and revision level.

#### 3.8.1 **Product ID and revision level**

OTP bytes 31 and 30 are programmed at ST factory before shipment and may be read by firmware to determine the STR91xFA product type and silicon revision so it can optionally take action based on the silicon on which it is running. In Rev H devices and 1MB/2MB Rev A devices, byte 31 contains the major family identifier of "9" (for STR9) in the high-nibble location and the minor family identifier in the low nibble location, which can be used to determine the size of primary flash memory. In all devices, byte 30 contains the silicon revision level indicator. See *Table 5* for values related to the revisions of STR9 production devices and size of primary Flash memory. See *Section 8* for details of external identification of silicon revisions.

| Production salestype | Silicon revision | Size of primary Flash | OTP byte 31 | OTP byte 30 |

|----------------------|------------------|-----------------------|-------------|-------------|

| STR91xFAxxxxx        | Rev G            | 256K or 512K          | 91h         | 20h         |

| STR91xFAxxxxx        | Rev H            | 256K                  | 90h         | 21h         |

| STR91xFAxxxxx        | Rev H            | 512K                  | 91h         | 21h         |

| STR91xFAx46xx        | Rev A            | 1024K                 | 92h         | 21h         |

| STR91xFAx47xx        | Rev A            | 2048K                 | 93h         | 21h         |

Table 5. Product ID and revision level values

#### **3.9** Vectored interrupt controller (VIC)

Interrupt management in the STR91xFA is implemented from daisy-chaining two standard ARM VIC units. This combined VIC has 32 prioritized interrupt request channels and generates two interrupt output signals to the CPU. The output signals are FIQ and IRQ, with FIQ having higher priority.

#### 3.9.1 FIQ handling

FIQ (Fast Interrupt reQuest) is the only non-vectored interrupt and the CPU can execute an Interrupt Service Routine (ISR) directly without having to determine/prioritize the interrupt source, minimizing ISR latency. Typically only one interrupt source is assigned to FIQ. An FIQ interrupt has its own set of banked registers to minimize the time to make a context switch. Any of the 32 interrupt request input signals coming into the VIC can be assigned to FIQ.

#### 3.9.2 IRQ handling

IRQ is a vectored interrupt and is the logical OR of all 32 interrupt request signals coming into the 32 IRQ channels. Priority of individual vectored interrupt requests is determined by hardware (IRQ channel Intr 0 is highest priority, IRQ channel Intr 31 is lowest).

However, inside the same VIC (primary or secondary VIC), CPU firmware may re-assign individual interrupt sources to individual hardware IRQ channels, meaning that firmware can effectively change interrupt priority levels as needed within the same VIC (from priority 0 to priority 16).

# Note: VIC0 (primary VIC) interrupts always have higher priority than VIC1 (secondary VIC) interrupts

When the IRQ signal is activated by an interrupt request, VIC hardware will resolve the IRQ interrupt priority, then the ISR reads the VIC to determine both the interrupt source and the vector address to jump to the service code.

The STR91xFA has a feature to reduce ISR response time for IRQ interrupts. Typically, it requires two memory accesses to read the interrupt vector address from the VIC, but the STR91xFA reduces this to a single access by adding a 16th entry in the instruction branch cache, dedicated for interrupts. This 16th cache entry always holds the instruction that reads the interrupt vector address from the VIC, eliminating one of the memory accesses typically required in traditional ARM implementations.

#### 3.9.3 Interrupt sources

The 32 interrupt request signals coming into the VIC on 32 IRQ channels are from various sources; 5 from a wake-up unit and the remaining 27 come from internal sources on the STR91xFA such as on-chip peripherals, see *Table 6*. Optionally, firmware may force an interrupt on any IRQ channel.

One of the 5 interrupt requests generated by the wake-up unit (IRQ25 in *Table 6*) is derived from the logical OR of all 32 inputs to the wake-up unit. Any of these 32 inputs may be used to wake up the CPU and cause an interrupt. These 32 inputs consist of 30 external interrupts on selected and enabled GPIO pins, plus the RTC interrupt, and the USB Resume interrupt.

## 5 Pin description

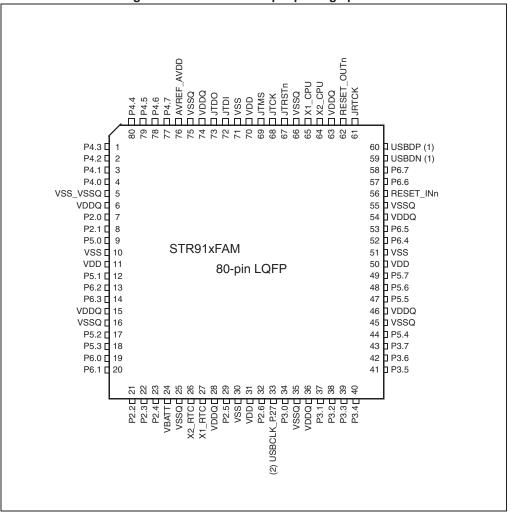

Figure 7. STR91xFAM 80-pin package pinout

1. NU (Not Used) on STR910FAM devices. Pin 59 is not connected, pin 60 must be pulled up by a 1.5Kohm resistor to VDDQ.

2. No USBCLK function on STR910FAM devices.

| F      | Packa   | age      |             | е           |                            |                              | Alternate functions          |                        |                              |                              |

|--------|---------|----------|-------------|-------------|----------------------------|------------------------------|------------------------------|------------------------|------------------------------|------------------------------|

| LQFP80 | LQFP128 | LFBGA144 | Pin<br>name | Signal type | Default pin<br>function    | Default<br>input<br>function | Alternate<br>input 1         | Alternate<br>output 1  | Alternate<br>output 2        | Alternate<br>output 3        |

| -      | 118     | E6       | P7.6        | I/O         | GPIO_7.6,<br>GP Input, HiZ | EXINT30,<br>External Intr    | TIM3_ICAP1,<br>Input Capture | GPIO_7.6,<br>GP Output | 8b) EMI_A6,<br>16b) EMI_A22  | EMI_CS1n,<br>EMI Chip Select |

| -      | 119     | A5       | P7.7        | I/O         | GPIO_7.7,<br>GP Input, HiZ | EXINT31,<br>External Intr    | TIM3_ICAP2,<br>Input Capture | GPIO_7.7,<br>GP Output | EMI_CS0n,<br>EMI chip select | 16b) EMI_A23,<br>8b) EMI_A7  |

| -      | 26      | L1       | P8.0        | I/O         | GPIO_8.0,<br>GP Input, HiZ | -                            | -                            | GPIO_8.0,<br>GP Output | 8b) EMI_D0,<br>16b) EMI_AD0  | -                            |

| -      | 28      | H3       | P8.1        | I/O         | GPIO_8.1,<br>GP Input, HiZ | -                            | -                            | GPIO_8.1,<br>GP Output | 8b) EMI_D1,<br>16b) EMI_AD1  | -                            |

| -      | 30      | J2       | P8.2        | I/O         | GPIO_8.2,<br>GP Input, HiZ | -                            | -                            | GPIO_8.2,<br>GP Output | 8b) EMI_D2,<br>16b) EMI_AD2  | -                            |

| -      | 32      | K2       | P8.3        | I/O         | GPIO_8.3,<br>GP Input, HiZ | -                            | -                            | GPIO_8.3,<br>GP Output | 8b) EMI_D3,<br>16b) EMI_AD3  | -                            |

| -      | 34      | L3       | P8.4        | I/O         | GPIO_8.4,<br>GP Input, HiZ | -                            | -                            | GPIO_8.4,<br>GP Output | 8b) EMI_D4,<br>16b) EMI_AD4  | -                            |

| -      | 36      | J4       | P8.5        | I/O         | GPIO_8.5,<br>GP Input, HiZ | -                            | -                            | GPIO_8.5,<br>GP Output | 8b) EMI_D5,<br>16b) EMI_AD5  | -                            |

| -      | 38      | M2       | P8.6        | I/O         | GPIO_8.6,<br>GP Input, HiZ | -                            | -                            | GPIO_8.6,<br>GP Output | 8b) EMI_D6,<br>16b) EMI_AD6  | -                            |

| -      | 44      | K5       | P8.7        | I/O         | GPIO_8.7,<br>GP Input, HiZ | -                            | -                            | GPIO_8.7,<br>GP Output | 8b) EMI_D7,<br>16b) EMI_AD7  | -                            |

|        |         |          |             |             |                            |                              |                              |                        |                              |                              |

| -      | 46      | M6       | P9.0        | I/O         | GPIO_9.0,<br>GP Input, HiZ | -                            | -                            | GPIO_9.0,<br>GP Output | 8b) EMI_A8<br>16b) EMI_AD8   | -                            |

| -      | 47      | M7       | P9.1        | I/O         | GPIO_9.1,<br>GP Input, HiZ | -                            | -                            | GPIO_9.1,<br>GP Output | 8b) EMI_A9,<br>16b) EMI_AD9  | -                            |

| -      | 50      | K6       | P9.2        | I/O         | GPIO_9.2,<br>GP Input, HiZ | -                            | -                            | GPIO_9.2,<br>GP Output | 8b) EMI_A10,<br>16b)EMI_AD10 | -                            |

| -      | 51      | J6       | P9.3        | I/O         | GPIO_9.3,<br>GP Input, HiZ | -                            | -                            | GPIO_9.3,<br>GP Output | 8b) EMI_A11,<br>16b)EMI_AD11 | -                            |

| -      | 52      | H6       | P9.4        | I/O         | GPIO_9.4,<br>GP Input, HiZ | -                            | -                            | GPIO_9.4,<br>GP Output | 8b) EMI_A12,<br>16b)EMI_AD12 | -                            |

| -      | 58      | L8       | P9.5        | I/O         | GPIO_9.5,<br>GP Input, HiZ | -                            | -                            | GPIO_9.5,<br>GP Output | 8b) EMI_A13,<br>16b)EMI_AD13 | -                            |

| -      | 62      | M9       | P9.6        | I/O         | GPIO_9.6,<br>GP Input, HiZ | -                            | -                            | GPIO_9.6,<br>GP Output | 8b) EMI_A14,<br>16b)EMI_AD14 | -                            |

| -      | 64      | K9       | P9.7        | I/O         | GPIO_9.7,<br>GP Input, HiZ | -                            | -                            | GPIO_9.7,<br>GP Output | 8b) EMI_A15,<br>16b)EMI_AD15 | -                            |

Table 8. Device pin description (continued)

| Table 8. Device pin description (continued) | in description (continued) | descriptio | pin | Device | Table 8. |

|---------------------------------------------|----------------------------|------------|-----|--------|----------|

|---------------------------------------------|----------------------------|------------|-----|--------|----------|

| F      | Packa   | age      |                      | đ           |                                                                                                                                                       |                              | escription (d        | ,                     | functions             |                       |

|--------|---------|----------|----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------|-----------------------|-----------------------|-----------------------|

| LQFP80 | LQFP128 | LFBGA144 | Pin<br>name          | Signal type | Default pin<br>function                                                                                                                               | Default<br>input<br>function | Alternate<br>input 1 | Alternate<br>output 1 | Alternate<br>output 2 | Alternate<br>output 3 |

| -      | 21      | G4       | EMI_<br>BWR_<br>WRLn | 0           | EMI byte write<br>strobe (8 bit<br>mode) or low<br>byte write<br>strobe (16 bit<br>mode)<br>Can also be<br>configured as<br>EMI_LBn in<br>BGA package |                              |                      | N/A                   |                       |                       |

| -      | 22      | H1       | EMI_<br>WRHn         | 0           | EMI high byte<br>write strobe<br>(16-bit mode)<br>Can also be<br>configured as<br>EMI_UBn in<br>BGA package                                           | N/A                          |                      |                       |                       |                       |

| -      | 74      | J10      | EMI_ALE              | 0           | EMI address<br>latch enable<br>(mux mode)                                                                                                             | N/A                          |                      |                       |                       |                       |

| -      | 75      | J9       | EMI_<br>RDn          | 0           | EMI read<br>strobe                                                                                                                                    | N/A                          |                      |                       |                       |                       |

| -      | -       | H8       | EMI_<br>BAAn         | 0           | EMI Burst<br>address<br>advance                                                                                                                       | N/A                          |                      |                       |                       |                       |

| -      | -       | K8       | EMI_<br>WAITn        | I           | EMI Wait input<br>for burst mode<br>device                                                                                                            |                              |                      | N/A                   |                       |                       |

| -      | -       | M8       | EMI_<br>BCLK         | 0           | EMI bus clock                                                                                                                                         |                              |                      | N/A                   |                       |                       |

| -      | -       | A12      | EMI_<br>WEn          | 0           | EMI write<br>enable                                                                                                                                   |                              |                      | N/A                   |                       |                       |

| -      | 91      | E10      | TAMPER<br>_IN        | I           | Tamper<br>detection input                                                                                                                             |                              |                      | N/A                   |                       |                       |

| -      | 94      | D11      | MII_<br>MDIO         | I/O         | MAC/PHY<br>management<br>data line                                                                                                                    |                              |                      | N/A                   |                       |                       |

| 59     | 95      | D10      | USBDN                | I/O         | USB data (-)<br>bus connect                                                                                                                           |                              |                      | N/A                   |                       |                       |

| 60     | 96      | C11      | USBDP                | I/O         | USB data (+)<br>bus connect                                                                                                                           |                              |                      | N/A                   |                       |                       |

| 56     | 89      | C12      | RESET<br>_INn        | I           | External reset input                                                                                                                                  |                              |                      | N/A                   |                       |                       |

| 62     | 100     | A9       | RESET<br>_OUTn       | 0           | Global or<br>System reset<br>output                                                                                                                   |                              |                      | N/A                   |                       |                       |

| 65     | 104     | A10      | X1_CPU               | I           | CPU oscillator<br>or crystal input                                                                                                                    |                              |                      | N/A                   |                       |                       |

| 64     | 103     | A11      | X2_CPU               | 0           | CPU crystal connection                                                                                                                                |                              |                      | N/A                   |                       |                       |

| <b>_</b> | Dect    |          |                | 1           |                                                                                      | Alternate functions          |                      |                       |                       |                       |

|----------|---------|----------|----------------|-------------|--------------------------------------------------------------------------------------|------------------------------|----------------------|-----------------------|-----------------------|-----------------------|

|          | Packa   | age      |                | ЭС          |                                                                                      |                              |                      | Alternate             | tunctions             | 1                     |

| LQFP80   | LQFP128 | LFBGA144 | Pin<br>name    | Signal type | Default pin<br>function                                                              | Default<br>input<br>function | Alternate<br>input 1 | Alternate<br>output 1 | Alternate<br>output 2 | Alternate<br>output 3 |

| 27       | 42      | M5       | X1_RTC         | I           | RTC oscillator<br>or crystal input<br>(32.768 kHz)                                   |                              |                      | N/A                   |                       |                       |

| 26       | 41      | M4       | X2_RTC         | 0           | RTC crystal connection                                                               |                              |                      | N/A                   |                       |                       |

| 61       | 97      | B11      | JRTCK          | 0           | JTAG return<br>clock or RTC<br>clock                                                 |                              |                      | N/A                   |                       |                       |

| 67       | 107     | D8       | JTRSTn         | I           | JTAG TAP<br>controller reset                                                         |                              |                      | N/A                   |                       |                       |

| 68       | 108     | E8       | JTCK           | I           | JTAG clock                                                                           |                              |                      | N/A                   |                       |                       |

| 69       | 111     | A6       | JTMS           | I           | JTAG mode<br>select                                                                  |                              |                      | N/A                   |                       |                       |

| 72       | 115     | C6       | JTDI           | I           | JTAG data in                                                                         |                              |                      | N/A                   |                       |                       |

| 73       | 117     | B6       | JTDO           | 0           | JTAG data out                                                                        |                              |                      | N/A                   |                       |                       |

|          |         |          |                |             |                                                                                      |                              |                      |                       |                       |                       |

| -        | 122     | A3       | AVDD           | v           | ADC analog<br>voltage source,<br>2.7 V - 3.6 V                                       |                              |                      | N/A                   |                       |                       |

| -        | 4       | C3       | AVSS           | G           | ADC analog<br>ground                                                                 | N/A                          |                      |                       |                       |                       |

| 5        | -       | -        | AVSS_<br>VSSQ  | G           | Common<br>ground point<br>for digital I/O &<br>analog ADC                            |                              |                      | N/A                   |                       |                       |

| -        | 123     | A2       | AVREF          | v           | ADC reference voltage input                                                          |                              |                      | N/A                   |                       |                       |

| 76       | -       | -        | AVREF_<br>AVDD | v           | Combined<br>ADC ref<br>voltage and<br>ADC analog<br>voltage source,<br>2.7 V - 3.6 V |                              |                      | N/A                   |                       |                       |

| 24       | 39      | M3       | VBATT          | v           | Standby<br>voltage input<br>for RTC and<br>SRAM backup                               |                              |                      | N/A                   |                       |                       |

| 6        | 9       | E1       | VDDQ           | V           |                                                                                      |                              |                      |                       |                       |                       |

| 15       | 23      | J1       | VDDQ           | V           |                                                                                      |                              |                      |                       |                       |                       |

| 36       | 57      | -        | VDDQ           | V           |                                                                                      |                              |                      |                       |                       |                       |

| 46       | 73      | K12      | VDDQ           | V           | V Source for                                                                         |                              |                      |                       |                       |                       |

| 54       | 86      | B5       | VDDQ           | V           | I/O and USB.<br>2.7 V to 3.6 V                                                       |                              |                      | N/A                   |                       |                       |

| 28       | 43      | L5       | VDDQ           | V           | 2.7 V (0 0.0 V                                                                       |                              |                      |                       |                       |                       |

| 63       | 102     | H7       | VDDQ           | V           |                                                                                      |                              |                      |                       |                       |                       |

| 74       | 120     | D9       | VDDQ           | V           |                                                                                      |                              |                      |                       |                       |                       |

| -        | -       | F9       | VDDQ           | V           |                                                                                      |                              |                      |                       |                       |                       |

Table 8. Device pin description (continued)

DocID13495 Rev 7

### 7.4 **RESET\_INn and power-on-reset characteristics**

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_{A}$  = -40 / 85  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol              | Parameter                              | Test conditions                                                                            |                    | Unit |     |      |  |

|---------------------|----------------------------------------|--------------------------------------------------------------------------------------------|--------------------|------|-----|------|--|

| Symbol              | Farameter                              | Test conditions                                                                            | Min <sup>(1)</sup> | Тур  | Max | Onit |  |

| t <sub>RINMIN</sub> | RESET_INn Valid Active Low             |                                                                                            | 100                |      |     | ns   |  |

| t <sub>POR</sub>    | Power-On-Reset Condition duration      | V <sub>DDQ</sub> ,V <sub>DD</sub> ramp<br>time is less than<br>10ms: 0V to V <sub>DD</sub> | 10                 |      |     | ms   |  |

| t <sub>RSO</sub>    | RESET_OUT Duration<br>(Watchdog reset) |                                                                                            | one PCLK           |      |     | ns   |  |

| Table 13. RESET | _INn and power-on-reset | characteristics |

|-----------------|-------------------------|-----------------|

|-----------------|-------------------------|-----------------|

1. Data based on bench measurements, not tested in production.

## 7.5 LVD electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_{A}$  = -40 / 85 °C unless otherwise specified.

| Symbol                       | Parameter                                    | Test       |      | Unit |      |      |

|------------------------------|----------------------------------------------|------------|------|------|------|------|

| Symbol                       | Farameter                                    | conditions | Min  | Тур  | Max  | Unit |

| V <sub>DD_LVD+</sub> (1.8V)  | LVD threshold during V <sub>DD</sub> rise    |            | 1.43 | 1.50 | 1.58 | V    |

| V <sub>DD_LVD-</sub> (1.8V)  | LVD threshold during V <sub>DD</sub> fall    |            | 1.33 | 1.40 | 1.47 | V    |

| V <sub>DD_BRN</sub> (1.8V)   | V <sub>DD</sub> brown out warning threshold  |            |      | 1.65 |      | V    |

| V <sub>DDQ_LVD+</sub> (3.0V) | LVD threshold during V <sub>DDQ</sub> rise   | (1)(2)     | 2.32 | 2.45 | 2.57 | V    |

| V <sub>DDQ_LVD-</sub> (3.0V) | LVD threshold during V <sub>DDQ</sub> fall   | (1)(2)     | 2.23 | 2.35 | 2.46 | v    |

| V <sub>DDQ_BRN</sub> (3.0V)  | V <sub>DDQ</sub> brown out warning threshold | (1)(2)     |      | 2.65 |      | V    |

| V <sub>DDQ_LVD+</sub> (3.3V) | LVD threshold during V <sub>DDQ</sub> rise   | (2)(3)     | 2.61 | 2.75 | 2.89 | V    |

| V <sub>DDQ_LVD-</sub> (3.3V) | LVD threshold during V <sub>DDQ</sub> fall   | (2)(3)     | 2.52 | 2.65 | 2.78 |      |

| V <sub>DDQ_BRN</sub> (3.3V)  | V <sub>DDQ</sub> brown out warning threshold | (2)(3)     |      | 2.95 |      | V    |

Table 14. LVD electrical characteristics

1. For  $V_{DDQ}$  I/O voltage operating at 2.7 - 3.3V.

Selection of V<sub>DDQ</sub> operation range is made using configuration software from ST, or IDE from 3rd parties. The default condition is V<sub>DDQ</sub>=2.7V - 3.3V.

3. For  $V_{\text{DDQ}}$  I/O voltage operating at 3.0 - 3.6V.

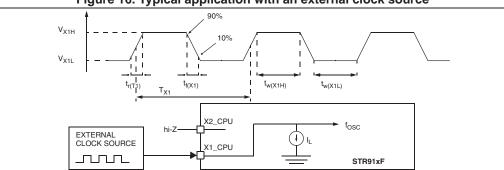

#### Figure 16. Typical application with an external clock source

#### 7.7.3 RTC clock generated from a crystal/ceramic resonator

The RTC (Real-Time Clock) can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results obtained with typical external components specified in *Table 20 & Table 21*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For CL1 and CL2 it is recommended to use high-quality ceramic capacitors in the 5 pF to 16 pF range, selected to match the requirements of the crystal or resonator. CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2.

Load capacitance CL has the following formula:

$CL = CL1 \times CL2 / (CL1 + CL2) + Cstray$

where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

Caution: Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF, and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

Conditions:  $V_{DDO}$  = 2.7 - 3.6 V,  $V_{DD}$  = 1.65 - 2 V,  $T_A$  = -40 / 85 °C unless otherwise specified.

| Symbol                  | Parameter                                  | Test                   | Va                            | Unit |     |          |

|-------------------------|--------------------------------------------|------------------------|-------------------------------|------|-----|----------|

| Symbol                  | Falameter                                  | conditions             | Min                           | Тур  | Max | Onic     |

| R <sub>F</sub>          | External feedback resistor                 |                        |                               | 22   |     | MΩ       |

| V <sub>START(RTC)</sub> | Oscillator start voltage                   |                        | $V_{DD_LVD^+}$ <sup>(1)</sup> |      |     | V        |

| g <sub>M</sub>          | Oscillator transconductance <sup>(2)</sup> | Start-up               | 1.8                           |      |     | µA/Volts |

| t <sub>STUP(RTC)</sub>  | Oscillator Start-up Time <sup>(2)</sup>    | V <sub>DD</sub> stable |                               |      | 1   | S        |

Table 20. RTC oscillator electrical characteristics

1. Refer to Table 14 for min. value of  $V_{DD LVD+}$

2. Data based on bench measurements, not tested in production.

#### 7.9.2 Electro magnetic interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbol           | Sumbol Devenator              | Conditions                                                                 | Monitored                         | Max<br>[fosc/fo                   | Unit |      |

|------------------|-------------------------------|----------------------------------------------------------------------------|-----------------------------------|-----------------------------------|------|------|

| Symbol Parameter | Conditions                    | Frequency Band                                                             | 24 MHz /<br>48 MHz <sup>(1)</sup> | 24 MHz /<br>96 MHz <sup>(1)</sup> |      |      |

|                  |                               | $V_{DDQ} = 3.3 \text{ V}, V_{DD} = 1.8 \text{ V}, T_{A} = +25 \text{ °C},$ | 0.1 MHz to 30 MHz                 | 14                                | 10   |      |

| S <sub>EMI</sub> | T <sub>A</sub> =              |                                                                            | 30 MHz to<br>130 MHz              | 18                                | 19   | dBμV |

|                  | conforming to SAE J<br>1752/3 | 130 MHz to 1GHz                                                            | 18                                | 22                                |      |      |

|                  |                               | SAE EMI Level                                                              | 4                                 | 4                                 | -    |      |

| Table | 28. | EMI | data |

|-------|-----|-----|------|

|-------|-----|-----|------|

1. Data based on characterization results, not tested in production.

2. BGA and LQFP devices have similar EMI characteristics.

#### 7.9.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

#### 7.9.4 Electro-static discharge (ESD)

Electro-Static Discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                                    | Conditions                                           | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|------------------------------------------------------------|------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)     | $T_A = +25^{\circ}C$<br>conforming to<br>JESD22-A114 | 2     | +/-2000                         | V    |

| V <sub>ESD(CDM)</sub> | Electro-static discharge voltage<br>(Charged Device Model) | $T_A = +25^{\circ}C$<br>conforming to<br>JESD22-C101 | II    | 1000                            | v    |

| Table | 29. | ESD | data |

|-------|-----|-----|------|

|-------|-----|-----|------|

1. Data based on characterization results, not tested in production.

#### Mux read

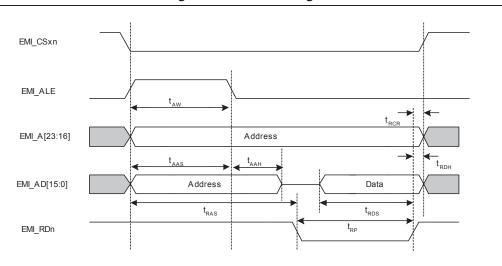

Figure 21. Mux read diagram

#### Table 36. Mux read times

| Symbol           | Parameter                 | Value                                            |                                           |  |  |

|------------------|---------------------------|--------------------------------------------------|-------------------------------------------|--|--|

| Symbol           | Farameter                 | Min                                              | Мах                                       |  |  |

| t <sub>RCR</sub> | Read to CSn<br>inactive   | 0                                                | 1.5 ns                                    |  |  |

| t <sub>RAS</sub> | Read address setup time   | ((WSTOEN) x t <sub>BCLK</sub> )- 4 ns            | ((WSTOEN) x t <sub>BCLK</sub> )           |  |  |

| t <sub>RDS</sub> | Read data setup<br>time   | 12 ns                                            | -                                         |  |  |

| t <sub>RDH</sub> | Read data hold time       | 0                                                |                                           |  |  |

| t <sub>RP</sub>  | Read pulse width          | ((WSTRD-WSTOEN+1) x t <sub>BCLK</sub> ) - 0.5 ns | ((WSTRD-WSTOEN+1) x $t_{BCLK}$ ) + 2.5 ns |  |  |

| t <sub>AW</sub>  | ALE pulse width           | (ALE_LENGTH x t <sub>BCLK</sub> ) - 3.5 ns       | (ALE_LENGTH x t <sub>BCLK</sub> )         |  |  |

| t <sub>AAS</sub> | Address to ALE setup time | (ALE_LENGTH x t <sub>BCLK</sub> ) - 3.5 ns       | (ALE_LENGTH x t <sub>BCLK</sub> )         |  |  |

| t <sub>AAH</sub> | Address to ALE hold time  | (t <sub>BCLK</sub> /2)- 1 ns                     | (t <sub>BCLK</sub> /2) + 2 ns             |  |  |

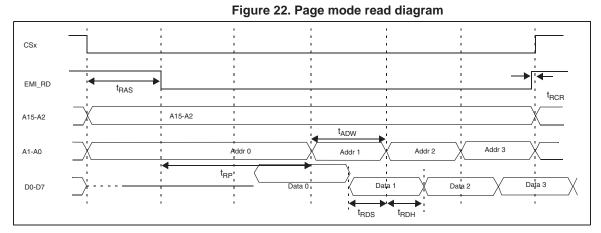

#### Page mode read

#### Table 37. Page mode read times

| Symbol           | Devenetor               | Value                                   |                                                |  |  |

|------------------|-------------------------|-----------------------------------------|------------------------------------------------|--|--|

| Symbol           | Parameter               | Min                                     | Мах                                            |  |  |

| t <sub>RDH</sub> | Read data hold time     | 0                                       |                                                |  |  |

| t <sub>RDS</sub> | Read data setup time    | 12 ns                                   | -                                              |  |  |

| t <sub>ADW</sub> | ALE pulse width         | (t <sub>BCLK</sub> ) - 1.5 ns           | (t <sub>BCLK</sub> )+ 0.5 ns                   |  |  |

| t <sub>RAS</sub> | Read address setup time | ((WSTOEN) x t <sub>BCLK</sub> )         | ((WSTOEN) x t <sub>BCLK</sub> ) + 2.5 ns       |  |  |

| t <sub>RP</sub>  | Read pulse width        | ((WSTRD-WSTOEN+1) x t <sub>BCLK</sub> ) | ((WSTRD-WSTOEN+1) x t <sub>BCLK</sub> ) + 2 ns |  |  |

| t <sub>RCR</sub> | Read to CSn inactive    | 0                                       | 1 ns                                           |  |  |

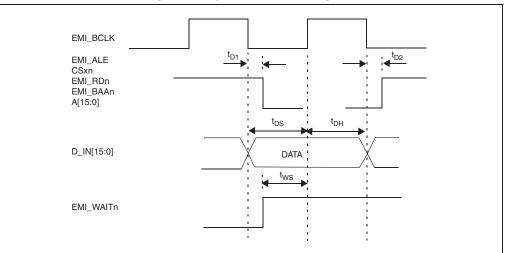

#### Sync burst read

Figure 24. Sync burst read diagram

| Table 39. Sync burst read tim |

|-------------------------------|

|-------------------------------|

| Querra had         | Demonster               | Val                           | lue                         |

|--------------------|-------------------------|-------------------------------|-----------------------------|

| Symbol             | Parameter               | Min                           | Мах                         |

| t <sub>D1BAA</sub> | BAA t <sub>D1</sub>     | 0 ns                          | 2 ns                        |

| t <sub>D2BAA</sub> | BAA t <sub>D2</sub>     | 0.5ns                         | 2.5 ns                      |

| t <sub>D1ALE</sub> | ALE t <sub>D1</sub>     | 1 ns                          | 3.5 ns                      |

| t <sub>D2ALE</sub> | ALE t <sub>D2</sub>     | (t <sub>BCLK</sub> /2)+0.5 ns | (t <sub>BCLK</sub> /2)+3 ns |

| t <sub>D1RD</sub>  | RD t <sub>D1</sub>      | 0                             | 2 ns                        |

| t <sub>D2RD</sub>  | RD t <sub>D2</sub>      | 0.5 ns                        | 2.5 ns                      |

| t <sub>D1A</sub>   | Address t <sub>D1</sub> | 2 ns                          | 4 ns                        |

| t <sub>D2A</sub>   | Address t <sub>D2</sub> | 2.5 ns                        | 3.5 ns                      |

| t <sub>D1CS</sub>  | CS t <sub>D1</sub>      | 0.5 ns                        | 3 ns                        |

| t <sub>D2CS</sub>  | CS t <sub>D2</sub>      | 1 ns                          | 3.5 ns                      |

| t <sub>WS</sub>    | WAIT set up time        | 1 ns                          | 4 ns                        |

| t <sub>DS</sub>    | Data setup time         | 4.5 ns                        | -                           |

| t <sub>DH</sub>    | Data hold time          | 0                             | -                           |

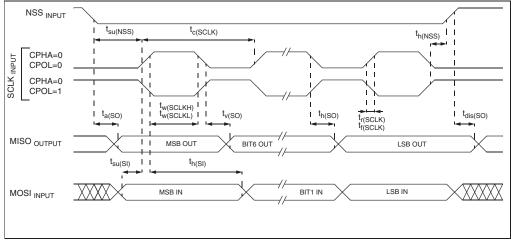

#### 7.12.5 SPI electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6 V,  $V_{DD}$  = 1.65 - 2 V,  $T_A$  = -40 / 85 °C unless otherwise specified.

| Cumbal                 | Parameter                     | Test conditions        | Value |     | Unit              |

|------------------------|-------------------------------|------------------------|-------|-----|-------------------|

| Symbol                 | Parameter                     | Test conditions        | Тур   | Max | Unit              |

| f <sub>SCLK</sub>      | SDI alaak fraguanay           | Master                 |       | 24  | MHz               |

| 1/t <sub>c(SCLK)</sub> | SPI clock frequency           | Slave                  |       | 4   | IVITIZ            |

| t <sub>r(SCLK)</sub>   | SPI clock rise and fall times | 50pF load              | 0     | .1  | V/ns              |

| t <sub>f(SCLK)</sub>   | or relock tise and fair times |                        | 0     | . 1 | V/113             |

| t <sub>su(SS)</sub>    | SS setup time                 | Slave                  | 1     |     |                   |

| t <sub>h(SS)</sub>     | SS hold time                  | Slave                  | 1     |     |                   |

| t <sub>w(SCLKH)</sub>  | SCLK high and low time        | Master                 | 1     |     |                   |

| t <sub>w(SCLKL)</sub>  |                               | Slave                  |       |     |                   |

| t <sub>su(MI)</sub>    | Data input setup time         | Master                 | TBD   |     |                   |

| t <sub>su(SI)</sub>    |                               | Slave                  | 5     |     |                   |

| t <sub>h(MI)</sub>     | Data input hold time          | Master                 | TBD   |     |                   |

| t <sub>h(SI)</sub>     | Data input noid time          | Slave                  | 6     |     | t <sub>PCLK</sub> |

| t <sub>a(SO)</sub>     | Data output access time       | Slave                  |       | 6   |                   |

| t <sub>dis(SO)</sub>   | Data output disable time      | Slave                  |       | 6   |                   |

| t <sub>v(SO)</sub>     | Data output valid time        | Slave (after enable    |       | 6   |                   |

| t <sub>h(SO)</sub>     | Data output hold time         | edge)                  | 0     |     |                   |

| t <sub>v(MO)</sub>     | Data output valid time        | Master (before capture | 0.25  |     |                   |

| t <sub>h(MO)</sub>     | Data output hold time         | edge)                  | 0.25  |     |                   |

#### Table 46. SPI electrical characteristics

#### Figure 30. SPI slave timing diagram with CPHA = 0

DocID13495 Rev 7

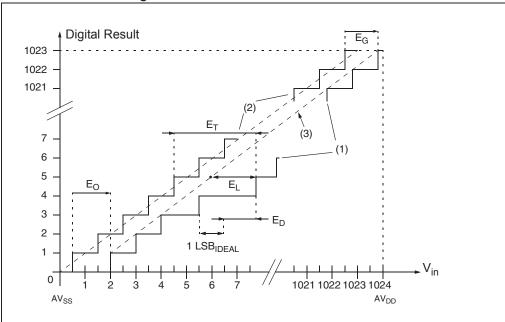

Figure 33. ADC conversion characteristics

1. Legend: (1) Example of an actual transfer curve (2) The ideal transfer curve (3) End point correlation line  $E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves.  $E_G$  = Offset Error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain Error: deviation between the last ideal transition and the last actual one.  $E_D$  = Differential Linearity Error: maximum deviation between actual steps and the ideal one.  $E_L$  = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

#### **Equation 1**

$$1LSB_{IDEAL} = \frac{V_{DDA} - V_{SSA}}{1024}$$

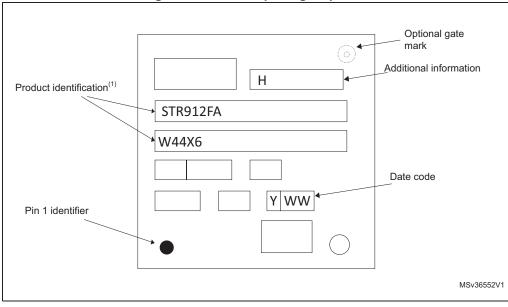

#### Marking of engineering samples for LQFP128

The following figure shows the engineering sample marking for the LQFP128 package. Only the information field containing the engineering sample marking is shown.

Figure 44. LQFP128 package top view

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol           |       | millimeters | ers inches <sup>(1)</sup> |        |        |        |

|------------------|-------|-------------|---------------------------|--------|--------|--------|

| Symbol           | Min   | Тур         | Max                       | Тур    | Min    | Max    |

| A <sup>(2)</sup> | -     | -           | 1.700                     |        |        | 0.0669 |

| A1               | 0.210 | -           | -                         | 0.0083 |        |        |

| A2               | -     | 1.060       | -                         |        | 0.0417 |        |

| A3               |       | 0.026       |                           |        | 0.0010 |        |

| A4               | -     | 0.800       | -                         | -      | 0.0315 | -      |

| b                | 0.350 | 0.400       | 0.450                     | 0.0138 | 0.0157 | 0.0177 |

| D                | 9.850 | 10.000      | 10.150                    | 0.3878 | 0.3937 | 0.3996 |

| D1               | -     | 8.800       | -                         | -      | 0.3465 | -      |

| E                | 9.850 | 10.000      | 10.150                    | 0.3878 | 0.3937 | 0.3996 |

| E1               | -     | 8.800       | -                         | -      | 0.3465 | -      |

| е                | -     | 0.800       | -                         | -      | 0.0315 | -      |

| F                | -     | 0.600       | -                         | -      | 0.0236 | -      |

| ddd              | 0.100 |             |                           |        | 0.0039 |        |

| eee              | 0.150 |             |                           | 0.0059 |        |        |

| fff              |       | 0.080       |                           |        | 0.0031 |        |

# Table 52.LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,0.8 mm pitch, package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. STATSChipPAC package dimensions.

## 11 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09-May-2007 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 26-Nov-2007 | 2        | Updated Standby current in Table 15: Supply current<br>characteristics on page 64<br>Added Section 7.1: Parameter conditions on page 58<br>Added Section 7.7.2: X1_CPU external clock source on page 67<br>Updated Section 7.11: External memory bus timings on page 76<br>Added Figure 14: LVD reset delay case 3 on page 63<br>Added Table 48 and Table 49 in ADC characteristics section<br>Added min/max values for E, D, E1, D1 in Figure 43 on page 98                                                                                                                                                                                                                                                                                                        |

| 14-May-2008 | 3        | Added 1MB and 2M devices, creating merged datasheet from<br>seperate STR91xFAx32, 42, 44, 46 and 47 devices.<br>Added STR912FAW32 to Table 1: Device summary on page 1<br>Added paragraph on voltage supply shutdown in Section 3.12 on<br>page 24<br>Removed DMA feature for I2C in Section 3.21 on page 33<br>Updated Sleep mode current in Table 10: Current characteristics<br>on page 60<br>Added Table 16: Typical current consumption at 25 °C on page 65<br>Updated operating conditions for V <sub>DD</sub> and f <sub>CPUCLK</sub> in Section 7.3<br>on page 61 and Section 7.7: Clock and timing characteristics on<br>page 66<br>Changed SPI master t <sub>SU</sub> and t <sub>H to</sub> TBD in Table 46: SPI electrical<br>characteristics on page 88 |

| 17-Jul-2008 | 4        | Updated Section 3.10.6: UART and SSP clock (BRCLK) on<br>page 22<br>Updated Table 11: Operating conditions on page 61<br>Updated I <sub>SLEEP(IDDQ)</sub> in Table 15: Supply current characteristics<br>on page 64<br>Updated Table 17: Internal clock frequencies on page 66<br>Updated Table 31: I/O characteristics on page 75                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22-Dec-2008 | 5        | Updated Section 7.7.3 on page 68. Small text changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 55. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Jul-2009 | 6        | Section 3.13.7: Tamper detection: Removed information about<br>"Normally Closed/Tamper Open mode".<br>Table 31: I/O characteristics: Updated V <sub>HYS</sub> row.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3-Mar-2015  | 7        | Updated Figure 40: LQFP80 12 x 12 mm 80 pin low-profile quad<br>flat package outline on page 95, Figure 43: LQFP128 14 x 14 mm<br>128 pin low-profile quad flat package outline on page 98 and<br>Figure 45: LFBGA144 – 144-ball low profile fine pitch ball grid<br>array, 10 x 10 mm, 0.8 mm pitch, package outline on page 101<br>Updated Table 50: LQFP80 12 x12 mm low-profile quad flat<br>package mechanical data on page 96, Table 51: LQFP128 - 128-<br>pin, 14 x 14 mm low-profile quad flat package mechanical data on<br>page 99, and Table 52: LFBGA144 – 144-ball low profile fine pitch<br>ball grid array, 10 x 10 mm, 0.8 mm pitch, package mechanical<br>data on page 102<br>Added Figure 42: LQFP80 package top view on page 97,<br>Figure 43: LQFP128 14 x 14 mm 128 pin low-profile quad flat<br>package outline on page 98, Figure 44: LQFP128 package top<br>view on page 100 and Figure 45: LFBGA144 – 144-ball low profile<br>fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package<br>outline on page 101 |

Table 55. Document revision history