#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 16-Core                                                |

| Speed                      | 2000MIPS                                                      |

| Connectivity               | USB                                                           |

| Peripherals                | -                                                             |

| Number of I/O              | 104                                                           |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | -                                                             |

| RAM Size                   | 512K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 236-LFBGA                                                     |

| Supplier Device Package    | 236-FBGA (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xu216-512-fb236-i20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1  | xCORE Multicore Microcontrollers     | 2 |

|----|--------------------------------------|---|

| 2  | XU216-512-FB236 Features             | 4 |

| 3  | Pin Configuration                    | 5 |

| 4  | Signal Description                   | 6 |

| 5  | Example Application Diagram          |   |

| 6  | Product Overview                     |   |

| 7  | PLL                                  |   |

| 8  | Boot Procedure                       |   |

| 9  | Memory                               |   |

| 10 | USB PHY                              |   |

| iĭ | JTAG                                 |   |

| 12 | Board Integration                    |   |

| 13 | DC and Switching Characteristics     |   |

| 14 |                                      |   |

| 15 | Package Information                  |   |

|    |                                      |   |

|    | endices                              | 4 |

| A  | Configuration of the XU216-512-FB236 |   |

| B  | Processor Status Configuration       | / |

| C  | Tile Configuration                   |   |

| D  | Node Configuration                   |   |

| E  | USB Node Configuration               |   |

| F  | USB PHY Configuration                |   |

| G  | JTAG, xSCOPE and Debugging           |   |

| Н  | Schematics Design Check List         |   |

| 1  | PCB Layout Design Check List         | 7 |

| J  | Associated Design Documentation      | 8 |

| ĸ  | Related Documentation                | 8 |

| L  | Revision History                     | 9 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

# 2 XU216-512-FB236 Features

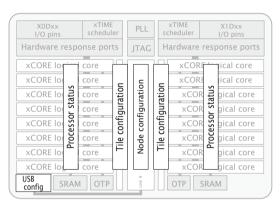

#### ► Multicore Microcontroller with Advanced Multi-Core RISC Architecture

- 16 real-time logical cores on 2 xCORE tiles

- Cores share up to 1000 MIPS

- Up to 2000 MIPS in dual issue mode

- Each logical core has:

- Guaranteed throughput of between 1/5 and 1/8 of tile MIPS

- 16x32bit dedicated registers

- 167 high-density 16/32-bit instructions

- All have single clock-cycle execution (except for divide)

- 32x32 ${\rightarrow}64$  bit MAC instructions for DSP, arithmetic and user-definable cryptographic functions

#### ▶ USB PHY, fully compliant with USB 2.0 specification

#### Programmable I/O

- 128 general-purpose I/O pins, configurable as input or output

- Up to 32 x 1bit port, 12 x 4bit port, 8 x 8bit port, 4 x 16bit port, 2 x 32bit port

8 xCONNECT links

- Port sampling rates of up to 60 MHz with respect to an external clock

- 64 channel endss (32 per tile) for communication with other cores, on or off-chip

#### Memory

- 512KB internal single-cycle SRAM (max 256KB per tile) for code and data storage

- 16KB internal OTP (max 8KB per tile) for application boot code

#### Hardware resources

- 12 clock blocks (6 per tile)

- 20 timers (10 per tile)

- 8 locks (4 per tile)

- ► JTAG Module for On-Chip Debug

#### Security Features

• Programming lock disables debug and prevents read-back of memory contents

-XM()S

• AES bootloader ensures secrecy of IP held on external flash memory

#### Ambient Temperature Range

- Commercial qualification: 0°C to 70°C

- Industrial qualification: -40 °C to 85 °C

- Speed Grade

- 20: 1000 MIPS

- Power Consumption

- 570 mA (typical)

- > 236-pin FBGA package 0.5 mm pitch

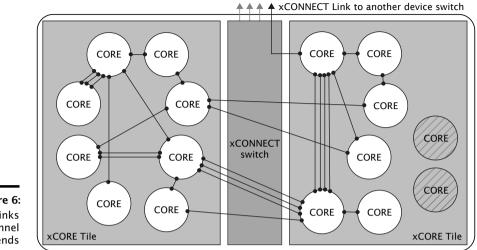

Figure 6: Switch, links and channel ends

and packet switched data can both be supported efficiently. Streams provide the fastest possible data rates between xCORE Tiles (up to 250 MBit/s), but each stream requires a single link to be reserved between switches on two tiles. All packet communications can be multiplexed onto a single link.

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-U Link Performance and Design Guide, X2999.

# 7 PLL

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock. The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 7:

Figure 7: PLL multiplier values and MODE pins

|      | Oscillator  | MC | DDE | Tile Boot   | PLL Ratio | PLL | setting | gs |  |

|------|-------------|----|-----|-------------|-----------|-----|---------|----|--|

|      | Frequency   | 1  | 0   | Frequency   |           | OD  | F       | R  |  |

| e 7: | 3.25-10 MHz | 0  | 0   | 130-400 MHz | 40        | 1   | 159     | 0  |  |

| lier | 9-25 MHz    | 1  | 1   | 144-400 MHz | 16        | 1   | 63      | 0  |  |

| ind  | 25-50 MHz   | 1  | 0   | 167-400 MHz | 8         | 1   | 31      | 0  |  |

| ins  | 50-100 MHz  | 0  | 1   | 196-400 MHz | 4         | 1   | 15      | 0  |  |

-XMOS

| Feature              | Bit  | Description                                                                                                                                                                                                                               |

|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                    |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Linl<br>access transforms an xCORE Tile into a "secure island<br>with other tiles free for non-secure user application<br>code. |

| Secure Boot          | 5    | The xCORE Tile is forced to boot from address 0 o<br>the OTP, allowing the xCORE Tile boot ROM to be<br>bypassed ( <i>see</i> §8).                                                                                                        |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                            |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                      |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                      |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                      |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                      |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up dates to all sectors and security register.                                                                                                                                               |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inte face to this OTP.                                                                                                                                                                    |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                       |

|                      | 2115 | General purpose software accessable security registe available to end-users.                                                                                                                                                              |

|                      | 3122 | General purpose user programmable JTAG UserII code extension.                                                                                                                                                                             |

Figure 13: Security register features

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

## 9.2 SRAM

Each xCORE Tile integrates a single 256KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

# 10 USB PHY

The USB PHY provides High-Speed and Full-Speed, device, host, and on-the-go functionality. The PHY is configured through a set of peripheral registers (Appendix F),

#### 12.2.1 General routing and placement guidelines

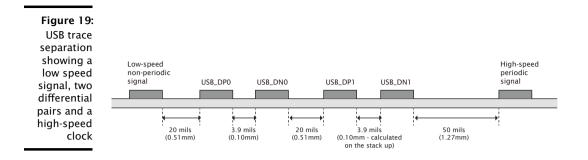

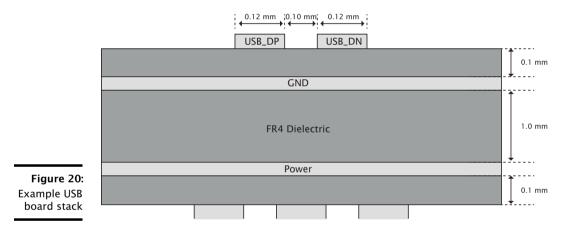

The following guidelines will help to avoid signal quality and EMI problems on high speed USB designs. They relate to a four-layer (Signal, GND, Power, Signal) PCB.

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS2-U16A-512-FB236 are on the top layer) closest to GND. Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

- Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible.

## 13.3 ESD Stress Voltage

Figure 24 ESD stress voltage

| 24: | Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|-----|--------|----------------------|-------|-----|------|-------|-------|

| ess | HBM    | Human body model     | -2.00 |     | 2.00 | KV    |       |

| ge  | CDM    | Charged Device Model | -500  |     | 500  | V     |       |

## 13.4 Reset Timing

|              | Symbol      | Parameters                                | MIN     | ТҮР  | MAX | UNITS | Notes |

|--------------|-------------|-------------------------------------------|---------|------|-----|-------|-------|

| Figure 25:   | T(RST)      | Reset pulse width                         | 5       |      |     | μs    |       |

| Reset timing | T(INIT)     | Initialization time                       |         |      | 150 | μs    | А     |

|              | A Shows the | time taken to start booting after PST N b | ac dono | high |     |       |       |

A Shows the time taken to start booting after RST\_N has gone high.

32

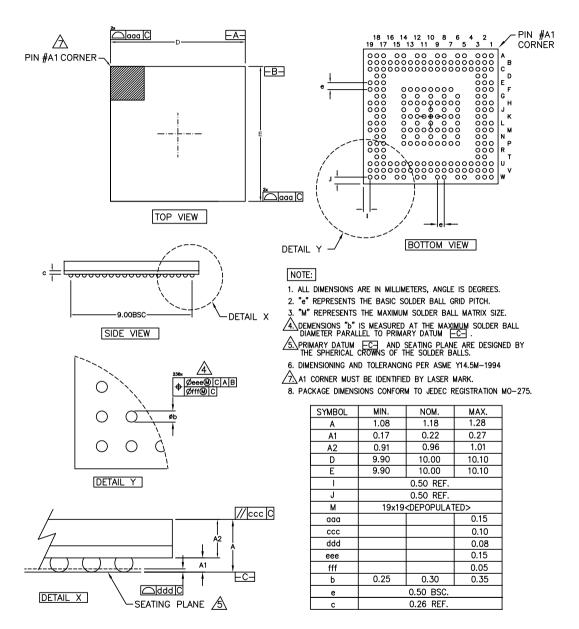

## 14 Package Information

-XMOS

# Appendices

# A Configuration of the XU216-512-FB236

The device is configured through banks of registers, as shown in Figure 33.

Figure 33: Registers

> The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

## A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0B. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

## A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile  $\rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnnn is the tile-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

control-token

24-bit response

16-bit

32-bit

control-token

192

channel-end identifier

register number

data

1

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

## A.4 Accessing a register of an analogue peripheral

Peripheral registers can be accessed through the interconnect using the functions write\_periph\_32(device, peripheral, ...), read\_periph\_32(device, peripheral, ...)  $\leftrightarrow$ , write\_periph\_8(device, peripheral, ...), and read\_periph\_8(device, peripheral  $\leftrightarrow$ , ...); where device is the name of the analogue device, and peripheral is the number of the peripheral. These functions implement the protocols described below.

A channel-end should be allocated to communicate with the configuration registers. The destination of the channel-end should be set to 0xnnnnpp02 where nnnn is the node-identifier and pp is the peripheral identifier.

35

| 0x12:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SSP | 31:0 | DRW  |      | Value.      |

#### **B.15 DGETREG operand 1: 0x13**

The resource ID of the logical core whose state is to be read.

| 0x13:     | Bits | Perm | Init | Description              |

|-----------|------|------|------|--------------------------|

| DGETREG   | 31:8 | RO   | -    | Reserved                 |

| operand 1 | 7:0  | DRW  |      | Thread number to be read |

#### B.16 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |  |

|------|------|------|----------------------------|--|

| 31:5 | RO   | -    | Reserved                   |  |

| 4:0  | DRW  |      | Register number to be read |  |

#### B.17 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                              |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 17:16 | DRW  |      | Number of the hardware breakpoint/watchpoint which caused<br>the interrupt (always 0 for =HOST= and =DCALL=). If multiple<br>breakpoints/watchpoints trigger at once, the lowest number is<br>taken.                     |

| 15:8  | DRW  |      | Number of thread which caused the debug interrupt (always 0 in the case of =HOST=).                                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point |

0x15: Debug interrupt type

| Bits     | Perm                                                                  | Init                                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31       | CRO                                                                   |                                                                                                                                                                                                                                                                                                    | Disables write permission on this register                                                                                                                                                                                                                                                    |

| 30:15    | RO                                                                    | -                                                                                                                                                                                                                                                                                                  | Reserved                                                                                                                                                                                                                                                                                      |

| 14       | CRO                                                                   |                                                                                                                                                                                                                                                                                                    | Disable access to XCore's global debug                                                                                                                                                                                                                                                        |

| 13       | RO                                                                    | -                                                                                                                                                                                                                                                                                                  | Reserved                                                                                                                                                                                                                                                                                      |

| 12       | CRO                                                                   |                                                                                                                                                                                                                                                                                                    | lock all OTP sectors                                                                                                                                                                                                                                                                          |

| 11:8 CRO |                                                                       | lock bit for each OTP sector                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                               |

| 7        | CRO                                                                   |                                                                                                                                                                                                                                                                                                    | Enable OTP reduanacy                                                                                                                                                                                                                                                                          |

| 6        | RO                                                                    | -                                                                                                                                                                                                                                                                                                  | Reserved                                                                                                                                                                                                                                                                                      |

| 5        | 5 CRO                                                                 | Override boot mode and read boot image from OTP                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                               |

| 4        | CRO                                                                   |                                                                                                                                                                                                                                                                                                    | Disable JTAG access to the PLL/BOOT configuration registers                                                                                                                                                                                                                                   |

| 3:1      | RO                                                                    | -                                                                                                                                                                                                                                                                                                  | Reserved                                                                                                                                                                                                                                                                                      |

| 0        | CRO                                                                   |                                                                                                                                                                                                                                                                                                    | Disable access to XCore's JTAG debug TAP                                                                                                                                                                                                                                                      |

|          | 31<br>30:15<br>14<br>13<br>12<br>11:8<br>7<br>6<br>5<br>5<br>4<br>3:1 | 31         CRO           30:15         RO           14         CRO           13         RO           14         CRO           15         CRO           11:8         CRO           11:8         CRO           6         RO           5         CRO           4         CRO           3:1         RO | 31         CRO           30:15         RO           14         CRO           13         RO           12         CRO           11:8         CRO           7         CRO           6         RO           5         CRO           4         CRO           5         CRO           31         RO |

0x07 Security configuration

## C.8 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27: Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| ratch         | 31:0 | CRW  |      | Value.      |

## C.9 PC of logical core 0: 0x40

Value of the PC of logical core 0.

0x40 PC of logical core 0

| <b>)x40:</b><br>gical | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ore 0                 | 31:0 | CRO  |      | Value.      |

-XMOS

## C.10 PC of logical core 1: 0x41

Value of the PC of logical core 1.

## C.24 SR of logical core 7: 0x67

Value of the SR of logical core 7

| 0x67:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 7        | 31:0 | CRO  |      | Value.      |

#### D.2 System switch description: 0x01

This register specifies the number of processors and links that are connected to this switch.

0x01 System switch description

|    | Bits  | Perm | Init | Description                          |

|----|-------|------|------|--------------------------------------|

| -  | 31:24 | RO   | -    | Reserved                             |

| l: | 23:16 | RO   |      | Number of SLinks on the SSwitch.     |

| h  | 15:8  | RO   |      | Number of processors on the SSwitch. |

| n  | 7:0   | RO   |      | Number of processors on the device.  |

#### D.3 Switch configuration: 0x04

This register enables the setting of two security modes (that disable updates to the PLL or any other registers) and the header-mode.

| Bits | Perm | Init | Description                                                                         |

|------|------|------|-------------------------------------------------------------------------------------|

| 31   | RW   | 0    | 0 = SSCTL registers have write access. $1 = SSCTL$ registers can not be written to. |

| 30:9 | RO   | -    | Reserved                                                                            |

| 8    | RW   | 0    | 0 = PLL_CTL_REG has write access. 1 = PLL_CTL_REG can not be written to.            |

| 7:1  | RO   | -    | Reserved                                                                            |

| 0    | RW   | 0    | 0 = 2-byte headers, $1 = 1$ -byte headers (reset as 0).                             |

**0x04:** Switch configuration

## D.4 Switch node identifier: 0x05

This register contains the node identifier.

**0x05** Switch node identifier

| <b>(05:</b> | Bits  | Perm | Init | Description                 |

|-------------|-------|------|------|-----------------------------|

| ode         | 31:16 | RO   | -    | Reserved                    |

| ifier       | 15:0  | RW   | 0    | The unique ID of this node. |

## D.5 PLL settings: 0x06

An on-chip PLL multiplies the input clock up to a higher frequency clock, used to clock the I/O, processor, and switch, see Oscillator. Note: a write to this register will cause the tile to be reset.

|            | Bits  | Perm | Init | Description                                     |

|------------|-------|------|------|-------------------------------------------------|

|            | 31:28 | RW   | 0    | The direction for packets whose dimension is F. |

|            | 27:24 | RW   | 0    | The direction for packets whose dimension is E. |

|            | 23:20 | RW   | 0    | The direction for packets whose dimension is D. |

| -          | 19:16 | RW   | 0    | The direction for packets whose dimension is C. |

|            | 15:12 | RW   | 0    | The direction for packets whose dimension is B. |

| 0x0D:      | 11:8  | RW   | 0    | The direction for packets whose dimension is A. |

| Directions | 7:4   | RW   | 0    | The direction for packets whose dimension is 9. |

| 8-15       | 3:0   | RW   | 0    | The direction for packets whose dimension is 8. |

# D.12 DEBUG\_N configuration, tile 0: 0x10

Configures the behavior of the DEBUG\_N pin.

0x1 DEBUG\_N con figuratio tile

|            | Bits | Perm | Init | Description                                                     |

|------------|------|------|------|-----------------------------------------------------------------|

| 10:<br>on- | 31:2 | RO   | -    | Reserved                                                        |

| on,        | 1    | RW   | 0    | Set 1 to enable GlobalDebug to generate debug request to XCore. |

| e 0        | 0    | RW   | 0    | Set 1 to enable inDebug bit to drive GlobalDebug.               |

## D.13 DEBUG\_N configuration, tile 1: 0x11

Configures the behavior of the DEBUG\_N pin.

0x1 DEBUG\_N co figuratio tile

| _         | Bits | Perm | Init | Description                                                     |

|-----------|------|------|------|-----------------------------------------------------------------|

| 1:<br>0n- | 31:2 | RO   | -    | Reserved                                                        |

| on,       | 1    | RW   | 0    | Set 1 to enable GlobalDebug to generate debug request to XCore. |

| : 1       | 0    | RW   | 0    | Set 1 to enable inDebug bit to drive GlobalDebug.               |

## D.14 Debug source: 0x1F

Contains the source of the most recent debug event.

$\cdot X MOS$

| Bits | Perm | Init | Description                                                    |

|------|------|------|----------------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                       |

| 4    | RW   |      | If set, external pin, is the source of last GlobalDebug event. |

| 3:2  | RO   | -    | Reserved                                                       |

| 1    | RW   |      | If set, XCore1 is the source of last GlobalDebug event.        |

| 0    | RW   |      | If set, XCore0 is the source of last GlobalDebug event.        |

**0x1F:** Debug source

## D.15 Link status, direction, and network: 0x20 .. 0x28

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                    |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |

| 15:12 | RO   | -    | Reserved                                                                                    |

| 11:8  | RW   | 0    | The direction that this link operates in.                                                   |

| 7:6   | RO   | -    | Reserved                                                                                    |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |

| 3     | RO   | -    | Reserved                                                                                    |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |

0x20 .. 0x28: Link status, direction, and network

## D.16 PLink status and network: 0x40 .. 0x47

These registers contain status information and the network number that each processor-link belongs to.

-XMOS-

XS2-U16A-512-FB236

| Bits  | Perm | Init | Description                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                    |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |

| 15:6  | RO   | -    | Reserved                                                                                    |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |

| 3     | RO   | -    | Reserved                                                                                    |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |

**0x40 .. 0x47:** PLink status and network

#### D.17 Link configuration and initialization: 0x80 .. 0x88

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                                                                   |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RW   |      | Write to this bit with '1' will enable the XLink, writing '0' will disable it. This bit controls the muxing of ports with overlapping xlinks. |

| 30    | RW   | 0    | 0: operate in 2 wire mode; 1: operate in 5 wire mode                                                                                          |

| 29:28 | RO   | -    | Reserved                                                                                                                                      |

| 27    | RO   |      | Rx buffer overflow or illegal token encoding received.                                                                                        |

| 26    | RO   | 0    | This end of the xlink has issued credit to allow the remote end to transmit                                                                   |

| 25    | RO   | 0    | This end of the xlink has credit to allow it to transmit.                                                                                     |

| 24    | wo   |      | Clear this end of the xlink's credit and issue a HELLO token.                                                                                 |

| 23    | wo   |      | Reset the receiver. The next symbol that is detected will be the first symbol in a token.                                                     |

| 22    | RO   | -    | Reserved                                                                                                                                      |

| 21:11 | RW   | 0    | Specify min. number of idle system clocks between two contin-<br>uous symbols witin a transmit token -1.                                      |

| 10:0  | RW   | 0    | Specify min. number of idle system clocks between two contin-<br>uous transmit tokens -1.                                                     |

-XMOS"

0x80 .. 0x88: Link configuration and initialization

## D.18 Static link configuration: 0xA0 .. 0xA7

These registers are used for static (ie, non-routed) links. When a link is made static, all traffic is forwarded to the designated channel end and no routing is attempted. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits | Perm | Init | Description                                                                                     |

|------|------|------|-------------------------------------------------------------------------------------------------|

| 31   | RW   | 0    | Enable static forwarding.                                                                       |

| 30:9 | RO   | -    | Reserved                                                                                        |

| 8    | RW   | 0    | The destination processor on this node that packets received in static mode are forwarded to.   |

| 7:5  | RO   | -    | Reserved                                                                                        |

| 4:0  | RW   | 0    | The destination channel end on this node that packets received in static mode are forwarded to. |

**0xA0 .. 0xA7:** Static link configuration

| Bits | Perm | Init | Description                                    |

|------|------|------|------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                       |

| 7    | RW   | 0    | Set to 1 to enable XEVACKMODE mode.            |

| 6    | RW   | 0    | Set to 1 to enable SOFISTOKEN mode.            |

| 5    | RW   | 0    | Set to 1 to enable UIFM power signalling mode. |

| 4    | RW   | 0    | Set to 1 to enable IF timing mode.             |

| 3    | RO   | -    | Reserved                                       |

| 2    | RW   | 0    | Set to 1 to enable UIFM linestate decoder.     |

| 1    | RW   | 0    | Set to 1 to enable UIFM CHECKTOKENS mode.      |

| 0    | RW   | 0    | Set to 1 to enable UIFM DOTOKENS mode.         |

0x04: UIFM IFM control

#### F.3 UIFM Device Address: 0x08

The device address whose packets should be received. 0 until enumeration, it should be set to the assigned value after enumeration.

**0x08:** UIFM Device Address

|   | Bits | Perm | Init | Description                                                                                        |

|---|------|------|------|----------------------------------------------------------------------------------------------------|

| : | 31:7 | RO   | -    | Reserved                                                                                           |

| 2 | 6:0  | RW   | 0    | The enumerated USB device address must be stored here. Only packets to this address are passed on. |

## F.4 UIFM functional control: 0x0C

**0x0C:** UIFM functional control

| Bits | Perm | Init | Description                                       |

|------|------|------|---------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                          |

| 4:2  | RW   | 1    | Set to 0 to disable UIFM to UTMI+ OPMODE mode.    |

| 1    | RW   | 1    | Set to 1 to switch UIFM to UTMI+ TERMSELECT mode. |

| 0    | RW   | 1    | Set to 1 to switch UIFM to UTMI+ XCVRSELECT mode. |

## F.5 UIFM on-the-go control: 0x10

This register is used to negotiate an on-the-go connection.

-XMOS<sup>®</sup>

| 0x2C:    |  |

|----------|--|

| UIFM PID |  |

| Bits | Perm | Init | Description                     |

|------|------|------|---------------------------------|

| 31:4 | RO   | -    | Reserved                        |

| 3:0  | RO   | 0    | Value of the last received PID. |

#### F.13 UIFM Endpoint: 0x30

The last endpoint seen

**0x30** UIFM Endpoint

|         | Bits | Perm | Init | Description                           |

|---------|------|------|------|---------------------------------------|

| 0:      | 31:5 | RO   | -    | Reserved                              |

| и.<br>И | 4    | RO   | 0    | 1 if endpoint contains a valid value. |

| t       | 3:0  | RO   | 0    | A copy of the last received endpoint. |

## F.14 UIFM Endpoint match: 0x34

This register can be used to mark UIFM endpoints as special.

**0x34:** UIFM Endpoint match

| Bits  | Perm | Init | Description                                                                                                                          |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                             |

| 15:0  | RW   | 0    | This register contains a bit for each endpoint. If its bit is set, the endpoint will be supplied on the RX port when ORed with 0x10. |

## F.15 OTG Flags mask: 0x38

**0x38** OTG Flags mask

| <b>38:</b><br>gs | Bits | Perm | Init | Description |

|------------------|------|------|------|-------------|

| sk               | 31:0 | RW   | 0    | Data        |

## F.16 UIFM power signalling: 0x3C

|                                          | Bits | Perm | Init | Description |

|------------------------------------------|------|------|------|-------------|

| <b>0x3C:</b><br>UIFM power<br>signalling | 31:9 | RO   | -    | Reserved    |

|                                          | 8    | RW   | 0    | Valid       |

|                                          | 7:0  | RW   | 0    | Data        |

# H Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XU216-512-FB236. Each of the following sections contains items to check for each design.

#### H.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 12).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 12).

- The VDD (core) supply is capable of supplying 700 mA (Section 12 and Figure 22).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 12

#### H.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 12).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 12).

#### H.3 Power on reset

The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place.

#### H.4 Clock

- The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

- Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 7. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.