Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | -                                                            |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | -                                                            |

| Number of I/O                  | -                                                            |

| Number of Gates                | -                                                            |

| Voltage - Supply               | -                                                            |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -                                                            |

| Package / Case                 | 600-BGA                                                      |

| Supplier Device Package        | 600-BGA (45x45)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k250ebc600-1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## General Description

Altera FLEX 10KE devices are an enhancement of the FLEX 10K device family. Based on reconfigurable CMOS SRAM elements, the Flexible Logic Element MatriX (FLEX) architecture incorporates all features necessary to implement common gate array megafunctions. With up to 250,000 gates, the FLEX 10KE family provides the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device.

FLEX 10KE devices are configurable, and they are 100% tested prior to shipment. As a result, the designer is not required to generate test vectors for fault coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different gate array designs; FLEX 10KE devices can be configured on the board for the specific functionality required.

Table 5 shows FLEX 10KE performance for some common designs. All performance values shown were obtained with Synopsys DesignWare or LPM functions. Special design techniques are not required to implement the applications; the designer simply infers or instantiates a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

| <b>A</b> pplication                                      | Resources Used |      | Performance    |                |                |     |

|----------------------------------------------------------|----------------|------|----------------|----------------|----------------|-----|

|                                                          | LEs            | EAβs | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade |     |

| 16-bit loadable counter                                  | 16             | 0    | 196            | 182            | 143            | MHz |

| 16-bit accumulator                                       | 16             | 0    | 196            | 182            | 143            | MHz |

| 16-to-1 multiplexer, Note (1)                            | 10             | 0    | 15             | 17             | 18             | ns  |

| 16-bit multiplier with 3 stage pipeline, <i>Note (2)</i> | 10             | 0    | 91             | 86             | 70             | MHz |

| 256 x 16 RAM read cycle speed,<br>Note (2)               | 0              | 1    | 181            | 142            | 125            | MHz |

| 256×16 RAM write cycle speed,<br>Note (2)                | 0              | 1    | 135            | 117            | 106            | MHz |

#### Notes:

- (1) This application uses combinatorial inputs and outputs.

- (2) This application uses registered inputs and outputs.

FLEX 10KE devices are configured at system power-up with data stored in an Altera serial Configuration EPROM device or provided by a system controller. Altera offers the EPC1, EPC2, and EPC1441 Configuration EPROMs, which configure FLEX 10KE devices via a serial data stream. Configuration data can also be downloaded from system RAM or from the Altera BitBlaster™ serial download cable, ByteBlaster™ parallel port download cable, or ByteBlasterMV™ parallel port download cable. After a FLEX 10KE device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Because reconfiguration requires less than 330 ms, real-time changes can be made during system operation.

FLEX 10KE devices contain an optimized interface that permits microprocessors to configure FLEX 10KE devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat a FLEX 10KE device as memory and configure the device by writing to a virtual memory location, making it very easy for the designer to reconfigure the device.

For more information, go to the following documents:

- Configuration EPROMs for FLEX Devices Data Sheet

- 🗱 BitBlaster Serial Download Cable Data Sheet

- 🗱 ByteBlaster Parallel Port Download Cable Data Sheet

- 🗱 ByteBlasterMV Parallel Port Download Cable Data Sheet

FLEX 10KE devices are supported by the Altera MAX+PLUS II development system, a single, integrated package that offers schematic, text—including AHDL—and waveform design entry; compilation and logic synthesis; full simulation and worst-case timing analysis; and device configuration. The MAX+PLUS II software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools.

The MAX+PLUS II software works easily with common gate array EDA tools for synthesis and simulation. For example, the MAX+PLUS II software can generate Verilog HDL files for simulation with tools such as Cadence Verilog-XL. Additionally, the MAX+PLUS II software contains EDA libraries that use device-specific features such as carry chains, which are used for fast counter and arithmetic functions. For instance, the Synopsys Design Compiler library supplied with the MAX+PLUS II development system includes DesignWare functions that are optimized for the FLEX 10KE architecture.

The MAX+PLUS II software runs on 486- and Pentium-based PCs, Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations.

Go to the MAX+PLUS II Programmable Logic Development System & Software Data Sheet in the **1998 Data Book** for more information.

## Functional Description

Each FLEX 10KE device contains an enhanced embedded array to implement memory and specialized logic functions, and a logic array to implement general logic.

The embedded array consists of a series of EABs. When implementing memory functions, each EAB provides 4,096 bits, which can be used to create RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. When implementing logic, each EAB can contribute 100 to 600 gates towards complex logic functions, such as multipliers, microcontrollers, state machines, and DSP functions. EABs can be used independently, or multiple EABs can be combined to implement larger functions.

The logic array consists of logic array blocks (LABs). Each LAB contains eight LEs and a local interconnect. An LE consists of a 4-input look-up table (LUT), a programmable flipflop, and dedicated signal paths for carry and cascade functions. The eight LEs can be used to create medium-sized blocks of logic—such as 8-bit counters, address decoders, or state machines—or combined across LABs to create larger logic blocks. Each LAB represents about 96 usable gates of logic.

Signal interconnections within FLEX 10KE devices (as well as to and from device pins) are provided by the FastTrack Interconnect routing structure, a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect routing structure. Each IOE contains a bidirectional I/O buffer and a flipflop that can be used as either an output or input register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. As inputs, they provide setup times as low as 2.9 ns and

Figure 3. FLEX 10KE Device in Single-Port EAB

Each LAB provides four control signals with programmable inversion that can be used in all eight LEs. Two of these signals can be used as clocks; the other two can be used for clear/preset control. The LAB clocks can be driven by the dedicated clock input pins, global signals, I/O signals, or internal signals via the LAB local interconnect. The LAB preset and clear control signals can be driven by the global signals, I/O signals, or internal signals via the LAB local interconnect. The global control signals are typically used for global clock, clear, or preset signals because they provide asynchronous control with very low skew across the device. If logic is required on a control signal, it can be generated in one or more LEs in any LAB and driven into the local interconnect of the target LAB. In addition, the global control signals can be generated from LE outputs.

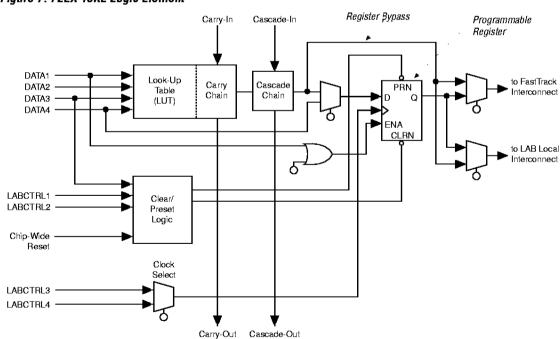

### Logic Element

The LE, the smallest unit of logic in the FLEX 10KE architecture, has a compact size that provides efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can quickly compute any function of four variables. In addition, each LE contains a programmable flipflop with a synchronous clock enable, a carry chain, and a cascade chain. Each LE drives both the local and the FastTrack Interconnect routing structure (see Figure 7).

Figure 7. FLEX 10KE Logic Element

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the output of the LE.

The LE has two outputs that drive the interconnect; one drives the local interconnect and the other drives either the row or column FastTrack Interconnect routing structure. The two outputs can be controlled independently; for example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

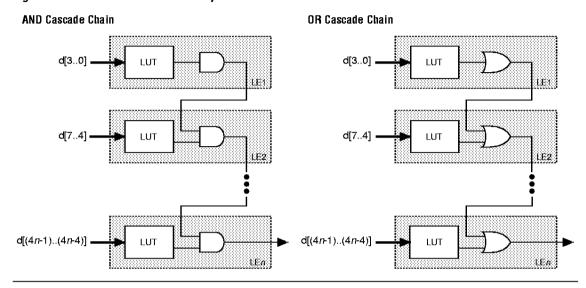

The FLEX 10KE architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. The carry chain supports high-speed counters and adders; the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in a LAB and all LABs in the same row. Intensive use of carry and cascade chains can reduce routing flexibility. Therefore, the use of these chains should be limited to speed-critical portions of a design.

### Carry Chain

The carry chain provides a very fast (as low as 0.2 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 10KE architecture to implement high-speed counters, adders, and comparators of arbitrary width efficiently. Carry chain logic can be created automatically by the MAX+PLUS II Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains.

Carry chains longer than eight LEs are automatically implemented by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the first LE of the third LAB in the row. The carry chain does not cross the EAB at the middle of the row. For instance, in the EPF10K50E device, the carry chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB.

Figure 9. FLEX 10KE Cascade Chain Operation

### LE Operating Modes

The FLEX 10KE LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- ₩ Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The MAX+PLUS II software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions to use an LE operating mode for optimal performance.

### Normal Mode

The normal mode is suitable for general logic applications and wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a 4-input LUT. The MAX+PLUS II Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. Either the register or the LUT can be used to drive both the local interconnect and the FastTrack Interconnect routing structure at the same time.

The LUT and the register in the LE can be used independently; this feature is known as register packing. To support register packing, the LE has two outputs; one drives the local interconnect, and the other drives the FastTrack Interconnect routing structure. The DATA4 signal can drive the register directly, allowing the LUT to compute a function that is independent of the registered signal; a 3-input function can be computed in the LUT, and a fourth independent signal can be registered. Alternatively, a 4-input function can be generated, and one of the inputs to this function can be used to drive the register. The register in a packed LE can still use the clock enable, clear, and preset signals in the LE. In a packed LE, the register can drive the FastTrack Interconnect routing structure while the LUT drives the local interconnect, or vice versa.

### Arithmetic Mode

The arithmetic mode offers two 3-input LUTs that are ideal for implementing adders, accumulators, and comparators. One LUT computes a 3-input function; the other generates a carry output. As shown in Figure 10 on page 20, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, in an adder, this output is the sum of three signals: a. b. and carry-in. The second LUT uses the same three signals to

# ClockLock & ClockBoost Features

To support high-speed designs, FLEX 10KE devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) that is used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by resource sharing within the device. ClockBoost allows the designer to distribute a low-speed clock and multiply that clock

If more than six clock enable or eight output enable signals are required, each IOE on the device can be controlled by clock enable and output enable signals driven by specific LEs. In addition to the two clock signals available on the peripheral control bus, each IOE can use one of two dedicated clock pins. Each peripheral control signal can be driven by any of the dedicated input pins or the first LE of each LAB in a particular row. In addition, a LE in a different row can drive a column interconnect, which causes a row interconnect to drive the peripheral control signal. The chipwide reset signal resets all IOE registers, overriding any other control signals.

When a dedicated clock pin drives IOE registers, it can be inverted for all IOEs in the device. All IOEs must use the same sense of the clock. For example, if any IOE uses the inverted clock, all IOEs must use the inverted clock and no IOE can use the non-inverted clock. However, LEs can still use the true or complement of the clock on a LAB-by-LAB basis.

The incoming signal may be inverted at the dedicated clock pin and will

Preliminary Information

FLEX 10KE Embedded Programmable Logic Family Data Sheet

### Slew-Rate Control

The output buffer in each IOE has an adjustable output slew rate that can be configured for low-noise or high-speed performance. A slower slew rate reduces system noise and adds a maximum delay of approximately

### Slew-Rate Control

The output buffer in each IOE has an adjustable output slew rate that can be configured for low-noise or high-speed performance. A slower slew rate reduces system noise and adds a maximum delay of approximately 4.3 ns. The fast slew rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew rate pin-by-pin or assign a default slew rate to all pins on a device-wide basis. The slow slew rate setting affects both the falling and rising edges of the output.

### Open-Drain Output Option

FLEX 10KE devices provide an optional open-drain output (electrically equivalent to open-collector output) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write enable signals) that can be asserted by any of several devices. It can also provide an additional wired-OR plane.

### MultiVolt I/O Interface

The FLEX 10KE device architecture supports the MultiVolt I/O interface feature, which allows FLEX 10KE devices in all packages to interface with systems of differing supply voltages. These devices have one set of  $V_{CC}$  pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The VCCINT pins must always be connected to a 2.5-V power supply. With a 2.5-V Vccnr level input voltages are compatible with 2.5-V 3.3-V and

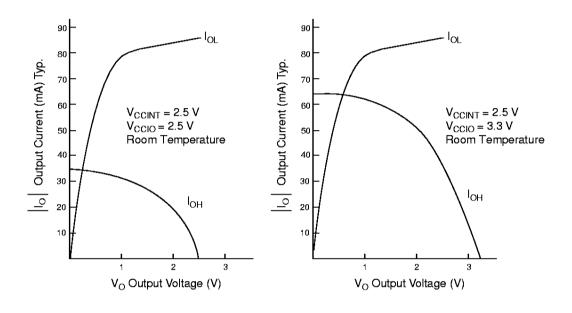

Figure 21 shows the typical output drive characteristics of FLEX 10KE devices with 3.3-V and 2.5-V  $V_{\rm CCIO}$ . The output driver is compatible with the 3.3-V *PCI Local Bus Specification, Revision 2.1* (with 3.3-V  $V_{\rm CCIO}$ ).

Figure 21. Output Drive Characteristics of FLEX 10KE Devices

### **Timing Model**

Table 15 shows the external timing parameters of FLEX 10KE devices. Detailed timing information for these devices will be released as it is available.

| Symbol           | Parameter                                                                           | Device        | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Uni  |

|------------------|-------------------------------------------------------------------------------------|---------------|----------------|------|----------------|------|----------------|------|------|

|                  |                                                                                     |               | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>DRR</sub> | Register-to-<br>register delay<br>via 4 LEs, 3 row<br>interconnects,<br>and 4 local | EPF10K30E     |                | 8.5  |                | 10.0 |                | 13.5 | ns   |

|                  |                                                                                     | EPF10K50E     |                | 8.5  |                | 10.0 |                | 13.5 | ns   |

|                  |                                                                                     | EPF10K100B    |                | 11.0 |                | 12.0 |                | 14.5 | ns   |

|                  |                                                                                     | EPF10K100E    |                | 10.0 |                | 12.0 |                | 16.0 | ns   |

|                  |                                                                                     | interconnects | EPF10K130E     |      | 10.0           |      | 12.0           |      | 16.0 |

|                  |                                                                                     | EPF10K200E    |                | 10.0 |                | 12.0 |                | 16.0 | ns   |

|                  |                                                                                     | EPF10K250E    |                | 11.0 |                | 13.5 |                | 17.0 | ns   |

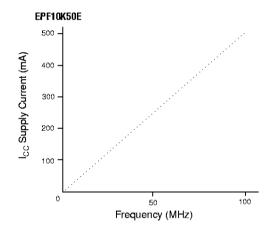

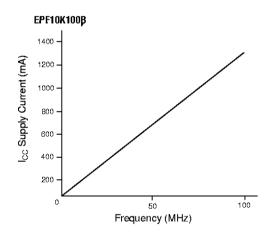

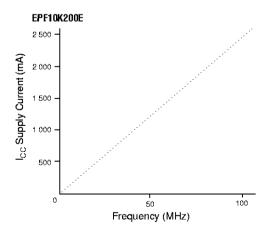

# Power Consumption

The supply power (P) for FLEX 10KE devices can be calculated with the following equation:

$$P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTIVE}) \times V_{CC} + P_{IO}$$

The  $I_{\text{CCACTIVE}}$  value depends on the switching frequency and the application logic. This value is calculated based on the amount of current that each LE typically consumes. The  $P_{\text{IO}}$  value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note 74 (Evaluating Fower for Altera Devices)* in the **1998 Data Book**.

1

Compared to the rest of the device, the embedded array consumes a negligible amount of power. Therefore, the embedded array can be ignored when calculating supply current.

The I<sub>CCACTIVE</sub> value can be calculated with the following equation:

$$I_{CCACTIVE} = K \times f_{MAX} \times N \times tog_{LC} \times \frac{\mu A}{MHz \times LE}$$

Where:

f<sub>MAX</sub> = Maximum operating frequency in MHz

N = Total number of LEs used in the device

$tog_{LC}$  = Average percent of LEs toggling at each clock

(typically 12.5%)

K = Constant

Table 16 provides the constant (K) values for EPF10K50E, EPF10K100B, and EPF10K200E devices. K factors for other FLEX 10KE devices will be released as they become available.

Tahle 16 FI FX 10KF K Constant Values

To better reflect actual designs, the power model (and the constant K in the power calculation equations) for continuous interconnect FLEX devices assume that LEs drive FastTrack Interconnect channels. In contrast, the power model of segmented FPGAs assume that all LEs drive only one short interconnect segment. This assumption may lead to inaccurate results when compared to measured power consumption for actual designs in segmented FPGAs.

Figure 22 shows the relationship between the current and operating frequency of EPF10K50E, EPF10K100B, and EPF10K200E devices. For other FLEX 10KE devices, contact Altera Applications at (800) 800-EPLD.

Figure 22. FLEX 10KE  $I_{CCACTIVE}$  vs. Operating Frequency

# Configuration & Operation

The FLEX 10KE architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

### **Operating Modes**

The FLEX 10KE architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. Before configuration, as  $V_{CC}$  rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The FLEX 10KE POR time does not exceed 50  $\mu s$ ; however, when configuring with a Configuration EPROM, the Configuration EPROM imposes a 100  $\mu s$  delay that allows system power to stabilize before configuration.

During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

SRAM configuration elements allow FLEX 10KE devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data.

Preliminary Information

FLEX 10KE Embedded Programmable Logic Family Data Sheet

| Pin Name | 144-Pin<br>TQFP<br>EPF10K30E<br>EPF10K50E  |                                                                  | 240-Pin<br>PQFP<br>EPF10K50E<br>EPF10K100E<br>EPF10K100B | 240-Pin<br>PQFP<br>EPF10K130E | 356-Pin<br>BGA<br>EPF10K100E | 599-Pin<br>PGA<br>EPF10K200E<br>EPF10K250E                                                        | 600-Pin<br>BGA<br>EPF10K200E<br>EPF10K250E                                               |

|----------|--------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| GNDIO    | 15, 40, 50,<br>66, 85,<br>104, 129,<br>139 | 20, 32, 48,<br>59, 72, 91,<br>124, 130,<br>152, 171,<br>188, 201 | _                                                        | _                             | _                            | D24, E9,<br>E15, E21,<br>E27, E33,<br>E39, G7,<br>G41, J5,<br>J43, R5,<br>R43, AA5,<br>AA43, AD4, | C8, E12,<br>C15, A20,<br>C23, A27,<br>AM26,<br>AR23,<br>AM19,<br>AN15, AL12,<br>AN8. C2. |

|   | Table 19. FL | EX 10KE Dev                               | vice Pin-Outs (                                                       | (Part 3 of 4) | Note (1)                      |                              |                                            |                                            |                |

|---|--------------|-------------------------------------------|-----------------------------------------------------------------------|---------------|-------------------------------|------------------------------|--------------------------------------------|--------------------------------------------|----------------|

|   | Pin Name     | 144-Pin<br>TQFP<br>EPF10K30E<br>EPF10K50E | 208-Pin<br>PQFP<br>EPF10K30E<br>EPF10K50E<br>EPF10K100E<br>EPF10K100B |               | 240-Pin<br>PQFP<br>EPF10K130E | 356-Pin<br>BGA<br>EPF10K100E | 599-Pin<br>PGA<br>EPF10K200E<br>EPF10K250E | 600-Pin<br>BGA<br>EPF10K200E<br>EPF10K250E |                |

|   | 1700T@       | 5,24 45                                   | E 00 04                                                               | 16 97 57      | 16 97 57                      | A7 A00                       | DCDE                                       | AD40                                       |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

| _ |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   | -            |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   | <u>.</u>     |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               | Br. T.                       |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            | <del>) -</del> |

|   |              |                                           | ,                                                                     |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              | ı                                          |                                            |                |

|   |              | L                                         |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|   |              |                                           |                                                                       |               |                               |                              |                                            |                                            |                |

|           | Table 19. FL | LEX 10KE Dev                              | vice Pin-Outs                                           | (Part 4 of 4)                                            | Note (1) |                              |                                            |                                            |   |   |

|-----------|--------------|-------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|----------|------------------------------|--------------------------------------------|--------------------------------------------|---|---|

|           | Pin Name     | 144-Pin<br>TQFP<br>EPF10K30E<br>EPF10K50E | 208-Pin<br>PQFP<br>EPF10K30E<br>EPF10K50E<br>EPF10K100E | 240-Pin<br>PQFP<br>EPF10K50E<br>EPF10K100E<br>EPF10K100B |          | 356-Pin<br>BGA<br>EPF10K100E | 599-Pin<br>PGA<br>EPF10K200E<br>EPF10K250E | 600-Pin<br>BGA<br>EPF10K200E<br>EPF10K250E |   |   |

| <u> :</u> |              |                                           | [ <u>FDC</u> 11112111112                                | · -                                                      |          |                              | -                                          |                                            |   | _ |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           | -            |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u> </u>  |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| •         | _            |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u>_</u>  |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u> </u>  |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| `-        |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u> </u>  |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           | <u> </u>     |                                           |                                                         |                                                          |          | Bo a w                       |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          | 12.72                        |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u></u>   |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u></u>   |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   | _ |

| ł         |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| ,         |              |                                           |                                                         |                                                          |          |                              |                                            |                                            | j |   |

|           |              |                                           | ,                                                       |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| ,         |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| <u>.</u>  |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              | <u>.</u>                                  |                                                         |                                                          |          | <b>.</b>                     |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

| •         |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

|           |              |                                           |                                                         |                                                          |          |                              |                                            |                                            |   |   |

Table 20 shows the dedicated pin-outs for FLEX 10KE devices in 256-pin FineLine BGA and 672-pin FineLine BGA packages.

| Pin Name      | 256-Pin<br>FineLine BGA<br>EPF10K30E | 256-Pin<br>FineLine BGA<br>EPF10K50E<br>EPF10K100E<br>EPF10K100B | 672-Pin<br>FineLine BGA<br>EPF10K130E | 672-Pin<br>FineLine BGA<br>EPF10K200E<br>EPF10K250E |

|---------------|--------------------------------------|------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------|

| MSELO (2)     | P1                                   | P1                                                               | W6                                    | W6                                                  |

| MSEL1 (2)     | R1                                   | R1                                                               | Y6                                    | Y6                                                  |

| nSTATUS (2)   | T16                                  | T16                                                              | AA21                                  | AA21                                                |

| nCONFIG (2)   | N4                                   | N4                                                               | V9                                    | V9                                                  |

| DCLK (2)      | B2                                   | B2                                                               | G7                                    | G7                                                  |

| CONF_DONE (2) | C15                                  | C15                                                              | H20                                   | H20                                                 |

| Pin Name          | 484-Pin<br>FineLine BGA<br>EPF10K30E | 484-Pin<br>FineLine BGA<br>EPF10K50E | 484-Pin<br>FineLine BGA<br>EPF10K100E | 484-Pin<br>FineLine BGA<br>EPF10K130E |  |

|-------------------|--------------------------------------|--------------------------------------|---------------------------------------|---------------------------------------|--|

| n.Coppect/N.C.) _ | Δο Δο ΔΛ Δε Δο                       | Δο Δο ΔΛ Δε Δο                       | A2 A2 A1 A5 R2                        | _                                     |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

| <u> </u>          |                                      |                                      |                                       |                                       |  |

| -1.05.1-2         | Market E. C. Land Lord F. C.         | LJ 1—1-8.                            |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   | ļ                                    |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

|                   |                                      |                                      |                                       |                                       |  |

| Table 21. FLEX 10KE Fine | Line BGA Device Pir                  | Note (1)                              |                                       |                                       |  |

|--------------------------|--------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|--|

| Pin Name                 | 484-Pin<br>FineLine BGA<br>EPF10K30E | 484-Pin<br>FineLine BGA<br>EPF1 0K50E | 484-Pin<br>FineLine BGA<br>EPF10K100E | 484-Pin<br>FineLine BGA<br>EPF10K130E |  |

Table 23 shows the FLEX 10KE device/package combinations that support SameFrame pin-outs. All FineLine BGA packages support SameFrame pin-outs providing the flexibility to migrate not only from device to device within the same package, but also from one package to another. The I/O count will vary, and MAX+PLUS II software versions 9.1 and higher provide features to help use only the common pins.

|                | Table 23. FLEX 10KE S | SameFrame Pin-Out Support | I |   |

|----------------|-----------------------|---------------------------|---|---|

|                |                       |                           |   |   |

|                |                       | <u> </u>                  |   |   |

|                |                       | <u> </u>                  |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

| -              | _                     |                           |   |   |

|                |                       |                           |   |   |

| <u> </u>       |                       |                           |   |   |

| •              |                       |                           |   |   |

| *              |                       |                           |   |   |

| _              |                       |                           |   |   |

| -              |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

| -<br> -        |                       |                           |   |   |

| •              |                       |                           |   |   |

|                |                       |                           |   |   |

| ·: . ` —       |                       |                           |   |   |

|                |                       |                           |   |   |

| <del>-</del>   |                       |                           |   |   |

| •              |                       |                           | - |   |

| <del></del>    |                       |                           |   |   |

| -              |                       |                           |   |   |

| _              |                       |                           |   |   |

| : <del>-</del> |                       |                           |   |   |

|                | -                     |                           |   |   |

|                | *                     |                           |   |   |

|                |                       |                           |   |   |

| • -            | *                     |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   | _ |

| <u></u>        |                       |                           |   |   |

| * -            |                       |                           |   |   |

|                |                       |                           |   |   |

| 1=             |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

| <del></del>    |                       |                           |   |   |

|                |                       |                           |   |   |

| -              |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

| 3.             |                       |                           |   |   |

|                |                       |                           |   |   |

| 5              |                       |                           |   |   |

| ÷ %            |                       |                           |   |   |

| :z=            |                       |                           |   |   |

| •              |                       |                           |   |   |

| -              |                       |                           |   |   |

| -              |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |

|                |                       |                           |   |   |