Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

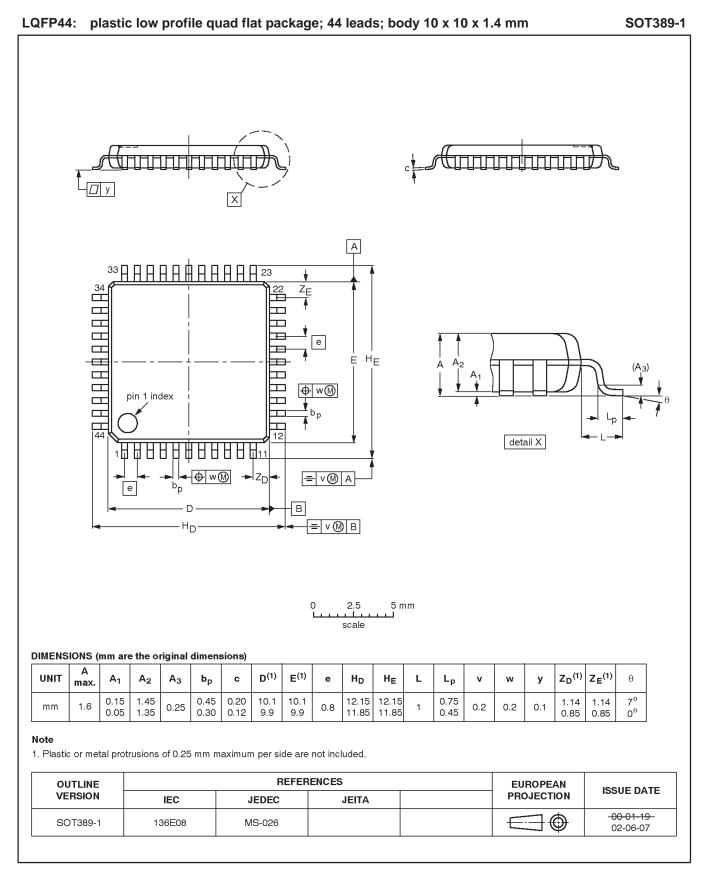

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89c664hbbd-00-557 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

P89C660/P89C662/P89C664/

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

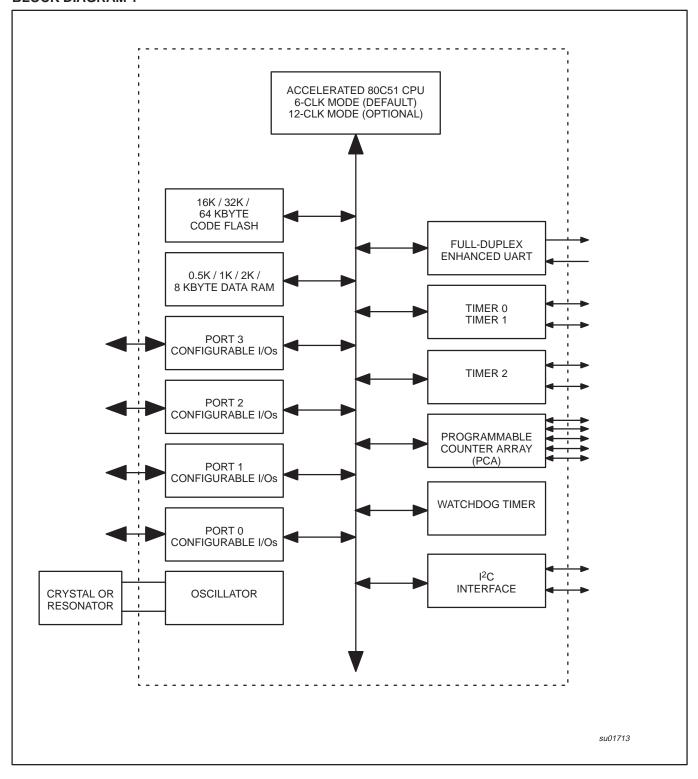

### **BLOCK DIAGRAM 1**

### P89C660/P89C662/P89C664/ P89C668

### Table 1. Special Function Registers

| SYMBOL             | DESCRIPTION                                 | DIRECT<br>ADDRESS | BIT A<br>MSB | DDRESS   | , SYMBO     | L, OR AL    | TERNATI | /E PORT     | FUNCTIO | N<br>LSB | RESET<br>VALUE |

|--------------------|---------------------------------------------|-------------------|--------------|----------|-------------|-------------|---------|-------------|---------|----------|----------------|

| ACC*               | Accumulator                                 | E0H               | E7           | E6       | E5          | E4          | E3      | E2          | E1      | E0       | 00H            |

| AUXR#              | Auxiliary                                   | 8EH               | -            | -        | -           | -           | -       | -           | EXTRAM  | AO       | xxxxxx10B      |

| AUXR1#             | Auxiliary 1                                 | A2H               | -            | -        | ENBOOT      | -           | GF2     | 0           | -       | DPS      | xxxxx0x0B      |

| B*                 | B register                                  | F0H               | F7           | F6       | F5          | F4          | F3      | F2          | F1      | F0       | 00H            |

| CCAP0H#            | Module 0 Capture High                       | FAH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP1H#            | Module 1 Capture High                       | FBH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP2H#            | Module 2 Capture High                       | FCH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP3H#            | Module 3 Capture High                       | FDH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP4H#            | Module 4 Capture High                       | FEH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP0L#            | Module 0 Capture Low                        | EAH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP1L#            | Module 1 Capture Low                        | EBH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP2L#            | Module 2 Capture Low                        | ECH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP3L#            | Module 3 Capture Low                        | EDH               |              |          |             |             |         |             |         |          | xxxxxxxB       |

| CCAP4L#            | Module 4 Capture Low                        | EEH               |              | -        | -           | _           |         | _           | -       |          | xxxxxxxB       |

| CCAPM0#            | Module 0 Mode                               | C2H               | _            | ECOM     | CAPP        | CAPN        | MAT     | TOG         | PWM     | ECCF     | x0000000B      |

| CCAPM1#            | Module 1 Mode                               | СЗН               | -            | ECOM     | CAPP        | CAPN        | MAT     | TOG         | PWM     | ECCF     | x0000000B      |

| CCAPM2#            | Module 2 Mode                               | C4H               | -            | ECOM     | CAPP        | CAPN        | MAT     | TOG         | PWM     | ECCF     | x0000000B      |

| CCAPM3#            | Module 3 Mode                               | C5H               | -            | ECOM     | CAPP        | CAPN        | MAT     | TOG         | PWM     | ECCF     | x0000000B      |

| CCAPM4#            | Module 4 Mode                               | C6H               | -            | ECOM     | CAPP        | CAPN        | MAT     | TOG         | PWM     | ECCF     | x0000000B      |

|                    |                                             |                   | C7           | C6       | C5          | C4          | C3      | C2          | C1      | C0       | 1              |

| CCON*#             | PCA Counter Control                         | СОН               | CF           | CR       | _           | CCF4        | CCF3    | CCF2        | CCF1    | CCF0     | 00x00000B      |

| CH#                | PCA Counter High                            | F9H               |              | 1        | 1           |             |         |             |         |          | 00H            |

| CL#                | PCA Counter Low                             | E9H               |              |          |             | -           |         |             | -       |          | 00H            |

| CMOD#              | PCA Counter Mode                            | C1H               | CIDL         | WDTE     | -           | -           | -       | CPS1        | CPS0    | ECF      | 00xxx000B      |

| DPTR:<br>DPH       | Data Pointer (2 bytes)<br>Data Pointer High | 83H               |              |          |             |             |         |             |         |          | 00H            |

| DPL                | Data Pointer Low                            | 82H               | AF           | AE       | AD          | AC          | AB      | AA          | A9      | A8       | 00H            |

| IEN0*              | Interrupt Enable 0                          | A8H               | EA           | EC       | ES1         | ES0         | ET1     | EX1         | ET0     | EX0      | 00H            |

| IEN1*              | Interrupt Enable 1                          | E8                | -            | _        | _           |             | _       | _           | _       | ET2      | xxxxxx0B       |

|                    |                                             | LU                | BF           | BE       | BD          | BC          | BB      | BA          | B9      | B8       | **********     |

| IP*                | Interrupt Priority                          | B8H               | PT2          | PPC      | PS1         | PS0         | PT1     | PX1         | PT0     | PX0      | x0000000B      |

| "<br>IPH#          | Interrupt Priority High                     | B7H               | PT2H         | PPCH     | PS1H        | PS0H        | PT1H    | PX1H        | PTOH    | PX0H     | x0000000B      |

| 11711#             | interrupt Fhonty Flight                     | ВЛП               |              | <u>I</u> | <u>I</u>    |             |         |             |         |          | X000000B       |

| Dot                | <b>D</b> / 0                                | 0.011             | 87           | 86       | 85          | 84          | 83      | 82          | 81      | 80       |                |

| P0*                | Port 0                                      | 80H               | AD7          | AD6      | AD5         | AD4         | AD3     | AD2         | AD1     | AD0      | FFH            |

| <b>D</b> / ±       | <b>-</b>                                    |                   | 97           | 96       | 95          | 94          | 93      | 92          | 91      | 90       | l              |

| P1*                | Port 1                                      | 90H               | SDA          | SCL      | CEX2        | CEX1        | CEX0    | ECI         | T2EX    | T2       | FFH            |

|                    |                                             |                   | A7           | A6       | A5          | A4          | A3      | A2          | A1      | A0       |                |

| P2*                | Port 2                                      | A0H               | AD15         | AD14     | AD13        | AD12        | AD11    | AD10        | AD9     | AD8      | FFH            |

|                    |                                             |                   | B7           | B6       | B5          | B4          | B3      | B2          | B1      | B0       |                |

| P3*                | Port 3                                      | вон               | RD           | WR       | T1/<br>CEX4 | T0/<br>CEX3 | INT1    | <u>INTO</u> | TxD     | RxD      | FFH            |

| PCON# <sup>1</sup> | Power Control                               | 87H               | SMOD1        | SMOD0    | _           | POF         | GF1     | GF0         | PD      | IDL      | 00xxx000B      |

\* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

Reserved bits.

1. Reset value depends on reset source.

#### Serial Clock Generator

This programmable clock pulse generator provides the SCL clock pulses when SIO1 is in the Master Transmitter or Master Receiver mode. It is switched off when SIO1 is in a Slave mode. The programmable output clock frequencies are:  $f_{OSC}/120$ ,  $f_{OSC}/9600$  (12-clock mode) or  $f_{OSC}/60$ ,  $f_{OSC}/4800$  (6-clock mode) and the Timer 1 overflow rate divided by eight. The output clock pulses have a 50% duty cycle unless the clock generator is synchronized with other SCL clock sources as described above.

#### **Timing and Control**

The timing and control logic generates the timing and control signals for serial byte handling. This logic block provides the shift pulses for S1DAT, enables the comparator, generates and detects start and stop conditions, receives and transmits acknowledge bits, controls the master and Slave modes, contains interrupt request logic, and monitors the  $I^2C$  bus status.

#### **Control Register, S1CON**

This 7-bit special function register is used by the microcontroller to control the following SIO1 functions: start and restart of a serial transfer, termination of a serial transfer, bit rate, address recognition, and acknowledgment.

#### Status Decoder and Status Register

The status decoder takes all of the internal status bits and compresses them into a 5-bit code. This code is unique for each I<sup>2</sup>C bus status. The 5-bit code may be used to generate vector addresses for fast processing of the various service routines. Each service routine processes a particular bus status. There are 26 possible bus states if all four modes of SIO1 are used. The 5-bit status code is latched into the five most significant bits of the status register when the serial interrupt flag is set (by hardware) and remains stable until the interrupt flag is cleared by software. The three least significant bits of the status register are always zero. If the status code is used as a vector to service routines, then the routines are displaced by eight address locations. Eight bytes of code is sufficient for most of the service routines.

#### The Four SIO1 Special Function Registers

The microcontroller interfaces to SIO1 via four special function registers. These four SFRs (S1ADR, S1DAT, S1CON, and S1STA) are described individually in the following sections.

#### The Address Register, S1ADR

The CPU can read from and write to this 8-bit, directly addressable SFR. S1ADR is not affected by the SIO1 hardware. The contents of this register are irrelevant when SIO1 is in a Master mode. In the Slave modes, the seven most significant bits must be loaded with the microcontroller's own slave address, and, if the least significant bit is set, the general call address (00H) is recognized; otherwise it is ignored.

|             | 7 | 6 | 5  | 4           | 3      | 2 | 1 | 0  |

|-------------|---|---|----|-------------|--------|---|---|----|

| S1ADR (DBH) | Х | х | Х  | Х           | Х      | Х | х | GC |

|             |   |   | ov | vn slave ad | ddress |   |   |    |

The most significant bit corresponds to the first bit received from the  $I^2C$  bus after a start condition. A logic 1 in S1ADR corresponds to a high level on the  $I^2C$  bus, and a logic 0 corresponds to a low level on the bus.

#### The Data Register, S1DAT

S1DAT contains a byte of serial data to be transmitted or a byte which has just been received. The CPU can read from and write to

this 8-bit, directly addressable SFR while it is not in the process of shifting a byte. This occurs when SIO1 is in a defined state and the serial interrupt flag is set. Data in S1DAT remains stable as long as SI is set. Data in S1DAT is always shifted from right to left: the first bit to be transmitted is the MSB (bit 7), and, after a byte has been received, the first bit of received data is located at the MSB of S1DAT. While data is being shifted out, data on the bus is simultaneously being shifted in; S1DAT always contains the last data byte present on the bus. Thus, in the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data in S1DAT.

|             | 7   | 6   | 5   | 4           | 3      | 2   | 1   | 0   |

|-------------|-----|-----|-----|-------------|--------|-----|-----|-----|

| S1DAT (DAH) | SD7 | SD6 | SD5 | SD4         | SD3    | SD2 | SD1 | SD0 |

|             | -   |     |     | shift direc | tion — |     |     |     |

#### SD7 - SD0:

Eight bits to be transmitted or just received. A logic 1 in S1DAT corresponds to a high level on the  $l^2C$  bus, and a logic 0 corresponds to a low level on the bus. Serial data shifts through S1DAT from right to left. Figure 6 shows how data in S1DAT is serially transferred to and from the SDA line.

S1DAT and the ACK flag form a 9-bit shift register which shifts in or shifts out an 8-bit byte, followed by an acknowledge bit. The ACK flag is controlled by the SIO1 hardware and cannot be accessed by the CPU. Serial data is shifted through the ACK flag into S1DAT on the rising edges of serial clock pulses on the SCL line. When a byte has been shifted into S1DAT, the serial data is available in S1DAT, and the acknowledge bit is returned by the control logic during the ninth clock pulse. Serial data is shifted out from S1DAT via a buffer (BSD7) on the falling edges of clock pulses on the SCL line.

When the CPU writes to S1DAT, BSD7 is loaded with the content of S1DAT.7, which is the first bit to be transmitted to the SDA line (see Figure 7). After nine serial clock pulses, the eight bits in S1DAT will have been transmitted to the SDA line, and the acknowledge bit will be present in ACK. Note that the eight transmitted bits are shifted back into S1DAT.

#### The Control Register, S1CON

The CPU can read from and write to this 8-bit, directly addressable SFR. Two bits are affected by the SIO1 hardware: the SI bit is set when a serial interrupt is requested, and the STO bit is cleared when a STOP condition is present on the  $I^{2}C$  bus. The STO bit is also cleared when ENS1 = "0".

|             | 7   | 6    | 5   | 4   | 3  | 2  | 1   | 0   |

|-------------|-----|------|-----|-----|----|----|-----|-----|

| S1CON (D8H) | CR2 | ENS1 | STA | STO | SI | AA | CR1 | CR0 |

**ENS1, the SIO1 Enable Bit:** ENS1 = "0": When ENS1 is "0", the SDA and SCL outputs are in a high impedance state. SDA and SCL input signals are ignored, SIO1 is in the "not addressed" slave state, and the STO bit in S1CON is forced to "0". No other bits are affected. P1.6 and P1.7 may be used as open drain I/O ports.

ENS1 = "1": When ENS1 is "1", SIO1 is enabled. The P1.6 and P1.7 port latches must be set to logic 1.

ENS1 should not be used to temporarily release SIO1 from the I2C bus since, when ENS1 is reset, the I2C bus status is lost. The AA flag should be used instead (see description of the AA flag in the following text).

### P89C660/P89C662/P89C664/ P89C668

### P89C660/P89C662/P89C664/ P89C668

If the STA and STO bits are both set, the a STOP condition is transmitted to the  $I^2C$  bus if SIO1 is in a Master mode (in a Slave mode, SIO1 generates an internal STOP condition which is not transmitted). SIO1 then transmits a START condition.

STO = "0": When the STO bit is reset, no STOP condition will be generated.

**The Serial Interrupt Flag, SI:** SI = "1": When the SI flag is set, then, if the EA and ES1 (interrupt enable register) bits are also set, a serial interrupt is requested. SI is set by hardware when one of 25 of the 26 possible SIO1 states is entered. The only state that does not cause SI to be set is state F8H, which indicates that no relevant state information is available.

While SI is set, the low period of the serial clock on the SCL line is stretched, and the serial transfer is suspended. A high level on the SCL line is unaffected by the serial interrupt flag. SI must be reset by software.

SI = "0": When the SI flag is reset, no serial interrupt is requested, and there is no stretching of the serial clock on the SCL line.

**The Assert Acknowledge Flag, AA:** AA = "1": If the AA flag is set, an acknowledge (low level to SDA) will be returned during the acknowledge clock pulse on the SCL line when:

- The "own slave address" has been received

- The general call address has been received while the general call bit (GC) in S1ADR is set

- A data byte has been received while SIO1 is in the Master Receiver mode

- A data byte has been received while SIO1 is in the addressed Slave Receiver mode

AA = "0": if the AA flag is reset, a not acknowledge (high level to SDA) will be returned during the acknowledge clock pulse on SCL when:

- A data has been received while SIO1 is in the Master Receiver mode

- A data byte has been received while SIO1 is in the addressed Slave Receiver mode

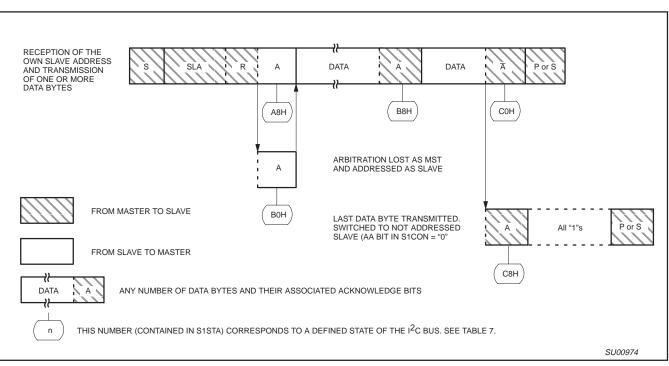

When SIO1 is in the addressed Slave Transmitter mode, state C8H will be entered after the last serial is transmitted (see Figure 11).

When SI is cleared, SIO1 leaves state C8H, enters the not addressed Slave Receiver mode, and the SDA line remains at a high level. In state C8H, the AA flag can be set again for future address recognition.

When SIO1 is in the not addressed Slave mode, its own slave address and the general call address are ignored. Consequently, no acknowledge is returned, and a serial interrupt is not requested. Thus, SIO1 can be temporarily released from the I<sup>2</sup>C bus while the bus status is monitored. While SIO1 is released from the bus, START and STOP conditions are detected, and serial data is shifted in. Address recognition can be resumed at any time by setting the AA flag. If the AA flag is set when the part's own Slave address or the general call address has been partly received, the address will be recognized at the end of the byte transmission.

The Clock Rate Bits CR0, CR1, and CR2: These three bits determine the serial clock frequency when SIO1 is in a Master mode. The various serial rates are shown in Table 3.

A 12.5 kHz bit rate may be used by devices that interface to the  $I^2C$  bus via standard I/O port lines which are software driven and slow. 100 kHz is usually the maximum bit rate and can be derived from a 16 MHz, 12 MHz, or a 6 MHz oscillator. A variable bit rate (0.5 kHz to 62.5 kHz) may also be used if Timer 1 is not required for any other purpose while SIO1 is in a Master mode.

The frequencies shown in Table 3 are unimportant when SIO1 is in a Slave mode. In the Slave modes, SIO1 will automatically synchronize with any clock frequency up to 100 kHz.

#### The Status Register, S1STA

S1STA is an 8-bit read-only special function register. The three least significant bits are always zero. The five most significant bits contain the status code. There are 26 possible status codes. When S1STA contains F8H, no relevant state information is available and no serial interrupt is requested. All other S1STA values correspond to defined SIO1 states. When each of these states is entered, a serial interrupt is requested (SI = "1"). A valid status code is present in S1STA one machine cycle after SI is set by hardware and is still present one machine cycle after SI has been reset by software.

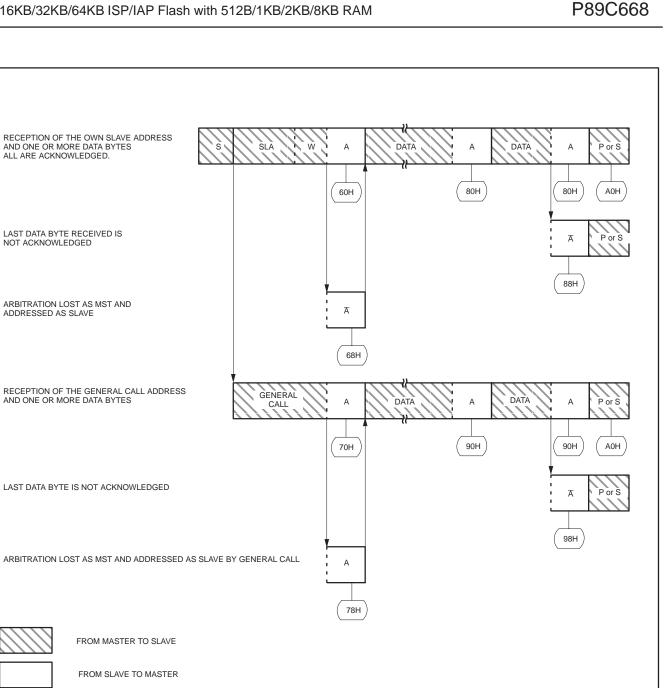

P89C660/P89C662/P89C664/

### 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

#### ANY NUMBER OF DATA BYTES AND THEIR ASSOCIATED ACKNOWLEDGE BITS

THIS NUMBER (CONTAINED IN S1STA) CORRESPONDS TO A DEFINED STATE OF THE I $^2$ C BUS. SEE TABLE 6.

SU00973

#### Figure 10. Format and States in the Slave Receiver mode

Data

n

А

P89C660/P89C662/P89C664/

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

Figure 11. Format and States of the Slave Transmitter mode

P89C660/P89C662/P89C664/

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

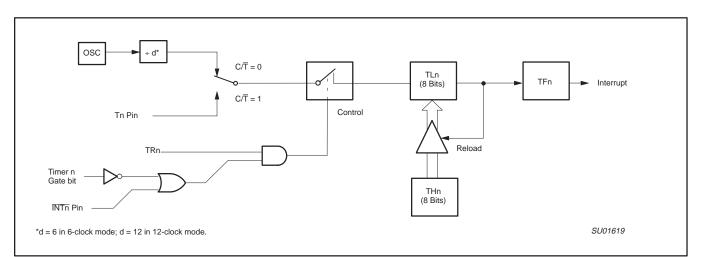

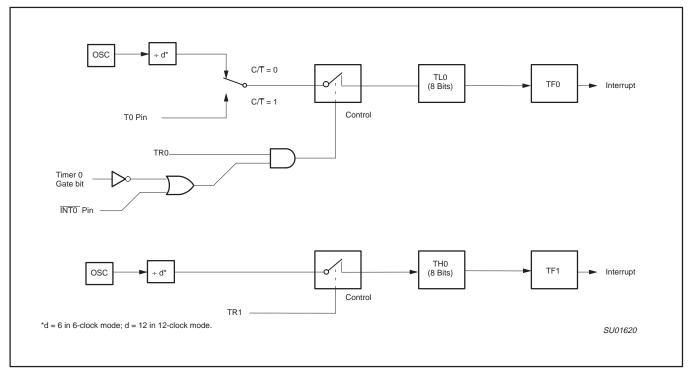

Figure 18. Timer/Counter 0/1 Mode 2: 8-Bit Auto-Reload

Figure 19. Timer/Counter 0 Mode 3: Two 8-Bit Counters

### P89C660/P89C662/P89C664/ P89C668

### **TIMER 2 OPERATION**

#### Timer 2

Timer 2 is a 16-bit Timer/Counter which can operate as either an event timer or an event counter, as selected by  $C/T^2$  in the special function register T2CON (see Figure 20). Timer 2 has three operating modes:

- Capture Mode

- Auto-Reload Mode (up or down counting)

- Baud Rate Generator Mode (see Table 10)

#### **Capture Mode**

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, then Timer 2 is a 16-bit timer or counter (as selected by C/T2 in T2CON) which, upon overflowing sets bit TF2, the Timer 2 overflow bit. This bit can be used to generate an interrupt (by enabling the Timer 2 interrupt bit in the IE register). If EXEN2 = 1, Timer 2 operates as described above, with the added feature that a 1-to-0 transition at external input pin T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. If Timer 2 interrupt has been enabled, EXF2 will generate an interrupt (which vectors to the same location as Timer 2 overflow interrupt). The Timer 2 interrupt service routine can interrogate TF2 and EXF2 to determine which event caused the interrupt. The capture mode is illustrated in Figure 21 (There is no reload value for TL2 and TH2 in this mode). Even when a capture event occurs from T2EX, the counter keeps on counting T2EX pin transitions or osc/6 pulses (osc/12 in 12 clock mode).

#### Auto-Reload Mode (Up or Down Counter)

In the 16-bit auto-reload mode, Timer 2 can be configured as either a timer or counter (C/ $\overline{T}$ 2 in T2CON), then programmed to count up

or down. The counting direction is determined by bit DCEN (Down Counter Enable) which is located in the T2MOD register (see Figure 22). When reset is applied (DCEN = 0), Timer 2 defaults to counting up. If DCEN bit is set, Timer 2 can count up or down depending on the value of the T2EX pin.

Figure 23 shows Timer 2 which will count up automatically since DCEN = 0. In this mode there are two options selected by bit EXEN2 in T2CON register. If EXEN2 = 0, then Timer 2 counts up to 0FFFFH and sets the TF2 (Overflow Flag) bit upon overflow. This causes the Timer 2 registers to be reloaded with the 16-bit value in RCAP2L and RCAP2H. The values in RCAP2L and RCAP2H are preset by software.

If EXEN2 = 1, then a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at input pin T2EX. This transition also sets the EXF2 bit. The Timer 2 interrupt, if enabled, can be generated when either TF2 or EXF2 are 1.

In Figure 24 DCEN = 1 which enables Timer 2 to count up or down. This mode allows pin T2EX to control the direction of count. When a logic 1 is applied at pin T2EX Timer 2 will count up. Timer 2 will overflow at 0FFFFH and set the TF2 flag, which can then generate an interrupt, if the interrupt is enabled. This timer overflow also causes the 16-bit value in RCAP2L and RCAP2H to be reloaded into the timer registers TL2 and TH2.

When a logic 0 is applied at pin T2EX this causes Timer 2 to count down. The timer will underflow when TL2 and TH2 become equal to the value stored in RCAP2L and RCAP2H. Timer 2 underflow sets the TF2 flag and causes 0FFFFH to be reloaded into the timer registers TL2 and TH2.

The external flag EXF2 toggles when Timer 2 underflows or overflows. This EXF2 bit can be used as a 17th bit of resolution if needed. The EXF2 flag does not generate an interrupt in this mode of operation.

|        | (MSE     | 3)                                                 |                               |                           |                             |             |               | (LSB)         |                                                                     |

|--------|----------|----------------------------------------------------|-------------------------------|---------------------------|-----------------------------|-------------|---------------|---------------|---------------------------------------------------------------------|

|        | Т        | F2 EXF2                                            | RCLK                          | TCLK                      | EXEN2                       | TR2         | C/T2          | CP/RL2        |                                                                     |

| Symbol | Position | Name and Sig                                       | nificance                     |                           |                             |             |               |               |                                                                     |

| TF2    | T2CON.7  | Timer 2 overflo<br>when either R                   |                               |                           | overflow and                | d must be c | leared by sc  | oftware. TF2  | will not be set                                                     |

| EXF2   | T2CON.6  |                                                    | hen Timer 2<br>e. EXF2 mu     | interrupt is st be cleare | enabled, EX                 | F2 = 1 will | cause the C   | PU to vector  | ition on T2EX and<br>r to the Timer 2<br>it in up/down              |

| RCLK   | T2CON.5  | Receive clock<br>in modes 1 and                    |                               |                           |                             |             |               |               | r its receive clock                                                 |

| TCLK   | T2CON.4  | Transmit clock<br>in modes 1 and                   |                               |                           |                             |             |               |               | or its transmit cloc<br>k.                                          |

| EXEN2  | T2CON.3  | Timer 2 extern<br>transition on T<br>ignore events | 2EX if Timer                  |                           |                             |             |               |               |                                                                     |

| TR2    | T2CON.2  | Start/stop cont                                    | rol for Timer                 | 2. A logic 1              | starts the ti               | mer.        |               |               |                                                                     |

| C/T2   | T2CON.1  |                                                    | nternal time                  | r (OSĆ/6 in               | 6-clock moc<br>falling edge |             | 2 in 12-cloc  | k mode)       |                                                                     |

| CP/RL2 | T2CON.0  | cleared, auto-r                                    | eloads will c<br>hen either R | occur either              | with Timer 2                | overflows   | or negative t | ransitions at | EXEN2 = 1. When<br>T2EX when<br>ced to auto-reload<br><i>SU0125</i> |

Figure 20. Timer/Counter 2 (T2CON) Control Register

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

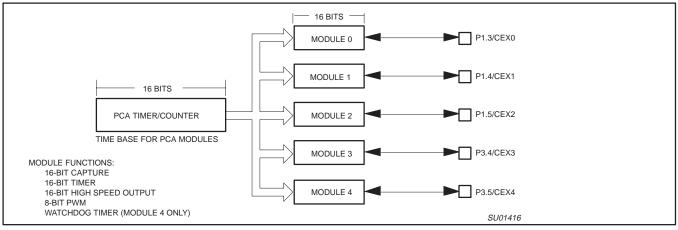

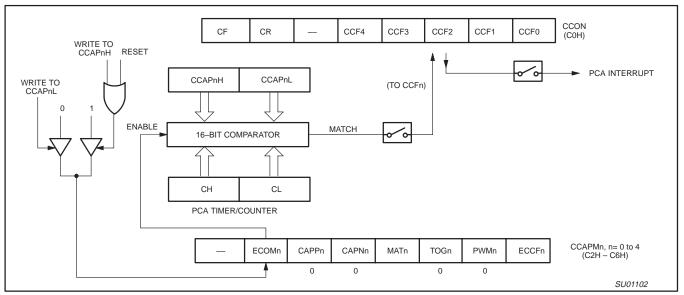

### Programmable Counter Array (PCA)

The Programmable Counter Array available on the 89C66x is a special 16-bit Timer that has five 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3(CEX0), module 1 to P1.4(CEX1), etc. The basic PCA configuration is shown in Figure 40.

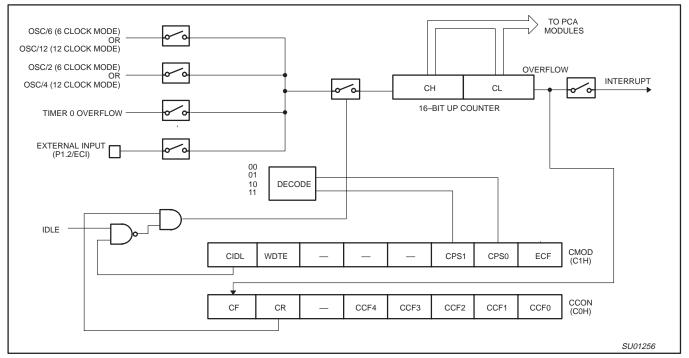

The PCA timer is a common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, the Timer 0 overflow, or the input on the ECI pin (P1.2). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see Figure 43):

#### CPS1 CPS0 PCA Timer Count Source

- 01/6 oscillator frequency (6 clock mode);<br/>1/12 oscillator frequency (12 clock mode)011/2 oscillator frequency (6 clock mode);

- 1/4 oscillator frequency (12 clock mode) 1 0 Timer 0 overflow

- 1 1 External Input at ECI pin

In the CMOD SFR, there are three additional bits associated with the PCA. They are CIDL which allows the PCA to stop during idle mode, WDTE which enables or disables the watchdog function on module 4, and ECF which, when set, causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows. These functions are shown in Figure 41.

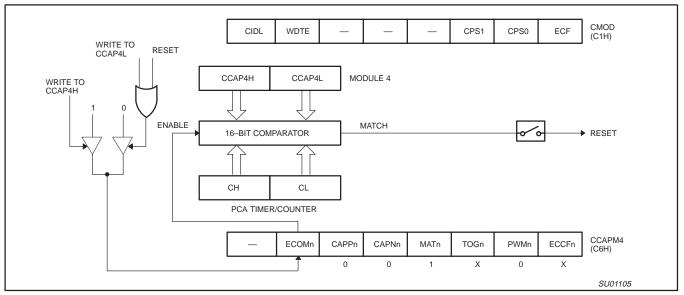

The watchdog timer function is implemented in module 4 (see Figure 50).

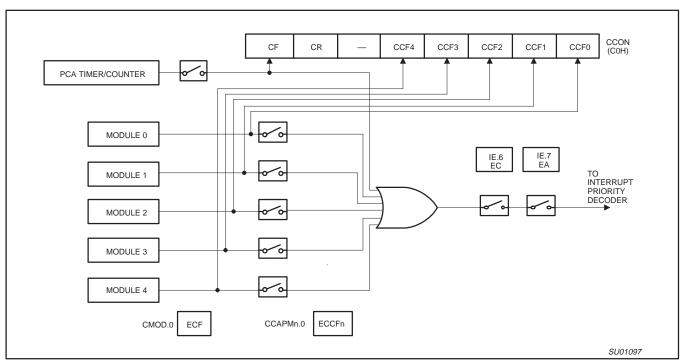

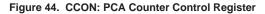

The CCON SFR contains the run control bit for the PCA, and the flags for the PCA timer (CF) and each module (refer to Figure 44). To run the PCA the CR bit (CCON.6) must be set by software. The PCA is shut off by clearing this bit. The CF bit (CCON.7) is set when

the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set, The CF bit can only be cleared by software. Bits 0 through 4 of the CCON register are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software. The PCA interrupt system is shown in Figure 42.

P89C660/P89C662/P89C664/

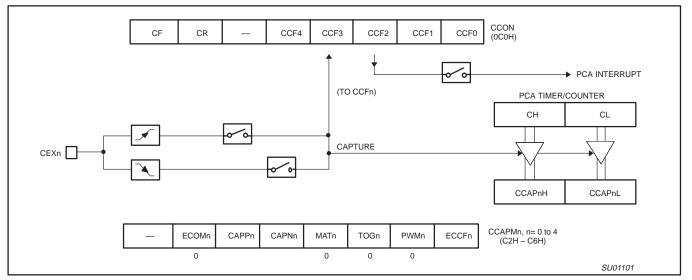

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (see Figure 45). The registers contain the bits that control the mode that each module will operate in. The ECCF bit (CCAPMn.0 where n = 0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2), when set, causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. The match bit MAT (CCAPMn.3), when set, will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set, both edges will be enabled and a capture will occur for either transition. The last bit ECOM (CCAPMn.6), when set, enables the comparator function. Figure 46 shows the CCAPMn settings for the various PCA functions.

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output.

Figure 40. Programmable Counter Array (PCA)

P89C660/P89C662/P89C664/

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

#### Figure 41. PCA Timer/Counter

Figure 42. PCA Interrupt System

### P89C660/P89C662/P89C664/ P89C668

|        |                      | CIDL                     | WDTE                         | -                       | -                                        | -                            | CPS1                           | CPS0                      | ECF          |                        |

|--------|----------------------|--------------------------|------------------------------|-------------------------|------------------------------------------|------------------------------|--------------------------------|---------------------------|--------------|------------------------|

|        | Bit:                 | 7                        | 6                            | 5                       | 4                                        | 3                            | 2                              | 1                         | 0            | -                      |

| Symbol | Functi               | ion                      |                              |                         |                                          |                              |                                |                           |              |                        |

| CIDL   |                      |                          | trol: CIDL =<br>during idle. | 0 progran               | ns the PCA                               | Counter to                   | continue fur                   | nctioning du              | ring idle M  | ode. CIDL = 1 programs |

| WDTE   | Watch                | dog Timer                | Enable: WI                   | DTE = 0 di              | sables Wat                               | chdog Time                   | er function o                  | n PCA Modu                | ule 4. WDT   | E = 1 enables it.      |

| _      | Not im               | plemented                | d, reserved f                | or future u             | ise.*                                    |                              |                                |                           |              |                        |

| CPS1   | PCA C                | ount Puls                | e Select bit                 | 1.                      |                                          |                              |                                |                           |              |                        |

| CPS0   | PCA C<br><b>CPS1</b> | ount Puls<br><b>CPS0</b> | e Select bit<br>Selecte      | 0.<br><b>d PCA In</b> j | out**                                    |                              |                                |                           |              |                        |

|        | 0                    | 0                        | 0                            | Intern                  | al clock, f <sub>Os</sub>                | $_{\rm SC}/6$ in 6 cl        | ock mode (fo                   | <sub>DSC</sub> /12 in 12  | clock mod    | le)                    |

|        | 0                    | 1                        | 1                            | Intern                  | al clock, f <sub>Os</sub>                | $_{\rm SC}^{\rm V2}$ in 6 cl | ock mode (fo                   | <sub>DSC</sub> /4 in 12 o | clock mode   | e)                     |

|        | 1                    | 0                        | 2                            | Timer                   | 0 overflow                               |                              |                                |                           |              |                        |

|        | 1                    | 1                        | 3                            |                         | nal clock at<br>x. rate = f <sub>O</sub> |                              | in<br>ock mode, f <sub>(</sub> | <sub>DCS</sub> /8 in 12   | clock mode   | e)                     |

| ECF    |                      | nable Counction of C     |                              | ow interrup             | ot: ECF = 1                              | enables C                    | F bit in CCO                   | N to genera               | te an interr | upt. ECF = 0 disables  |

#### Figure 43. CMOD: PCA Counter Mode Register

|                   | Bit Ado                                               | dressable                                                                               | _                                                                                |                                                                                              |                                                                                      |                                                                           |                                        |                                                                        |                                                                     | _                                                          |

|-------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|

|                   |                                                       | CF                                                                                      | CR                                                                               | -                                                                                            | CCF4                                                                                 | CCF3                                                                      | CCF2                                   | CCF1                                                                   | CCF0                                                                |                                                            |

|                   | Bit:                                                  | 7                                                                                       | 6                                                                                | 5                                                                                            | 4                                                                                    | 3                                                                         | 2                                      | 1                                                                      | 0                                                                   |                                                            |

| Symbol            | Funct                                                 | ion                                                                                     |                                                                                  |                                                                                              |                                                                                      |                                                                           |                                        |                                                                        |                                                                     |                                                            |

| CF                | PCA (                                                 | Counter O                                                                               | verflow flag                                                                     | . Set by ha                                                                                  | rdware whe                                                                           | n the counte                                                              | er rolls over                          | . CF flags a                                                           | n interrupt                                                         | if bit ECF in CMOD is                                      |

|                   |                                                       |                                                                                         |                                                                                  |                                                                                              | e or software                                                                        |                                                                           | ly be cleare                           |                                                                        |                                                                     |                                                            |

| CR                | set. C                                                | F may be<br>Counter R                                                                   | set by eithe                                                                     | er hardware                                                                                  | e or software                                                                        | but can on                                                                |                                        | ed by softwa                                                           | are.                                                                | oftware to turn the PC                                     |

| CR<br>-           | set. C<br>PCA (<br>counte                             | F may be<br>Counter R<br>er off.                                                        | set by eithe                                                                     | er hardware<br>hit. Set by s                                                                 | e or software<br>oftware to tu                                                       | but can on                                                                |                                        | ed by softwa                                                           | are.                                                                |                                                            |

| CR<br>-<br>CCF4   | set. C<br>PCA (<br>counte<br>Not im                   | F may be<br>Counter R<br>er off.<br>plemente                                            | set by eithe<br>un control b<br>d, reserved                                      | er hardware<br>vit. Set by s<br>for future u                                                 | e or software<br>oftware to tu<br>use*.                                              | but can on<br>urn the PCA                                                 | counter on                             | ed by softwa<br>. Must be c                                            | are.<br>leared by s                                                 |                                                            |

| _                 | set. C<br>PCA (<br>counte<br>Not im<br>PCA N          | F may be<br>Counter R<br>er off.<br>nplemente<br>Module 4 i                             | set by eithe<br>un control b<br>ed, reserved<br>interrupt flag                   | er hardware<br>hit. Set by s<br>for future to<br>g. Set by ha                                | e or software<br>oftware to tu<br>use*.<br>ardware whe                               | but can on<br>urn the PCA<br>en a match o                                 | counter on                             | ed by softwa<br>. Must be c<br>occurs. Mus                             | are.<br>leared by s<br>t be cleared                                 | oftware to turn the PC                                     |

| -<br>CCF4         | set. C<br>PCA C<br>counte<br>Not im<br>PCA N<br>PCA N | F may be<br>Counter R<br>er off.<br>nplemente<br>Module 4 i<br>Module 3 i               | set by eithe<br>un control b<br>d, reserved<br>nterrupt flag                     | er hardware<br>hit. Set by s<br>for future t<br>g. Set by ha<br>g. Set by ha                 | e or software<br>oftware to tu<br>use*.<br>ardware whe<br>ardware whe                | but can on<br>urn the PCA<br>en a match o<br>en a match o                 | or capture c                           | ed by softwa<br>. Must be c<br>occurs. Mus<br>occurs. Mus              | are.<br>leared by s<br>t be cleared<br>t be cleared                 | oftware to turn the PC<br>d by software.                   |

| -<br>CCF4<br>CCF3 | set. C<br>PCA C<br>counte<br>Not im<br>PCA N<br>PCA N | F may be<br>Counter R<br>er off.<br>nplemente<br>Module 4 i<br>Module 3 i<br>Module 2 i | set by eithe<br>un control b<br>ed, reserved<br>interrupt flag<br>interrupt flag | er hardware<br>bit. Set by s<br>for future u<br>g. Set by ha<br>g. Set by ha<br>g. Set by ha | e or software<br>oftware to tu<br>use*.<br>ardware whe<br>ardware whe<br>ardware whe | but can on<br>urn the PCA<br>en a match o<br>en a match o<br>en a match o | or capture cor capture cor capture cor | ed by softwa<br>Must be c<br>occurs. Mus<br>occurs. Mus<br>occurs. Mus | are.<br>leared by s<br>t be cleared<br>t be cleared<br>t be cleared | oftware to turn the PC<br>d by software.<br>d by software. |

SU01099

# P89C660/P89C662/P89C664/ P89C668

Figure 47. PCA Capture Mode

Figure 48. PCA Compare Mode

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

Figure 51. PCA Watchdog Timer m(Module 4 only)

#### PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed.

Figure 51 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for **all** modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

P89C660/P89C662/P89C664/

Figure 52 shows the code for initializing the watchdog timer. Module 4 can be configured in either compare mode, and the WDTE bit in CMOD must also be set. The user's software must periodically change (CCAP4H,CCAP4L) to keep a match from occurring with the PCA timer (CH,CL). This code is given in the WATCHDOG routine in Figure 52.

This routine should not be part of an interrupt service routine, because if the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the watchdog will keep getting reset. Thus, the purpose of the watchdog would be defeated. Instead, call this subroutine from the main program within  $2^{16}$  count of the PCA timer.

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

#### Expanded Data RAM Addressing

The P89C660/662/664/668 has internal data memory that is mapped into four separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM, 128 bytes Special Function Register (SFR), and 256 bytes expanded RAM (ERAM) (256 bytes for the '660; 768 bytes for the '662; 1792 bytes for the '664; 7936 bytes for the '668).

The four segments are:

- The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- The 256/768/1792/7936-bytes expanded RAM (ERAM, 00H – XFFH/2FFH/6FFH/1FFFH) are indirectly accessed by move external instruction, MOVX, and with the EXTRAM bit cleared, see Figure 53.

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM, or to SFR space by the addressing mode used in the instruction. Instructions that use direct addressing, access SFR space. For example:

MOV 0A0H,A

accesses the SFR at location 0A0H (which is P2). Instructions that use indirect addressing, access the Upper 128 bytes of data RAM.

For example:

MOV @R0,A

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

P89C660/P89C662/P89C664/

The ERAM can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory is physically located on-chip, logically occupies the first 256 bytes (660), 768 (662), 1792 (664), 7936 (668) of external data memory.

With EXTRAM = 0, the ERAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to ERAM will not affect ports P0, P3.6 (WR#) and P3.7 (RD#). P2 SFR is in output state during external addressing. For example, with EXTRAM = 0,

MOVX @R0,A

where R0 contains 0A0H, access the ERAM at address 0A0H rather than external memory. An access to external data memory locations higher than the ERAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51 (with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals. Refer to Figure 54).

With EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an 8-bit address multiplexed with data on Port 0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a 16-bit address. Port 2 outputs the high-order eight address bits (the contents of DPH) while Port 0 multiplexes the low-order eight address bits (the contents of DPL) with data. MOVX @Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the ERAM.

| AUXR   | Audies                             | s = 8EH    |                                                                                            |                                                                              |                                                       |                          |               |               | I        | Reset Value = xxxx xx10                                         |

|--------|------------------------------------|------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------|---------------|---------------|----------|-----------------------------------------------------------------|

|        | Not Bit                            | Addressat  | le                                                                                         |                                                                              |                                                       |                          |               |               |          |                                                                 |

|        |                                    | _          | _                                                                                          | —                                                                            | _                                                     | _                        | _             | EXTRAM        | AO       |                                                                 |

|        | Bit:                               | 7          | 6                                                                                          | 5                                                                            | 4                                                     | 3                        | 2             | 1             | 0        |                                                                 |

| Symbol | Func                               | tion       |                                                                                            |                                                                              |                                                       |                          |               |               |          |                                                                 |

| AO     | Disab                              | le/Enable  | ALE                                                                                        |                                                                              |                                                       |                          |               |               |          |                                                                 |

|        | AO                                 |            | <b>O</b>                                                                                   | Mada                                                                         |                                                       |                          |               |               |          |                                                                 |

|        | AU                                 |            | Operating                                                                                  | woae                                                                         |                                                       |                          |               |               |          |                                                                 |

|        | 0                                  |            |                                                                                            |                                                                              | onstant rate                                          | of $1/3$ the os          | scillator fre | equency (6 cl | ock mode | ; <sup>1</sup> / <sub>6</sub> f <sub>OSC</sub> in 12 clock mo   |

|        | -                                  |            | ALE is emi                                                                                 | tted at a co                                                                 |                                                       | of $1/3$ the osmemory ac |               | equency (6 cl | ock mode | ; $^{1/}_{6}$ f <sub>OSC</sub> in 12 clock mod                  |

| EXTRAM | 0<br>1                             | al/Externa | ALE is emi                                                                                 | itted at a co<br>ve only du                                                  | ring off-chip                                         | memory ac                |               | equency (6 cl | ock mode | ; $^{1/_{6}}$ f <sub>OSC</sub> in 12 clock mod                  |

| EXTRAM | 0<br>1                             |            | ALE is emi<br>ALE is acti<br>I RAM acce                                                    | itted at a co<br>ve only dui<br>ss using M                                   | ring off-chip                                         | memory ac                |               | equency (6 cl | ock mode | $^{1/6} f_{OSC}$ in 12 clock mod                                |

| EXTRAM | 0<br>1<br>Intern                   |            | ALE is emi<br>ALE is acti<br>I RAM acces<br><b>Operating</b>                               | itted at a co<br>ve only dui<br>ss using M<br><b>Mode</b>                    | ring off-chip<br>OVX @Ri/@                            | memory ac                | CESS.         | equency (6 cl | ock mode | e; <sup>1</sup> / <sub>6</sub> f <sub>OSC</sub> in 12 clock mod |

| EXTRAM | 0<br>1<br>Intern<br>EXTR           |            | ALE is emi<br>ALE is acti<br>I RAM acces<br><b>Operating</b>                               | itted at a co<br>ve only dui<br>ss using M<br>Mode<br>RAM acces              | ring off-chip<br>OVX @Ri/@<br>s using MO              | memory ac<br>DPTR        | CESS.         | equency (6 cl | ock mode | e; <sup>1</sup> / <sub>6</sub> f <sub>OSC</sub> in 12 clock mod |

| EXTRAM | 0<br>1<br>Intern<br>EXTR<br>0<br>1 | RAM        | ALE is emi<br>ALE is acti<br>I RAM acce<br><b>Operating</b><br>Internal EF                 | itted at a co<br>ve only du<br>ss using M<br>Mode<br>RAM acces<br>ata memory | ring off-chip<br>OVX @Ri/@<br>s using MO<br>y access. | memory ac<br>DPTR        | CESS.         | equency (6 cl | ock mode | e; <sup>1</sup> / <sub>6</sub> f <sub>OSC</sub> in 12 clock mod |

| EXTRAM | 0<br>1<br>Intern<br>EXTR<br>0<br>1 | RAM        | ALE is emi<br>ALE is acti<br>I RAM acces<br><b>Operating</b><br>Internal EF<br>External da | itted at a co<br>ve only du<br>ss using M<br>Mode<br>RAM acces<br>ata memory | ring off-chip<br>OVX @Ri/@<br>s using MO<br>y access. | memory ac<br>DPTR        | CESS.         | equency (6 cl | ock mode | ; <sup>1</sup> / <sub>6</sub> f <sub>OSC</sub> in 12 clock mod  |

#### Figure 53. AUXR: Auxiliary Register

# P89C660/P89C662/P89C664/ P89C668

### Security

The security feature protects against software piracy and prevents the contents of the Flash from being read. The Security Lock bits are located in Flash. The P89C660/662/664/668 has 3 programmable security lock bits that will provide different levels of protection for the on-chip code and data (see Table 16).

### Table 16.

|       | SECURITY I | OCK BITS <sup>1</sup> |     | PROTECTION DESCRIPTION                                                                                              |

|-------|------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| Level | LB1        | LB2                   | LB3 | PROTECTION DESCRIPTION                                                                                              |

| 1     | 0          | 0                     | 0   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory. |

| 2     | 1          | 0                     | 0   | Same as level 1, plus block erase is disabled. Erase or programming of the status byte or boot vector is disabled.  |

| 3     | 1          | 1                     | 0   | Same as level 2, plus verify of code memory is disabled.                                                            |

| 4     | 1          | 1                     | 1   | Same as level 3, plus external execution is disabled.                                                               |

#### NOTE:

1. Security bits are independent of each other. Full-chip erase may be performed regardless of the state of the security bits.

2. Any other combination of lockbits is undefined.

3. Setting LBx doesn't prevent programming of unprogrammed bits.

### P89C660/P89C662/P89C664/ P89C668

### **ABSOLUTE MAXIMUM RATINGS1, 2, 3**

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on EA/V <sub>PP</sub> pin to V <sub>SS</sub>                                         | 0 to +13.0             | V    |

| Voltage on any other pin to $V_{SS}$                                                         | -0.5 to +6.5           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

NOTES:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted. 2.

3.

### P89C660/P89C662/P89C664/ P89C668

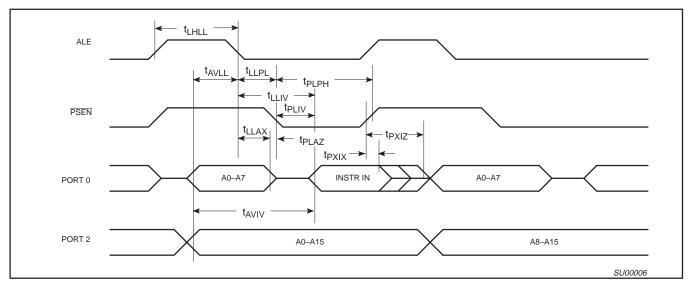

# AC ELECTRICAL CHARACTERISTICS (12 CLOCK MODE) $T_{amb} = 0 \ ^{\circ}C \ to \ +70 \ ^{\circ}C, \ V_{CC} = 5 \ V \pm 10\%, \ or \ -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C, \ V_{CC} = 5 \ V \pm 5\%, \ V_{SS} = 0 \ V^{1, 2, 3}$

|                     |        |                                          | VARIABL                  | E CLOCK <sup>4</sup>                 | 33 MHz | CLOCK <sup>4</sup> |     |

|---------------------|--------|------------------------------------------|--------------------------|--------------------------------------|--------|--------------------|-----|

| SYMBOL              | FIGURE | PARAMETER                                | MIN                      | MAX                                  | MIN    | MAX                |     |

| 1/t <sub>CLCL</sub> | 57     | Oscillator frequency                     | 0                        | 33                                   | -      | -                  | MHz |

| t <sub>LHLL</sub>   | 57     | ALE pulse width                          | 2t <sub>CLCL</sub> -40   | -                                    | 21     | -                  | ns  |

| t <sub>AVLL</sub>   | 57     | Address valid to ALE low                 | t <sub>CLCL</sub> -25    | -                                    | 5      | -                  | ns  |

| t <sub>LLAX</sub>   | 57     | Address hold after ALE low               | t <sub>CLCL</sub> -25    | -                                    | 5      | -                  | ns  |

| t <sub>LLIV</sub>   | 57     | ALE low to valid instruction in          | -                        | 4t <sub>CLCL</sub> -65               | -      | 55                 | ns  |

| t <sub>LLPL</sub>   | 57     | ALE low to PSEN low                      | t <sub>CLCL</sub> -25    | -                                    | 5      | -                  | ns  |

| t <sub>PLPH</sub>   | 57     | PSEN pulse width                         | 3t <sub>CLCL</sub> -45   | -                                    | 45     | -                  | ns  |

| t <sub>PLIV</sub>   | 57     | PSEN low to valid instruction in         | -                        | 3t <sub>CLCL</sub> -60               | -      | 30                 | ns  |

| t <sub>PXIX</sub>   | 57     | Input instruction hold after PSEN        | 0                        | -                                    | 0      | -                  | ns  |

| t <sub>PXIZ</sub>   | 57     | Input instruction float after PSEN       | -                        | t <sub>CLCL</sub> -25                | -      | 5                  | ns  |

| t <sub>AVIV</sub>   | 57     | Address to valid instruction in          | -                        | 5t <sub>CLCL</sub> -80               | -      | 70                 | ns  |

| t <sub>PLAZ</sub>   | 57     | PSEN low to address float                | -                        | 10                                   | -      | 10                 | ns  |

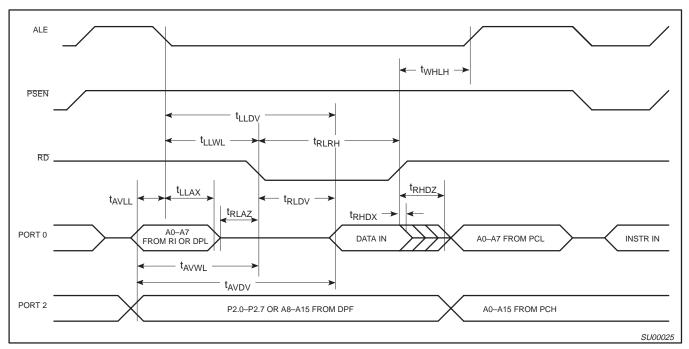

| Data Mem            | ory    | •                                        | •                        | •                                    |        |                    |     |

| t <sub>RLRH</sub>   | 58, 59 | RD pulse width                           | 6t <sub>CLCL</sub> -100  | -                                    | 82     | -                  | ns  |

| t <sub>WLWH</sub>   | 58, 59 | WR pulse width                           | 6t <sub>CLCL</sub> -100  | -                                    | 82     | -                  | ns  |

| t <sub>RLDV</sub>   | 58, 59 | RD low to valid data in                  | -                        | 5t <sub>CLCL</sub> -90               | -      | 60                 | ns  |

| t <sub>RHDX</sub>   | 58, 59 | Data hold after RD                       | 0                        | -                                    | 0      | -                  | ns  |

| t <sub>RHDZ</sub>   | 58, 59 | Data float after RD                      | -                        | 2t <sub>CLCL</sub> -28               | -      | 32                 | ns  |

| t <sub>LLDV</sub>   | 58, 59 | ALE low to valid data in                 | -                        | 8t <sub>CLCL</sub> -150              | -      | 90                 | ns  |

| t <sub>AVDV</sub>   | 58, 59 | Address to valid data in                 | -                        | 9t <sub>CLCL</sub> -165              | -      | 105                | ns  |

| t <sub>LLWL</sub>   | 58, 59 | ALE low to RD or WR low                  | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50               | 40     | 140                | ns  |

| t <sub>AVWL</sub>   | 58, 59 | Address valid to WR low or RD low        | 4t <sub>CLCL</sub> -75   | -                                    | 45     | -                  | ns  |

| t <sub>QVWX</sub>   | 58, 59 | Data valid to WR transition              | t <sub>CLCL</sub> -30    | -                                    | 0      | -                  | ns  |

| t <sub>WHQX</sub>   | 58, 59 | Data hold after WR                       | t <sub>CLCL</sub> -25    | -                                    | 5      | -                  | ns  |

| t <sub>QVWH</sub>   | 59     | Data valid to WR high                    | 7t <sub>CLCL</sub> -130  | -                                    | 80     | -                  | ns  |

| t <sub>RLAZ</sub>   | 58, 59 | RD low to address float                  | -                        | 0                                    | -      | 0                  | ns  |

| t <sub>WHLH</sub>   | 58, 59 | RD or WR high to ALE high                | t <sub>CLCL</sub> -25    | t <sub>CLCL</sub> +25                | 5      | 55                 | ns  |

| External C          | lock   | •                                        | •                        | •                                    |        |                    |     |

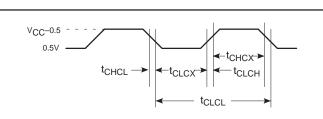

| t <sub>CHCX</sub>   | 61     | High time                                | 17                       | t <sub>CLCL</sub> -t <sub>CLCX</sub> | -      | -                  | ns  |

| t <sub>CLCX</sub>   | 61     | Low time                                 | 17                       | t <sub>CLCL</sub> -t <sub>CHCX</sub> | -      | -                  | ns  |

| t <sub>CLCH</sub>   | 61     | Rise time                                | -                        | 5                                    | -      | -                  | ns  |

| t <sub>CHCL</sub>   | 61     | Fall time                                | -                        | 5                                    | -      | -                  | ns  |

| Shift Regi          | ster   | ·                                        | •                        |                                      |        | •                  |     |

| t <sub>XLXL</sub>   | 60     | Serial port clock cycle time             | 12t <sub>CLCL</sub>      | -                                    | 360    | -                  | ns  |

| t <sub>QVXH</sub>   | 60     | Output data setup to clock rising edge   | 10t <sub>CLCL</sub> -133 | -                                    | 167    | -                  | ns  |

| t <sub>XHQX</sub>   | 60     | Output data hold after clock rising edge | 2t <sub>CLCL</sub> -80   | -                                    | 50     | -                  | ns  |

| t <sub>XHDX</sub>   | 60     | Input data hold after clock rising edge  | 0                        | -                                    | 0      | - 1                | ns  |

| t <sub>XHDV</sub>   | 60     | Clock rising edge to input data valid    |                          | 10t <sub>CLCL</sub> -133             | -      | 167                | ns  |

NOTES:

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

3. Interfacing the microcontroller to devices with float times up to 45 ns is permitted. This limited bus contention will not cause damage to Port 0 drivers.

4. Parts are tested to 3.5 MHz, but guaranteed to operate down to 0 Hz.

### **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

- A Address

- C Clock

- D Input data

- H Logic level high

- I Instruction (program memory contents)

- L Logic level low, or ALE

- P PSEN

- Q Output data

- R RD signal

- t Time V Valid

- W- WR signal

- X No longer a valid logic level

Z - Float

**Examples:** t<sub>AVLL</sub> = Time for address valid to ALE low.  $t_{LLPL}$  = Time for ALE low to  $\overline{PSEN}$  low.

Figure 57. External Program Memory Read Cycle

Figure 58. External Data Memory Read Cycle

P89C660/P89C662/P89C664/ P89C668

P89C660/P89C662/P89C664/

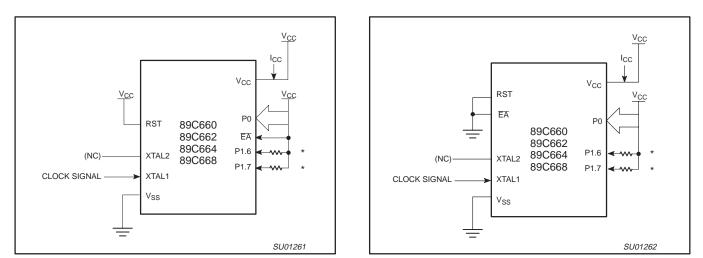

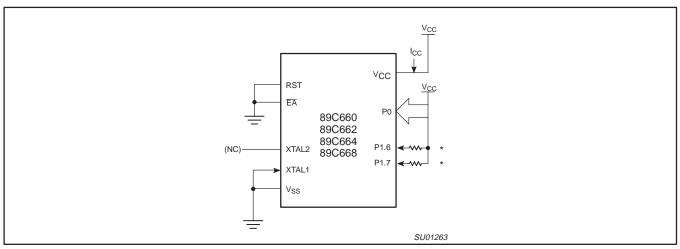

Figure 69.  $I_{CC}$  Test Condition, Idle Mode.

All other pins are disconnected

# 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

Figure 71.  $I_{CC}$  Test Condition, Power-Down mode. All other pins are disconnected;  $V_{CC}$  = 2V to 5.5V

#### NOTE:

Ports 1.6 and 1.7 should be connected to  $V_{CC}$  through resistors of sufficiently high value such that the sink current into these pins does not exceed the  $I_{OL1}$  specification.

P89C660/P89C662/P89C664/ P89C668