Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | FR81S                                                                          |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, CSIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                        |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                        |

| Number of I/O              | 96                                                                             |

| Program Memory Size        | 448KB (448K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 64K x 8                                                                        |

| RAM Size                   | 56K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 42x12b; D/A 2x8b                                                           |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 120-LQFP                                                                       |

| Supplier Device Package    | 120-LQFP (16x16)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f523jsepmc-gse1 |

| A d drass                | Address offset value / Register name |         |                               |                    |          |  |  |  |  |

|--------------------------|--------------------------------------|---------|-------------------------------|--------------------|----------|--|--|--|--|

| Address                  | +0                                   | +1      | +2                            | +3                 | Block    |  |  |  |  |

| 000954н                  | TPUTCN11 [R/W]<br>B,H,W<br>00000     | _       | _                             | _                  |          |  |  |  |  |

| 000958н                  | TPUTCN12 [R/W]<br>B,H,W<br>00000     | _       |                               |                    |          |  |  |  |  |

| 00095Сн                  | TPUTCN13 [R/W]<br>B,H,W<br>00000     | _       |                               |                    |          |  |  |  |  |

| 000960н                  | TPUTCN14 [R/W]<br>B,H,W<br>00000     | _       | _                             | _                  |          |  |  |  |  |

| 000964н                  | TPUTCN15 [R/W]<br>B,H,W<br>00000     | _       | _                             | _                  |          |  |  |  |  |

| 000968н                  | TPUTCN16 [R/W]<br>B,H,W<br>00000     | _       | _                             | _                  |          |  |  |  |  |

| 00096Сн                  | TPUTCN17 [R/W]<br>B,H,W<br>00000     | _       | Time Protection Unit [S]      |                    |          |  |  |  |  |

| 000970н                  |                                      |         | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 000974н                  |                                      |         | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 000978н                  |                                      | TPUTCC2 | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 00097Сн                  |                                      | TPUTCC3 | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 000980н                  |                                      |         | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 000984н                  |                                      |         | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 000988н                  |                                      | TPUTCC6 | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 00098Сн                  |                                      |         | [R] B,H,W<br>0000000 00000000 |                    |          |  |  |  |  |

| 000990н<br>to<br>0009FCн | _                                    | _       | _                             | _                  | 1        |  |  |  |  |

| 000A00н<br>to<br>000BECн | _                                    | _       | _                             | _                  | Reserved |  |  |  |  |

| 000ВF0н                  |                                      |         | /W] B,H,W<br>000000 00000000  |                    | OCDU     |  |  |  |  |

| 000ВF4н                  | <u> </u>                             | _       | _                             | _                  |          |  |  |  |  |

| 000ВF8н                  | _                                    | _       | 00 X                          | W] B,H,W<br>XXXXXX | OCDU     |  |  |  |  |

| 000BFC <sub>н</sub>      | _                                    | _       | UER [W                        | 0000               |          |  |  |  |  |

| Address             |                                          | Address offset val                       | ue / Register name                       |                                                                | Diesk                                                                        |  |

|---------------------|------------------------------------------|------------------------------------------|------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------|--|

| Address             | +0                                       | +1                                       | +2                                       | +3                                                             | Block                                                                        |  |

| 001778н             | SCR1/(IBCR1) [R/W]<br>B,H,W<br>000000    | SMR1[R/W] B,H,W<br>000-00-0              | SSR1[R/W] B,H,W<br>0-000011              | ESCR1/(IBSR1)[R/W<br>] B,H,W<br>00000000                       | Multi-UART1                                                                  |  |

| 00177Сн             | — /(RDR11/(TDF                           | R11))[R/W] B,H,W<br>*3                   | ,                                        | 01)[R/W] B,H,W<br>0000000 *1                                   |                                                                              |  |

| 001780н             | SACSR1[F<br>0000 (                       | R/W] B,H,W<br>00000000                   | _                                        | R] B,H,W<br>00000000                                           | Multi-UART1                                                                  |  |

| 001784н             | _                                        | R/W] B,H,W<br>00000000                   | ,                                        | UR1)[R/W] B,H,W                                                | *1: Byte access is possible                                                  |  |

| 001788н             | — /(SCSTR31)/<br>(LAMSR1)<br>[R/W] B,H,W | — /(SCSTR21)/<br>(LAMCR1)<br>[R/W] B,H,W | — /(SCSTR11)/<br>(SFLR11)<br>[R/W] B,H,W | — /(SCSTR01)/<br>(SFLR01)<br>[R/W] B,H,W                       | only for access to lower 8<br>bits.<br>*2: Reserved because I <sup>2</sup> C |  |

| 00178С <sub>н</sub> | _                                        | — /(SCSFR21)[R/W]<br>B,H,W<br>*3         | — /(SCSFR11)<br>[R/W] B,H,W              | — /(SCSFR01)<br>[R/W] B,H,W                                    | mode is not set immediately after reset.                                     |  |

| 001790н             | —/(TBYTE31)/<br>(LAMESR1)<br>[R/W] B,H,W | —/(TBYTE21)/<br>(LAMERT1)<br>[R/W] B,H,W | —/(TBYTE11)/<br>(LAMIER1)<br>[R/W] B,H,W | TBYTE01/(LAMRID1)<br>/<br>(LAMTID1)<br>[R/W] B,H,W<br>00000000 | Multi-UART1 *3: Reserved because CSIO                                        |  |

| 001794н             | _ ·                                      | W] H,W<br>00000000                       | — /(ISMK1)[R/W]<br>B,H,W<br>*2           | — /(ISBA1)[R/W]<br>B,H,W<br>                                   | mode is not set immediately after reset.                                     |  |

| 001798н             | FCR11[R/W]<br>B,H,W<br>00100             | FCR01[R/W]<br>B,H,W<br>-0000000          | -                                        | R/W] B,H,W<br>00000000                                         | *4: Reserved because<br>LIN2.1 mode is not set<br>immediately after reset.   |  |

| 00179Сн             | _                                        | /W] B,H,W<br>00000000                    | _                                        | _                                                              |                                                                              |  |

|                                                   | Interrupt | Number          | l                  |                   | Default               |                  |

|---------------------------------------------------|-----------|-----------------|--------------------|-------------------|-----------------------|------------------|

| Interrupt Factor                                  | Decimal   | Hexa<br>Decimal | Interrupt<br>Level | Offset            | Address for TBR       | RN               |

| Multi-function serial interface                   |           |                 |                    |                   |                       |                  |

| ch_4 (reception completed)                        | 28        | 1C              | ICR12              | 38Сн              | 000FFF8Сн             | 12* <sup>1</sup> |

| Multi-function serial interface                   | 20        | 10              | ICK12              | SOCH              | UUUFFFOCH             | 12               |

| ch.4 (status)                                     |           |                 |                    |                   |                       |                  |

| Multi-function serial interface                   | 29        | 1D              | ICR13              | 388н              | 000FFF88н             | 13               |

| ch.4 (transmission completed)                     | 23        | 10              | 101(13             | 300H              | 00011100н             | 13               |

| Multi-function serial interface                   |           |                 |                    |                   |                       |                  |

| ch.5 (reception completed)                        | 30        | 1E              | ICR14              | 384н              | 000FFF84 <sub>н</sub> | 14* <sup>1</sup> |

| Multi-function serial interface                   |           | '-              | 101114             | 30 <del>1</del> n | 000111046             | 14               |

| ch.5 (status)                                     |           |                 |                    |                   |                       |                  |

| Multi-function serial interface                   | 31        | 1F              | ICR15              | 380н              | 000FFF80н             | 15               |

| ch.5 (transmission completed)                     | 01        |                 | 101110             | 00011             | 0001110011            |                  |

| Multi-function serial interface                   |           |                 |                    |                   |                       |                  |

| ch.6 (reception completed)                        | 32        | 20              | ICR16              | 37Сн              | 000FFF7Сн             | 16* <sup>1</sup> |

| Multi-function serial interface                   | V-        | 20              | 101110             | 07 On             |                       | . •              |

| ch.6 (status)                                     |           |                 |                    |                   |                       |                  |

| Multi-function serial interface                   | 33        | 21              | ICR17              | 378н              | 000FFF78 <sub>н</sub> | 17               |

| ch.6 (transmission completed)                     |           |                 |                    |                   |                       |                  |

| CAN0                                              | 34        | 22              | ICR18              | 374 <sub>H</sub>  | 000FFF74 <sub>H</sub> | -                |

| CAN1                                              |           |                 |                    |                   |                       |                  |

| RAM diagnosis end                                 |           |                 |                    |                   |                       |                  |

| RAM initialization completion                     |           |                 |                    |                   |                       |                  |

| Error generation during RAM diagnosis             | 35        | 23              | ICR19              | 370н              | 000FFF70н             | -                |

| Backup RAM diagnosis end                          |           |                 |                    |                   |                       |                  |

| Backup RAM initialization completion              |           |                 |                    |                   |                       |                  |

| Error generation during Backup RAM diagnosis      |           |                 |                    |                   |                       |                  |

| CAN2                                              |           |                 |                    |                   |                       |                  |

| Up/down counter 0                                 | 36        | 24              | ICR20              | 36Сн              | 000FFF6Сн             | -                |

| Up/down counter 1                                 |           |                 |                    |                   |                       |                  |

| Real time clock                                   | 37        | 25              | ICR21              | 368 <sub>H</sub>  | 000FFF68 <sub>н</sub> | -                |

| -                                                 | 38        | 26              | ICR22              | 364н              | 000FFF64н             | _*6              |

| 16-bit Free-run timer 0 (0 detection) /           | 39        | 27              | ICR23              | 360н              | 000FFF60н             | 23               |

| (compare clear)                                   |           |                 |                    |                   |                       |                  |

| PPG 1/10/11/20/30/31                              |           |                 |                    |                   |                       | 0                |

| 16-bit Free-run timer 1 (0 detection) /           | 40        | 28              | ICR24              | 35Сн              | 000FFF5С <sub>н</sub> | 24* <sup>3</sup> |

| (compare clear)                                   |           |                 |                    |                   |                       |                  |

| PPG 2/3/12/13/23/43                               |           |                 |                    |                   |                       |                  |

| 16-bit Free-run timer 2 (0 detection) /           | 41        | 29              | ICR25              | 358н              | 000FFF58н             | 25* <sup>3</sup> |

| (compare clear)                                   |           | _               |                    |                   |                       |                  |

| PPG 4/5/15/24/35                                  | 42        | 2A              | ICR26              | 354н              | 000FFF54н             | 26*3             |

| PPG 7/16/17/26/27/37                              | 43        | 2B              | ICR27              | 350н              | 000FFF50н             | 27*3             |

| PPG 8/18/19/29                                    | 44        | 2C              | ICR28              | 34C <sub>H</sub>  | 000FFF4C <sub>H</sub> | 28*3             |

| 16-bit ICU 0 (fetching) / 16-bit ICU 1 (fetching) | 45        | 2D              | ICR29              | 348н              | 000FFF48 <sub>н</sub> | 29               |

| Main timer                                        |           |                 |                    |                   |                       |                  |

| Sub timer                                         | 46        | 2E              | ICR30              | 344 <sub>H</sub>  | 000FFF44 <sub>н</sub> | 30               |

| PLL timer                                         |           |                 | 10.100             | J                 | 300                   |                  |

| 16-bit ICU 2 (fetching) /16-bit ICU 3 (fetching)  |           |                 |                    |                   |                       |                  |

## 11. Electrical Characteristics

**Absolute Maximum Ratings**

| Parameter                                      | Symbol             | Ra                   | ting                 | Unit | Remarks                                   |  |

|------------------------------------------------|--------------------|----------------------|----------------------|------|-------------------------------------------|--|

| Parameter                                      | Symbol             | Min                  | Max                  | Unit | Remarks                                   |  |

| Power supply voltage *1,*2                     | Vcc                | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +6.0 | V    |                                           |  |

| Analog power supply voltage *1,*2              | AVcc               | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +6.0 | V    | AVRH ≤ AV <sub>CC</sub> ≤ V <sub>CC</sub> |  |

| Analog reference voltage *1                    | AVRH               | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +6.0 | V    | AVRH ≤ AV <sub>CC</sub>                   |  |

| Input voltage *1                               | Vı                 | Vss-0.3              | Vcc+0.3              | V    |                                           |  |

| Analog pin input voltage *1                    | V <sub>IA5</sub>   | Vss-0.3              | Vcc+0.3              | V    |                                           |  |

| Output voltage *1                              | Vo                 | Vss-0.3              | Vcc+0.3              | V    |                                           |  |

| Maximum clamp current                          | I <sub>CLAMP</sub> | -                    | 4.0                  | mA   | *6                                        |  |

| Total maximum clamp current                    | ΣICLAMP            | -                    | 20                   | mA   | *6                                        |  |

| "L" level maximum output current *3            | I <sub>OL1</sub>   | -                    | 15                   | mA   |                                           |  |

| L level maximum output current                 | I <sub>OL2</sub>   | -                    | 30                   | mA   |                                           |  |

| "L" level average output current *4            | lolav1             | -                    | 4                    | mA   | *9                                        |  |

| L level average output current                 | I <sub>OLAV2</sub> | -                    | 12                   | mA   | *10                                       |  |

| "L" level total output current *5              | ΣI <sub>OL1</sub>  | -                    | 100                  | mA   |                                           |  |

| L level total output current                   | ΣI <sub>OL2</sub>  | -                    | 120                  | mA   |                                           |  |

| "H" level maximum output current*3             | I <sub>OH1</sub>   | -                    | -15                  | mA   |                                           |  |

| H level maximum output current                 | I <sub>OH2</sub>   | -                    | -30                  | mA   |                                           |  |

| "H" level average output current*4             | I <sub>OHAV1</sub> | -                    | -4                   | mA   | *9                                        |  |

| H level average output current                 | I <sub>OHAV2</sub> | -                    | -12                  | mA   | *10                                       |  |

| "LI" lovel total output ourrent *5             | ΣI <sub>OH1</sub>  | -                    | -100                 | mA   |                                           |  |

| "H" level total output current *5              | $\Sigma I_{OH2}$   | -                    | -120                 | mA   |                                           |  |

| Power T <sub>A</sub> : -40 °C to +105 °C       | D <sub>D</sub>     | -                    | 882                  | mW   | *8                                        |  |

| consumption T <sub>A</sub> : -40 °C to +125 °C | - P <sub>D</sub>   | -                    | 675                  | mW   | *8                                        |  |

| Operating temperature                          |                    | -40                  | +105                 | °C   |                                           |  |

| Operating temperature                          | T <sub>A</sub>     | -40                  | +125                 | °C   | *7                                        |  |

| Storage temperature                            | Tstg               | -55                  | +150                 | °C   |                                           |  |

<sup>\*1:</sup> These parameters are based on the condition that  $V_{SS} = AV_{SS} = 0.0 \text{ V}$

- · Use within recommended operating conditions.

- · Use at DC voltage (current).

- · The + B signal should always be applied by connecting a limiting resistor between the + B signal and the microcontroller.

- The value of the limiting resistor should be set so that the current input to the microcontroller pin does not exceed rated values at any time regardless of instantaneously or constantly when the + B signal is input.

- Note that when the microcontroller drive current is low, such as in the low power consumption modes, the + B input potential can increase the potential at the V<sub>CC</sub> pin via a protective diode, possibly affecting other devices.

- Note that if the + B signal is input when the microcontroller is off (not fixed at 0 V), since the power is supplied through the pin, the microcontroller may operate incompletely.

- Note that if the +B signal is input at power-on, since the power is supplied through the pin, the power-on reset may not function in the power supply voltage.

- · Do not leave + B input pins open.

Document Number: 002-04662 Rev. \*F

<sup>\*2:</sup> Caution must be taken that AVcc, AVRH do not exceed Vcc upon power-on and under other circumstances.

<sup>\*3:</sup> The maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

<sup>\*4:</sup> The average output current is defined as the value of the average current flowing through any one of the corresponding pins for a 10 ms period. The average value is the operation current × the operation ratio.

<sup>\*5:</sup> The total output current is defined as the maximum current value flowing through all of corresponding pins.

<sup>\*6:</sup> Corresponding pins: all general-purpose ports except P035, 041, 093, 122.

<sup>\*7:</sup> When it is used under this condition, contact your sales representative.

(4) Multi-function Serial

(4-1) CSIO timing

(4-1-1) Bit setting: SMR: MD2 = 0, SMR: MD1 = 1, SMR: MD0 = 0, SMR: SCINV = 0, SCR:SPI = 0

$(T_A: -40 \degree C \text{ to } +125 \degree C, V_{CC} = AV_{CC} = 5.0 \text{ V} \pm 10 \%/V_{CC} = AV_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{SS} = AV_{SS} = 0.0 \text{ V})$

| Dozomotor                                                                       | Cumbal             | Din Nama                                                         | Conditions | Valu                 | ıe  | l lmi4 | Remarks                            |

|---------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------|------------|----------------------|-----|--------|------------------------------------|

| Parameter                                                                       | Symbol             | Pin Name                                                         | Conditions | Min                  | Max | Unit   | Remarks                            |

| Serial clock cycle time                                                         | tscyc              | SCK0 to SCK11                                                    |            | 4t <sub>CPP</sub>    | -   | ns     |                                    |

| SCK ↓ → SOT delay time                                                          | tsLOVI             | SCK0 to SCK2,<br>SCK5 to SCK11<br>SOT0 to SOT2,<br>SOT5 to SOT11 |            | -30                  | 30  | ns     |                                    |

|                                                                                 |                    | SCK3 , SCK4<br>SOT3 , SOT4                                       |            | -300                 | 300 | ns     | Internal shift clock mode          |

| Valid SIN → SCK ↑ setup time                                                    | t <sub>IVSHI</sub> | SCK0 to SCK2,<br>SCK5 to SCK11<br>SIN0 to SIN2,<br>SIN5 to SIN11 | -          | 34                   | -   | ns     | output pin : $C_L = 50 \text{ pF}$ |

|                                                                                 |                    | SCK3 , SCK4<br>SIN3 , SIN4                                       |            | 300                  | 1   | ns     |                                    |

| $\begin{array}{c} SCK \uparrow \to \\ Valid \; SIN \; hold \; time \end{array}$ | t <sub>SHIXI</sub> | SCK0 to SCK11<br>SIN0 to SIN11                                   |            | 0                    | -   | ns     |                                    |

| Serial clock "H"pulse width                                                     | tshsl              |                                                                  |            | t <sub>CPP</sub> +10 | -   | ns     |                                    |

| Serial clock "L" pulse width                                                    | t <sub>SLSH</sub>  | SCK0 to SCK11                                                    |            | 2t <sub>CPP</sub> -1 | -   | ns     |                                    |

| SCK ↓ → SOT delay time                                                          | <b>t</b> slove     | SCK0 to SCK2,<br>SCK5 to SCK11<br>SOT0 to SOT2,<br>SOT5 to SOT11 |            | -                    | 33  | ns     | External shift                     |

| ·                                                                               |                    | SCK3 , SCK4<br>SOT3 , SOT4                                       | -          | -                    | 300 | ns     | clock mode output pin:             |

| Valid SIN → SCK ↑ setup time                                                    | t <sub>IVSHE</sub> | SCK0 to SCK11                                                    |            | 10                   | -   | ns     | C <sub>L</sub> = 50 pF             |

| SCK ↑ → Valid SIN hold time                                                     | tshixe             | SIN0 to SIN11                                                    |            | 20                   | -   | ns     |                                    |

| SCK fall time                                                                   | t <sub>F</sub>     | SCK0 to SCK11                                                    |            | -                    | 5   | ns     |                                    |

| SCK rise time                                                                   | t <sub>R</sub>     | SCK0 to SCK11                                                    |            | -                    | 5   | ns     |                                    |

## Notes:

AC characteristic in CLK synchronized mode.

C<sub>L</sub> is the load capacitance applied to pins during testing.

The maximum bard rate is limited by internal operation clock used and other parameters. Please use ch.3 and ch.4 with maximum baud rate 400 kbps or less.

See Hardware Manual for details.

(4-1-4) Bit setting: SMR : MD2 = 0, SMR:MD1 = 1, SMR : MD0 = 0, SMR:SCINV = 1, SCR:SPI = 1 ( $T_A$ :-40 °C to +125 °C,  $V_{CC}$  = A  $V_{CC}$  = 5.0 V ± 10 %/ $V_{CC}$  = A $V_{CC}$  = 3.3 V ±0.3 V,  $V_{SS}$  = A $V_{SS}$  = 0.0V)

| Parameter                    |                    |                                                                  |            | Valu                 |     |      | Domonko                                                             |

|------------------------------|--------------------|------------------------------------------------------------------|------------|----------------------|-----|------|---------------------------------------------------------------------|

| Parameter                    | Symbol             | Pin Name                                                         | Conditions | Min                  | Max | Unit | Remarks                                                             |

| Serial clock cycle time      | tscyc              | SCK0 to SCK11                                                    |            | 4t <sub>CPP</sub>    | -   | ns   |                                                                     |

| SCK↓→<br>SOT delay time      | tslovi             | SCK0 to SCK2,<br>SCK5 to SCK11<br>SOT0 to SOT2,<br>SOT5 to SOT11 |            | -30                  | 30  | ns   |                                                                     |

|                              |                    | SCK3 , SCK4<br>SOT3 , SOT4                                       |            | -300                 | 300 | ns   |                                                                     |

| Valid SIN → SCK†setup time   | tıvshı             | SCK0 to SCK2,<br>SCK5 to SCK11<br>SIN0 to SIN2,<br>SIN5 to SIN11 | -          | 34                   | -   | ns   | Internal shift clock<br>mode output pin :<br>C <sub>L</sub> = 50 pF |

|                              |                    | SCK3 , SCK4<br>SIN3 , SIN4                                       |            | 300                  | -   | ns   |                                                                     |

| SCK↑→<br>Valid SIN hold time | t <sub>SHIXI</sub> | SCK0 to SCK11<br>SIN0 to SIN11                                   |            | 0                    | -   | ns   |                                                                     |

| SOT→SCK↑<br>delay time       | tsovні             | SCK0 to SCK11<br>SOT0 to SOT11                                   |            | 2tcpp-30             | -   | ns   |                                                                     |

| Serial clock "H"pulse width  | t <sub>SHSL</sub>  | 201/2 / 201/44                                                   |            | t <sub>CPP</sub> +10 | -   | ns   |                                                                     |

| Serial clock "L" pulse width | tslsh              | SCK0 to SCK11                                                    |            | 2tcpp-10             | -   | ns   |                                                                     |

| SCK↓→<br>SOT delay time      | t <sub>SLOVE</sub> | SCK0 to SCK2,<br>SCK5 to SCK11<br>SOT0 to SOT2,<br>SOT5 to SOT11 |            | -                    | 33  | ns   |                                                                     |

|                              |                    | SCK3 , SCK4<br>SOT3 , SOT4                                       | -          | -                    | 300 | ns   | External shift clock mode output pin:                               |

| Valid SIN → SCK↑setup time   | tivshe             | SCK0 to SCK11                                                    |            | 10                   | -   | ns   | C <sub>L</sub> = 50 pF                                              |

| SCK↑→<br>Valid SIN hold time | tshixe             | SIN0 to SIN11                                                    |            | 20                   | -   | ns   |                                                                     |

| SCK fall time                | t <sub>F</sub>     | SCK0 to SCK11                                                    |            | -                    | 5   | ns   |                                                                     |

| SCK rise time                | t <sub>R</sub>     | SCK0 to SCK11                                                    |            | -                    | 5   | ns   |                                                                     |

## Notes:

AC characteristic in CLK synchronized mode.

C<sub>L</sub> is the load capacitance applied to pins during testing.

The maximum bard rate is limited by internal operation clock used and other parameters. Please use ch.3 and ch.4 with maximum baud rate 400 kbps or less.

See Hardware Manual for details.

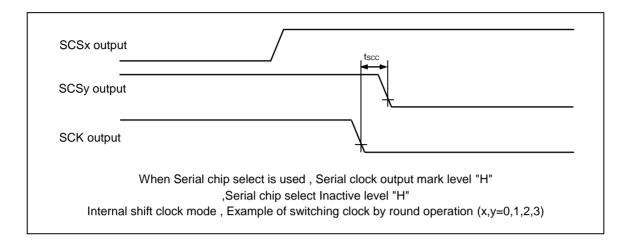

(4-1-5) Bit setting: SMR:MD2 = 0, SMR:MD1 = 1, SMR:MD0 = 0,

When Serial chip select is used: SCSCR:CSEN = 1,

Serial clock output mark level "H": SMR,SCSFR:SCINV = 0, Serial chip select Inactive level "H": SCSCR,SCSFR:CSLVL = 1

$(T_A:-40 \, ^{\circ}C \text{ to } +125 \, ^{\circ}C, \, V_{CC} = AV_{CC} = 5.0 \, V \pm 10 \, \%/V_{CC} = AV_{CC} = 3.3 \, V \pm 0.3 \, V, \, V_{SS} = AV_{SS} = 0.0V)$

| Parameter              | Symbol | Pin Name                                                                                                              | Conditions |                       | lue                    | Unit | Remarks                                                                |

|------------------------|--------|-----------------------------------------------------------------------------------------------------------------------|------------|-----------------------|------------------------|------|------------------------------------------------------------------------|

| Parameter              | Symbol | Pin Name                                                                                                              | Conditions | Min                   | Max                    | Onit | Remarks                                                                |

| SCS↓→SCK↓ setup time   | tcssı  | SCK1, SCK2,<br>SCK5 to SCK11<br>SCS1, SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 |            | tcssu-50              | tcssu+0 *1             | ns   |                                                                        |

|                        |        | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                 |            | t <sub>CSSU</sub> -50 | t <sub>CSSU</sub> +300 | ns   |                                                                        |

| SCK↑→SCS↑<br>hold time | tсsні  | SCK1, SCK2,<br>SCK5 to SCK11<br>SCS1, SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 | -          | tcshd-10              | tcshp+50               | ns   | Internal shift<br>clock mode<br>output pin :<br>C <sub>L</sub> = 50 pF |

|                        |        | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                 |            | tcshd-300             | tcshp+50 *2            | ns   |                                                                        |

| SCS<br>deselect time   | tcspi  | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11            |            | tcsps-50              | tcsps+50               | ns   |                                                                        |

(4-1-8) Bit setting: SMR:MD2 = 0, SMR:MD1 = 1, SMR:MD0 = 0,

When Serial chip select is used: SCSCR:CSEN = 1,

Serial clock output mark level "L" : SMR,SCSFR:SCINV = 1, Serial chip select Inactive level "L" : SCSCR,SCSFR:CSLVL = 0

(T<sub>A</sub>: -40 °C to +125 °C,  $V_{CC} = AV_{CC} = 5.0 \text{ V} \pm 10 \text{ %/V}_{CC} = AV_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{SS} = AV_{SS} = 0.0 \text{ V}$ )

|                        |        | Din Name                                                                                                                | Conditions |                       | lue                    | Unit | Remarks                                                      |  |

|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|------------------------|------|--------------------------------------------------------------|--|

| Parameter              | Symbol | Pin Name                                                                                                                | Conditions | Min                   | Max                    | Onit | Remarks                                                      |  |

| SCS↑→SCK↑ setup time   | tcssı  | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 |            | tcssu-50              | tcssu+0                | ns   |                                                              |  |

|                        |        | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                   |            | t <sub>CSSU</sub> -50 | t <sub>CSSU</sub> +300 | ns   |                                                              |  |

| SCK↓→SCS↓<br>hold time | tсsні  | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 | -          | tcshp-10              | tcshb+50               | ns   | Internal shift clock mode output pin: C <sub>L</sub> = 50 pF |  |

|                        |        | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                   |            | tcshd-300             | tcshp+50<br>*2         | ns   |                                                              |  |

| SCS<br>deselect time   | tcspi  | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11              |            | tcsps-50              | tcsps+50               | ns   |                                                              |  |

| Damanastan                        | 0                 | Dia Nama                                                                                                                               | 0          | Va                    | lue                   | Hadi | Damaria                                                          |  |

|-----------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|-----------------------|------|------------------------------------------------------------------|--|

| Parameter                         | Symbol            | Pin Name                                                                                                                               | Conditions | Min                   | Max                   | Unit | Remarks                                                          |  |

| SCS↑→SCK↑ setup time              | t <sub>CSSE</sub> | SCK1 to SCK11<br>SCS1 to SCS3,<br>SCS40 to SCS43,                                                                                      |            | 3t <sub>CPP</sub> +30 | -                     | ns   |                                                                  |  |

| SCK↓→SCS↓<br>hold time            | tсsне             | SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                                                                 |            | +0                    | -                     | ns   |                                                                  |  |

| SCS<br>deselect time              | tcsde             | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                             | -          | 3tcpp+30              | -                     | ns   | External shift clock mode output pin:                            |  |

| SCS↑→SOT<br>delay time            | tose              | SCS1, SCS2,<br>SCS50~SCS53,<br>SCS60~SCS63,<br>SCS70~SCS73,<br>SCS8~SCS11<br>SOT1, SOT2,<br>SOT5~SOT11                                 |            | -                     | 40                    | ns   | C <sub>L</sub> = 50 pF                                           |  |

|                                   |                   | SCS3,<br>SCS40~SCS43<br>SOT3,SOT4                                                                                                      |            | -                     | 300                   | ns   |                                                                  |  |

| SCS↓→SOT<br>delay time            | tdee              | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SOT1 to SOT11            | -          | +0                    | -                     | ns   | External shift clock mode output pin: C <sub>L</sub> = 50 pF     |  |

| SCK↑→SCS↑<br>clock switch<br>time | tscc              | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SCK3 , SCK4 | -          | Зtсрр-10              | 3t <sub>CPP</sub> +50 | ns   | Internal shift clock mode Round operation output pin: CL = 50 pF |  |

|                                   |                   | SCS3,<br>SCS40 to SCS43                                                                                                                |            | 3tсрр-300             | 3t <sub>CPP</sub> +50 |      |                                                                  |  |

<sup>\*1:</sup> tcssu = SCSTR:CSSU7-0 × Serial chip select timing operating clock

Regardless of the deselect time setting, once after the serial chip select pin becomes inactive, it will take at least five peripheral bus clock cycles to be active again

Please see the hardware manual for details of above-mentioned \*1,\*2, and \*3.

<sup>\*2:</sup> tcshd = SCSTR:CSHD7-0 x Serial chip select timing operating clock

<sup>\*3:</sup> tcsps = SCSTR:CSDS15-0 × Serial chip select timing operating clock

| Parameter                          | Symbol             | Pin Name                | Valu      | е   | Unit  | Remarks                                                                                                                                                                                                                                                                                                     |

|------------------------------------|--------------------|-------------------------|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rarameter                          | Symbol             | FIII Name               | Min       | Max | Oiiit | Remarks                                                                                                                                                                                                                                                                                                     |

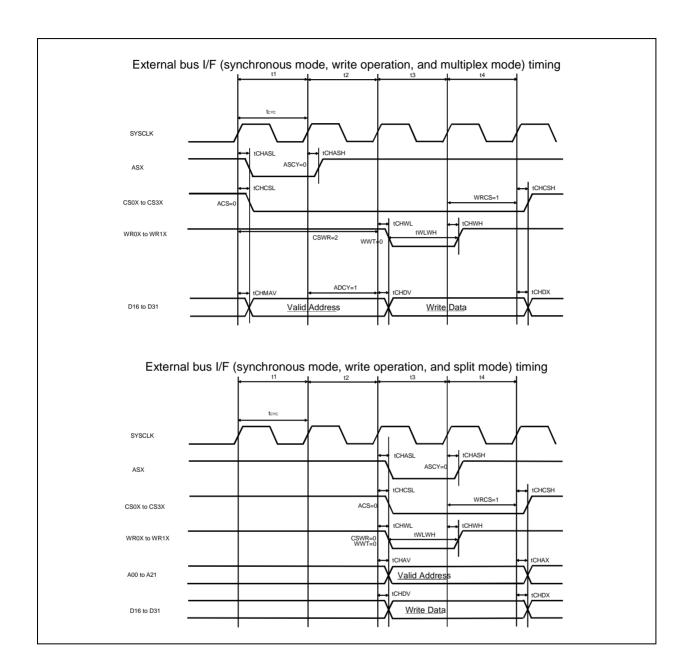

| WRnX delay<br>time                 | tснwL,<br>tснwн    | SYSCLK<br>WR0X,<br>WR1X | 0.5       | 18  | ns    |                                                                                                                                                                                                                                                                                                             |

| WRnX<br>minimum pulse              | twtwh              | WR0X,<br>WR1X           | tcyc - 10 | -   | ns    | WWT = 0 *2                                                                                                                                                                                                                                                                                                  |

| SYSCLK↑→ data output time          | tсноv              | SYSCLK                  | 0.5       | 18  | ns    |                                                                                                                                                                                                                                                                                                             |

| SYSCLK↑→<br>data hold time         | tchdx              | D16 to D31              | -         | 18  | ns    | Set WRCS to 1 or more.                                                                                                                                                                                                                                                                                      |

| SYSCLK↑→<br>address output<br>time | t <sub>CHMAV</sub> |                         | 0.5       | 18  | ns    |                                                                                                                                                                                                                                                                                                             |

| SYSCLK↑→ address hold time         | tснмах             | SYSCLK<br>D16 to D31    | -         | 18  | ns    | In multiplex mode, set as follows:  □ Set CSWR and CSRD to 2 or more.  □ ASCY must satisfy the following conditions because of setting ADCY > ASCY and protocol violation prevention.  ADCY +1 ≤ ACS + CSRD ADCY +1 ≤ ACS + CSWR ASCY +1 ≤ ACS + CSRD ASCY +1 ≤ ACS + CSWR See Hardware Manual for details. |

<sup>\*1:</sup> Please use it with external load capacity 12 pF or less for VCC =  $3.3 \text{ V} \pm 0.3 \text{ V}$  (40 MHz operation).

<sup>\*2:</sup> If the bus is expanded by automatic wait insertion or RDY input, add time (t<sub>CYC</sub> × the number of expanded cycles) to the rated value.

(11) External bus I/F (asynchronous mode) timing

(T<sub>A</sub>: -40 °C to +105 °C,  $V_{CC} = AV_{CC} = 5.0 \text{ V} \pm 10 \text{ %/V}_{CC} = AV_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{SS} = AV_{SS} = 0.0 \text{ V}$ )

(external load capacitance 50pF)

| Donomotor                   | Comple al | Din Nama           | Value                 | •                     | l lmit | Domonto                                                                                                                                                                                                                                                                                                     |

|-----------------------------|-----------|--------------------|-----------------------|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                   | Symbol    | Pin Name           | Min                   | Max                   | Unit   | Remarks                                                                                                                                                                                                                                                                                                     |

| 0 1 1                       |           | 0)/0011/           | 25                    |                       |        | Vcc = 5.0 V ± 10 %*1                                                                                                                                                                                                                                                                                        |

| Cycle time                  | tcyc      | SYSCLK             | 31.25                 | -                     | ns     | Vcc = 3.3 V ± 0.3 V                                                                                                                                                                                                                                                                                         |

| Address setup → RDX↑time    | tasrh     | RDX                | 2×tcyc - 12           | 2×tcyc + 12           | ns     | RWT = 1,<br>set RWT to 1 or more.*2                                                                                                                                                                                                                                                                         |

| RDX↑→<br>Address hold       | trнан     | A00 to A21         | tcyc - 12             | tcyc + 12             | ns     | Set RDCS to 1 or more.                                                                                                                                                                                                                                                                                      |

| Data setup→<br>RDX↑time     | tdsrн     | RDX                | 18 +<br>tcyc          | -                     | ns     | RWT = 1, set RWT to 1 or more.                                                                                                                                                                                                                                                                              |

| RDX↑→<br>Data hold          | trнон     | D16 to D31         | 0                     | -                     | ns     |                                                                                                                                                                                                                                                                                                             |

| Address setup→<br>WRnX↑time | taswh     | WR0X to            | tcyc - 12             | tcyc + 12             | ns     | WWT = 0 *2                                                                                                                                                                                                                                                                                                  |

| WRnX↑→<br>Address hold      | twhah     | WR1X<br>A00 to A21 | t <sub>CYC</sub> - 12 | t <sub>CYC</sub> + 12 | ns     | Set WRCS to 1 or more.                                                                                                                                                                                                                                                                                      |

| Data setup→<br>WRnX↑time    | tоswн     | WR0X to            | teye - 16             | tcyc + 16             | ns     | WWT = 0 *2                                                                                                                                                                                                                                                                                                  |

| WRnX↑→<br>Data hold         | twhoh     | WR1X<br>D16 to D31 | t <sub>CYC</sub> - 16 | t <sub>CYC</sub> + 16 | ns     | Set WRCS to 1 or more.                                                                                                                                                                                                                                                                                      |

| Address setup →<br>ASX†time | tmasash   |                    | tcyc-16               | tcyc+ 16              | ns     | ASCY = 0                                                                                                                                                                                                                                                                                                    |

| ASX↑→Address<br>hold        | tmashah   | ASX<br>D16 to D31  | tcyc-16               | tcyc + 16             | ns     | In multiplex mode, set as follows:  □ Set CSWR and CSRD to 2 or more.  □ ASCY must satisfy the following conditions because of setting ADCY > ASCY and protocol violation prevention.  ADCY +1 ≤ ACS + CSRD ADCY +1 ≤ ACS + CSWR ASCY +1 ≤ ACS + CSWR ASCY +1 ≤ ACS + CSWR See Hardware Manual for details. |

<sup>\*1:</sup> Please use it with external load capacity 12 pF or less for VCC =  $3.3 \text{ V} \pm 0.3 \text{ V}$  (40 MHz operation).

<sup>\*2:</sup> If the bus is expanded by automatic wait insertion or RDY input, add time (tcyc x the number of expanded cycles) to the rated value.

| Part Number    | Sub Clock | CSV Initial Value | LVD Initial Value | Package*       |

|----------------|-----------|-------------------|-------------------|----------------|

| MB91F526FWEPMC | Yes       | ON                | ON                |                |

| MB91F526FJEPMC |           | OFF               | ON                |                |

| MB91F525FWEPMC |           | ON                | ON                |                |

| MB91F525FJEPMC |           | OFF               | ON                |                |

| MB91F524FWEPMC |           | ON                | ON                |                |

| MB91F524FJEPMC |           | OFF               | ON                |                |

| MB91F523FWEPMC |           | ON                | ON                |                |

| MB91F523FJEPMC |           | OFF               | ON                |                |

| MB91F522FWEPMC |           | ON                | ON                |                |

| MB91F522FJEPMC |           | OFF               | ON                | LQI · 100 pin, |

| MB91F526FSEPMC | None      | ON                | ON                | Plastic        |

| MB91F526FHEPMC |           | OFF               | ON                |                |

| MB91F525FSEPMC |           | ON                | ON                |                |

| MB91F525FHEPMC |           | OFF               | ON                |                |

| MB91F524FSEPMC |           | ON                | ON                |                |

| MB91F524FHEPMC |           | OFF               | ON                |                |

| MB91F523FSEPMC |           | ON                | ON                |                |

| MB91F523FHEPMC |           | OFF               | ON                |                |

| MB91F522FSEPMC |           | ON                | ON                |                |

| MB91F522FHEPMC |           | OFF               | ON                |                |

| MB91F526DWEPMC | Yes       | ON                | ON                |                |

| MB91F526DJEPMC |           | OFF               | ON                |                |

| MB91F525DWEPMC |           | ON                | ON                |                |

| MB91F525DJEPMC |           | OFF               | ON                |                |

| MB91F524DWEPMC |           | ON                | ON                |                |

| MB91F524DJEPMC |           | OFF               | ON                |                |

| MB91F523DWEPMC |           | ON                | ON                |                |

| MB91F523DJEPMC |           | OFF               | ON                |                |

| MB91F522DWEPMC |           | ON                | ON                |                |

| MB91F522DJEPMC |           | OFF               | ON                | LQH ⋅ 80 pin,  |

| MB91F526DSEPMC | None      | ON                | ON                | Plastic        |

| MB91F526DHEPMC |           | OFF               | ON                |                |

| MB91F525DSEPMC |           | ON                | ON                |                |

| MB91F525DHEPMC |           | OFF               | ON                |                |

| MB91F524DSEPMC |           | ON                | ON                |                |

| MB91F524DHEPMC |           | OFF               | ON                |                |

| MB91F523DSEPMC |           | ON                | ON                |                |

| MB91F523DHEPMC |           | OFF               | ON                |                |

| MB91F522DSEPMC |           | ON                | ON                |                |

| MB91F522DHEPMC |           | OFF               | ON                |                |

| Page | Section                   | Change Results    |

|------|---------------------------|-------------------|

| 14   | ■Pin Assignment MB91F52xD | - Right side    0 |

| Page   | Section          | Change Results           |          |       |       |     |     |                                        |

|--------|------------------|--------------------------|----------|-------|-------|-----|-----|----------------------------------------|

|        |                  | (Continued)<br>(Correct) |          |       |       |     |     |                                        |

|        |                  | (3377)                   | /        | Pin   | no.   |     |     | Pin                                    |

|        |                  | 64                       | 80       | 100   | 120   | 144 | 176 | Name                                   |

|        |                  |                          |          |       |       |     |     | P047                                   |

|        |                  |                          |          |       |       |     |     | A17 *2, *3, *4, *5                     |

|        |                  | 15 *1                    | 5*1 18*1 | 23*1  | 27 *1 | 30  | 37  | AN45                                   |

|        |                  | 15                       |          |       |       |     |     | TRG8_0                                 |

|        |                  |                          |          |       |       |     |     | TIN3_2                                 |

|        |                  |                          |          |       |       |     |     | SOT0_1                                 |

|        |                  | -                        | _        | -     | -     | _   | 38  | P177                                   |

|        |                  |                          |          |       |       |     |     | TRG11_0                                |

|        |                  |                          | -        | -     | 28 *1 | 31  |     | P050                                   |

|        |                  | -                        |          |       |       |     | 39  | A18 <sup>*5</sup><br>TRG5_1            |

|        |                  |                          |          |       |       |     |     | PPG33_0                                |

|        |                  |                          |          |       |       |     |     | P051                                   |

|        |                  | -                        | -        | -     | -     | 32  | 40  | A19                                    |

|        |                  |                          |          |       |       |     |     | TRG9_0                                 |

|        |                  |                          |          |       |       |     |     | P052                                   |

|        |                  | _                        | _        | _     | _     | 33  | 41  | A20                                    |

|        |                  |                          | _        | _     |       | 33  | 71  | PPG34_0                                |

| 23, 24 | ■PIN Description |                          |          |       |       |     |     | INT14_0                                |

| _0,    |                  |                          | 19*1     | 24 *1 | 29 *1 | 34  |     | P053<br>A21 *2, *3, *4, *5             |

|        |                  |                          |          |       |       |     | 42  | AN44                                   |

|        |                  | 16 *1                    |          |       |       |     |     | PPG35_0                                |

|        |                  |                          |          |       |       |     |     | INT14_1                                |

|        |                  |                          |          |       |       |     |     | SCK0_1                                 |

|        |                  |                          |          |       |       |     |     | P054                                   |

|        |                  | -                        | -        | -     | -     | 35  | 43  | SYSCLK                                 |

|        |                  |                          |          |       |       |     |     | PPG36_0                                |

|        |                  | 17*1                     | 22*1     | 27 *1 | 32 *1 | 38  | 46  | P055<br>CS2X <sup>*2, *3, *4, *5</sup> |

|        |                  |                          |          |       |       |     |     | SIN10_0                                |

|        |                  |                          |          |       |       |     |     | AN43                                   |

|        |                  |                          |          |       |       |     |     | PPG37_0                                |

|        |                  |                          |          |       |       |     |     | TIN4_1                                 |

|        |                  |                          |          |       |       |     |     |                                        |

|        |                  |                          |          | -     |       |     | 49  | P056                                   |

|        |                  | -                        |          |       | 33*1  |     |     | CS3X <sup>*5</sup>                     |

|        |                  |                          |          |       |       | 39  |     | ICU9_0                                 |

|        |                  |                          | -        |       |       |     |     | PPG0_1<br>ICU0_1                       |

|        |                  |                          |          |       |       |     |     | TIN5_1                                 |

|        |                  |                          |          |       |       |     |     | DTTI_2                                 |

|        |                  |                          | <u> </u> | l .   | l .   | I   | I   | <del>_</del>                           |

| Deriv | Coatles                 | Change Describe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Page  | Section                 | Change Results  "42" is deleted as shown below from the interrunt factor in Interrunt vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 131   | ■Interrupt Vector Table | "42" is deleted as shown below from the interrupt factor in Interrupt vector 120pin.  (Error)  PPG2/3/12/13/22 /23/32/33/42/43  16-bit free-run timer 2 (0 detection) / (compare clear)    Compare clear   Com |  |  |  |  |  |

|       |                         | (compare disal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|       |                         | (Correct)  PPG2/3/12/13/22 /23/32/33/43  16-bit free-run timer 2 (0 detection) / (compare clear)  PFG2/3/12/13/22  41 29 ICR 358 FF58 25  H H FF58 H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |