Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | FR81S                                                                             |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, CSIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 76                                                                                |

| Program Memory Size        | 576KB (576K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 64K x 8                                                                           |

| RAM Size                   | 72K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                       |

| Data Converters            | A/D 37x12b; D/A 2x8b                                                              |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP                                                                          |

| Supplier Device Package    | 100-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f524fhbpmc-gs-f4e1 |

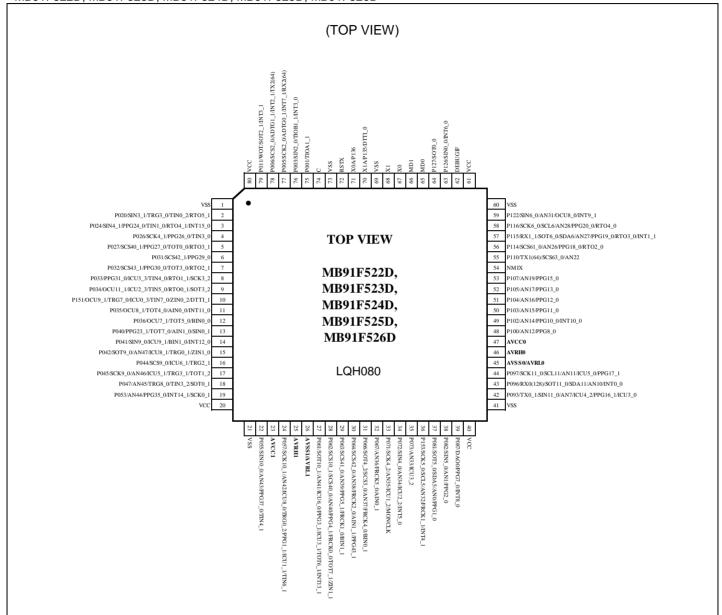

# MB91F52xD

MB91F522D, MB91F523D, MB91F524D, MB91F525D, MB91F526D

<sup>\*</sup> In a single clock product, pin 70 and pin 71 are the general-purpose ports.

|          |    | Pir   | No.              |     |     | Pin Name            | Polarity | I/O<br>Circuit | Function*9                                        |                      |

|----------|----|-------|------------------|-----|-----|---------------------|----------|----------------|---------------------------------------------------|----------------------|

| 64       | 80 | 100   | 120              | 144 | 176 |                     |          | types*8        |                                                   |                      |

|          |    |       |                  |     |     | P053                | -        |                | General-purpose I/O port                          |                      |

|          |    |       |                  |     |     | A21 *2, *3, *4, *5  | -        |                | External bus/Address bit21 output                 |                      |

| 16       | 19 | 04*1  | 20.*1            | 24  | 40  | AN44                | -        |                | ADC analog 44 input                               |                      |

| *1       | *1 | 24 *1 | 29 *1            | 34  | 34  | 42                  | PPG35_0  | -              | В                                                 | PPG ch.35 output (0) |

|          |    |       |                  |     |     | INT14_1             | -        |                | INT14 External interrupt input (1)                |                      |

|          |    |       |                  |     |     | SCK0_1              | -        |                | Multi-function serial ch.0 clock I/O (1)          |                      |

|          |    |       |                  |     |     | P054                | -        |                | General-purpose I/O port                          |                      |

| -        | -  | -     | -                | 35  | 43  | SYSCLK              | -        | Α              | External bus/System clock output                  |                      |

|          |    |       |                  |     |     | PPG36_0             | -        |                | PPG ch.36 output (0)                              |                      |

|          |    |       |                  |     |     | P055                | -        |                | General-purpose I/O port                          |                      |

|          |    |       |                  |     |     | CS2X *2, *3, *4, *5 | -        |                | External bus chip select 2 output                 |                      |

| 17       | 22 | 07.*1 | 00 *1            | 00  | 40  | SIN10_0             | -        |                | Multi-function serial ch.10 serial data input (0) |                      |

| *1       | *1 | 27 *1 | 32 *1            | 38  | 46  | AN43                | -        | G              | ADC analog 43 input                               |                      |

|          |    |       |                  |     |     | PPG37_0             | -        |                | PPG ch.37 output (0)                              |                      |

|          |    |       |                  |     |     | TIN4_1              | -        |                | Reload timer ch.4 event input (1)                 |                      |

|          |    |       |                  |     | 47  | P180                | -        |                | General-purpose I/O port                          |                      |

| -        | -  | -     | -                | -   | 47  | PPG40_0             | -        | Α              | PPG ch.40 output (0)                              |                      |

|          |    |       |                  |     | 40  | P181                | -        |                | General-purpose I/O port                          |                      |

| -        | -  | -     | -                | -   | 48  | PPG41_0             | -        | Α              | PPG ch.41 output (0)                              |                      |

|          |    |       |                  |     |     | P056                | -        |                | General-purpose I/O port                          |                      |

|          |    |       |                  |     |     | CS3X <sup>*5</sup>  | -        |                | External bus chip select 3 output                 |                      |

|          |    |       |                  |     |     | ICU9_0              | -        |                | Input capture ch.9 input (0)                      |                      |

| -        | -  | -     | 33 *1            | 39  | 49  | PPG0_1              | -        | Α              | PPG ch.0 output (1)                               |                      |

|          |    |       |                  |     |     | ICU0_1              | -        |                | Input capture ch.0 input (1)                      |                      |

|          |    |       |                  |     |     | TIN5_1              | -        |                | Reload timer ch.5 event input (1)                 |                      |

|          |    |       |                  |     |     | DTTI_2              | -        |                | Waveform generator ch.0-ch.5 input pin (2)        |                      |

|          |    |       |                  |     |     | P057                | -        |                | General-purpose I/O port                          |                      |

|          |    |       |                  |     |     | RDY *2, *3, *4, *5  | -        |                | External bus/Ready input (0)                      |                      |

|          |    |       |                  |     |     | SCK10_1             | -        |                | Multi-function serial ch.10 clock I/O (1)         |                      |

|          |    |       |                  |     |     | AN42                | -        |                | ADC analog 42 input                               |                      |

| 19<br>*1 | 24 | 29 *1 | 35 <sup>*1</sup> | 41  | 51  | ICU8_0              | -        | G              | Input capture ch.8 input (0)                      |                      |

|          |    |       |                  |     |     | TRG0_2              | -        |                | PPG trigger 0 input (2)                           |                      |

|          |    |       |                  |     |     | PPG1_1              | -        |                | PPG ch.1 output (1)                               |                      |

|          |    |       |                  |     |     | ICU1_1              | -        |                | Input capture ch.1 input (1)                      |                      |

|          |    |       |                  |     |     | TIN6_1              | -        |                | Reload timer ch.6 event input (1)                 |                      |

|          |    |       |                  |     | _   | P142                | -        |                | General-purpose I/O port                          |                      |

|          |    |       |                  |     |     | SCK10_0/            |          |                | Multi-function serial ch.10 clock I/O (0)/        |                      |

| -        | -  | -     | -                | 44  | 54  | SCL10               | _        | F              | I <sup>2</sup> C bus serial clock I/O             |                      |

|          |    |       |                  |     |     | PPG38_0             | -        | 1              | PPG ch.38 output (0)                              |                      |

|          |    |       |                  |     |     | TIN7_1              | -        |                | Reload timer ch.7 event input (1)                 |                      |

# ■ Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### ■ Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

# ■ Precautions Related to Usage of Devices

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

**CAUTION:** Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

#### 2. Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress's recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### ■ Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

#### ■ Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. Cypress recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with Cypress ranking of recommended conditions.

# ■ Lead-Free Packaging

**CAUTION:** When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

# ■ Storage of Semiconductor Devices

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause

Document Number: 002-04662 Rev. \*F

absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (1) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- (2) Use dry boxes for product storage. Products should be stored below 70 % relative humidity, and at temperatures between 5 °C and 30 °C.

- When you open Dry Package that recommends humidity 40 % to 70 % relative humidity.

- (3) When necessary, Cypress packages semiconductor devices in highly moisture-resistant aluminum laminate bags, with a silica gel desiccant. Devices should be sealed in their aluminum laminate bags for storage.

- (4) Avoid storing packages where they are exposed to corrosive gases or high levels of dust.

#### ■ Baking

Packages that have absorbed moisture may be de-moisturized by baking (heat drying). Follow the Cypress recommended conditions for baking.

Condition: 125 °C/24 h

# ■ Static Electricity

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- (1) Maintain relative humidity in the working environment between 40 % and 70 %. Use of an apparatus for ion generation may be needed to remove electricity.

- (2) Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- (3) Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1 MΩ).

- Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- (4) Ground all fixtures and instruments, or protect with anti-static measures.

- (5) Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

- 3. Precautions for Use Environment

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above.

For reliable performance, do the following:

#### (1) Humidity

Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

(2) Discharge of Static Electricity

When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation. In such cases, use anti-static measures or processing to prevent discharges.

- (3) Corrosive Gases, Dust, or Oil

- Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

- (4) Radiation, Including Cosmic Radiation

- Most devices are not designed for environments involving exposure to radiation or cosmic radiation. Users should provide shielding as appropriate.

- (5) Smoke, Flame

# 6. Handling Devices

This section explains the latch-up prevention and pin processing.

#### ■ For latch-up prevention

If a voltage higher than VCC or a voltage lower than VSS is applied to an I/O pin, or if a voltage exceeding the ratings is applied between VCC and VSS pins, a latch-up may occur in CMOS IC. If the latch-up occurs, the power supply current increases excessively and device elements may be damaged by heat. Take care to prevent any voltage from exceeding the maximum ratings in device application.

Also, the analog power supply (AVCC, AVRH) and analog input must not be exceed the digital power supply (VCC) when the power supply to the analog system is turned on or off.

In the correct power-on sequence of the microcontroller, turn on the digital power supply (VCC) and analog power supplies (AVCC, AVRH) simultaneously. Or, turn on the digital power supply (VCC), and then turn on analog power supplies (AVCC, AVRH).

#### ■ Treatment of unused pins

If unused input pins are left open, they may cause a permanent damage to the device due to malfunction or latch-up. Connect at least a  $2 \text{ k}\Omega$  resistor to each of the unused pins for pull-up or pull-down processing.

Also, if I/O pins are not used, they must be set to the output state for releasing or they must be set to the input state and treated in the same way as for the input pins.

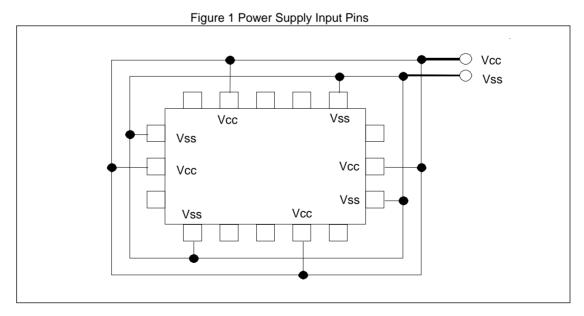

# ■ Power supply pins

The device is designed to ensure that if the device contains multiple VCC or VSS pins, the pins that should be at the same potential are interconnected to prevent latch-up or other malfunctions. Further, connect these pins to an external power supply or ground to reduce unwanted radiation, prevent strobe signals from malfunctioning due to a raised ground level, and fulfill the total output current standard, etc. As shown in figure 1, all Vss power supply pins must be treated in the similar way. If multiple Vcc or Vss systems are connected, the device cannot operate correctly even within the guaranteed operating range.

The power supply pins should be connected to VCC and VSS pins of this device at the low impedance from the power supply source.

In the area close to this device, a ceramic capacitor having the capacitance larger than the capacitor of C pin is recommended to use as a bypass capacitor between VCC and VSS pins.

Document Number: 002-04662 Rev. \*F

| A al alma = =       |              | Address offset val | ue / Register name                      |                  | District                  |

|---------------------|--------------|--------------------|-----------------------------------------|------------------|---------------------------|

| Address             | +0           | +1                 | +2                                      | +3               | Block                     |

| 000258н             |              |                    |                                         |                  |                           |

| to                  | _            | _                  | _                                       | _                | Reserved                  |

| 0002C0 <sub>Н</sub> |              |                    |                                         |                  |                           |

| 0002С4н             |              |                    |                                         |                  |                           |

| to                  | _            | _                  | _                                       | _                | Reserved                  |

| 0002FCн             |              |                    |                                         |                  |                           |

| 000300н             |              |                    |                                         |                  |                           |

| to                  | _            | _                  | _                                       | _                | Reserved                  |

| 00030Сн             |              |                    | MDUCD                                   | [DAA] H          |                           |

| 000310н             | _            | _                  |                                         | [R/W] H<br>00100 |                           |

| 000314н             |              |                    |                                         |                  |                           |

| 000314H             | <del>_</del> |                    | <u> </u>                                | _                |                           |

| 00031Cн             |              | _                  | _                                       |                  |                           |

|                     |              | DPVAF              | R [R] W                                 |                  |                           |

| 000320н             |              | XXXXXXXX XXXXXXXX  |                                         | ΧX               |                           |

|                     |              |                    |                                         | [R/W] H          |                           |

| 000324н             | _            | _                  |                                         | 000000           |                           |

| 22222               |              | DEAR               | [R] W                                   |                  |                           |

| 000328н             |              | XXXXXXXX XXXXXXXX  |                                         | ΧX               |                           |

| 000000              |              |                    | DESR                                    | [R/W] H          |                           |

| 00032Сн             | _            | _                  | C                                       | 00000            |                           |

| 000330н             |              | PABR0              | [R/W] W                                 |                  |                           |

| 000330H             |              | XXXXXXXX XXXXXXX   | XXXXXXXX XXXXX                          | 000              |                           |

| 000334н             | _            | _                  |                                         | [R/W] H          |                           |

| 00000 111           |              |                    |                                         | 000000           |                           |

| 000338н             |              |                    | [R/W] W                                 |                  |                           |

|                     |              | XXXXXXXX XXXXXXX   |                                         |                  | MPU [S]                   |

| 00033Сн             | _            | _                  |                                         | [R/W] H          | (Only CPU core can access |

|                     |              | DARRO              |                                         | 000000           | this area)                |

| 000340н             |              | XXXXXXXX XXXXXXXX  | [R/W] W                                 | 000              |                           |

|                     |              |                    |                                         | [R/W] H          |                           |

| 000344н             | _            | _                  |                                         | 000000           |                           |

|                     |              | PARR3              | [R/W] W                                 | 00000 0          |                           |

| 000348н             |              | XXXXXXXX XXXXXXX   |                                         | 000              |                           |

|                     |              |                    |                                         | [R/W] H          |                           |

| 00034Сн             | _            | _                  |                                         | 000000           |                           |

| 000050              |              | PABR4              | [R/W] W                                 |                  |                           |

| 000350н             |              | XXXXXXXX XXXXXXX   | = = = = = = = = = = = = = = = = = = = = | 000              |                           |

| 000354н             |              |                    | PACR4                                   | [R/W] H          |                           |

| 000354H             | <u>-</u>     | _                  | 000000-0                                | 000000           |                           |

| 000358н             |              |                    | [R/W] W                                 |                  |                           |

| 300000H             |              | XXXXXXXX XXXXXXX   |                                         |                  | _                         |

| 00035Сн             | _            | _                  |                                         | [R/W] H          |                           |

| 555550п             |              |                    | •                                       | 000000           | _                         |

| 000360н             |              |                    | [R/W] W                                 |                  |                           |

|                     |              | XXXXXXXX XXXXXXX   |                                         |                  | _                         |

| 000364н             | _            | _                  |                                         | [R/W] H          |                           |

| .,                  |              |                    | 000000-0                                | 000000           |                           |

| Address                                          |                             | Address offset val                               | ue / Register name              |                                   | Block                                                                     |

|--------------------------------------------------|-----------------------------|--------------------------------------------------|---------------------------------|-----------------------------------|---------------------------------------------------------------------------|

| Audress                                          | +0                          | +1                                               | +2                              | +3                                | DIOCK                                                                     |

| 000F68 <sub>н</sub>                              | XX                          | MSCY6                                            |                                 | (XX                               | Input<br>Capture 6,7                                                      |

| 000F6Сн                                          |                             | MSCY7                                            | [R] H,W                         |                                   | Cycle measurement data register 67                                        |

| 000F70 <sub>н</sub>                              | RCRH0 [W] H,W<br>XXXXXXXX   | RCRL0 [W] B,H,W                                  | UDCRH0 [R] H,W<br>00000000      | UDCRL0 [R] B,H,W<br>00000000      | - J                                                                       |

| 000F74н                                          | CCR0 [F                     | R/W] B,H<br>-0001000                             | _                               | CSR0 [R/W] B<br>00000000          | Up/Down Counter 0                                                         |

| 000F78н<br>to<br>000F7Сн                         | _                           | _                                                | _                               | _                                 | Reserved                                                                  |

| 000F80 <sub>Н</sub>                              | RCRH1 [W] H,W<br>XXXXXXXX   | RCRL1 [W] B,H,W<br>XXXXXXXX                      | UDCRH1 [R] H,W<br>00000000      | UDCRL1 [R] B,H,W<br>00000000      | Up/Down Counter 1                                                         |

| 000F84н                                          | -                           | R/W] B,H<br>-0001000                             | _                               | CSR1 [R/W] B<br>00000000          | op/Bown counter 1                                                         |

| 000F88н                                          | _                           | _                                                | MSCH45 [R]<br>B,H,W<br>00000000 | MSCL45 [R/W]<br>B,H,W<br>00       | Input Capture 4,5 32-bit ICU Cycle and pulse width measurement control 45 |

| 000F8Сн                                          | _                           | _                                                | MSCH67 [R]<br>B,H,W<br>00000000 | MSCL67 [R/W]<br>B,H,W<br>00       | Input Capture 6,7 32-bit ICU Cycle and pulse width measurement control 67 |

| 000F90н                                          |                             | OCCP10                                           |                                 |                                   | Output 0-7-7-40 44                                                        |

| 000F94 <sub>н</sub>                              |                             | 00000000 00000000<br>OCCP11<br>00000000 00000000 | [R/W] W                         |                                   | Output Compare 10,11<br>32-bit OCU                                        |

| 000F98н                                          | _                           | _                                                | OCSH1011 [R/W]<br>B,H,W<br>0-00 | OCSL1011 [R/W]<br>B,H,W<br>000000 | Output Compare 10,11<br>32-bit OCU                                        |

| 000F9Сн                                          | _                           | _                                                | _                               | OCLS1011 [R/W]<br>B,H,W<br>0000   | OCU1011<br>Output level control register                                  |

| 000FA0н                                          |                             | CPCLR5                                           | - Table                         |                                   |                                                                           |

| 000FA4н                                          |                             | TCDT5  <br>00000000 00000000                     |                                 |                                   | Free-run Timer 5                                                          |

| 000FA8 <sub>Н</sub>                              | TCCSH5<br>[R/W]B,H,W<br>000 | TCCSL5 [R/W]B,H,W<br>-1-00000                    |                                 | _                                 | 32-bit FRT                                                                |

| 000FAC <sub>H</sub><br>to<br>000FCC <sub>H</sub> | _                           | _                                                | _                               | _                                 | Reserved                                                                  |

| 000ГООН                                          |                             | IPCP4                                            |                                 | 00/                               |                                                                           |

| 000FD4 <sub>H</sub>                              |                             | XXXXXX XXXXXXXX<br>IPCP5                         | [R] W                           |                                   | Input                                                                     |

| 000FD8н                                          | XX                          |                                                  |                                 | ICS45 [R/W] B,H,W<br>00000000     | Capture 4,5<br>32-bit ICU                                                 |

| A al al ma a a |                                          | Address offset val                       | ue / Register name                       |                                                                | Disale                                                                               |

|----------------|------------------------------------------|------------------------------------------|------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Address        | +0                                       | +1                                       | +2                                       | +3                                                             | Block                                                                                |

| 001884н        | BGR7[R/<br>00000000                      | -                                        | — /(ISMK7)[R/W]<br>B,H,W<br>*2           | — /(ISBA7)[R/W]<br>B,H,W<br>*2                                 |                                                                                      |

| 001888н        | FCR17[R/W]<br>B,H,W<br>00100             | FCR07[R/W]<br>B,H,W<br>-0000000          | _                                        | R/W] B,H,W<br>00000000                                         | Multi-UART7                                                                          |

| 00188Сн        | FTICR7[R<br>00000000                     | W] B,H,W<br>00000000                     | _                                        | _                                                              |                                                                                      |

| 001890н        | SCR8/(IBCR8) [R/W]<br>B,H,W<br>000000    | SMR8[R/W] B,H,W<br>000-00-0              | SSR8[R/W] B,H,W<br>0-000011              | ESCR8/(IBSR8)[R/W<br>] B,H,W<br>00000000                       |                                                                                      |

| 001894н        | — /(RDR18/(TDF                           |                                          | ·                                        | 08)[R/W] B,H,W<br>0000000 *1                                   | Multi-UART8                                                                          |

| 001898н        | SACSR8[R<br>0000 (                       | 2/W] B,H,W<br>00000000                   | -                                        | R] B,H,W<br>00000000                                           | *1: Byte access is possible                                                          |

| 00189Сн        | STMCR8[F<br>00000000                     | R/W] B,H,W<br>00000000                   | ,                                        | UR8)[R/W] B,H,W<br>*3 *4                                       | only for access to lower 8 bits.                                                     |

| 0018А0н        | — /(SCSTR38)/<br>(LAMSR8)<br>[R/W] B,H,W | — /(SCSTR28)/<br>(LAMCR8)<br>[R/W] B,H,W | — /(SCSTR18)/<br>(SFLR18)<br>[R/W] B,H,W | — /(SCSTR08)/<br>(SFLR08)<br>[R/W] B,H,W                       | *2: Reserved because I <sup>2</sup> C<br>mode is not set immediately<br>after reset. |

| 0018А4н        | _                                        | — /(SCSFR28)<br>[R/W] B,H,W              | — /(SCSFR18)<br>[R/W] B,H,W              | — /(SCSFR08)<br>[R/W] B,H,W                                    | *3: Reserved because CSIO mode is not set immediately                                |

| 0018А8н        | —/(TBYTE38)/<br>(LAMESR8)<br>[R/W] B,H,W | —/(TBYTE28)/<br>(LAMERT8)<br>[R/W] B,H,W | —/(TBYTE18)/<br>(LAMIER8)<br>[R/W] B,H,W | TBYTE08/(LAMRID8)<br>/<br>(LAMTID8)<br>[R/W] B,H,W<br>00000000 | after reset.  *4: Reserved because LIN2.1 mode is not set immediately after reset.   |

| 0018АСн        | BGR8[R<br>00000000                       | /W] H,W<br>00000000                      | — /(ISMK8)[R/W]<br>B,H,W<br>*2           | — /(ISBA8)[R/W]<br>B,H,W<br>*2                                 |                                                                                      |

| 0018В0н        | FCR18[R/W]<br>B,H,W<br>00100             | FCR08[R/W]<br>B,H,W<br>-0000000          | -                                        | R/W] B,H,W<br>00000000                                         | Multi-UART8                                                                          |

| 0018В4н        | FTICR8[R<br>00000000                     | •                                        | _                                        | _                                                              |                                                                                      |

|                               | Interrupt | Number          | Interrupt |                  | Default         |    |

|-------------------------------|-----------|-----------------|-----------|------------------|-----------------|----|

| Interrupt Factor              | Decimal   | Hexa<br>Decimal | l evel    | Offset           | Address for TBR | RN |

|                               | 66        | 42              |           | 2F4 <sub>H</sub> | 000FFEF4н       |    |

| Used with the INT instruction | [         |                 | -         |                  | 1               | -  |

|                               | 255       | FF              |           | 000н             | 000FFC00н       |    |

**Note:** It does not support a DMA transfer request caused by an interrupt generated from a peripheral to which no RN (Resource Number) is assigned.

- \*1: It does not support a DMA transfer by the status of the multi-function serial interface and I<sup>2</sup>C reception.

- \*2: Reload timer ch.4 to ch.7 do not support a DMA transfer by the interrupt.

- \*3: PPG ch.24 to ch.47 do not support a DMA transfer by the interrupt.

- \*4: The clock calibration unit does not support a DMA transfer by the interrupt.

- \*5: 32-bit Free-run timer ch.3, ch.4 and ch.5 do not support a DMA transfer by the interrupt.

- \*6: There is no resource corresponding to the interrupt level.

- \*7: It does not support a DMA transfer by the external low-voltage detection interrupt.

- \*8: REALOS is a trademark of Cypress.

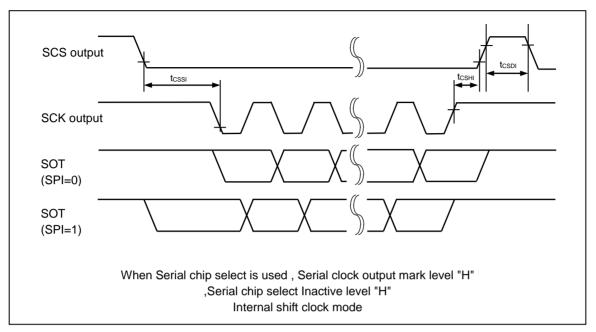

(4-1-6) Bit setting: SMR:MD2 = 0, SMR:MD1 = 1, SMR:MD0 = 0,

When Serial chip select is used: SCSCR:CSEN = 1,

Serial clock output mark level "L" : SMR,SCSFR:SCINV = 1, Serial chip select Inactive level "H" : SCSCR,SCSFR:CSLVL = 1

$(T_A:-40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, V_{CC} = AV_{CC} = 5.0 \, V \pm 10 \, \%/V_{CC} = AV_{CC} = 3.3 \, V \pm 0.3 \, V, \, V_{SS} = AV_{SS} = 0.0 \, V)$

|                         |                   | Din Name                                                                                                                |            | Val                   |                        | Unit | Domouleo                                                      |

|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|------------------------|------|---------------------------------------------------------------|

| Parameter               | Symbol            | Pin Name                                                                                                                | Conditions | Min                   | Max                    | Onit | Remarks                                                       |

| SCS↓→SCK↑<br>setup time | tcssı             | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 |            | tcssu-50              | tcssu+0 *1             | ns   |                                                               |

|                         |                   | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                   |            | t <sub>CSSU</sub> -50 | t <sub>CSSU</sub> +300 | ns   |                                                               |

| SCK↓→SCS↑<br>hold time  | t <sub>CSHI</sub> | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 | -          | tcshd-10              | tcshp+50 *2            | ns   | Internal shift clock mode output pin : C <sub>L</sub> = 50 pF |

|                         |                   | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                   |            | tcshd-300             | tcshp+50 *2            | ns   |                                                               |

| SCS<br>deselect time    | tcspi             | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11              |            | t <sub>CSDS</sub> -50 | tcsps+50               | ns   |                                                               |

| Damanastan                        | 0                 | Dia Nama                                                                                                                               | 0          | Va                    | lue                   | I I mit | Damaria                                                          |

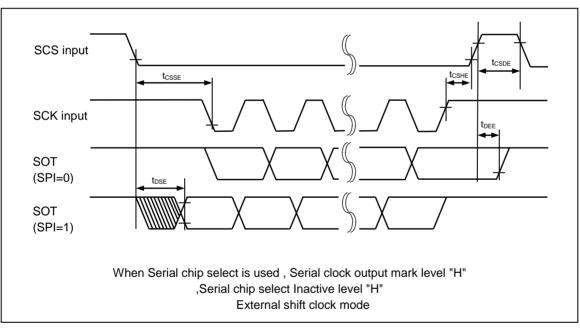

|-----------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|-----------------------|---------|------------------------------------------------------------------|

| Parameter                         | Symbol            | Pin Name                                                                                                                               | Conditions | Min                   | Max                   | Unit    | Remarks                                                          |

| SCS↑→SCK↑ setup time              | t <sub>CSSE</sub> | SCK1 to SCK11<br>SCS1 to SCS3,<br>SCS40 to SCS43,                                                                                      |            | 3t <sub>CPP</sub> +30 | -                     | ns      |                                                                  |

| SCK↓→SCS↓<br>hold time            | tсsне             | SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                                                                 |            | +0                    | -                     | ns      |                                                                  |

| SCS<br>deselect time              | tcsde             | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                             | -          | 3tcpp+30              | -                     | ns      | External shift clock mode output pin:                            |

| SCS↑→SOT<br>delay time            | tose              | SCS1, SCS2,<br>SCS50~SCS53,<br>SCS60~SCS63,<br>SCS70~SCS73,<br>SCS8~SCS11<br>SOT1, SOT2,<br>SOT5~SOT11                                 |            | -                     | 40                    | ns      | C <sub>L</sub> = 50 pF                                           |

|                                   |                   | SCS3,<br>SCS40~SCS43<br>SOT3,SOT4                                                                                                      |            | -                     | 300                   | ns      |                                                                  |

| SCS↓→SOT<br>delay time            | tdee              | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SOT1 to SOT11            | -          | +0                    | -                     | ns      | External shift clock mode output pin: C <sub>L</sub> = 50 pF     |

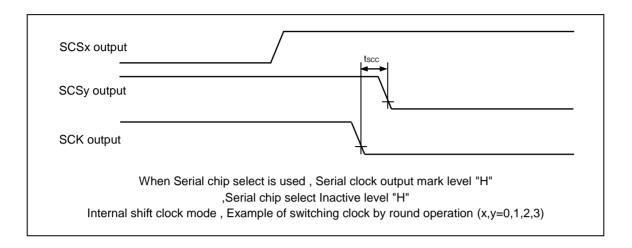

| SCK↑→SCS↑<br>clock switch<br>time | tscc              | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SCK3 , SCK4 | -          | Зtсрр-10              | 3t <sub>CPP</sub> +50 | ns      | Internal shift clock mode Round operation output pin: CL = 50 pF |

|                                   |                   | SCS3,<br>SCS40 to SCS43                                                                                                                |            | 3tсрр-300             | 3t <sub>CPP</sub> +50 |         |                                                                  |

<sup>\*1:</sup> tcssu = SCSTR:CSSU7-0 × Serial chip select timing operating clock

Regardless of the deselect time setting, once after the serial chip select pin becomes inactive, it will take at least five peripheral bus clock cycles to be active again

Please see the hardware manual for details of above-mentioned \*1,\*2, and \*3.

<sup>\*2:</sup> tcshd = SCSTR:CSHD7-0 x Serial chip select timing operating clock

<sup>\*3:</sup> tcsps = SCSTR:CSDS15-0 × Serial chip select timing operating clock

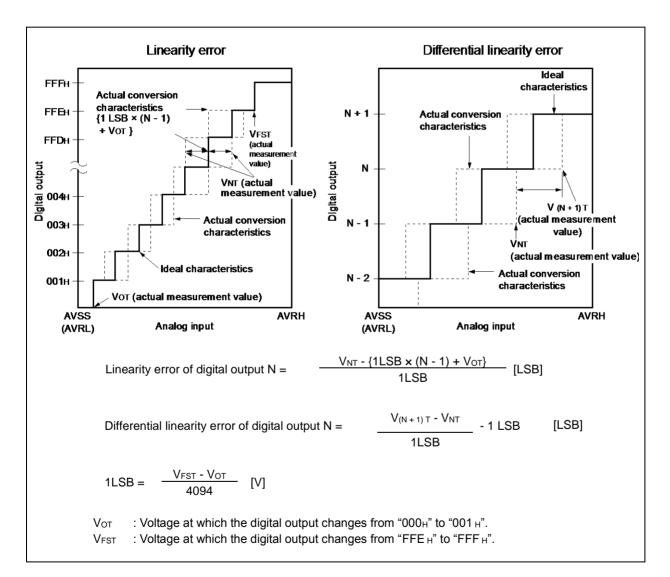

# (2) Definition of A/D Converter Terms

Resolution : Analog variation that is recognized by an A/D converter.

Linearity error : Deviation of the actual conversion characteristics from a straight line that connects

the zero transition point ("0000 0000 0000"  $\leftarrow$   $\rightarrow$  "0000 0000 0001") to the full-scale

transition point ("1111 1111 1110" $\leftarrow \rightarrow$ "1111 1111 1111").

Differential linearity

: Deviation of the input voltage from the ideal value that is required to change the

error output code by LSB.

| Page | Section         | Change Results                                                                                                                                                                                                                                                                                   |

|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                 | Corrected the following description for Product lineup comparison(120 pin).  Multi-Function  12ch                                                                                                                                                                                                |

| 9    | ■Product Lineup | Serial Interface    Multi-Function   12ch*1                                                                                                                                                                                                                                                      |

| 9    | ■Product Lineup | Added the following sentences under Product lineup comparison(120 pin)  *1: Only channel 3 and channel 4 support the I <sup>2</sup> C (high-speed mode/standard mode).  Only channel 5, channel 6, channel 7, channel 8 and channel 11 support the I <sup>2</sup> C (standard mode).             |

| 10   | ■Product Lineup | Corrected the following description for Product lineup comparison(144 pin).  Multi-Function Serial Interface  Multi-Function 12ch*1                                                                                                                                                              |

| 10   | ■Product Lineup | Added the following sentences under Product lineup comparison(144 pin)  *1: Only channel 3 and channel 4 support the I <sup>2</sup> C (high-speed mode/standard mode).  Only channel 5, channel 6, channel 7, channel 8, channel 10 and channel 11 support the I <sup>2</sup> C (standard mode). |

| 11   | ■Product Lineup | Corrected the following description for Product lineup comparison(176 pin).  Multi-Function Serial Interface  Multi-Function                                                                                                                                                                     |

| 11   | ■Product Lineup | Added the following sentences under Product lineup comparison(176 pin)  *1: Only channel 3 and channel 4 support the I <sup>2</sup> C (high-speed mode/standard mode).  Only channel 5, channel 6, channel 7, channel 8, channel 10 and channel 11 support the I <sup>2</sup> C (standard mode). |

| Signals indicated by the shading below deleted in Figure.  - Left side  VSS 1  P020/SIN3_1/TRG3_0/TIN0_2/RT05_1 2  P024/SIN4_1/PPG24_0/TIN1_0/RT04_1/INT15_0 3  P022/SCS40_1/PPG27_0/TOT0_0/RT03_1 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page | Section | Change Results                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------------------------------------------------------------------------------|

| P033SCS4_IPPGG_0TOT_0RTO_I 5 P033PGG_1_0RCU3_3TTN4_0RTO_I_SCK3_2 6 P034OCUI_I_RCU3_3TTN5_0RTO_I_SOT_3 7 P151SCK8_0SCI_0CU9_ITRG7_0CU0_3TTN7_0ZN0_0DTTI_I 5 P035INI_0CU1_ITG7_0AIN0_0NTI_I_0 9 P040SCS3_INCUT_ITOTS_0BIN0_0 10 P040SPG3_INCUT_INCTS_0BIN0_0 10 P040SPG3_INCUT_INCTS_0BIN0_0 10 P040SCS3_INCUT_INCTS_0BIN0_0 10 P040SCS3_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_INCUT_IN |      |         | Signals indicated by the shading below deleted in Figure.  - Left side    VSS |

| Page | Section                   | Change Results   |

|------|---------------------------|------------------|

| 13   | ■Pin Assignment MB91F52xB | - Right side  48 |

| Page  | Section          | Change Results                    |                  |          |                  |     |     |                                     |  |

|-------|------------------|-----------------------------------|------------------|----------|------------------|-----|-----|-------------------------------------|--|

|       |                  | (Continued) (Correct) Pin no. Pin |                  |          |                  |     |     |                                     |  |

|       |                  |                                   |                  |          |                  |     |     |                                     |  |

|       |                  | 64                                | 80               | 100      | 120              | 144 | 176 | Name                                |  |

|       |                  |                                   |                  |          |                  |     |     | P034                                |  |

|       |                  |                                   |                  |          |                  |     |     | A06 *2, *3, *4, *5                  |  |

|       |                  |                                   |                  |          |                  |     |     | OCU11_1                             |  |

|       |                  | 7 *1                              | 9 *1             | 11 *1    | 14 *1            | 17  | 21  | ICU2_3                              |  |

|       |                  |                                   |                  |          |                  |     |     | TIN5_0                              |  |

|       |                  |                                   |                  |          |                  |     |     | RTO0_1                              |  |

|       |                  |                                   |                  | <u> </u> | <u> </u>         | ł   | :   | SOT3_2                              |  |

|       |                  | l <del> </del>                    |                  | <u> </u> |                  |     |     | P151                                |  |

|       |                  |                                   |                  |          |                  |     |     | SCK8_0/                             |  |

|       |                  |                                   |                  |          | 3 16             | 19  |     | SCL8 *2, *3                         |  |

|       |                  |                                   | 10*1             | 13       |                  |     |     | OCU9_1                              |  |

|       |                  | 8 *1                              |                  |          |                  |     | 23  | TRG7_0                              |  |

|       |                  |                                   |                  |          |                  |     |     | ICU0_3                              |  |

|       |                  |                                   |                  |          |                  |     |     | TIN7_0                              |  |

|       | BN B             |                                   |                  |          |                  |     |     | ZIN0_2                              |  |

| 1, 22 | ■PIN Description |                                   |                  |          |                  |     |     | DTTI_1                              |  |

|       |                  |                                   |                  | 14*1     | 1 17*1           | 20  | 24  | P035                                |  |

|       |                  |                                   | 11 *1            |          |                  |     |     | A07 *2, *3, *4, *5<br>SIN8_0 *2, *3 |  |

|       |                  | 9 *1                              |                  |          |                  |     |     | OCU8_1                              |  |

|       |                  |                                   |                  |          |                  |     |     | TOT4_0                              |  |

|       |                  |                                   |                  |          |                  |     |     | AIN0_0                              |  |

|       |                  |                                   |                  |          |                  |     |     | INT11_0                             |  |

|       |                  |                                   |                  |          |                  |     |     | P036                                |  |

|       |                  |                                   |                  |          |                  |     |     | A08 *2, *3, *4, *5                  |  |

|       |                  | 10 *1                             | 12 <sup>*1</sup> | 15 *1    | 18 <sup>*1</sup> | 21  | 25  | SCS8_0 *2, *3                       |  |

|       |                  |                                   |                  | . •      |                  |     |     | OCU7_1                              |  |

|       |                  |                                   |                  |          |                  |     |     | TOT5_0                              |  |

|       |                  |                                   |                  |          |                  |     |     | BIN0_0<br>P037                      |  |

|       |                  |                                   |                  |          |                  |     |     | A09 *4, *5                          |  |

|       |                  | _                                 | _                | 16 *1    | 19 <sup>*1</sup> | 22  | 26  | OCU6_1                              |  |

|       |                  |                                   |                  |          |                  |     | 20  | TOT6_0                              |  |

|       |                  |                                   |                  |          |                  |     |     | ZIN0_0                              |  |

|       |                  |                                   |                  |          |                  |     | 27  | P174                                |  |

|       |                  | -                                 | -                | -        | -                | -   | 27  | TRG8_1                              |  |