Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 2006                                                     |

| Number of Logic Elements/Cells | 20060                                                    |

| Total RAM Bits                 | 294912                                                   |

| Number of I/O                  | 301                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 400-BGA                                                  |

| Supplier Device Package        | 400-FBGA (21x21)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1c20f400c8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1. Introduction

C51001-1.5

#### Introduction

The Cyclone® field programmable gate array family is based on a 1.5-V, 0.13-µm, all-layer copper SRAM process, with densities up to 20,060 logic elements (LEs) and up to 288 Kbits of RAM. With features like phase-locked loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements, Cyclone devices are a cost-effective solution for data-path applications. Cyclone devices support various I/O standards, including LVDS at data rates up to 640 megabits per second (Mbps), and 66- and 33-MHz, 64- and 32-bit peripheral component interconnect (PCI), for interfacing with and supporting ASSP and ASIC devices. Altera also offers new low-cost serial configuration devices to configure Cyclone devices.

#### **Features**

The Cyclone device family offers the following features:

- 2,910 to 20,060 LEs, see Table 1–1

- Up to 294,912 RAM bits (36,864 bytes)

- Supports configuration through low-cost serial configuration device

- Support for LVTTL, LVCMOS, SSTL-2, and SSTL-3 I/O standards

- Support for 66- and 33-MHz, 64- and 32-bit PCI standard

- High-speed (640 Mbps) LVDS I/O support

- Low-speed (311 Mbps) LVDS I/O support

- 311-Mbps RSDS I/O support

- Up to two PLLs per device provide clock multiplication and phase shifting

- Up to eight global clock lines with six clock resources available per logic array block (LAB) row

- Support for external memory, including DDR SDRAM (133 MHz),

FCRAM, and single data rate (SDR) SDRAM

- Support for multiple intellectual property (IP) cores, including Altera® MegaCore® functions and Altera Megafunctions Partners Program (AMPPSM) megafunctions.

| Table 1–1. Cyclone Device Features (Part 1 of 2) |       |       |       |        |        |

|--------------------------------------------------|-------|-------|-------|--------|--------|

| Feature EP1C3 EP1C4 EP1C6 EP1C12 EP1C20          |       |       |       |        |        |

| LEs                                              | 2,910 | 4,000 | 5,980 | 12,060 | 20,060 |

| M4K RAM blocks (128 × 36 bits)                   | 13    | 17    | 20    | 52     | 64     |

to the appropriate plane on the board. The Quartus II software reserves I/O pins as power pins as necessary for layout with the larger densities in the same package having more power pins.

| Table 1–3. Cyclone QFP and FineLine BGA Package Sizes                                            |                 |                 |                 |                            |                            |                            |

|--------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------------------|----------------------------|----------------------------|

| Dimension                                                                                        | 100-Pin<br>TQFP | 144-Pin<br>TQFP | 240-Pin<br>PQFP | 256-Pin<br>FineLine<br>BGA | 324-Pin<br>FineLine<br>BGA | 400-Pin<br>FineLine<br>BGA |

| Pitch (mm)                                                                                       | 0.5             | 0.5             | 0.5             | 1.0                        | 1.0                        | 1.0                        |

| Area (mm²)                                                                                       | 256             | 484             | 1,024           | 289                        | 361                        | 441                        |

| $\begin{array}{c} \text{Length} \times \text{width} \\ \text{(mm} \times \text{mm)} \end{array}$ | 16×16           | 22×22           | 34.6×34.6       | 17×17                      | 19×19                      | 21×21                      |

# Document Revision History

Table 1–4 shows the revision history for this document.

| Table 1–4. Document Revision History |                                                                                                                   |                    |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Date and<br>Document<br>Version      | Changes Made                                                                                                      | Summary of Changes |  |

| May 2008<br>v1.5                     | Minor textual and style changes.                                                                                  | _                  |  |

| January 2007<br>v1.4                 | Added document revision history.                                                                                  | _                  |  |

| August 2005<br>v1.3                  | Minor updates.                                                                                                    | _                  |  |

| October 2003<br>v1.2                 | Added 64-bit PCI support information.                                                                             | _                  |  |

| September<br>2003 v1.1               | <ul> <li>Updated LVDS data rates to 640 Mbps from 311 Mbps.</li> <li>Updated RSDS feature information.</li> </ul> | _                  |  |

| May 2003 v1.0                        | Added document to Cyclone Device Handbook.                                                                        | _                  |  |

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

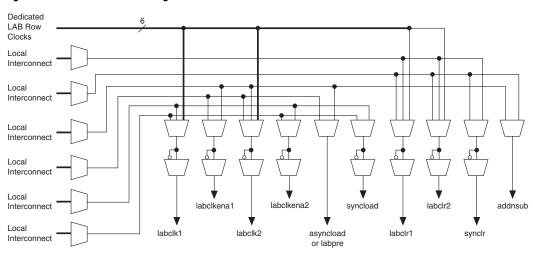

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

### **Logic Elements**

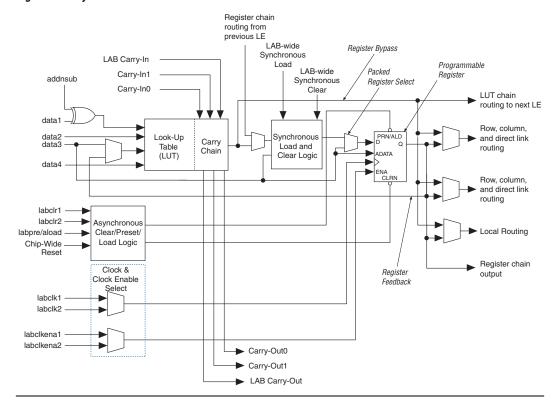

The smallest unit of logic in the Cyclone architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by a LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

Figure 2-5. Cyclone LE

Each LE's programmable register can be configured for D, T, JK, or SR operation. Each register has data, true asynchronous load data, clock, clock enable, clear, and asynchronous load/preset inputs. Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous data. The asynchronous load data input comes from the data3 input of the LE. For combinatorial functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive column or row and direct link routing connections and one drives local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated

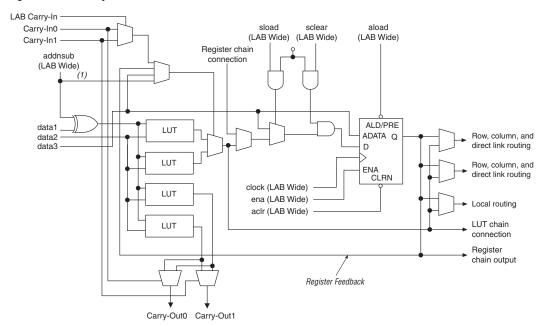

Figure 2-7. LE in Dynamic Arithmetic Mode

Note to Figure 2-7:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

#### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within a LAB.

The speed advantage of the carry-select chain is in the parallel pre-computation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Cyclone architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

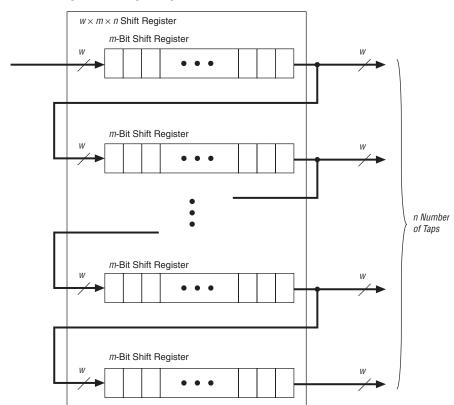

register outputs (number of taps  $n \times$  width w) must be less than the maximum data width of the M4K RAM block (×36). To create larger shift registers, multiple memory blocks are cascaded together.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 2–14 shows the M4K memory block in the shift register mode.

Figure 2-14. Shift Register Memory Configuration

## **Memory Configuration Sizes**

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration

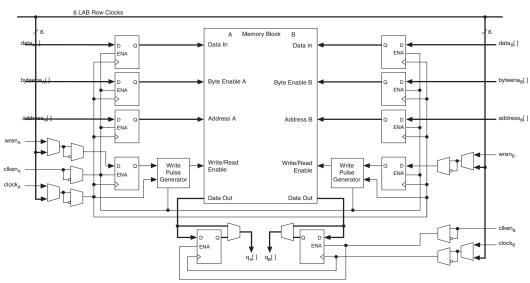

Figure 2–18. Input/Output Clock Mode in True Dual-Port Mode Notes (1), (2)

#### Notes to Figure 2–18:

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

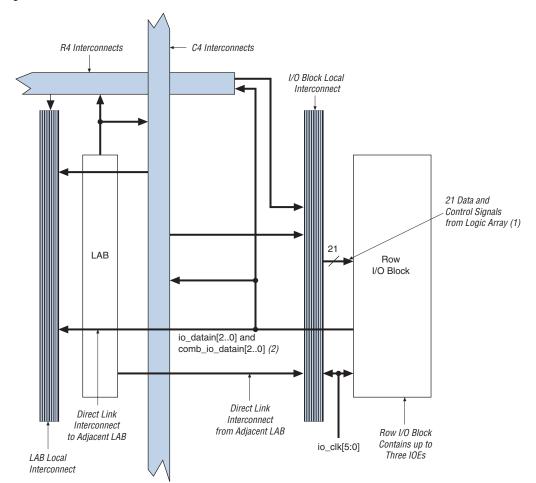

Figure 2-28. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–28:*

- (1) The 21 data and control signals consist of three data out lines, io\_dataout[2..0], three output enables, io\_coe[2..0], three input clock enables, io\_cce\_in[2..0], three output clock enables, io\_cce\_out[2..0], three clocks, io\_cclk[2..0], three asynchronous clear signals, io\_caclr[2..0], and three synchronous clear signals, io\_csclr[2..0].

- (2) Each of the three IOEs in the row I/O block can have one io\_datain input (combinatorial or registered) and one comb\_io\_datain (combinatorial) input.

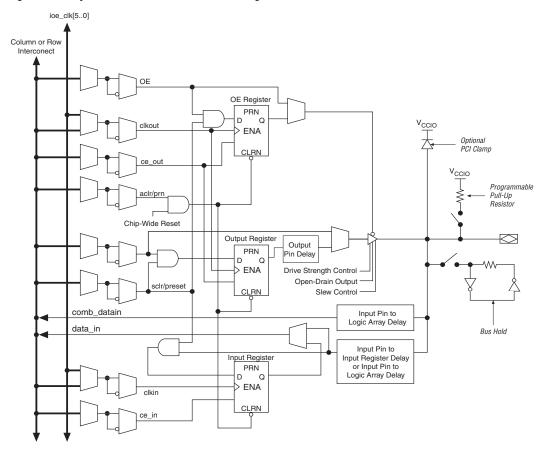

Figure 2-32. Cyclone IOE in Bidirectional I/O Configuration

The Cyclone device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays

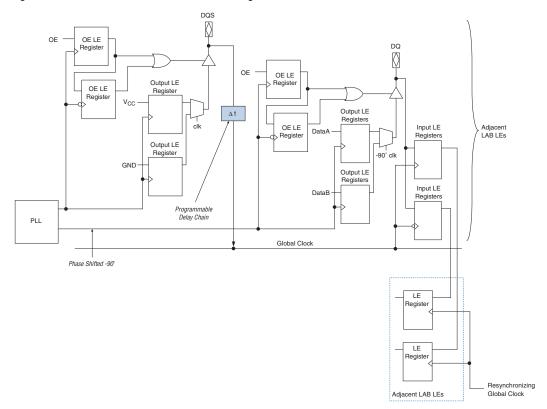

Figure 2-34. DDR SDRAM and FCRAM Interfacing

# **Programmable Drive Strength**

The output buffer for each Cyclone device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standards have several levels of drive strength that the designer can control. SSTL-3 class I and II, and SSTL-2 class I and II support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/I_{OL}$

#### Slew-Rate Control

The output buffer for each Cyclone device I/O pin has a programmable output slew-rate control that can be configured for low noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each I/O pin has an individual slew-rate control, allowing the designer to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

#### **Bus Hold**

Each Cyclone device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. The designer can select this feature individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\text{CCIO}}$  to prevent overdriving signals. If the bus-hold feature is enabled, the device cannot use the programmable pull-up option. Disable the bus-hold feature when the I/O pin is configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance (RBH) of approximately 7 k $\Omega$ to pull the signal level to the last-driven state. Table 4–15 on page 4–6 gives the specific sustaining current for each  $V_{\text{CCIO}}$  voltage level driven through this resistor and overdrive current used to identify the next-driven input level.

The bus-hold circuitry is only active after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

#### Programmable Pull-Up Resistor

Each Cyclone device I/O pin provides an optional programmable pull-up resistor during user mode. If the designer enables this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the V<sub>CCIO</sub> level of the output pin's bank. Dedicated clock pins do not have the optional programmable pull-up resistor.

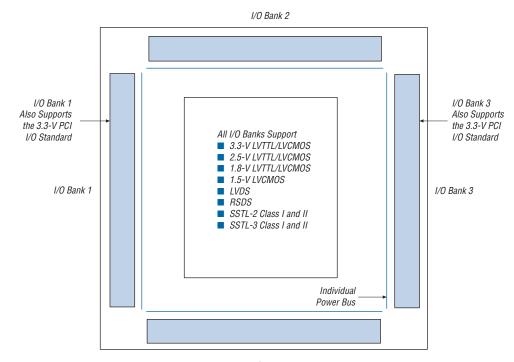

and DM pins to support a DDR SDRAM or FCRAM interface. I/O bank 1 can also support a DDR SDRAM or FCRAM interface, however, the configuration input pins in I/O bank 1 must operate at 2.5 V. I/O bank 3 can also support a DDR SDRAM or FCRAM interface, however, all the JTAG pins in I/O bank 3 must operate at 2.5 V.

**Figure 2–35. Cyclone I/O Banks** Notes (1), (2)

I/O Bank 4

#### *Notes to Figure 2–35:*

- (1) Figure 2–35 is a top view of the silicon die.

- (2) Figure 2–35 is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced standards (e.g., SSTL-3) independently. If an I/O bank does not use voltage-referenced standards, the  $V_{\rm REF}$  pins are available as user I/O pins.

Each I/O bank can support multiple standards with the same  $V_{CCIO}$  for input and output pins. For example, when  $V_{CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

#### LVDS I/O Pins

A subset of pins in all four I/O banks supports LVDS interfacing. These dual-purpose LVDS pins require an external-resistor network at the transmitter channels in addition to 100- $\Omega$  termination resistors on receiver channels. These pins do not contain dedicated serialization or deserialization circuitry; therefore, internal logic performs serialization and deserialization functions.

Table 2–13 shows the total number of supported LVDS channels per device density.

| Table 2–13. Cyclone Device LVDS Channels |           |                         |  |  |

|------------------------------------------|-----------|-------------------------|--|--|

| Device                                   | Pin Count | Number of LVDS Channels |  |  |

| EP1C3                                    | 100       | (1)                     |  |  |

|                                          | 144       | 34                      |  |  |

| EP1C4                                    | 324       | 103                     |  |  |

|                                          | 400       | 129                     |  |  |

| EP1C6                                    | 144       | 29                      |  |  |

|                                          | 240       | 72                      |  |  |

|                                          | 256       | 72                      |  |  |

| EP1C12                                   | 240       | 66                      |  |  |

|                                          | 256       | 72                      |  |  |

|                                          | 324       | 103                     |  |  |

| EP1C20                                   | 324       | 95                      |  |  |

|                                          | 400       | 129                     |  |  |

*Note to Table 2–13:*

#### MultiVolt I/O Interface

The Cyclone architecture supports the MultiVolt I/O interface feature, which allows Cyclone devices in all packages to interface with systems of different supply voltages. The devices have one set of  $V_{CC}$  pins for internal operation and input buffers ( $V_{CCINT}$ ), and four sets for I/O output drivers ( $V_{CCIO}$ ).

EP1C3 devices in the 100-pin TQFP package do not support the LVDS I/O standard.

# 3. Configuration and Testing

C51003-1.4

# IEEE Std. 1149.1 (JTAG) Boundary Scan Support

All Cyclone<sup>®</sup> devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1a-1990 specification. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Cyclone devices can also use the JTAG port for configuration together with either the Quartus<sup>®</sup> II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Cyclone devices support reconfiguring the I/O standard settings on the IOE through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode. Designers can use this ability for JTAG testing before configuration when some of the Cyclone pins drive or receive from other devices on the board using voltage-referenced standards. Since the Cyclone device might not be configured before JTAG testing, the I/O pins might not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows designers to fully test I/O connection to other devices.

The JTAG pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The TDO pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The bank  $V_{\rm CCIO}$  selects whether the JTAG inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

Cyclone devices also use the JTAG port to monitor the operation of the device with the SignalTap® II embedded logic analyzer. Cyclone devices support the JTAG instructions shown in Table 3–1.

| Table 3–1. Cyclone JTAG Instructions (Part 1 of 2) |                  |                                                                                                                                                                                                                                         |  |  |

|----------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| JTAG Instruction                                   | Instruction Code | Description                                                                                                                                                                                                                             |  |  |

| SAMPLE/PRELOAD                                     | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer. |  |  |

| EXTEST (1)                                         | 00 0000 0000     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                     |  |  |

| BYPASS                                             | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                             |  |  |

#### **Operating Modes**

The Cyclone architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Cyclone devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. Designers can perform in-field upgrades by distributing new configuration files either within the system or remotely.

A built-in weak pull-up resistor pulls all user I/O pins to  $V_{\text{CCIO}}$  before and during device configuration.

The configuration pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The voltage level of the configuration output pins is determined by the  $V_{CCIO}$  of the bank where the pins reside. The bank  $V_{CCIO}$  selects whether the configuration inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

#### **Configuration Schemes**

Designers can load the configuration data for a Cyclone device with one of three configuration schemes (see Table 3–5), chosen on the basis of the target application. Designers can use a configuration device, intelligent controller, or the JTAG port to configure a Cyclone device. A low-cost configuration device can automatically configure a Cyclone device at system power-up.

Multiple Cyclone devices can be configured in any of the three configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 3–5. Data Sources for Configuration                                                                                 |                                                                                          |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Configuration Scheme                                                                                                      | Data Source                                                                              |  |  |

| Active serial                                                                                                             | Low-cost serial configuration device                                                     |  |  |

| Passive serial (PS)  Enhanced or EPC2 configuration device, MasterBlaster or ByteBlasterMV download or serial data source |                                                                                          |  |  |

| JTAG                                                                                                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor with a Jam or JBC file |  |  |

# Referenced Documents

This chapter references the following document:

- AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

- Jam Programming & Test Language Specification

# Document Revision History

Table 3–6 shows the revision history for this chapter.

| Date and<br>Document<br>Version | Changes Made                                                                                         | Summary of Changes |

|---------------------------------|------------------------------------------------------------------------------------------------------|--------------------|

| May 2008<br>v1.4                | Minor textual and style changes. Added "Referenced Documents" section.                               | _                  |

| January 2007<br>v1.3            | <ul> <li>Added document revision history.</li> <li>Updated handpara note below Table 3–4.</li> </ul> | _                  |

| August 2005<br>V1.2             | Minor updates.                                                                                       | _                  |

| February 2005<br>V1.1           | Updated JTAG chain limits. Added information concerning test vectors.                                | _                  |

| May 2003 v1.0                   | Added document to Cyclone Device Handbook.                                                           | _                  |

| Table 4–16. Cyclone Device Capacitance   Note (14) |                                                                    |         |      |  |

|----------------------------------------------------|--------------------------------------------------------------------|---------|------|--|

| Symbol                                             | Parameter                                                          | Typical | Unit |  |

| C <sub>IO</sub>                                    | Input capacitance for user I/O pin                                 | 4.0     | pF   |  |

| C <sub>LVDS</sub>                                  | Input capacitance for dual-purpose LVDS/user I/O pin               | 4.7     | pF   |  |

| C <sub>VREF</sub>                                  | Input capacitance for dual-purpose V <sub>REF</sub> /user I/O pin. | 12.0    | pF   |  |

| C <sub>DPCLK</sub>                                 | Input capacitance for dual-purpose DPCLK/user I/O pin.             | 4.4     | pF   |  |

| C <sub>CLK</sub>                                   | Input capacitance for CLK pin.                                     | 4.7     | pF   |  |

#### *Notes to Tables 4–1 through 4–16:*

- (1) Refer to the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.5$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

- (7)  $V_I$  = ground, no load, no toggling inputs.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) R<sub>CONF</sub> is the measured value of internal pull-up resistance when the I/O pin is tied directly to GND. R<sub>CONF</sub> value will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (11) Drive strength is programmable according to values in Cyclone Architecture chapter in the Cyclone Device Handbook.

- (12) Overdrive is possible when a 1.5 V or 1.8 V and a 2.5 V or 3.3 V input signal feeds an input pin. Turn on "Allow voltage overdrive" for LVTTL/LVCMOS input pins in the Assignments > Device > Device and Pin Options > Pin Placement tab when a device has this I/O combination. However, higher leakage current is expected.

- (13) The Cyclone LVDS interface requires a resistor network outside of the transmitter channels.

- (14) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within ±0.5 pF.

| Table 4–22. IOE Internal Timing Microparameter Descriptions |                                                       |  |  |

|-------------------------------------------------------------|-------------------------------------------------------|--|--|

| Symbol                                                      | Parameter                                             |  |  |

| $t_{SU}$                                                    | IOE input and output register setup time before clock |  |  |

| t <sub>H</sub>                                              | IOE input and output register hold time after clock   |  |  |

| t <sub>CO</sub>                                             | IOE input and output register clock-to-output delay   |  |  |

| t <sub>PIN2COMBOUT_R</sub>                                  | Row input pin to IOE combinatorial output             |  |  |

| t <sub>PIN2COMBOUT_C</sub>                                  | Column input pin to IOE combinatorial output          |  |  |

| t <sub>COMBIN2PIN_R</sub>                                   | Row IOE data input to combinatorial output pin        |  |  |

| t <sub>COMBIN2PIN_C</sub>                                   | Column IOE data input to combinatorial output pin     |  |  |

| t <sub>CLR</sub>                                            | Minimum clear pulse width                             |  |  |

| t <sub>PRE</sub>                                            | Minimum preset pulse width                            |  |  |

| t <sub>CLKHL</sub>                                          | Minimum clock high or low time                        |  |  |

| Table 4–23. M4K Block Internal Timing Microparameter Descriptions |                                                   |  |  |

|-------------------------------------------------------------------|---------------------------------------------------|--|--|

| Symbol                                                            | Parameter                                         |  |  |

| t <sub>M4KRC</sub>                                                | Synchronous read cycle time                       |  |  |

| t <sub>M4KWC</sub>                                                | Synchronous write cycle time                      |  |  |

| t <sub>M4KWERESU</sub>                                            | Write or read enable setup time before clock      |  |  |

| t <sub>M4KWEREH</sub>                                             | Write or read enable hold time after clock        |  |  |

| t <sub>M4KBESU</sub>                                              | Byte enable setup time before clock               |  |  |

| t <sub>M4KBEH</sub>                                               | Byte enable hold time after clock                 |  |  |

| t <sub>M4KDATAASU</sub>                                           | A port data setup time before clock               |  |  |

| t <sub>M4KDATAAH</sub>                                            | A port data hold time after clock                 |  |  |

| t <sub>M4KADDRASU</sub>                                           | A port address setup time before clock            |  |  |

| t <sub>M4KADDRAH</sub>                                            | A port address hold time after clock              |  |  |

| t <sub>M4KDATABSU</sub>                                           | B port data setup time before clock               |  |  |

| t <sub>M4KDATABH</sub>                                            | B port data hold time after clock                 |  |  |

| t <sub>M4KADDRBSU</sub>                                           | B port address setup time before clock            |  |  |

| t <sub>M4KADDRBH</sub>                                            | B port address hold time after clock              |  |  |

| t <sub>M4KDATACO1</sub>                                           | Clock-to-output delay when using output registers |  |  |

| t <sub>M4KDATACO2</sub>                                           | Clock-to-output delay without output registers    |  |  |

| t <sub>M4KCLKHL</sub>                                             | Minimum clock high or low time                    |  |  |

| t <sub>M4KCLR</sub>                                               | Minimum clear pulse width                         |  |  |

# 5. Reference and Ordering Information

C51005-1.4

#### Software

Cyclone® devices are supported by the Altera® Quartus® II design software, which provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, SignalTap® II logic analysis, and device configuration.

For more information about the Quartus II software features, refer to the *Quartus II Handbook*.

The Quartus II software supports the Windows 2000/NT/98, Sun Solaris, Linux Red Hat v7.1 and HP-UX operating systems. It also supports seamless integration with industry-leading EDA tools through the NativeLink® interface.

#### **Device Pin-Outs**

Device pin-outs for Cyclone devices are available on the Altera website (www.altera.com) and in the *Cyclone Device Handbook*.

# Ordering Information

Figure 5–1 describes the ordering codes for Cyclone devices. For more information about a specific package, refer to the *Package Information for Cyclone Devices* chapter in the *Cyclone Device Handbook*.

| February 2005<br>v1.1 | Updated Figure 5-1.                        | _ |

|-----------------------|--------------------------------------------|---|

| May 2003<br>v1.0      | Added document to Cyclone Device Handbook. | _ |