Welcome to **E-XFL.COM**

## **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 2006                                                     |

| Number of Logic Elements/Cells | 20060                                                    |

| Total RAM Bits                 | 294912                                                   |

| Number of I/O                  | 301                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 400-BGA                                                  |

| Supplier Device Package        | 400-FBGA (21x21)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1c20f400i7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Introduction

C51001-1.5

#### Introduction

The Cyclone® field programmable gate array family is based on a 1.5-V, 0.13-µm, all-layer copper SRAM process, with densities up to 20,060 logic elements (LEs) and up to 288 Kbits of RAM. With features like phase-locked loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements, Cyclone devices are a cost-effective solution for data-path applications. Cyclone devices support various I/O standards, including LVDS at data rates up to 640 megabits per second (Mbps), and 66- and 33-MHz, 64- and 32-bit peripheral component interconnect (PCI), for interfacing with and supporting ASSP and ASIC devices. Altera also offers new low-cost serial configuration devices to configure Cyclone devices.

#### **Features**

The Cyclone device family offers the following features:

- 2,910 to 20,060 LEs, see Table 1–1

- Up to 294,912 RAM bits (36,864 bytes)

- Supports configuration through low-cost serial configuration device

- Support for LVTTL, LVCMOS, SSTL-2, and SSTL-3 I/O standards

- Support for 66- and 33-MHz, 64- and 32-bit PCI standard

- High-speed (640 Mbps) LVDS I/O support

- Low-speed (311 Mbps) LVDS I/O support

- 311-Mbps RSDS I/O support

- Up to two PLLs per device provide clock multiplication and phase shifting

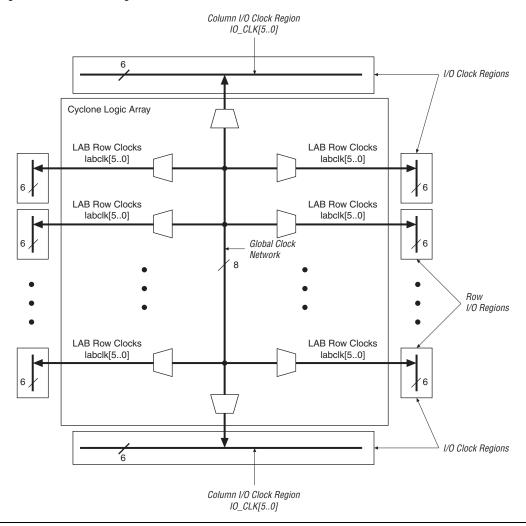

- Up to eight global clock lines with six clock resources available per logic array block (LAB) row

- Support for external memory, including DDR SDRAM (133 MHz),

FCRAM, and single data rate (SDR) SDRAM

- Support for multiple intellectual property (IP) cores, including Altera® MegaCore® functions and Altera Megafunctions Partners Program (AMPPSM) megafunctions.

| Table 1–1. Cyclone Device Features (Part 1 of 2) |       |       |       |        |        |  |

|--------------------------------------------------|-------|-------|-------|--------|--------|--|

| Feature                                          | EP1C3 | EP1C4 | EP1C6 | EP1C12 | EP1C20 |  |

| LEs                                              | 2,910 | 4,000 | 5,980 | 12,060 | 20,060 |  |

| M4K RAM blocks (128 × 36 bits)                   | 13    | 17    | 20    | 52     | 64     |  |

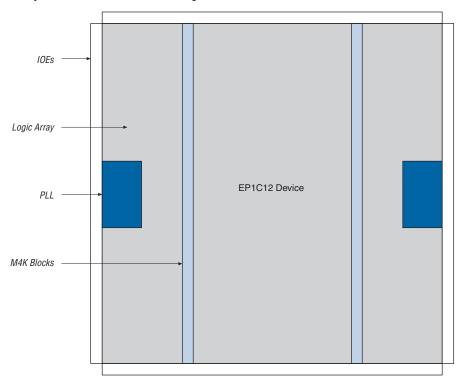

Figure 2-1. Cyclone EP1C12 Device Block Diagram

The number of M4K RAM blocks, PLLs, rows, and columns vary per device. Table 2–1 lists the resources available in each Cyclone device.

| Table 2–1. Cyclone Device Resources |         |        |      |               |          |  |  |

|-------------------------------------|---------|--------|------|---------------|----------|--|--|

| Device                              | M4K RAM |        | PLLs | LAB Columns   | LADD     |  |  |

| Device                              | Columns | Blocks | PLLS | LAD CUIUIIIIS | LAB Rows |  |  |

| EP1C3                               | 1       | 13     | 1    | 24            | 13       |  |  |

| EP1C4                               | 1       | 17     | 2    | 26            | 17       |  |  |

| EP1C6                               | 1       | 20     | 2    | 32            | 20       |  |  |

| EP1C12                              | 2       | 52     | 2    | 48            | 26       |  |  |

| EP1C20                              | 2       | 64     | 2    | 64            | 32       |  |  |

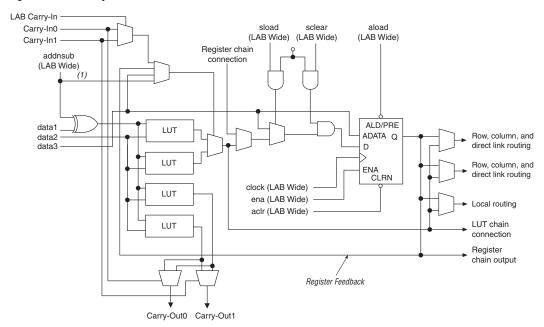

## Logic Array Blocks

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, look-up table (LUT) chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within a LAB. The Quartus® II Compiler places associated logic within a LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–2 details the Cyclone LAB.

Row Interconnect Column Interconnect Direct link interconnect from Direct link adjacent block interconnect from adjacent block Direct link Direct link interconnect to interconnect to adjacent block adjacent block LÄB Local Interconnect

Figure 2-2. Cyclone LAB Structure

#### LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, PLLs, and M4K RAM blocks from the left and right can also drive a LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher

Figure 2-7. LE in Dynamic Arithmetic Mode

Note to Figure 2-7:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

#### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within a LAB.

The speed advantage of the carry-select chain is in the parallel pre-computation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Cyclone architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

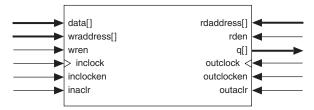

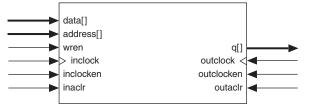

In addition to true dual-port memory, the M4K memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write. Single-port memory supports non-simultaneous reads and writes. Figure 2–13 shows these different M4K RAM memory port configurations.

Figure 2–13. Simple Dual-Port and Single-Port Memory Configurations

#### Simple Dual-Port Memory

#### Single-Port Memory (1)

#### *Note to Figure 2–13:*

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

The Cyclone memory architecture can implement fully synchronous RAM by registering both the input and output signals to the M4K RAM block. All M4K memory block inputs are registered, providing synchronous write cycles. In synchronous operation, the memory block generates its own self-timed strobe write enable (wren) signal derived from a global clock. In contrast, a circuit using asynchronous RAM must generate the RAM wren signal while ensuring its data and address signals meet setup and hold time specifications relative to the wren

Figure 2-24. I/O Clock Regions

#### **PLLs**

Cyclone PLLs provide general-purpose clocking with clock multiplication and phase shifting as well as outputs for differential I/O support. Cyclone devices contain two PLLs, except for the EP1C3 device, which contains one PLL.

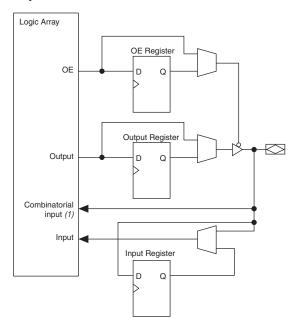

Figure 2-27. Cyclone IOE Structure

Note to Figure 2-27:

There are two paths available for combinatorial inputs to the logic array. Each path contains a unique programmable delay chain.

The IOEs are located in I/O blocks around the periphery of the Cyclone device. There are up to three IOEs per row I/O block and up to three IOEs per column I/O block (column I/O blocks span two columns). The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–28 shows how a row I/O block connects to the logic array. Figure 2–29 shows how a column I/O block connects to the logic array.

output pins (nSTATUS and CONF\_DONE) and all the JTAG pins in I/O bank 3 must operate at 2.5 V because the  $V_{CCIO}$  level of SSTL-2 is 2.5 V. I/O banks 1, 2, 3, and 4 support DQS signals with DQ bus modes of  $\times$  8.

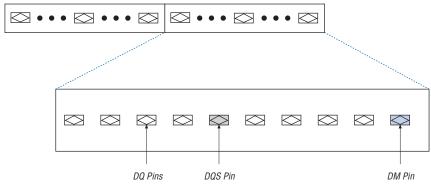

For ×8 mode, there are up to eight groups of programmable DQS and DQ pins, I/O banks 1, 2, 3, and 4 each have two groups in the 324-pin and 400-pin FineLine BGA packages. Each group consists of one DQS pin, a set of eight DQ pins, and one DM pin (see Figure 2–33). Each DQS pin drives the set of eight DQ pins within that group.

Figure 2–33. Cyclone Device DQ and DQS Groups in ×8 Mode Note (1)

Note to Figure 2-33:

(1) Each DQ group consists of one DQS pin, eight DQ pins, and one DM pin.

Table 2–10 shows the number of DQ pin groups per device.

| Table 2–10. DQ Pin Groups (Part 1 of 2) |                      |                                |                       |  |  |  |

|-----------------------------------------|----------------------|--------------------------------|-----------------------|--|--|--|

| Device                                  | Package              | Number of × 8 DQ<br>Pin Groups | Total DQ Pin<br>Count |  |  |  |

| EP1C3                                   | 100-pin TQFP (1)     | 3                              | 24                    |  |  |  |

|                                         | 144-pin TQFP         | 4                              | 32                    |  |  |  |

| EP1C4                                   | 324-pin FineLine BGA | 8                              | 64                    |  |  |  |

|                                         | 400-pin FineLine BGA | 8                              | 64                    |  |  |  |

of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot. Table 2–11 shows the possible settings for the I/O standards with drive strength control.

| Table 2–11. Programmable Drive Strength Note (1) |                                                                |  |  |  |

|--------------------------------------------------|----------------------------------------------------------------|--|--|--|

| I/O Standard                                     | I <sub>OH</sub> /I <sub>OL</sub> Current Strength Setting (mA) |  |  |  |

| LVTTL (3.3 V)                                    | 4                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12                                                             |  |  |  |

|                                                  | 16                                                             |  |  |  |

|                                                  | 24(2)                                                          |  |  |  |

| LVCMOS (3.3 V)                                   | 2                                                              |  |  |  |

|                                                  | 4                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12(2)                                                          |  |  |  |

| LVTTL (2.5 V)                                    | 2                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12                                                             |  |  |  |

|                                                  | 16(2)                                                          |  |  |  |

| LVTTL (1.8 V)                                    | 2                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12(2)                                                          |  |  |  |

| LVCMOS (1.5 V)                                   | 2                                                              |  |  |  |

|                                                  | 4                                                              |  |  |  |

|                                                  | 8(2)                                                           |  |  |  |

#### *Notes to Table 2–11:*

- SSTL-3 class I and II, SSTL-2 class I and II, and 3.3-V PCI I/O Standards do not support programmable drive strength.

- (2) This is the default current strength setting in the Quartus II software.

## **Open-Drain Output**

Cyclone devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

#### Slew-Rate Control

The output buffer for each Cyclone device I/O pin has a programmable output slew-rate control that can be configured for low noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each I/O pin has an individual slew-rate control, allowing the designer to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

#### **Bus Hold**

Each Cyclone device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. The designer can select this feature individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\text{CCIO}}$  to prevent overdriving signals. If the bus-hold feature is enabled, the device cannot use the programmable pull-up option. Disable the bus-hold feature when the I/O pin is configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance (RBH) of approximately 7 k $\Omega$ to pull the signal level to the last-driven state. Table 4–15 on page 4–6 gives the specific sustaining current for each  $V_{\text{CCIO}}$  voltage level driven through this resistor and overdrive current used to identify the next-driven input level.

The bus-hold circuitry is only active after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

### Programmable Pull-Up Resistor

Each Cyclone device I/O pin provides an optional programmable pull-up resistor during user mode. If the designer enables this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the V<sub>CCIO</sub> level of the output pin's bank. Dedicated clock pins do not have the optional programmable pull-up resistor.

| Table 3–1. Cyclone JTAG Instructions (Part 2 of 2) |                  |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|----------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| JTAG Instruction                                   | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| USERCODE                                           | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                          |  |  |  |  |

| IDCODE                                             | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                              |  |  |  |  |

| HIGHZ (1)                                          | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                 |  |  |  |  |

| CLAMP (1)                                          | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register.                                                                    |  |  |  |  |

| ICR instructions                                   | _                | Used when configuring a Cyclone device via the JTAG port with a MasterBlaster <sup>TM</sup> or ByteBlasterMV <sup>TM</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.                                                                                                                               |  |  |  |  |

| PULSE_NCONFIG                                      | 00 0000 0001     | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                        |  |  |  |  |

| CONFIG_IO                                          | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, after, or during configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction will hold nSTATUS low to reset the configuration device. nSTATUS is held low until the device is reconfigured. |  |  |  |  |

| SignalTap II instructions                          | _                | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                  |  |  |  |  |

#### *Note to Table 3–1:*

In the Quartus II software, there is an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. Choose Assignments > Device > Device and Pin Options > General. Turn on **Auto Usercode**.

<sup>(1)</sup> Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

#### **Operating Modes**

The Cyclone architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Cyclone devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. Designers can perform in-field upgrades by distributing new configuration files either within the system or remotely.

A built-in weak pull-up resistor pulls all user I/O pins to  $V_{\text{CCIO}}$  before and during device configuration.

The configuration pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The voltage level of the configuration output pins is determined by the  $V_{CCIO}$  of the bank where the pins reside. The bank  $V_{CCIO}$  selects whether the configuration inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

### **Configuration Schemes**

Designers can load the configuration data for a Cyclone device with one of three configuration schemes (see Table 3–5), chosen on the basis of the target application. Designers can use a configuration device, intelligent controller, or the JTAG port to configure a Cyclone device. A low-cost configuration device can automatically configure a Cyclone device at system power-up.

# 4. DC and Switching Characteristics

C51004-1.7

## Operating Conditions

Cyclone® devices are offered in both commercial, industrial, and extended temperature grades. However, industrial-grade and extended-temperature-grade devices may have limited speed-grade availability.

Tables 4–1 through 4–16 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for Cyclone devices.

| Table 4-1          | Table 4–1. Cyclone Device Absolute Maximum Ratings    Notes (1), (2) |                            |         |         |      |  |  |  |

|--------------------|----------------------------------------------------------------------|----------------------------|---------|---------|------|--|--|--|

| Symbol             | Parameter                                                            | Conditions                 | Minimum | Maximum | Unit |  |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                       | With respect to ground (3) | -0.5    | 2.4     | V    |  |  |  |

| V <sub>CCIO</sub>  |                                                                      |                            | -0.5    | 4.6     | V    |  |  |  |

| V <sub>CCA</sub>   | Supply voltage                                                       | With respect to ground (3) | -0.5    | 2.4     | V    |  |  |  |

| Vı                 | DC input voltage                                                     |                            | -0.5    | 4.6     | V    |  |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                           |                            | -25     | 25      | mA   |  |  |  |

| T <sub>STG</sub>   | Storage temperature                                                  | No bias                    | -65     | 150     | °C   |  |  |  |

| T <sub>AMB</sub>   | Ambient temperature                                                  | Under bias                 | -65     | 135     | °C   |  |  |  |

| T <sub>J</sub>     | Junction temperature                                                 | BGA packages under bias    | _       | 135     | °C   |  |  |  |

| Table 4–2. Cyclone Device Recommended Operating Conditions (Part 1 of 2) |                                                     |            |         |         |      |  |  |

|--------------------------------------------------------------------------|-----------------------------------------------------|------------|---------|---------|------|--|--|

| Symbol                                                                   | Parameter                                           | Conditions | Minimum | Maximum | Unit |  |  |

| V <sub>CCINT</sub>                                                       | Supply voltage for internal logic and input buffers | (4)        | 1.425   | 1.575   | V    |  |  |

| V <sub>CCIO</sub>                                                        | Supply voltage for output buffers, 3.3-V operation  | (4)        | 3.00    | 3.60    | V    |  |  |

|                                                                          | Supply voltage for output buffers, 2.5-V operation  | (4)        | 2.375   | 2.625   | V    |  |  |

|                                                                          | Supply voltage for output buffers, 1.8-V operation  | (4)        | 1.71    | 1.89    | V    |  |  |

|                                                                          | Supply voltage for output buffers, 1.5-V operation  | (4)        | 1.4     | 1.6     | V    |  |  |

| V <sub>I</sub>                                                           | Input voltage                                       | (3), (5)   | -0.5    | 4.1     | V    |  |  |

| Table 4–13. SSTL-3 Class I Specifications (Part 2 of 2) |                           |                                |                        |         |                         |      |  |  |

|---------------------------------------------------------|---------------------------|--------------------------------|------------------------|---------|-------------------------|------|--|--|

| Symbol                                                  | Parameter                 | Conditions                     | Minimum                | Typical | Maximum                 | Unit |  |  |

| $V_{REF}$                                               | Reference voltage         | _                              | 1.3                    | 1.5     | 1.7                     | V    |  |  |

| V <sub>IH</sub>                                         | High-level input voltage  | _                              | V <sub>REF</sub> + 0.2 | _       | V <sub>CCIO</sub> + 0.3 | ٧    |  |  |

| $V_{IL}$                                                | Low-level input voltage   | _                              | -0.3                   | _       | V <sub>REF</sub> - 0.2  | ٧    |  |  |

| V <sub>OH</sub>                                         | High-level output voltage | $I_{OH} = -8 \text{ mA } (11)$ | V <sub>TT</sub> + 0.6  | _       | _                       | V    |  |  |

| V <sub>OL</sub>                                         | Low-level output voltage  | I <sub>OL</sub> = 8 mA (11)    | _                      | _       | V <sub>TT</sub> - 0.6   | ٧    |  |  |

| Table 4–14. SSTL-3 Class II Specifications |                           |                               |                         |                  |                         |      |  |  |

|--------------------------------------------|---------------------------|-------------------------------|-------------------------|------------------|-------------------------|------|--|--|

| Symbol                                     | Parameter                 | Conditions                    | Minimum                 | Typical          | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage     | _                             | 3.0                     | 3.3              | 3.6                     | V    |  |  |

| V <sub>TT</sub>                            | Termination voltage       | _                             | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V    |  |  |

| V <sub>REF</sub>                           | Reference voltage         | _                             | 1.3                     | 1.5              | 1.7                     | V    |  |  |

| V <sub>IH</sub>                            | High-level input voltage  | _                             | V <sub>REF</sub> + 0.2  | _                | V <sub>CCIO</sub> + 0.3 | V    |  |  |

| V <sub>IL</sub>                            | Low-level input voltage   | _                             | -0.3                    | _                | V <sub>REF</sub> - 0.2  | V    |  |  |

| V <sub>OH</sub>                            | High-level output voltage | I <sub>OH</sub> = -16 mA (11) | V <sub>TT</sub> + 0.8   | _                | _                       | V    |  |  |

| V <sub>OL</sub>                            | Low-level output voltage  | I <sub>OL</sub> = 16 mA (11)  | _                       | _                | V <sub>TT</sub> – 0.8   | V    |  |  |

| Table 4–15. Bus Hold Parameters |                                                |     |     |     |      |     |      |     |      |      |

|---------------------------------|------------------------------------------------|-----|-----|-----|------|-----|------|-----|------|------|

|                                 | V <sub>CC10</sub> Level                        |     |     |     |      |     |      |     |      |      |

| Parameter                       | Conditions                                     | 1.5 | 5 V | 1.8 | B V  | 2.  | 5 V  | 3.3 | 3 V  | Unit |

|                                 |                                                | Min | Max | Min | Max  | Min | Max  | Min | Max  |      |

| Low sustaining current          | $V_{IN} > V_{IL}$ (maximum)                    | _   | _   | 30  | _    | 50  | _    | 70  | _    | μΑ   |

| High sustaining current         | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | _   | _   | -30 | _    | -50 | _    | -70 | _    | μΑ   |

| Low overdrive current           | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _   | _   | _   | 200  | _   | 300  | _   | 500  | μА   |

| High overdrive current          | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _   | _   | _   | -200 | _   | -300 | _   | -500 | μА   |

Typically, the user-mode current during device operation is lower than the power-up current in Table 4–17. Altera recommends using the Cyclone Power Calculator, available on the Altera web site, to estimate the user-mode  $I_{\text{CCINT}}$  consumption and then select power supplies or regulators based on the higher value.

## **Timing Model**

The DirectDrive technology and MultiTrack interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Cyclone device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

#### **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus® II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–18 shows the status of the Cyclone device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 4–18. Cyclone Device Timing Model Status |             |       |  |  |  |

|------------------------------------------------|-------------|-------|--|--|--|

| Device                                         | Preliminary | Final |  |  |  |

| EP1C3                                          | _           | ✓     |  |  |  |

| EP1C4                                          | _           | ✓     |  |  |  |

| EP1C6                                          | _           | ✓     |  |  |  |

| EP1C12                                         | _           | ✓     |  |  |  |

| EP1C20                                         | _           | ✓     |  |  |  |

| Table 4–22. IOE Internal Timing Microparameter Descriptions |                                                       |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| Symbol                                                      | Parameter                                             |  |  |  |  |

| $t_{SU}$                                                    | IOE input and output register setup time before clock |  |  |  |  |

| t <sub>H</sub>                                              | IOE input and output register hold time after clock   |  |  |  |  |

| t <sub>CO</sub>                                             | IOE input and output register clock-to-output delay   |  |  |  |  |

| t <sub>PIN2COMBOUT_R</sub>                                  | Row input pin to IOE combinatorial output             |  |  |  |  |

| t <sub>PIN2COMBOUT_C</sub>                                  | Column input pin to IOE combinatorial output          |  |  |  |  |

| t <sub>COMBIN2PIN_R</sub>                                   | Row IOE data input to combinatorial output pin        |  |  |  |  |

| t <sub>COMBIN2PIN_C</sub>                                   | Column IOE data input to combinatorial output pin     |  |  |  |  |

| t <sub>CLR</sub>                                            | Minimum clear pulse width                             |  |  |  |  |

| t <sub>PRE</sub>                                            | Minimum preset pulse width                            |  |  |  |  |

| t <sub>CLKHL</sub>                                          | Minimum clock high or low time                        |  |  |  |  |

| Table 4–23. M4K Block Internal Timing Microparameter Descriptions |                                                   |  |  |  |  |  |

|-------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| Symbol                                                            | Parameter                                         |  |  |  |  |  |

| t <sub>M4KRC</sub>                                                | Synchronous read cycle time                       |  |  |  |  |  |

| t <sub>M4KWC</sub>                                                | Synchronous write cycle time                      |  |  |  |  |  |

| t <sub>M4KWERESU</sub>                                            | Write or read enable setup time before clock      |  |  |  |  |  |

| t <sub>M4KWEREH</sub>                                             | Write or read enable hold time after clock        |  |  |  |  |  |

| t <sub>M4KBESU</sub>                                              | Byte enable setup time before clock               |  |  |  |  |  |

| t <sub>M4KBEH</sub>                                               | Byte enable hold time after clock                 |  |  |  |  |  |

| t <sub>M4KDATAASU</sub>                                           | A port data setup time before clock               |  |  |  |  |  |

| t <sub>M4KDATAAH</sub>                                            | A port data hold time after clock                 |  |  |  |  |  |

| t <sub>M4KADDRASU</sub>                                           | A port address setup time before clock            |  |  |  |  |  |

| t <sub>M4KADDRAH</sub>                                            | A port address hold time after clock              |  |  |  |  |  |

| t <sub>M4KDATABSU</sub>                                           | B port data setup time before clock               |  |  |  |  |  |

| t <sub>M4KDATABH</sub>                                            | B port data hold time after clock                 |  |  |  |  |  |

| t <sub>M4KADDRBSU</sub>                                           | B port address setup time before clock            |  |  |  |  |  |

| t <sub>M4KADDRBH</sub>                                            | B port address hold time after clock              |  |  |  |  |  |

| t <sub>M4KDATACO1</sub>                                           | Clock-to-output delay when using output registers |  |  |  |  |  |

| t <sub>M4KDATACO2</sub>                                           | Clock-to-output delay without output registers    |  |  |  |  |  |

| t <sub>M4KCLKHL</sub>                                             | Minimum clock high or low time                    |  |  |  |  |  |

| t <sub>M4KCLR</sub>                                               | Minimum clear pulse width                         |  |  |  |  |  |

| Table 4–47. Cyclone IOE Programmable Delays on Row Pins |         |                |       |                |       |                |       |         |

|---------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|-------|---------|

| Parameter                                               | Setting | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | II.a.iA |

|                                                         |         | Min            | Max   | Min            | Max   | Min            | Max   | Unit    |

| Decrease input delay to                                 | Off     | _              | 154   | _              | 177   | _              | 200   | ps      |

| internal cells                                          | Small   | _              | 2,212 | _              | 2,543 | _              | 2,875 | ps      |

|                                                         | Medium  | _              | 2,639 | _              | 3,034 | _              | 3,430 | ps      |

|                                                         | Large   | _              | 3,057 | _              | 3,515 | _              | 3,974 | ps      |

|                                                         | On      | _              | 154   | _              | 177   | _              | 200   | ps      |

| Decrease input delay to input                           | Off     | _              | 0     | _              | 0     | _              | 0     | ps      |

| register                                                | On      | _              | 3,057 | _              | 3,515 | _              | 3,974 | ps      |

| Increase delay to output pin                            | Off     | _              | 0     | _              | 0     |                | 0     | ps      |

|                                                         | On      | _              | 556   | _              | 639   | _              | 722   | ps      |

Note to Table 4-47:

## **Maximum Input and Output Clock Rates**

Tables 4--48 and 4--49 show the maximum input clock rate for column and row pins in Cyclone devices.

| Table 4–48. Cyclone Maximum Input Clock Rate for Column Pins |                   |                   |                   |      |  |  |

|--------------------------------------------------------------|-------------------|-------------------|-------------------|------|--|--|

| I/O Standard                                                 | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

| LVTTL                                                        | 464               | 428               | 387               | MHz  |  |  |

| 2.5 V                                                        | 392               | 302               | 207               | MHz  |  |  |

| 1.8 V                                                        | 387               | 311               | 252               | MHz  |  |  |

| 1.5 V                                                        | 387               | 320               | 243               | MHz  |  |  |

| LVCMOS                                                       | 405               | 374               | 333               | MHz  |  |  |

| SSTL-3 class I                                               | 405               | 356               | 293               | MHz  |  |  |

| SSTL-3 class II                                              | 414               | 365               | 302               | MHz  |  |  |

| SSTL-2 class I                                               | 464               | 428               | 396               | MHz  |  |  |

| SSTL-2 class II                                              | 473               | 432               | 396               | MHz  |  |  |

| LVDS                                                         | 567               | 549               | 531               | MHz  |  |  |

<sup>(1)</sup> EPC1C3 devices do not support the PCI I/O standard.

| Table 4–49. Cyclone Maximum Input Clock Rate for Row Pins |                   |                   |                   |      |  |

|-----------------------------------------------------------|-------------------|-------------------|-------------------|------|--|

| I/O Standard                                              | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |

| LVTTL                                                     | 464               | 428               | 387               | MHz  |  |

| 2.5 V                                                     | 392               | 302               | 207               | MHz  |  |

| 1.8 V                                                     | 387               | 311               | 252               | MHz  |  |

| 1.5 V                                                     | 387               | 320               | 243               | MHz  |  |

| LVCMOS                                                    | 405               | 374               | 333               | MHz  |  |

| SSTL-3 class I                                            | 405               | 356               | 293               | MHz  |  |

| SSTL-3 class II                                           | 414               | 365               | 302               | MHz  |  |

| SSTL-2 class I                                            | 464               | 428               | 396               | MHz  |  |

| SSTL-2 class II                                           | 473               | 432               | 396               | MHz  |  |

| 3.3-V PCI (1)                                             | 464               | 428               | 387               | MHz  |  |

| LVDS                                                      | 567               | 549               | 531               | MHz  |  |

Note to Tables 4–48 through 4–49:

Tables 4–50 and 4–51 show the maximum output clock rate for column and row pins in Cyclone devices.

| Table 4–50. Cyclone Maximum Output Clock Rate for Column Pins |                   |                   |                   |      |  |  |

|---------------------------------------------------------------|-------------------|-------------------|-------------------|------|--|--|

| I/O Standard                                                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

| LVTTL                                                         | 304               | 304               | 304               | MHz  |  |  |

| 2.5 V                                                         | 220               | 220               | 220               | MHz  |  |  |

| 1.8 V                                                         | 213               | 213               | 213               | MHz  |  |  |

| 1.5 V                                                         | 166               | 166               | 166               | MHz  |  |  |

| LVCMOS                                                        | 304               | 304               | 304               | MHz  |  |  |

| SSTL-3 class I                                                | 100               | 100               | 100               | MHz  |  |  |

| SSTL-3 class II                                               | 100               | 100               | 100               | MHz  |  |  |

| SSTL-2 class I                                                | 134               | 134               | 134               | MHz  |  |  |

| SSTL-2 class II                                               | 134               | 134               | 134               | MHz  |  |  |

| LVDS                                                          | 320               | 320               | 275               | MHz  |  |  |

Note to Table 4-50:

(1) EP1C3 devices do not support the PCI I/O standard.

<sup>(1)</sup> EP1C3 devices do not support the PCI I/O standard. These parameters are only available on row I/O pins.

| Table 4–51. Cyclone Maximum Output Clock Rate for Row Pins |                   |                   |                   |      |  |  |

|------------------------------------------------------------|-------------------|-------------------|-------------------|------|--|--|

| I/O Standard                                               | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

| LVTTL                                                      | 296               | 285               | 273               | MHz  |  |  |

| 2.5 V                                                      | 381               | 366               | 349               | MHz  |  |  |

| 1.8 V                                                      | 286               | 277               | 267               | MHz  |  |  |

| 1.5 V                                                      | 219               | 208               | 195               | MHz  |  |  |

| LVCMOS                                                     | 367               | 356               | 343               | MHz  |  |  |

| SSTL-3 class I                                             | 169               | 166               | 162               | MHz  |  |  |

| SSTL-3 class II                                            | 160               | 151               | 146               | MHz  |  |  |

| SSTL-2 class I                                             | 160               | 151               | 142               | MHz  |  |  |

| SSTL-2 class II                                            | 131               | 123               | 115               | MHz  |  |  |

| 3.3-V PCI (1)                                              | 66                | 66                | 66                | MHz  |  |  |

| LVDS                                                       | 320               | 303               | 275               | MHz  |  |  |

*Note to Tables 4–50 through 4–51:*

## **PLL Timing**

Table 4–52 describes the Cyclone FPGA PLL specifications.

| Table 4–52. Cyclone PLL Specifications (Part 1 of 2) |                                       |        |       |      |  |

|------------------------------------------------------|---------------------------------------|--------|-------|------|--|

| Symbol                                               | Parameter                             | Min    | Max   | Unit |  |

| f <sub>IN</sub>                                      | Input frequency (-6 speed grade)      | 15.625 | 464   | MHz  |  |

|                                                      | Input frequency (-7 speed grade)      | 15.625 | 428   | MHz  |  |

|                                                      | Input frequency (-8 speed grade)      | 15.625 | 387   | MHz  |  |

| f <sub>IN</sub> DUTY                                 | Input clock duty cycle                | 40.00  | 60    | %    |  |

| t <sub>IN</sub> JITTER                               | Input clock period jitter             | _      | ± 200 | ps   |  |

| f <sub>OUT_EXT</sub> (external PLL clock output)     | PLL output frequency (-6 speed grade) | 15.625 | 320   | MHz  |  |

|                                                      | PLL output frequency (-7 speed grade) | 15.625 | 320   | MHz  |  |

|                                                      | PLL output frequency (-8 speed grade) | 15.625 | 275   | MHz  |  |

<sup>(1)</sup> EP1C3 devices do not support the PCI I/O standard. These parameters are only available on row I/O pins.