Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 291                                                     |

| Number of Logic Elements/Cells | 2910                                                    |

| Total RAM Bits                 | 59904                                                   |

| Number of I/O                  | 104                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 144-LQFP                                                |

| Supplier Device Package        | 144-TQFP (20x20)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1c3t144i7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

# Logic Array Blocks

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, look-up table (LUT) chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within a LAB. The Quartus® II Compiler places associated logic within a LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–2 details the Cyclone LAB.

Row Interconnect Column Interconnect Direct link interconnect from Direct link adjacent block interconnect from adjacent block Direct link Direct link interconnect to interconnect to adjacent block adjacent block LÄB Local Interconnect

Figure 2-2. Cyclone LAB Structure

#### LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, PLLs, and M4K RAM blocks from the left and right can also drive a LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher

performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

Direct link interconnect from

left LAB, M4K memory

block, PLL, or IOE output

Direct link

interconnect

to left

Local

Interconnect

Local

Interconnect

Direct link interconnect from

right LAB, M4K memory

block, PLL, or IOE output

Direct link

interconnect

to right

Figure 2-3. Direct Link Connection

# **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, synchronous load, and add/subtract control signals. This gives a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal will also use labclkenal. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal will turn off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous load acts as a preset when the asynchronous load data input is tied high.

functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

### **LUT Chain and Register Chain**

In addition to the three general routing outputs, the LEs within a LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows a LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. "MultiTrack Interconnect" on page 2–12 for more information on LUT chain and register chain connections.

### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A + B or A -B. The LUT computes addition; subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

# **LE Operating Modes**

The Cyclone LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect, carry-in0 and carry-in1 from the previous LE, the LAB carry-in from the previous carry-chain LAB, and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous

migrating through different device densities. Dedicated row interconnects route signals to and from LABs, PLLs, and M4K memory blocks within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

The direct link interconnect allows a LAB or M4K memory block to drive into the local interconnect of its left and right neighbors. Only one side of a PLL block interfaces with direct link and row interconnects. The direct link interconnect provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, or two LABs and one M4K RAM block. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from a LAB. R4 interconnects can drive and be driven by M4K memory blocks, PLLs, and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 interconnects for connections from one row to another.

# Embedded Memory

The Cyclone embedded memory consists of columns of M4K memory blocks. EP1C3 and EP1C6 devices have one column of M4K blocks, while EP1C12 and EP1C20 devices have two columns (refer to Table 1–1 on page 1–1 for total RAM bits per density). Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250 MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Mixed clock mode

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

### **Memory Modes**

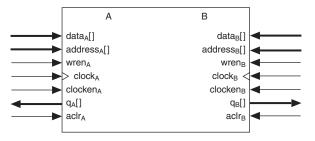

The M4K memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2–12. True Dual-Port Memory Configuration

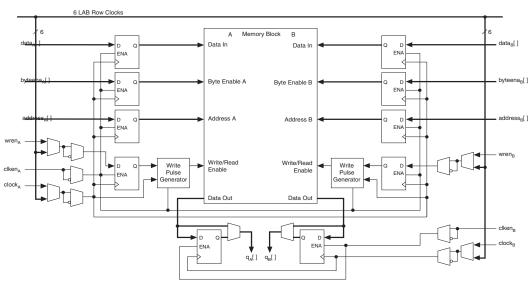

Figure 2–18. Input/Output Clock Mode in True Dual-Port Mode Notes (1), (2)

#### Notes to Figure 2–18:

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

## **External Clock Inputs**

Each PLL supports single-ended or differential inputs for source-synchronous receivers or for general-purpose use. The dedicated clock pins (CLK[3..0]) feed the PLL inputs. These dual-purpose pins can also act as LVDS input pins. See Figure 2–25.

Table 2–8 shows the I/O standards supported by PLL input and output pins.

| Table 2–8. PLL I/O Standards |           |               |

|------------------------------|-----------|---------------|

| I/O Standard                 | CLK Input | EXTCLK Output |

| 3.3-V LVTTL/LVCMOS           | ✓         | ✓             |

| 2.5-V LVTTL/LVCMOS           | ✓         | ✓             |

| 1.8-V LVTTL/LVCMOS           | ✓         | ✓             |

| 1.5-V LVCMOS                 | ✓         | ✓             |

| 3.3-V PCI                    | ✓         | ✓             |

| LVDS                         | ✓         | ✓             |

| SSTL-2 class I               | ✓         | ✓             |

| SSTL-2 class II              | ✓         | ✓             |

| SSTL-3 class I               | ✓         | ✓             |

| SSTL-3 class II              | ✓         | ✓             |

| Differential SSTL-2          | _         | ✓             |

For more information on LVDS I/O support, refer to "LVDS I/O Pins" on page 2–54.

# **External Clock Outputs**

Each PLL supports one differential or one single-ended output for source-synchronous transmitters or for general-purpose external clocks. If the PLL does not use these PLL\_OUT pins, the pins are available for use as general-purpose I/O pins. The PLL\_OUT pins support all I/O standards shown in Table 2–8.

The external clock outputs do not have their own  $V_{CC}$  and ground voltage supplies. Therefore, to minimize jitter, do not place switching I/O pins next to these output pins. The EP1C3 device in the 100-pin TQFP package

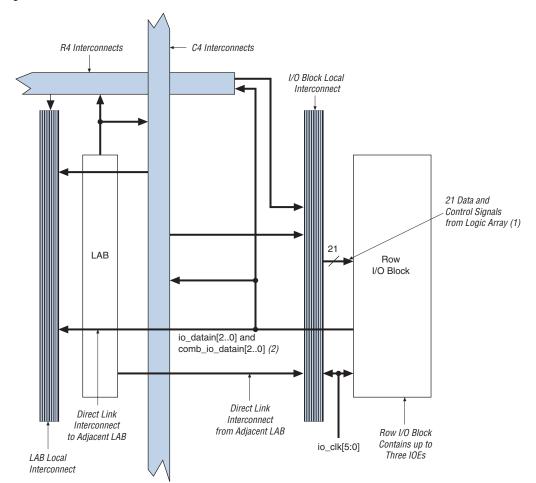

Figure 2-28. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–28:*

- (1) The 21 data and control signals consist of three data out lines, io\_dataout[2..0], three output enables, io\_coe[2..0], three input clock enables, io\_cce\_in[2..0], three output clock enables, io\_cce\_out[2..0], three clocks, io\_cclk[2..0], three asynchronous clear signals, io\_caclr[2..0], and three synchronous clear signals, io\_csclr[2..0].

- (2) Each of the three IOEs in the row I/O block can have one io\_datain input (combinatorial or registered) and one comb\_io\_datain (combinatorial) input.

to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output registers. Table 2–9 shows the programmable delays for Cyclone devices.

| Table 2–9. Cyclone Programmable Delay Chain |                                         |  |  |  |

|---------------------------------------------|-----------------------------------------|--|--|--|

| Programmable Delays Quartus II Logic Option |                                         |  |  |  |

| Input pin to logic array delay              | Decrease input delay to internal cells  |  |  |  |

| Input pin to input register delay           | Decrease input delay to input registers |  |  |  |

| Output pin delay                            | Increase delay to output pin            |  |  |  |

There are two paths in the IOE for a combinatorial input to reach the logic array. Each of the two paths can have a different delay. This allows you adjust delays from the pin to internal LE registers that reside in two different areas of the device. The designer sets the two combinatorial input delays by selecting different delays for two different paths under the **Decrease input delay to internal cells** logic option in the Quartus II software. When the input signal requires two different delays for the combinatorial input, the input register in the IOE is no longer available.

The IOE registers in Cyclone devices share the same source for clear or preset. The designer can program preset or clear for each individual IOE. The designer can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally a synchronous reset signal is available to the designer for the IOE registers.

# **External RAM Interfacing**

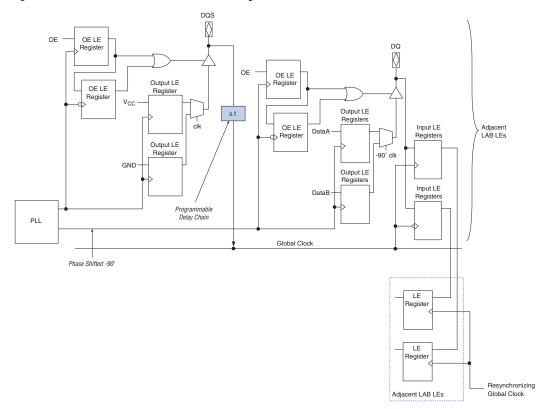

Cyclone devices support DDR SDRAM and FCRAM interfaces at up to 133 MHz through dedicated circuitry.

#### DDR SDRAM and FCRAM

Cyclone devices have dedicated circuitry for interfacing with DDR SDRAM. All I/O banks support DDR SDRAM and FCRAM I/O pins. However, the configuration input pins in bank 1 must operate at 2.5 V because the SSTL-2  $\rm V_{CCIO}$  level is 2.5 V. Additionally, the configuration

| Table 2–10. DQ Pin Groups (Part 2 of 2) |                      |                                |                       |  |  |  |  |

|-----------------------------------------|----------------------|--------------------------------|-----------------------|--|--|--|--|

| Device                                  | Package              | Number of × 8 DQ<br>Pin Groups | Total DQ Pin<br>Count |  |  |  |  |

| EP1C6                                   | 144-pin TQFP         | 4                              | 32                    |  |  |  |  |

|                                         | 240-pin PQFP         | 4                              | 32                    |  |  |  |  |

|                                         | 256-pin FineLine BGA | 4                              | 32                    |  |  |  |  |

| EP1C12                                  | 240-pin PQFP         | 4                              | 32                    |  |  |  |  |

|                                         | 256-pin FineLine BGA | 4                              | 32                    |  |  |  |  |

|                                         | 324-pin FineLine BGA | 8                              | 64                    |  |  |  |  |

| EP1C20                                  | 324-pin FineLine BGA | 8                              | 64                    |  |  |  |  |

|                                         | 400-pin FineLine BGA | 8                              | 64                    |  |  |  |  |

*Note to Table 2–10:*

EP1C3 devices in the 100-pin TQFP package do not have any DQ pin groups in I/O bank 1.

A programmable delay chain on each DQS pin allows for either a  $90^{\circ}$  phase shift (for DDR SDRAM), or a  $72^{\circ}$  phase shift (for FCRAM) which automatically center-aligns input DQS synchronization signals within the data window of their corresponding DQ data signals. The phase-shifted DQS signals drive the global clock network. This global DQS signal clocks DQ signals on internal LE registers.

These DQS delay elements combine with the PLL's clocking and phase shift ability to provide a complete hardware solution for interfacing to high-speed memory.

The clock phase shift allows the PLL to clock the DQ output enable and output paths. The designer should use the following guidelines to meet 133 MHz performance for DDR SDRAM and FCRAM interfaces:

- The DQS signal must be in the middle of the DQ group it clocks

- Resynchronize the incoming data to the logic array clock using successive LE registers or FIFO buffers

- LE registers must be placed in the LAB adjacent to the DQ I/O pin column it is fed by

Figure 2–34 illustrates DDR SDRAM and FCRAM interfacing from the I/O through the dedicated circuitry to the logic array.

Figure 2-34. DDR SDRAM and FCRAM Interfacing

# **Programmable Drive Strength**

The output buffer for each Cyclone device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standards have several levels of drive strength that the designer can control. SSTL-3 class I and II, and SSTL-2 class I and II support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/I_{OL}$

of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot. Table 2–11 shows the possible settings for the I/O standards with drive strength control.

| Table 2–11. Programmable Drive Strength Note (1) |                                                                |  |  |  |

|--------------------------------------------------|----------------------------------------------------------------|--|--|--|

| I/O Standard                                     | I <sub>OH</sub> /I <sub>OL</sub> Current Strength Setting (mA) |  |  |  |

| LVTTL (3.3 V)                                    | 4                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12                                                             |  |  |  |

|                                                  | 16                                                             |  |  |  |

|                                                  | 24(2)                                                          |  |  |  |

| LVCMOS (3.3 V)                                   | 2                                                              |  |  |  |

|                                                  | 4                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12(2)                                                          |  |  |  |

| LVTTL (2.5 V)                                    | 2                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12                                                             |  |  |  |

|                                                  | 16(2)                                                          |  |  |  |

| LVTTL (1.8 V)                                    | 2                                                              |  |  |  |

|                                                  | 8                                                              |  |  |  |

|                                                  | 12(2)                                                          |  |  |  |

| LVCMOS (1.5 V)                                   | 2                                                              |  |  |  |

|                                                  | 4                                                              |  |  |  |

|                                                  | 8(2)                                                           |  |  |  |

#### Notes to Table 2–11:

# **Open-Drain Output**

Cyclone devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

SSTL-3 class I and II, SSTL-2 class I and II, and 3.3-V PCI I/O Standards do not support programmable drive strength.

<sup>(2)</sup> This is the default current strength setting in the Quartus II software.

Each I/O bank can support multiple standards with the same  $V_{CCIO}$  for input and output pins. For example, when  $V_{CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

### LVDS I/O Pins

A subset of pins in all four I/O banks supports LVDS interfacing. These dual-purpose LVDS pins require an external-resistor network at the transmitter channels in addition to 100- $\Omega$  termination resistors on receiver channels. These pins do not contain dedicated serialization or deserialization circuitry; therefore, internal logic performs serialization and deserialization functions.

Table 2–13 shows the total number of supported LVDS channels per device density.

| Table 2–13. Cyclone Device LVDS Channels |           |                         |  |  |  |  |

|------------------------------------------|-----------|-------------------------|--|--|--|--|

| Device                                   | Pin Count | Number of LVDS Channels |  |  |  |  |

| EP1C3                                    | 100       | (1)                     |  |  |  |  |

|                                          | 144       | 34                      |  |  |  |  |

| EP1C4                                    | 324       | 103                     |  |  |  |  |

|                                          | 400       | 129                     |  |  |  |  |

| EP1C6                                    | 144       | 29                      |  |  |  |  |

|                                          | 240       | 72                      |  |  |  |  |

|                                          | 256       | 72                      |  |  |  |  |

| EP1C12                                   | 240       | 66                      |  |  |  |  |

|                                          | 256       | 72                      |  |  |  |  |

|                                          | 324       | 103                     |  |  |  |  |

| EP1C20                                   | 324       | 95                      |  |  |  |  |

|                                          | 400       | 129                     |  |  |  |  |

*Note to Table 2–13:*

### MultiVolt I/O Interface

The Cyclone architecture supports the MultiVolt I/O interface feature, which allows Cyclone devices in all packages to interface with systems of different supply voltages. The devices have one set of  $V_{CC}$  pins for internal operation and input buffers ( $V_{CCINT}$ ), and four sets for I/O output drivers ( $V_{CCIO}$ ).

EP1C3 devices in the 100-pin TQFP package do not support the LVDS I/O standard.

Typically, the user-mode current during device operation is lower than the power-up current in Table 4–17. Altera recommends using the Cyclone Power Calculator, available on the Altera web site, to estimate the user-mode  $I_{\text{CCINT}}$  consumption and then select power supplies or regulators based on the higher value.

# **Timing Model**

The DirectDrive technology and MultiTrack interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Cyclone device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

### **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus® II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–18 shows the status of the Cyclone device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 4–18. Cyclone Device Timing Model Status |             |       |  |  |  |  |

|------------------------------------------------|-------------|-------|--|--|--|--|

| Device                                         | Preliminary | Final |  |  |  |  |

| EP1C3                                          | _           | ✓     |  |  |  |  |

| EP1C4                                          | _           | ✓     |  |  |  |  |

| EP1C6                                          | _           | ✓     |  |  |  |  |

| EP1C12                                         | _           | ✓     |  |  |  |  |

| EP1C20                                         | _           | ✓     |  |  |  |  |

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–25 through 4–28 show the internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

| Table 4–25. LE Internal Timing Microparameters |       |     |       |     |       |     |      |

|------------------------------------------------|-------|-----|-------|-----|-------|-----|------|

| Cumbal                                         | -     | -6  |       | -7  |       | -8  |      |

| Symbol                                         | Min   | Max | Min   | Max | Min   | Max | Unit |

| t <sub>SU</sub>                                | 29    | _   | 33    | _   | 37    | _   | ps   |

| t <sub>H</sub>                                 | 12    | _   | 13    | _   | 15    | _   | ps   |

| t <sub>CO</sub>                                | _     | 173 | _     | 198 | _     | 224 | ps   |

| t <sub>LUT</sub>                               | _     | 454 | _     | 522 | _     | 590 | ps   |

| t <sub>CLR</sub>                               | 129   | _   | 148   | _   | 167   | _   | ps   |

| t <sub>PRE</sub>                               | 129   | _   | 148   | _   | 167   | _   | ps   |

| t <sub>CLKHL</sub>                             | 1,234 | _   | 1,562 | _   | 1,818 |     | ps   |

| Table 4–26. IOE Internal Timing Microparameters |       |       |       |       |       |       |      |

|-------------------------------------------------|-------|-------|-------|-------|-------|-------|------|

| Cumbal                                          | -     | 6     | -7    |       | -8    |       |      |

| Symbol                                          | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>SU</sub>                                 | 348   | _     | 400   | _     | 452   | _     | ps   |

| t <sub>H</sub>                                  | 0     | _     | 0     | _     | 0     | _     | ps   |

| t <sub>CO</sub>                                 | _     | 511   | _     | 587   | _     | 664   | ps   |

| t <sub>PIN2COMBOUT_R</sub>                      | _     | 1,130 | _     | 1,299 | _     | 1,469 | ps   |

| t <sub>PIN2COMBOUT_C</sub>                      | _     | 1,135 | _     | 1,305 | _     | 1,475 | ps   |

| t <sub>COMBIN2PIN_R</sub>                       | _     | 2,627 | _     | 3,021 | _     | 3,415 | ps   |

| t <sub>COMBIN2PIN_C</sub>                       | _     | 2,615 | _     | 3,007 | _     | 3,399 | ps   |

| t <sub>CLR</sub>                                | 280   | _     | 322   | _     | 364   | _     | ps   |

| t <sub>PRE</sub>                                | 280   | _     | 322   | _     | 364   | _     | ps   |

| t <sub>CLKHL</sub>                              | 1,234 | _     | 1,562 | _     | 1,818 | _     | ps   |

| Table 4–43. Cyclone I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 2 of 2) |       |         |          |         |          |         |         |      |

|---------------------------------------------------------------------------------------------------|-------|---------|----------|---------|----------|---------|---------|------|

| Ctond                                                                                             | aud   | -6 Spee | ed Grade | -7 Spec | ed Grade | -8 Spee | d Grade |      |

| Stand                                                                                             | aru   | Min     | Max      | Min     | Max      | Min     | Max     | Unit |

| 1.8-V LVTTL                                                                                       | 2 mA  | _       | 1,290    | _       | 1,483    | _       | 1,677   | ps   |

|                                                                                                   | 8 mA  | _       | 4        | _       | 4        | _       | 5       | ps   |

|                                                                                                   | 12 mA | _       | -208     | _       | -240     | _       | -271    | ps   |

| 1.5-V LVTTL                                                                                       | 2 mA  | _       | 2,288    | _       | 2,631    | _       | 2,974   | ps   |

|                                                                                                   | 4 mA  | _       | 608      | _       | 699      | _       | 790     | ps   |

|                                                                                                   | 8 mA  | _       | 292      | _       | 335      | _       | 379     | ps   |

| 3.3-V PCI (1)                                                                                     |       | _       | -877     | _       | -1,009   | _       | -1,141  | ps   |

| SSTL-3 class I                                                                                    |       | _       | -410     | _       | -472     | _       | -533    | ps   |

| SSTL-3 class I                                                                                    | I     | _       | -811     | _       | -933     | _       | -1,055  | ps   |

| SSTL-2 class I                                                                                    |       | _       | -485     | _       | -558     | _       | -631    | ps   |

| SSTL-2 class I                                                                                    | I     | _       | -758     | _       | -872     | _       | -986    | ps   |

| LVDS                                                                                              |       | _       | -998     | _       | -1,148   | _       | -1,298  | ps   |

| Table 4–44. Cyclone I/O Standard Output Delay Adders for Slow Slew Rate on Column Pins (Part 1 of 2) |       |                |       |                |       |                |       |      |

|------------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| I/O Standard                                                                                         |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       |      |

| 1/U Sta                                                                                              | nuaru | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| LVCMOS                                                                                               | 2 mA  | _              | 1,800 | _              | 2,070 | _              | 2,340 | ps   |

|                                                                                                      | 4 mA  | _              | 1,311 | _              | 1,507 | _              | 1,704 | ps   |

|                                                                                                      | 8 mA  | _              | 945   | _              | 1,086 | _              | 1,228 | ps   |

|                                                                                                      | 12 mA | _              | 807   | _              | 928   | _              | 1,049 | ps   |

| 3.3-V LVTTL                                                                                          | 4 mA  | _              | 1,831 | _              | 2,105 | _              | 2,380 | ps   |

|                                                                                                      | 8 mA  | _              | 1,484 | _              | 1,705 | _              | 1,928 | ps   |

|                                                                                                      | 12 mA | _              | 973   | _              | 1,118 | _              | 1,264 | ps   |

|                                                                                                      | 16 mA | _              | 1,012 | _              | 1,163 | _              | 1,315 | ps   |

|                                                                                                      | 24 mA | _              | 838   | _              | 963   | _              | 1,089 | ps   |

| 2.5-V LVTTL                                                                                          | 2 mA  | _              | 2,747 | _              | 3,158 | _              | 3,570 | ps   |

|                                                                                                      | 8 mA  | _              | 1,757 | _              | 2,019 | _              | 2,283 | ps   |

|                                                                                                      | 12 mA | _              | 1,763 | _              | 2,026 | _              | 2,291 | ps   |

|                                                                                                      | 16 mA | _              | 1,623 | _              | 1,865 | _              | 2,109 | ps   |

| 1.8-V LVTTL                                                                                          | 2 mA  | _              | 5,506 | _              | 6,331 | _              | 7,157 | ps   |

|                                                                                                      | 8 mA  | _              | 4,220 | _              | 4,852 | _              | 5,485 | ps   |

|                                                                                                      | 12 mA | _              | 4,008 | _              | 4,608 | _              | 5,209 | ps   |

| Table 4–52. Cyclone PLL Specifications (Part 2 of 2) |                                                        |        |          |         |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------|--------|----------|---------|--|--|--|--|

| Symbol                                               | Parameter                                              | Min    | Max      | Unit    |  |  |  |  |

| f <sub>OUT</sub> (to global clock)                   | PLL output frequency<br>(-6 speed grade)               | 15.625 | 405      | MHz     |  |  |  |  |

|                                                      | PLL output frequency<br>(-7 speed grade)               | 15.625 | 320      | MHz     |  |  |  |  |

|                                                      | PLL output frequency<br>(-8 speed grade)               | 15.625 | 275      | MHz     |  |  |  |  |

| t <sub>OUT</sub> DUTY                                | Duty cycle for external clock output (when set to 50%) | 45.00  | 55       | %       |  |  |  |  |

| t <sub>JITTER</sub> (1)                              | Period jitter for external clock output                | _      | ±300 (2) | ps      |  |  |  |  |

| t <sub>LOCK</sub> (3)                                | Time required to lock from end of device configuration | 10.00  | 100      | μs      |  |  |  |  |

| f <sub>vco</sub>                                     | PLL internal VCO operating range                       | 500.00 | 1,000    | MHz     |  |  |  |  |

| -                                                    | Minimum areset time                                    | 10     | _        | ns      |  |  |  |  |

| N, G0, G1, E                                         | Counter values                                         | 1      | 32       | integer |  |  |  |  |

#### Notes to Table 4-52:

- (1) The t<sub>JITTER</sub> specification for the PLL[2..1]\_OUT pins are dependent on the I/O pins in its V<sub>CCIO</sub> bank, how many of them are switching outputs, how much they toggle, and whether or not they use programmable current strength or slow slew rate.

- (2)  $f_{OUT} \ge 100$  MHz. When the PLL external clock output frequency ( $f_{OUT}$ ) is smaller than 100 MHz, the jitter specification is 60 mUI.

- (3)  $f_{IN/N}$  must be greater than 200 MHz to ensure correct lock detect circuit operation below -20 C. Otherwise, the PLL operates with the specified parameters under the specified conditions.

| July 2003<br>v1.1 | Updated timing information. Timing finalized for EP1C6 and EP1C20 devices. Updated performance information. Added PLL Timing section. | _ |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|---|

| May 2003<br>v1.0  | Added document to Cyclone Device Handbook.                                                                                            | _ |

| February 2005<br>v1.1 | Updated Figure 5-1.                        | _ |

|-----------------------|--------------------------------------------|---|

| May 2003<br>v1.0      | Added document to Cyclone Device Handbook. | _ |