Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 598                                                     |

| Number of Logic Elements/Cells | 5980                                                    |

| Total RAM Bits                 | 92160                                                   |

| Number of I/O                  | 185                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 240-BFQFP                                               |

| Supplier Device Package        | 240-PQFP (32x32)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1c6q240c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 2-1. Cyclone EP1C12 Device Block Diagram

The number of M4K RAM blocks, PLLs, rows, and columns vary per device. Table 2–1 lists the resources available in each Cyclone device.

| Table 2–1. Cyclone Device Resources |         |        |      |               |           |  |  |  |  |  |

|-------------------------------------|---------|--------|------|---------------|-----------|--|--|--|--|--|

| Device                              | M4K     | RAM    | PLLs | LAB Columns   | LAP Pouro |  |  |  |  |  |

| Device                              | Columns | Blocks | PLLS | LAD CUIUIIIIS | LAB Rows  |  |  |  |  |  |

| EP1C3                               | 1       | 13     | 1    | 24            | 13        |  |  |  |  |  |

| EP1C4                               | 1       | 17     | 2    | 26            | 17        |  |  |  |  |  |

| EP1C6                               | 1       | 20     | 2    | 32            | 20        |  |  |  |  |  |

| EP1C12                              | 2       | 52     | 2    | 48            | 26        |  |  |  |  |  |

| EP1C20                              | 2       | 64     | 2    | 64            | 32        |  |  |  |  |  |

performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

Direct link interconnect from

left LAB, M4K memory

block, PLL, or IOE output

Direct link

interconnect

to left

Local

Interconnect

Local

Interconnect

Direct link interconnect from

right LAB, M4K memory

block, PLL, or IOE output

Direct link

interconnect

to right

Figure 2-3. Direct Link Connection

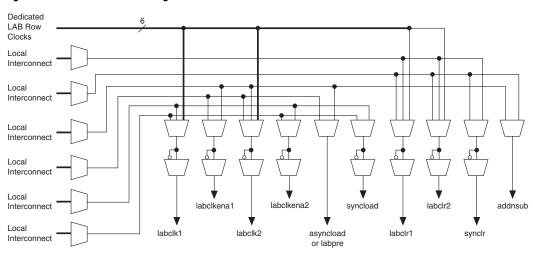

#### **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, synchronous load, and add/subtract control signals. This gives a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal will also use labclkenal. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal will turn off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous load acts as a preset when the asynchronous load data input is tied high.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

### **Logic Elements**

The smallest unit of logic in the Cyclone architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by a LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

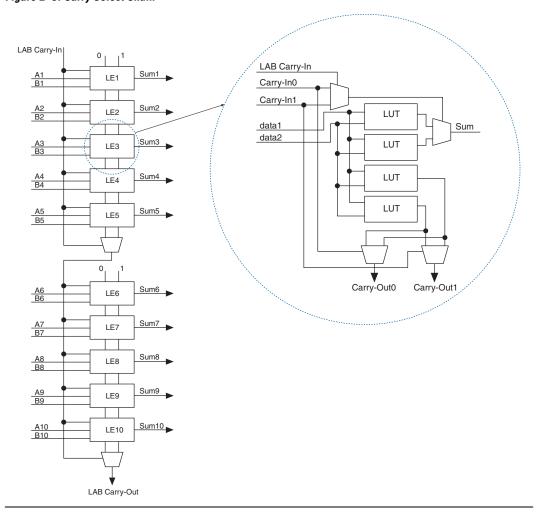

Figure 2–8 shows the carry-select circuitry in a LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. A LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

Figure 2-8. Carry Select Chain

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to M4K memory blocks. A carry chain can continue as far as a full column.

#### Clear and Preset Logic Control

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Cyclone devices support simultaneous preset/asynchronous load and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Cyclone devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

## MultiTrack Interconnect

In the Cyclone architecture, connections between LEs, M4K memory blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive<sup>TM</sup> technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when

## Embedded Memory

The Cyclone embedded memory consists of columns of M4K memory blocks. EP1C3 and EP1C6 devices have one column of M4K blocks, while EP1C12 and EP1C20 devices have two columns (refer to Table 1–1 on page 1–1 for total RAM bits per density). Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 250 MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Mixed clock mode

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

#### **Memory Modes**

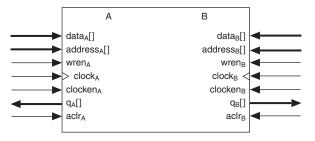

The M4K memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2–12. True Dual-Port Memory Configuration

#### Read/Write Clock Mode

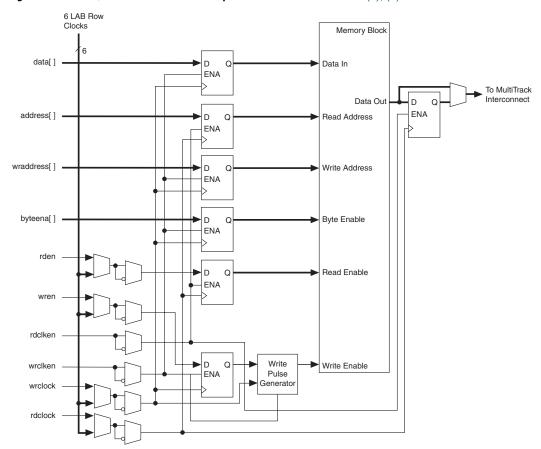

The M4K memory blocks implement read/write clock mode for simple dual-port memory. You can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 2–20 shows a memory block in read/write clock mode.

Figure 2–20. Read/Write Clock Mode in Simple Dual-Port Mode Notes (1), (2)

#### *Notes to Figure 2–20:*

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

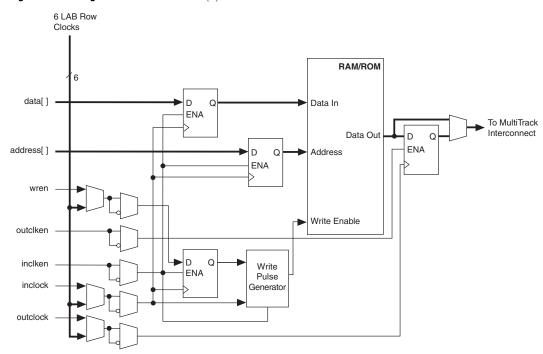

#### **Single-Port Mode**

The M4K memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–21. A single M4K memory block can support up to two single-port mode RAM blocks if each RAM block is less than or equal to 2K bits in size.

Figure 2–21. Single-Port Mode Note (1)

Note to Figure 2–21:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

## Global Clock Network and Phase-Locked Loops

Cyclone devices provide a global clock network and up to two PLLs for a complete clock management solution.

#### **Global Clock Network**

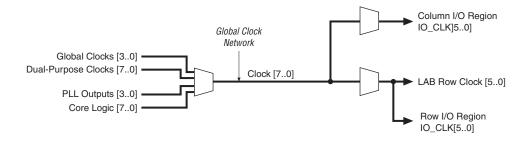

There are four dedicated clock pins (CLK[3..0], two pins on the left side and two pins on the right side) that drive the global clock network, as shown in Figure 2–22. PLL outputs, logic array, and dual-purpose clock (DPCLK[7..0]) pins can also drive the global clock network.

#### **Dual-Purpose Clock Pins**

Each Cyclone device except the EP1C3 device has eight dual-purpose clock pins, DPCLK[7..0] (two on each I/O bank). EP1C3 devices have five DPCLK pins in the 100-pin TQFP package. These dual-purpose pins can connect to the global clock network (see Figure 2–22) for high-fanout control signals such as clocks, asynchronous clears, presets, and clock enables, or protocol control signals such as TRDY and IRDY for PCI, or DQS signals for external memory interfaces.

#### **Combined Resources**

Each Cyclone device contains eight distinct dedicated clocking resources. The device uses multiplexers with these clocks to form six-bit buses to drive LAB row clocks, column IOE clocks, or row IOE clocks. See Figure 2–23. Another multiplexer at the LAB level selects two of the six LAB row clocks to feed the LE registers within the LAB.

Figure 2-23. Global Clock Network Multiplexers

IOE clocks have row and column block regions. Six of the eight global clock resources feed to these row and column regions. Figure 2–24 shows the I/O clock regions.

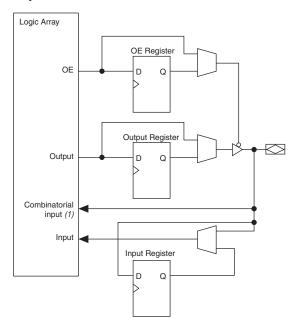

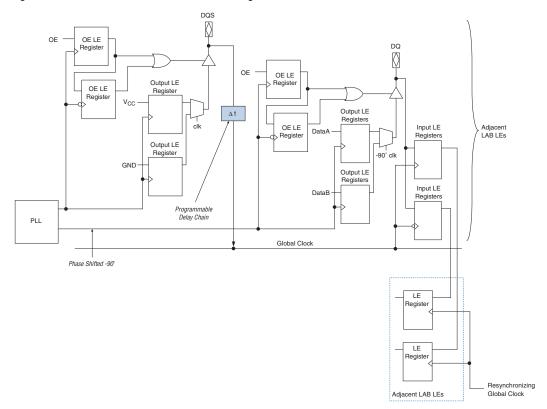

Figure 2-27. Cyclone IOE Structure

Note to Figure 2-27:

There are two paths available for combinatorial inputs to the logic array. Each path contains a unique programmable delay chain.

The IOEs are located in I/O blocks around the periphery of the Cyclone device. There are up to three IOEs per row I/O block and up to three IOEs per column I/O block (column I/O blocks span two columns). The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–28 shows how a row I/O block connects to the logic array. Figure 2–29 shows how a column I/O block connects to the logic array.

Figure 2-34. DDR SDRAM and FCRAM Interfacing

## **Programmable Drive Strength**

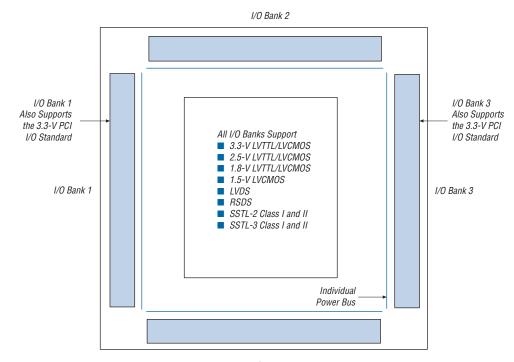

The output buffer for each Cyclone device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standards have several levels of drive strength that the designer can control. SSTL-3 class I and II, and SSTL-2 class I and II support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/I_{OL}$

and DM pins to support a DDR SDRAM or FCRAM interface. I/O bank 1 can also support a DDR SDRAM or FCRAM interface, however, the configuration input pins in I/O bank 1 must operate at 2.5 V. I/O bank 3 can also support a DDR SDRAM or FCRAM interface, however, all the JTAG pins in I/O bank 3 must operate at 2.5 V.

**Figure 2–35. Cyclone I/O Banks** Notes (1), (2)

I/O Bank 4

#### *Notes to Figure 2–35:*

- (1) Figure 2–35 is a top view of the silicon die.

- (2) Figure 2–35 is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced standards (e.g., SSTL-3) independently. If an I/O bank does not use voltage-referenced standards, the  $V_{\rm REF}$  pins are available as user I/O pins.

Figure 3-1. Cyclone JTAG Waveforms TMS TDI TCK t <sub>JPXZ</sub> t<sub>JPZX</sub> t<sub>JPCO</sub> TDO t<sub>JSH</sub> t<sub>JSSU</sub> Signal to Be Captured t<sub>JSCO</sub> t<sub>JSXZ</sub> t<sub>JSZX</sub> -Signal to Be Driven

Figure 3–1 shows the timing requirements for the JTAG signals.

Table 3–4 shows the JTAG timing parameters and values for Cyclone devices.

| Table 3-          | Table 3–4. Cyclone JTAG Timing Parameters and Values |     |     |      |  |  |  |  |  |  |

|-------------------|------------------------------------------------------|-----|-----|------|--|--|--|--|--|--|

| Symbol            | Parameter                                            | Min | Max | Unit |  |  |  |  |  |  |

| $t_{JCP}$         | TCK clock period                                     | 100 | _   | ns   |  |  |  |  |  |  |

| t <sub>JCH</sub>  | TCK clock high time                                  | 50  | _   | ns   |  |  |  |  |  |  |

| t <sub>JCL</sub>  | TCK clock low time                                   | 50  | _   | ns   |  |  |  |  |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                                 | 20  | _   | ns   |  |  |  |  |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                                  | 45  | _   | ns   |  |  |  |  |  |  |

| t <sub>JPCO</sub> | JTAG port clock to output                            | _   | 25  | ns   |  |  |  |  |  |  |

| $t_{JPZX}$        | JTAG port high impedance to valid output             | _   | 25  | ns   |  |  |  |  |  |  |

| $t_{JPXZ}$        | JTAG port valid output to high impedance             | _   | 25  | ns   |  |  |  |  |  |  |

| t <sub>JSSU</sub> | Capture register setup time                          | 20  | _   | ns   |  |  |  |  |  |  |

| t <sub>JSH</sub>  | Capture register hold time                           | 45  | _   | ns   |  |  |  |  |  |  |

| $t_{\text{JSCO}}$ | Update register clock to output                      | _   | 35  | ns   |  |  |  |  |  |  |

| t <sub>JSZX</sub> | Update register high impedance to valid output       | _   | 35  | ns   |  |  |  |  |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance       | _   | 35  | ns   |  |  |  |  |  |  |

| Table 4–5. LVCMOS Specifications |                           |                                              |                         |         |      |  |  |  |  |  |

|----------------------------------|---------------------------|----------------------------------------------|-------------------------|---------|------|--|--|--|--|--|

| Symbol                           | Parameter                 | Conditions                                   | Minimum                 | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                | Output supply voltage     | _                                            | 3.0                     | 3.6     | V    |  |  |  |  |  |

| V <sub>IH</sub>                  | High-level input voltage  | _                                            | 1.7                     | 4.1     | V    |  |  |  |  |  |

| $V_{IL}$                         | Low-level input voltage   | _                                            | -0.5                    | 0.7     | V    |  |  |  |  |  |

| V <sub>OH</sub>                  | High-level output voltage | $V_{CCIO} = 3.0,$ $I_{OH} = -0.1 \text{ mA}$ | V <sub>CCIO</sub> - 0.2 | _       | V    |  |  |  |  |  |

| V <sub>OL</sub>                  | Low-level output voltage  | $V_{CCIO} = 3.0,$ $I_{OL} = 0.1 \text{ mA}$  | _                       | 0.2     | V    |  |  |  |  |  |

| Table 4–6.        | 2.5-V I/O Specifications  |                                                |         |         |      |

|-------------------|---------------------------|------------------------------------------------|---------|---------|------|

| Symbol            | Parameter                 | Conditions                                     | Minimum | Maximum | Unit |

| V <sub>CCIO</sub> | Output supply voltage     | _                                              | 2.375   | 2.625   | V    |

| V <sub>IH</sub>   | High-level input voltage  | _                                              | 1.7     | 4.1     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _                                              | -0.5    | 0.7     | V    |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OH</sub> = -0.1 mA                      | 2.1     | _       | V    |

|                   |                           | $I_{OH} = -1 \text{ mA}$                       | 2.0     | _       | V    |

|                   |                           | $I_{OH} = -2 \text{ to } -16 \text{ mA } (11)$ | 1.7     | _       | V    |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 0.1 mA                       | _       | 0.2     | V    |

|                   |                           | I <sub>OH</sub> = 1 mA                         | _       | 0.4     | V    |

|                   |                           | I <sub>OH</sub> = 2 to 16 mA (11)              |         | 0.7     | V    |

| Table 4–7. 1.8-V I/O Specifications |                           |                                               |                             |                             |      |  |  |  |  |  |

|-------------------------------------|---------------------------|-----------------------------------------------|-----------------------------|-----------------------------|------|--|--|--|--|--|

| Symbol                              | Parameter                 | Conditions                                    | Minimum                     | Maximum                     | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     | _                                             | 1.65                        | 1.95                        | V    |  |  |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  | _                                             | 0.65 ×<br>V <sub>CCIO</sub> | 2.25 (12)                   | V    |  |  |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   | _                                             | -0.3                        | 0.35 ×<br>V <sub>CCIO</sub> | V    |  |  |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ to } -8 \text{ mA } (11)$ | V <sub>CCIO</sub> - 0.45    | _                           | V    |  |  |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 to 8 mA (11)              | _                           | 0.45                        | V    |  |  |  |  |  |

| Table 4–36. Parameters |         |         | n Global ( | Clock Exte | rnal I/O Ti | iming   |       |

|------------------------|---------|---------|------------|------------|-------------|---------|-------|

| Symbol                 | -6 Spee | d Grade | -7 Spee    | d Grade    | -8 Spee     | d Grade | Unit  |

| Syllibul               | Min     | Max     | Min        | Max        | Min         | Max     | Ullit |

0.000

0.500

1.913

0.000

0.500

ns

ns

2.164

0.000

0.500

1.663

tinhpll

$t_{\text{OUTCOPLL}}$

| Table 4–37. EP1C12 Row Pin Global Clock External I/O Timing Parameters |         |         |         |         |         |         |      |  |  |

|------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|------|--|--|

| Cumbal                                                                 | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | Hait |  |  |

| Symbol                                                                 | Min     | Max     | Min     | Max     | Min     | Max     | Unit |  |  |

| t <sub>INSU</sub>                                                      | 2.620   | _       | 3.012   | _       | 3.404   | _       | ns   |  |  |

| t <sub>INH</sub>                                                       | 0.000   | _       | 0.000   | _       | 0.000   | _       | ns   |  |  |

| toutco                                                                 | 2.000   | 3.671   | 2.000   | 4.221   | 2.000   | 4.774   | ns   |  |  |

| t <sub>INSUPLL</sub>                                                   | 1.698   | _       | 1.951   | _       | 2.206   | _       | ns   |  |  |

| t <sub>INHPLL</sub>                                                    | 0.000   | _       | 0.000   | _       | 0.000   | _       | ns   |  |  |

| toutcople                                                              | 0.500   | 1.536   | 0.500   | 1.767   | 0.500   | 1.998   | ns   |  |  |

Tables 4–38 through 4–39 show the external timing parameters on column and row pins for EP1C20 devices.

| Table 4–38. EP1C20 Column Pin Global Clock External I/O Timing<br>Parameters |         |         |         |         |         |                |      |  |  |  |

|------------------------------------------------------------------------------|---------|---------|---------|---------|---------|----------------|------|--|--|--|

| Cumbal                                                                       | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | -8 Speed Grade |      |  |  |  |

| Symbol                                                                       | Min     | Max     | Min     | Max     | Min     | Max            | Unit |  |  |  |

| t <sub>INSU</sub>                                                            | 2.417   | _       | 2.779   | _       | 3.140   | _              | ns   |  |  |  |

| t <sub>INH</sub>                                                             | 0.000   | _       | 0.000   | _       | 0.000   | _              | ns   |  |  |  |

| t <sub>outco</sub>                                                           | 2.000   | 3.724   | 2.000   | 4.282   | 2.000   | 4.843          | ns   |  |  |  |

| t <sub>INSUPLL</sub>                                                         | 1.417   | _       | 1.629   | _       | 1.840   | _              | ns   |  |  |  |

| t <sub>INHPLL</sub>                                                          | 0.000   | _       | 0.000   | _       | 0.000   | _              | ns   |  |  |  |

| toutcople                                                                    | 0.500   | 1.667   | 0.500   | 1.917   | 0.500   | 2.169          | ns   |  |  |  |

| Table 4–43. Cyclone I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 2 of 2) |       |         |          |         |          |         |         |      |  |

|---------------------------------------------------------------------------------------------------|-------|---------|----------|---------|----------|---------|---------|------|--|

| Ctond                                                                                             | aud   | -6 Spee | ed Grade | -7 Spec | ed Grade | -8 Spee | d Grade |      |  |

| Stand                                                                                             | aru   | Min     | Max      | Min     | Max      | Min     | Max     | Unit |  |

| 1.8-V LVTTL                                                                                       | 2 mA  | _       | 1,290    | _       | 1,483    | _       | 1,677   | ps   |  |

|                                                                                                   | 8 mA  | _       | 4        | _       | 4        | _       | 5       | ps   |  |

|                                                                                                   | 12 mA | _       | -208     | _       | -240     | _       | -271    | ps   |  |

| 1.5-V LVTTL                                                                                       | 2 mA  | _       | 2,288    | _       | 2,631    | _       | 2,974   | ps   |  |

|                                                                                                   | 4 mA  | _       | 608      | _       | 699      | _       | 790     | ps   |  |

|                                                                                                   | 8 mA  | _       | 292      | _       | 335      | _       | 379     | ps   |  |

| 3.3-V PCI (1)                                                                                     |       | _       | -877     | _       | -1,009   | _       | -1,141  | ps   |  |

| SSTL-3 class I                                                                                    |       | _       | -410     | _       | -472     | _       | -533    | ps   |  |

| SSTL-3 class I                                                                                    | I     | _       | -811     | _       | -933     | _       | -1,055  | ps   |  |

| SSTL-2 class I                                                                                    |       | _       | -485     | _       | -558     | _       | -631    | ps   |  |

| SSTL-2 class I                                                                                    | I     | _       | -758     | _       | -872     | _       | -986    | ps   |  |

| LVDS                                                                                              |       | _       | -998     | _       | -1,148   | _       | -1,298  | ps   |  |

| Table 4–44. Cyclone I/O Standard Output Delay Adders for Slow Slew Rate on Column Pins (Part 1 of 2) |       |                |       |        |                |     |                |      |  |

|------------------------------------------------------------------------------------------------------|-------|----------------|-------|--------|----------------|-----|----------------|------|--|

| 1/0 Sto                                                                                              | ndoud | -6 Speed Grade |       | -7 Spe | -7 Speed Grade |     | -8 Speed Grade |      |  |

| I/O Standard                                                                                         |       | Min            | Max   | Min    | Max            | Min | Max            | Unit |  |

| LVCMOS                                                                                               | 2 mA  | _              | 1,800 | _      | 2,070          | _   | 2,340          | ps   |  |

|                                                                                                      | 4 mA  | _              | 1,311 | _      | 1,507          | _   | 1,704          | ps   |  |

|                                                                                                      | 8 mA  | _              | 945   | _      | 1,086          | _   | 1,228          | ps   |  |

|                                                                                                      | 12 mA | _              | 807   | _      | 928            | _   | 1,049          | ps   |  |

| 3.3-V LVTTL                                                                                          | 4 mA  | _              | 1,831 | _      | 2,105          | _   | 2,380          | ps   |  |

|                                                                                                      | 8 mA  | _              | 1,484 | _      | 1,705          | _   | 1,928          | ps   |  |

|                                                                                                      | 12 mA | _              | 973   | _      | 1,118          | _   | 1,264          | ps   |  |

|                                                                                                      | 16 mA | _              | 1,012 | _      | 1,163          | _   | 1,315          | ps   |  |

|                                                                                                      | 24 mA | _              | 838   | _      | 963            | _   | 1,089          | ps   |  |

| 2.5-V LVTTL                                                                                          | 2 mA  | _              | 2,747 | _      | 3,158          | _   | 3,570          | ps   |  |

|                                                                                                      | 8 mA  | _              | 1,757 | _      | 2,019          | _   | 2,283          | ps   |  |

|                                                                                                      | 12 mA | _              | 1,763 | _      | 2,026          | _   | 2,291          | ps   |  |

|                                                                                                      | 16 mA | _              | 1,623 | _      | 1,865          | _   | 2,109          | ps   |  |

| 1.8-V LVTTL                                                                                          | 2 mA  | _              | 5,506 | _      | 6,331          | _   | 7,157          | ps   |  |

|                                                                                                      | 8 mA  | _              | 4,220 | _      | 4,852          | _   | 5,485          | ps   |  |

|                                                                                                      | 12 mA | _              | 4,008 | _      | 4,608          | _   | 5,209          | ps   |  |

| Table 4–45. Cyclone I/O Standard Output Delay Adders for Slow Slew Rate on Row Pins (Part 2 of 2) |         |          |         |          |         |          |      |  |  |

|---------------------------------------------------------------------------------------------------|---------|----------|---------|----------|---------|----------|------|--|--|

| I/O Standard                                                                                      | -6 Spec | ed Grade | -7 Spec | ed Grade | -8 Spee | II m i A |      |  |  |

|                                                                                                   | Min     | Max      | Min     | Max      | Min     | Max      | Unit |  |  |

| SSTL-3 class I                                                                                    | _       | 1,390    | _       | 1,598    | _       | 1,807    | ps   |  |  |

| SSTL-3 class II                                                                                   | _       | 989      | _       | 1,137    | _       | 1,285    | ps   |  |  |

| SSTL-2 class I                                                                                    | _       | 1,965    | _       | 2,259    | _       | 2,554    | ps   |  |  |

| SSTL-2 class II                                                                                   | _       | 1,692    | _       | 1,945    | _       | 2,199    | ps   |  |  |

| LVDS                                                                                              | _       | 802      | _       | 922      | _       | 1,042    | ps   |  |  |

*Note to Tables 4–40 through 4–45:*

Tables 4–46 through 4–47 show the adder delays for the IOE programmable delays. These delays are controlled with the Quartus II software options listed in the Parameter column.

| Parameter                              | Setting | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Unit  |

|----------------------------------------|---------|----------------|-------|----------------|-------|----------------|-------|-------|

|                                        |         | Min            | Max   | Min            | Max   | Min            | Max   | UIIIL |

| Decrease input delay to internal cells | Off     | _              | 155   | _              | 178   | _              | 201   | ps    |

|                                        | Small   | _              | 2,122 | _              | 2,543 | _              | 2,875 | ps    |

|                                        | Medium  | _              | 2,639 | _              | 3,034 | _              | 3,430 | ps    |

|                                        | Large   | _              | 3,057 | _              | 3,515 | _              | 3,974 | ps    |

|                                        | On      | _              | 155   | _              | 178   | _              | 201   | ps    |

| Decrease input delay to input register | Off     | _              | 0     | _              | 0     | _              | 0     | ps    |

|                                        | On      | _              | 3,057 | _              | 3,515 | _              | 3,974 | ps    |

| Increase delay to output pin           | Off     | _              | 0     | _              | 0     | _              | 0     | ps    |

|                                        | On      | _              | 552   | _              | 634   | _              | 717   | ps    |

<sup>(1)</sup> EP1C3 devices do not support the PCI I/O standard.

| Table 4–52. Cyclone PLL Specifications (Part 2 of 2) |                                                        |        |          |         |  |  |  |

|------------------------------------------------------|--------------------------------------------------------|--------|----------|---------|--|--|--|

| Symbol                                               | Symbol Parameter                                       |        | Max      | Unit    |  |  |  |

| f <sub>OUT</sub> (to global clock)                   | PLL output frequency<br>(-6 speed grade)               | 15.625 | 405      | MHz     |  |  |  |

|                                                      | PLL output frequency<br>(-7 speed grade)               | 15.625 | 320      | MHz     |  |  |  |

|                                                      | PLL output frequency<br>(-8 speed grade)               | 15.625 | 275      | MHz     |  |  |  |

| t <sub>OUT</sub> DUTY                                | Duty cycle for external clock output (when set to 50%) | 45.00  | 55       | %       |  |  |  |

| t <sub>JITTER</sub> (1)                              | Period jitter for external clock output                | _      | ±300 (2) | ps      |  |  |  |

| t <sub>LOCK</sub> (3)                                | Time required to lock from end of device configuration | 10.00  | 100      | μs      |  |  |  |

| f <sub>vco</sub>                                     | PLL internal VCO operating range                       | 500.00 | 1,000    | MHz     |  |  |  |

| -                                                    | Minimum areset time                                    | 10     | _        | ns      |  |  |  |

| N, G0, G1, E                                         | Counter values                                         | 1      | 32       | integer |  |  |  |

#### Notes to Table 4-52:

- (1) The t<sub>JITTER</sub> specification for the PLL[2..1]\_OUT pins are dependent on the I/O pins in its V<sub>CCIO</sub> bank, how many of them are switching outputs, how much they toggle, and whether or not they use programmable current strength or slow slew rate.

- (2)  $f_{OUT} \ge 100$  MHz. When the PLL external clock output frequency ( $f_{OUT}$ ) is smaller than 100 MHz, the jitter specification is 60 mUI.

- (3)  $f_{IN/N}$  must be greater than 200 MHz to ensure correct lock detect circuit operation below -20 C. Otherwise, the PLL operates with the specified parameters under the specified conditions.

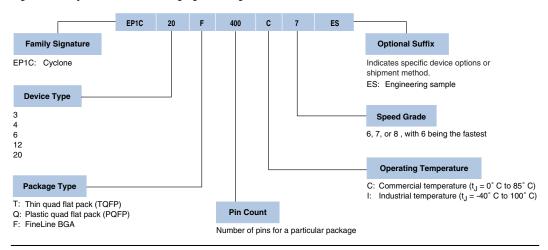

Figure 5-1. Cyclone Device Packaging Ordering Information

# Referenced Documents

This chapter references the following documents:

- Package Information for Cyclone Devices chapter in the Cyclone Device Handbook

- Quartus II Handbook

## Document Revision History

Table 5–1 shows the revision history for this chapter.

| Table 5–1. Document Revision History |                                                                        |                    |  |  |  |

|--------------------------------------|------------------------------------------------------------------------|--------------------|--|--|--|

| Date and<br>Document<br>Version      | Changes Made                                                           | Summary of Changes |  |  |  |

| May 2008<br>v1.4                     | Minor textual and style changes. Added "Referenced Documents" section. | _                  |  |  |  |

| January 2007<br>v1.3                 | Added document revision history.                                       | _                  |  |  |  |

| August 2005<br>v1.2                  | Minor updates.                                                         | _                  |  |  |  |