Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 598                                                     |

| Number of Logic Elements/Cells | 5980                                                    |

| Total RAM Bits                 | 92160                                                   |

| Number of I/O                  | 98                                                      |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 144-LQFP                                                |

| Supplier Device Package        | 144-TQFP (20x20)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1c6t144c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

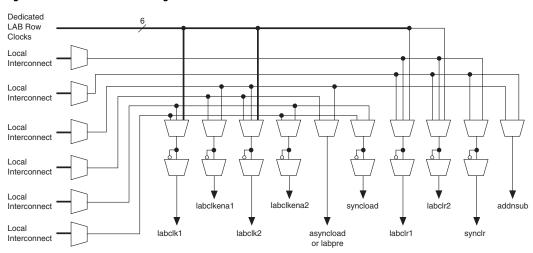

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

# **Logic Elements**

The smallest unit of logic in the Cyclone architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by a LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

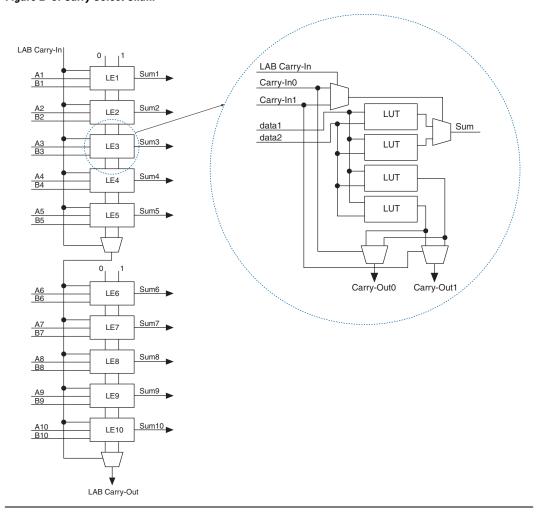

Figure 2–8 shows the carry-select circuitry in a LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. A LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

Figure 2-8. Carry Select Chain

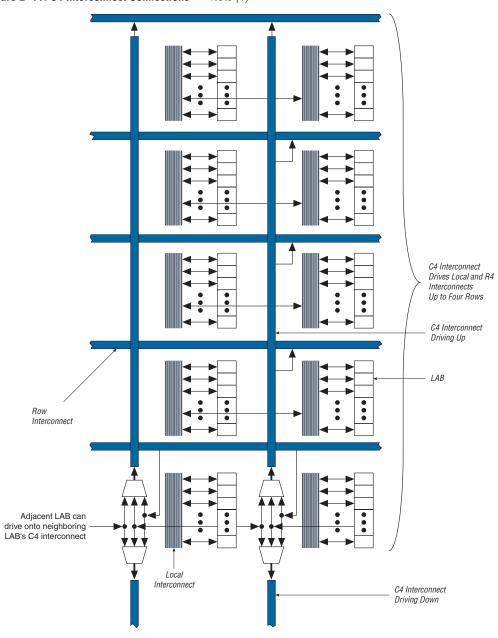

Figure 2–11. C4 Interconnect Connections Note (1)

Note to Figure 2–11:

(1) Each C4 interconnect can drive either up or down four rows.

| Table 2–7. Global Clock Network Sources (Part 2 of 2) |            |          |          |          |          |          |          |          |          |  |

|-------------------------------------------------------|------------|----------|----------|----------|----------|----------|----------|----------|----------|--|

| Sou                                                   | rce        | GCLKO    | GCLK1    | GCLK2    | GCLK3    | GCLK4    | GCLK5    | GCLK6    | GCLK7    |  |

| Dual-Purpose                                          | DPCLK0 (3) | _        | _        | _        | <b>✓</b> | _        | _        | _        | _        |  |

| Clock Pins                                            | DPCLK1 (3) | _        | _        | <b>✓</b> | _        | _        | _        | _        | _        |  |

|                                                       | DPCLK2     | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        |  |

|                                                       | DPCLK3     | _        | _        | _        | _        | <b>✓</b> | _        | _        | _        |  |

|                                                       | DPCLK4     |          | _        | _        | _        | _        |          | <b>✓</b> | _        |  |

|                                                       | DPCLK5 (3) | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> |  |

|                                                       | DPCLK6     | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        |  |

|                                                       | DPCLK7     | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        |  |

Notes to Table 2-7:

- (1) EP1C3 devices only have one PLL (PLL 1).

- (2) EP1C3 devices in the 100-pin TQFP package do not have dedicated clock pins CLK1 and CLK3.

- (3) EP1C3 devices in the 100-pin TQFP package do not have the DPCLK0, DPCLK1, or DPCLK5 pins.

### **Clock Multiplication and Division**

Cyclone PLLs provide clock synthesis for PLL output ports using  $m/(n \times post$  scale counter) scaling factors. The input clock is divided by a pre-scale divider, n, and is then multiplied by the m feedback factor. The control loop drives the VCO to match  $f_{\rm IN} \times (m/n)$ . Each output port has a unique post-scale counter to divide down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO is set to the least-common multiple of the output frequencies that meets its frequency specifications. Then, the post-scale dividers scale down the output frequency for each output port. For example, if the output frequencies required from one PLL are 33 and 66 MHz, the VCO is set to 330 MHz (the least-common multiple in the VCO's range).

Each PLL has one pre-scale divider, n, that can range in value from 1 to 32. Each PLL also has one multiply divider, m, that can range in value from 2 to 32. Global clock outputs have two post scale G dividers for global clock outputs, and external clock outputs have an E divider for external clock output, both ranging from 1 to 32. The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered.

## **Programmable Duty Cycle**

The programmable duty cycle allows PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each PLL post-scale counter (g0, g1, e). The duty cycle setting is achieved by a low- and high-time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

## **Control Signals**

There are three control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and the ability to gate PLL output clocks for low-power applications.

The pllenable signal enables and disables PLLs. When the pllenable signal is low, the clock output ports are driven by ground and all the PLLs go out of lock. When the pllenable signal goes high again, the PLLs relock and resynchronize to the input clocks. An input pin or LE output can drive the pllenable signal.

The areset signals are reset/resynchronization inputs for each PLL. Cyclone devices can drive these input signals from input pins or from LEs. When areset is driven high, the PLL counters will reset, clearing the PLL output and placing the PLL out of lock. When driven low again, the PLL will resynchronize to its input as it relocks.

The pfdena signals control the phase frequency detector (PFD) output with a programmable gate. If you disable the PFD, the VCO will operate at its last set value of control voltage and frequency with some drift, and the system will continue running when the PLL goes out of lock or the input clock disables. By maintaining the last locked frequency, the system has time to store its current settings before shutting down. You can either use their own control signal or gated locked status signals to trigger the pfdena signal.

For more information about Cyclone PLLs, refer to *Using PLLs in Cyclone Devices* chapter in the *Cyclone Device Handbook*.

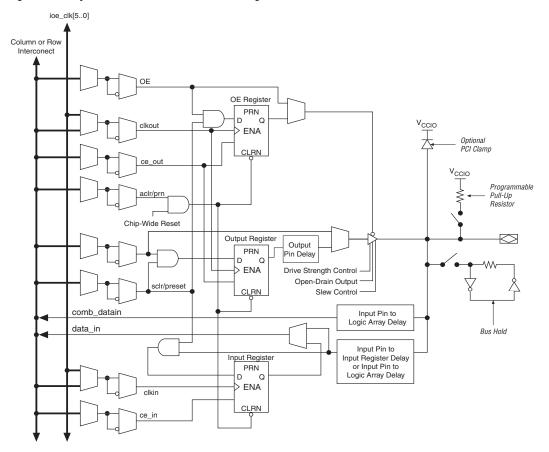

Figure 2-32. Cyclone IOE in Bidirectional I/O Configuration

The Cyclone device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays

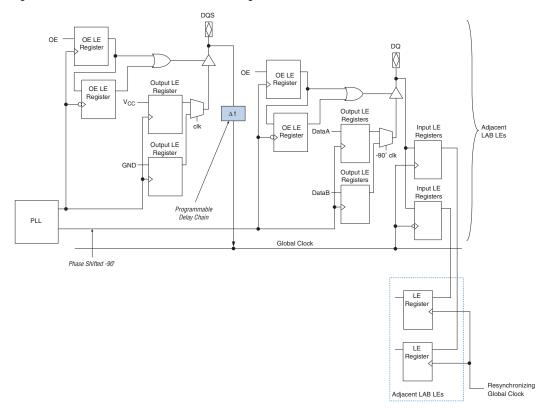

Figure 2-34. DDR SDRAM and FCRAM Interfacing

# **Programmable Drive Strength**

The output buffer for each Cyclone device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standards have several levels of drive strength that the designer can control. SSTL-3 class I and II, and SSTL-2 class I and II support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/I_{OL}$

#### Slew-Rate Control

The output buffer for each Cyclone device I/O pin has a programmable output slew-rate control that can be configured for low noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each I/O pin has an individual slew-rate control, allowing the designer to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

#### **Bus Hold**

Each Cyclone device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. The designer can select this feature individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\text{CCIO}}$  to prevent overdriving signals. If the bus-hold feature is enabled, the device cannot use the programmable pull-up option. Disable the bus-hold feature when the I/O pin is configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance (RBH) of approximately 7 k $\Omega$ to pull the signal level to the last-driven state. Table 4–15 on page 4–6 gives the specific sustaining current for each  $V_{\text{CCIO}}$  voltage level driven through this resistor and overdrive current used to identify the next-driven input level.

The bus-hold circuitry is only active after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

# Programmable Pull-Up Resistor

Each Cyclone device I/O pin provides an optional programmable pull-up resistor during user mode. If the designer enables this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the V<sub>CCIO</sub> level of the output pin's bank. Dedicated clock pins do not have the optional programmable pull-up resistor.

Each I/O bank can support multiple standards with the same  $V_{CCIO}$  for input and output pins. For example, when  $V_{CCIO}$  is 3.3-V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

### LVDS I/O Pins

A subset of pins in all four I/O banks supports LVDS interfacing. These dual-purpose LVDS pins require an external-resistor network at the transmitter channels in addition to 100- $\Omega$  termination resistors on receiver channels. These pins do not contain dedicated serialization or deserialization circuitry; therefore, internal logic performs serialization and deserialization functions.

Table 2–13 shows the total number of supported LVDS channels per device density.

| Table 2–13. Cyclone Device LVDS Channels |           |                         |  |  |  |  |  |

|------------------------------------------|-----------|-------------------------|--|--|--|--|--|

| Device                                   | Pin Count | Number of LVDS Channels |  |  |  |  |  |

| EP1C3                                    | 100       | (1)                     |  |  |  |  |  |

|                                          | 144       | 34                      |  |  |  |  |  |

| EP1C4                                    | 324       | 103                     |  |  |  |  |  |

|                                          | 400       | 129                     |  |  |  |  |  |

| EP1C6                                    | 144       | 29                      |  |  |  |  |  |

|                                          | 240       | 72                      |  |  |  |  |  |

|                                          | 256       | 72                      |  |  |  |  |  |

| EP1C12                                   | 240       | 66                      |  |  |  |  |  |

|                                          | 256       | 72                      |  |  |  |  |  |

|                                          | 324       | 103                     |  |  |  |  |  |

| EP1C20                                   | 324       | 95                      |  |  |  |  |  |

|                                          | 400       | 129                     |  |  |  |  |  |

*Note to Table 2–13:*

## MultiVolt I/O Interface

The Cyclone architecture supports the MultiVolt I/O interface feature, which allows Cyclone devices in all packages to interface with systems of different supply voltages. The devices have one set of  $V_{CC}$  pins for internal operation and input buffers ( $V_{CCINT}$ ), and four sets for I/O output drivers ( $V_{CCIO}$ ).

EP1C3 devices in the 100-pin TQFP package do not support the LVDS I/O standard.

The Cyclone  $V_{\rm CCINT}$  pins must always be connected to a 1.5-V power supply. If the  $V_{\rm CCINT}$  level is 1.5 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The  $V_{\rm CCIO}$  pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when  $V_{\rm CCIO}$  pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When  $V_{\rm CCIO}$  pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V or 5.0-V systems. Table 2–14 summarizes Cyclone MultiVolt I/O support.

| Table 2–14. Cyclone MultiVolt I/O Support Note (1) |          |                            |              |              |              |              |              |              |          |              |

|----------------------------------------------------|----------|----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|----------|--------------|

| V (V)                                              |          | Input Signal Output Signal |              |              |              |              |              |              |          |              |

| V <sub>CCIO</sub> (V)                              | 1.5 V    | 1.8 V                      | 2.5 V        | 3.3 V        | 5.0 V        | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V    | 5.0 V        |

| 1.5                                                | <b>✓</b> | <b>✓</b>                   | <b>√</b> (2) | <b>√</b> (2) | _            | <b>✓</b>     | _            | _            | _        | _            |

| 1.8                                                | <b>✓</b> | <b>✓</b>                   | <b>√</b> (2) | <b>√</b> (2) | _            | <b>√</b> (3) | <b>✓</b>     | _            | _        | _            |

| 2.5                                                | _        | _                          | <b>✓</b>     | <b>✓</b>     | _            | <b>√</b> (5) | <b>√</b> (5) | <b>✓</b>     | _        | _            |

| 3.3                                                | _        | _                          | <b>√</b> (4) | <b>✓</b>     | <b>√</b> (6) | <b>√</b> (7) | <b>√</b> (7) | <b>√</b> (7) | <b>✓</b> | <b>√</b> (8) |

#### Notes to Table 2-14:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>.

- (2) When V<sub>CCIO</sub> = 1.5-V or 1.8-V and a 2.5-V or 3.3-V input signal feeds an input pin, higher pin leakage current is expected. Turn on Allow voltage overdrive for LVTTL / LVCMOS input pins in the Assignments > Device > Device and Pin Options > Pin Placement tab when a device has this I/O combinations.

- (3) When  $V_{CCIO} = 1.8$ -V, a Cyclone device can drive a 1.5-V device with 1.8-V tolerant inputs.

- (4) When  $V_{CCIO} = 3.3$ -V and a 2.5-V input signal feeds an input pin, the  $V_{CCIO}$  supply current will be slightly larger than expected.

- (5) When V<sub>CCIO</sub> = 2.5-V, a Cyclone device can drive a 1.5-V or 1.8-V device with 2.5-V tolerant inputs.

- (6) Cyclone devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (7) When V<sub>CCIO</sub> = 3.3-V, a Cyclone device can drive a 1.5-V, 1.8-V, or 2.5-V device with 3.3-V tolerant inputs.

- (8) When  $V_{CCIO} = 3.3$ -V, a Cyclone device can drive a device with 5.0-V LVTTL inputs but not 5.0-V LVCMOS inputs.

# Power Sequencing and Hot Socketing

Because Cyclone devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$  power supplies may be powered in any order.

Signals can be driven into Cyclone devices before and during power up without damaging the device. In addition, Cyclone devices do not drive out during power up. Once operating conditions are reached and the device is configured, Cyclone devices operate as specified by the user.

| Table 3–1. Cyclone JTAG Instructions (Part 2 of 2) |                  |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|----------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| JTAG Instruction                                   | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| USERCODE                                           | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                          |  |  |  |  |  |

| IDCODE                                             | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                              |  |  |  |  |  |

| HIGHZ (1)                                          | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                 |  |  |  |  |  |

| CLAMP (1)                                          | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register.                                                                    |  |  |  |  |  |

| ICR instructions                                   | _                | Used when configuring a Cyclone device via the JTAG port with a MasterBlaster <sup>TM</sup> or ByteBlasterMV <sup>TM</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.                                                                                                                               |  |  |  |  |  |

| PULSE_NCONFIG                                      | 00 0000 0001     | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                        |  |  |  |  |  |

| CONFIG_IO                                          | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, after, or during configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction will hold nSTATUS low to reset the configuration device. nSTATUS is held low until the device is reconfigured. |  |  |  |  |  |

| SignalTap II instructions                          | _                | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

#### *Note to Table 3–1:*

In the Quartus II software, there is an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. Choose Assignments > Device > Device and Pin Options > General. Turn on **Auto Usercode**.

<sup>(1)</sup> Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

| Table 4–8. 1.5-V I/O Specifications |                           |                                |                             |                              |      |  |  |  |  |  |

|-------------------------------------|---------------------------|--------------------------------|-----------------------------|------------------------------|------|--|--|--|--|--|

| Symbol                              | Parameter                 | Conditions                     | Minimum                     | Maximum                      | Unit |  |  |  |  |  |

| $V_{CCIO}$                          | Output supply voltage     | _                              | 1.4                         | 1.6                          | V    |  |  |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  | _                              | 0.65 ×<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 (12) | V    |  |  |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   | _                              | -0.3                        | 0.35 ×<br>V <sub>CCIO</sub>  | V    |  |  |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ mA } (11)$ | 0.75 ×<br>V <sub>CCIO</sub> | _                            | V    |  |  |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 mA (11)    | _                           | 0.25 × V <sub>CCIO</sub>     | V    |  |  |  |  |  |

| Table 4–9. 2.5-V LVDS I/O SpecificationsNote (13) |                                                |                         |         |         |         |      |  |  |  |  |  |

|---------------------------------------------------|------------------------------------------------|-------------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                                            | Parameter                                      | Conditions              | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                                 | I/O supply voltage                             | _                       | 2.375   | 2.5     | 2.625   | V    |  |  |  |  |  |

| V <sub>OD</sub>                                   | Differential output voltage                    | $R_L = 100 \Omega$      | 250     |         | 550     | mV   |  |  |  |  |  |

| Δ V <sub>OD</sub>                                 | Change in V <sub>OD</sub> between high and low | R <sub>L</sub> = 100 Ω  | _       | _       | 50      | mV   |  |  |  |  |  |

| V <sub>OS</sub>                                   | Output offset voltage                          | $R_L = 100 \Omega$      | 1.125   | 1.25    | 1.375   | V    |  |  |  |  |  |

| Δ V <sub>OS</sub>                                 | Change in V <sub>OS</sub> between high and low | R <sub>L</sub> = 100 Ω  | _       | _       | 50      | mV   |  |  |  |  |  |

| V <sub>TH</sub>                                   | Differential input threshold                   | V <sub>CM</sub> = 1.2 V | -100    | _       | 100     | mV   |  |  |  |  |  |

| V <sub>IN</sub>                                   | Receiver input voltage range                   | _                       | 0.0     | _       | 2.4     | V    |  |  |  |  |  |

| R <sub>L</sub>                                    | Receiver differential input resistor           | _                       | 90      | 100     | 110     | Ω    |  |  |  |  |  |

| Table 4–10. 3.3-V PCI Specifications (Part 1 of 2) |                          |            |                            |         |                            |      |  |  |  |  |

|----------------------------------------------------|--------------------------|------------|----------------------------|---------|----------------------------|------|--|--|--|--|

| Symbol                                             | Parameter                | Conditions | Minimum                    | Typical | Maximum                    | Unit |  |  |  |  |

| V <sub>CCIO</sub>                                  | Output supply voltage    | _          | 3.0                        | 3.3     | 3.6                        | ٧    |  |  |  |  |

| V <sub>IH</sub>                                    | High-level input voltage | _          | 0.5 ×<br>V <sub>CCIO</sub> | _       | V <sub>CCIO</sub> + 0.5    | V    |  |  |  |  |

| V <sub>IL</sub>                                    | Low-level input voltage  | _          | -0.5                       | _       | 0.3 ×<br>V <sub>CCIO</sub> | V    |  |  |  |  |

# Power Consumption

Designers can use the Altera web Early Power Estimator to estimate the device power.

Cyclone devices require a certain amount of power-up current to successfully power up because of the nature of the leading-edge process on which they are fabricated. Table 4–17 shows the maximum power-up current required to power up a Cyclone device.

| Table 4–17. Cyclone Maximum Power-Up Current (I <sub>CCINT</sub> ) Requirements (In-Rush Current) |                          |      |    |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|--------------------------|------|----|--|--|--|--|--|--|

| Device                                                                                            | Industrial Specification | Unit |    |  |  |  |  |  |  |

| EP1C3                                                                                             | 150                      | 180  | mA |  |  |  |  |  |  |

| EP1C4                                                                                             | 150                      | 180  | mA |  |  |  |  |  |  |

| EP1C6                                                                                             | 175                      | 210  | mA |  |  |  |  |  |  |

| EP1C12                                                                                            | 300                      | 360  | mA |  |  |  |  |  |  |

| EP1C20                                                                                            | 500                      | 600  | mA |  |  |  |  |  |  |

#### *Notes to Table 4–17:*

- The Cyclone devices (except for the EP1C20 device) meet the power up specification for Mini PCI.

- (2) The lot codes 9G0082 to 9G2999, or 9G3109 and later comply to the specifications in Table 4–17 and meet the Mini PCI specification. Lot codes appear at the top of the device.

- (3) The lot codes 9H0004 to 9H29999, or 9H3014 and later comply to the specifications in this table and meet the Mini PCI specification. Lot codes appear at the top of the device.

Designers should select power supplies and regulators that can supply this amount of current when designing with Cyclone devices. This specification is for commercial operating conditions. Measurements were performed with an isolated Cyclone device on the board. Decoupling capacitors were not used in this measurement. To factor in the current for decoupling capacitors, sum up the current for each capacitor using the following equation:

$$I = C (dV/dt)$$

The exact amount of current that is consumed varies according to the process, temperature, and power ramp rate. If the power supply or regulator can supply more current than required, the Cyclone device may consume more current than the maximum current specified in Table 4–17. However, the device does not require any more current to successfully power up than what is listed in Table 4–17.

The duration of the  $I_{CCINT}$  power-up requirement depends on the  $V_{CCINT}$  voltage supply rise time. The power-up current consumption drops when the  $V_{CCINT}$  supply reaches approximately 0.75 V. For example, if the  $V_{CCINT}$  rise time has a linear rise of 15 ms, the current consumption spike drops by 7.5 ms.

| Table 4–29. C | yclone Global Clock External I/O Timing Parameters No                                                                                 | tes (1), (2) <b>(Part 2 of 2)</b> |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Symbol        | Parameter                                                                                                                             | Conditions                        |

| toutcople     | Clock-to-output delay output or bidirectional pin using IOE output register with global clock enhanced PLL with default phase setting | C <sub>LOAD</sub> = 10 pF         |

#### Notes to Table 4-29:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for IOE pins using a 3.3-V LVTTL, 24-mA setting. Designers should use the Quartus II software to verify the external timing for any pin.

Tables 4–30 through 4–31 show the external timing parameters on column and row pins for EP1C3 devices.

| Table 4–30. EP1C3 Column Pin Global Clock External I/O Timing<br>Parameters |         |         |         |         |         |       |      |  |  |  |  |

|-----------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|--|--|

| Symbol                                                                      | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | Hait  |      |  |  |  |  |

|                                                                             | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |  |  |

| t <sub>INSU</sub>                                                           | 3.085   | _       | 3.547   | _       | 4.009   | _     | ns   |  |  |  |  |

| t <sub>INH</sub>                                                            | 0.000   | _       | 0.000   | _       | 0.000   | _     | ns   |  |  |  |  |

| toutco                                                                      | 2.000   | 4.073   | 2.000   | 4.682   | 2.000   | 5.295 | ns   |  |  |  |  |

| t <sub>INSUPLL</sub>                                                        | 1.795   | _       | 2.063   | _       | 2.332   | _     | ns   |  |  |  |  |

| t <sub>INHPLL</sub>                                                         | 0.000   | _       | 0.000   | _       | 0.000   | _     | ns   |  |  |  |  |

| toutcople                                                                   | 0.500   | 2.306   | 0.500   | 2.651   | 0.500   | 2.998 | ns   |  |  |  |  |

| Table 4–31. EP1C3 Row Pin Global Clock External I/O Timing Parameters |                |       |                |       |         |       |      |  |  |  |

|-----------------------------------------------------------------------|----------------|-------|----------------|-------|---------|-------|------|--|--|--|

| Symbol                                                                | -6 Speed Grade |       | -7 Speed Grade |       | -8 Spee | 11    |      |  |  |  |

|                                                                       | Min            | Max   | Min            | Max   | Min     | Max   | Unit |  |  |  |

| t <sub>INSU</sub>                                                     | 3.157          | _     | 3.630          | _     | 4.103   | _     | ns   |  |  |  |

| t <sub>INH</sub>                                                      | 0.000          | _     | 0.000          | _     | 0.000   | _     | ns   |  |  |  |

| t <sub>outco</sub>                                                    | 2.000          | 3.984 | 2.000          | 4.580 | 2.000   | 5.180 | ns   |  |  |  |

| t <sub>INSUPLL</sub>                                                  | 1.867          | _     | 2.146          | _     | 2.426   | _     | ns   |  |  |  |

| t <sub>INHPLL</sub>                                                   | 0.000          | _     | 0.000          | _     | 0.000   | _     | ns   |  |  |  |

| toutcople                                                             | 0.500          | 2.217 | 0.500          | 2.549 | 0.500   | 2.883 | ns   |  |  |  |

| Table 4–39. EP1C20 Row Pin Global Clock External I/O Timing Parameters |                |       |         |         |         |       |      |

|------------------------------------------------------------------------|----------------|-------|---------|---------|---------|-------|------|

| 0                                                                      | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee | IIia  |      |

| Symbol                                                                 | Min            | Max   | Min     | Max     | Min     | Max   | Unit |

| t <sub>INSU</sub>                                                      | 2.417          | _     | 2.779   | _       | 3.140   | _     | ns   |

| t <sub>INH</sub>                                                       | 0.000          | _     | 0.000   | _       | 0.000   | _     | ns   |

| toutco                                                                 | 2.000          | 3.724 | 2.000   | 4.282   | 2.000   | 4.843 | ns   |

| t <sub>XZ</sub>                                                        | _              | 3.645 | _       | 4.191   | _       | 4.740 | ns   |

| t <sub>ZX</sub>                                                        | _              | 3.645 | _       | 4.191   | _       | 4.740 | ns   |

| t <sub>INSUPLL</sub>                                                   | 1.417          | _     | 1.629   | _       | 1.840   | _     | ns   |

| t <sub>INHPLL</sub>                                                    | 0.000          | _     | 0.000   | _       | 0.000   | _     | ns   |

| toutcople                                                              | 0.500          | 1.667 | 0.500   | 1.917   | 0.500   | 2.169 | ns   |

| t <sub>XZPLL</sub>                                                     | _              | 1.588 | _       | 1.826   | _       | 2.066 | ns   |

| t <sub>ZXPLL</sub>                                                     |                | 1.588 | _       | 1.826   | _       | 2.066 | ns   |

# **External I/O Delay Parameters**

External I/O delay timing parameters for I/O standard input and output adders and programmable input and output delays are specified by speed grade independent of device density.

Tables 4–40 through 4–45 show the adder delays associated with column and row I/O pins for all packages. If an I/O standard is selected other than LVTTL 4 mA with a fast slew rate, add the selected delay to the external  $t_{CO}$  and  $t_{SU}$  I/O parameters shown in Tables 4–25 through 4–28.

| Table 4–40. Cyclone I/O Standard Column Pin Input Delay Adders (Part 1 of 2) |                |      |                |      |                |      |      |

|------------------------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| I/O Otenderal                                                                | -6 Speed Grade |      | -7 Speed Grade |      | -8 Speed Grade |      | Hait |

| I/O Standard                                                                 | Min            | Max  | Min            | Max  | Min            | Max  | Unit |

| LVCMOS                                                                       | _              | 0    | _              | 0    | _              | 0    | ps   |

| 3.3-V LVTTL                                                                  | _              | 0    | _              | 0    | _              | 0    | ps   |

| 2.5-V LVTTL                                                                  | _              | 27   | _              | 31   | _              | 35   | ps   |

| 1.8-V LVTTL                                                                  | _              | 182  | _              | 209  | _              | 236  | ps   |

| 1.5-V LVTTL                                                                  | _              | 278  | _              | 319  | _              | 361  | ps   |

| SSTL-3 class I                                                               | _              | -250 | _              | -288 | _              | -325 | ps   |

| SSTL-3 class II                                                              | _              | -250 | _              | -288 | _              | -325 | ps   |

| SSTL-2 class I                                                               | _              | -278 | _              | -320 |                | -362 | ps   |

| Table 4–44. Cyclone I/O Standard Output Delay Adders for Slow Slew Rate on Column Pins (Part 2 of 2) |       |                |       |                |       |                |       |      |

|------------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| I/O Standard                                                                                         |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | IIi4 |

| i/U Star                                                                                             | iuaru | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| 1.5-V LVTTL                                                                                          | 2 mA  | _              | 6,789 | _              | 7,807 | _              | 8,825 | ps   |

|                                                                                                      | 4 mA  | _              | 5,109 | _              | 5,875 | _              | 6,641 | ps   |

|                                                                                                      | 8 mA  | _              | 4,793 | _              | 5,511 | _              | 6,230 | ps   |

| SSTL-3 class I                                                                                       |       | _              | 1,390 | _              | 1,598 | _              | 1,807 | ps   |

| SSTL-3 class I                                                                                       | I     | _              | 989   | _              | 1,137 | _              | 1,285 | ps   |

| SSTL-2 class I                                                                                       |       | _              | 1,965 | _              | 2,259 | _              | 2,554 | ps   |

| SSTL-2 class II                                                                                      |       | _              | 1,692 | _              | 1,945 |                | 2,199 | ps   |

| LVDS                                                                                                 | ·     | _              | 802   | _              | 922   | _              | 1,042 | ps   |

|              |       | -6 Snor        | ad Grado | -7 Sno         | ad Grada | -8 Sno         | ad Grado |      |

|--------------|-------|----------------|----------|----------------|----------|----------------|----------|------|

| I/O Standard |       | -6 Speed Grade |          | -7 Speed Grade |          | -8 Speed Grade |          | Unit |

| ·            |       | Min            | Max      | Min            | Max      | Min            | Max      |      |

| LVCMOS       | 2 mA  | _              | 1,800    | _              | 2,070    | _              | 2,340    | ps   |

|              | 4 mA  | _              | 1,311    | _              | 1,507    | _              | 1,704    | ps   |

|              | 8 mA  | _              | 945      | _              | 1,086    | _              | 1,228    | ps   |

|              | 12 mA | _              | 807      | _              | 928      | _              | 1,049    | ps   |

| 3.3-V LVTTL  | 4 mA  | _              | 1,831    | _              | 2,105    | _              | 2,380    | ps   |

|              | 8 mA  | _              | 1,484    | _              | 1,705    | _              | 1,928    | ps   |

|              | 12 mA | _              | 973      | _              | 1,118    | _              | 1,264    | ps   |

|              | 16 mA | _              | 1,012    | _              | 1,163    | _              | 1,315    | ps   |

|              | 24 mA | _              | 838      | _              | 963      | _              | 1,089    | ps   |

| 2.5-V LVTTL  | 2 mA  | _              | 2,747    | _              | 3,158    | _              | 3,570    | ps   |

|              | 8 mA  | _              | 1,757    | _              | 2,019    | _              | 2,283    | ps   |

|              | 12 mA | _              | 1,763    | _              | 2,026    | _              | 2,291    | ps   |

|              | 16 mA | _              | 1,623    | _              | 1,865    | _              | 2,109    | ps   |

| 1.8-V LVTTL  | 2 mA  | _              | 5,506    | _              | 6,331    | _              | 7,157    | ps   |

|              | 8 mA  | _              | 4,220    | _              | 4,852    | _              | 5,485    | ps   |

|              | 12 mA | _              | 4,008    | _              | 4,608    | _              | 5,209    | ps   |

| 1.5-V LVTTL  | 2 mA  | _              | 6,789    | _              | 7,807    | _              | 8,825    | ps   |

|              | 4 mA  | _              | 5,109    | _              | 5,875    | _              | 6,641    | ps   |

|              | 8 mA  | _              | 4,793    | _              | 5,511    | _              | 6,230    | ps   |

| 3.3-V PCI    |       | _              | 923      | _              | 1,061    | _              | 1,199    | ps   |

| Table 4–51. Cyclone Maximum Output Clock Rate for Row Pins |                   |                   |                   |      |  |  |

|------------------------------------------------------------|-------------------|-------------------|-------------------|------|--|--|

| I/O Standard                                               | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

| LVTTL                                                      | 296               | 285               | 273               | MHz  |  |  |

| 2.5 V                                                      | 381               | 366               | 349               | MHz  |  |  |

| 1.8 V                                                      | 286               | 277               | 267               | MHz  |  |  |

| 1.5 V                                                      | 219               | 208               | 195               | MHz  |  |  |

| LVCMOS                                                     | 367               | 356               | 343               | MHz  |  |  |

| SSTL-3 class I                                             | 169               | 166               | 162               | MHz  |  |  |

| SSTL-3 class II                                            | 160               | 151               | 146               | MHz  |  |  |

| SSTL-2 class I                                             | 160               | 151               | 142               | MHz  |  |  |

| SSTL-2 class II                                            | 131               | 123               | 115               | MHz  |  |  |

| 3.3-V PCI (1)                                              | 66                | 66                | 66                | MHz  |  |  |

| LVDS                                                       | 320               | 303               | 275               | MHz  |  |  |

*Note to Tables 4–50 through 4–51:*

# **PLL Timing**

Table 4–52 describes the Cyclone FPGA PLL specifications.

| Table 4–52. Cyclone PLL Specifications (Part 1 of 2) |                                       |        |       |      |  |  |  |

|------------------------------------------------------|---------------------------------------|--------|-------|------|--|--|--|

| Symbol                                               | Parameter                             | Min    | Max   | Unit |  |  |  |

| f <sub>IN</sub>                                      | Input frequency (-6 speed grade)      | 15.625 | 464   | MHz  |  |  |  |

|                                                      | Input frequency (-7 speed grade)      | 15.625 | 428   | MHz  |  |  |  |

|                                                      | Input frequency (-8 speed grade)      | 15.625 | 387   | MHz  |  |  |  |

| f <sub>IN</sub> DUTY                                 | Input clock duty cycle                | 40.00  | 60    | %    |  |  |  |

| t <sub>IN</sub> JITTER                               | Input clock period jitter             | _      | ± 200 | ps   |  |  |  |

| f <sub>OUT_EXT</sub> (external PLL clock output)     | PLL output frequency (-6 speed grade) | 15.625 | 320   | MHz  |  |  |  |

|                                                      | PLL output frequency (-7 speed grade) | 15.625 | 320   | MHz  |  |  |  |

|                                                      | PLL output frequency (-8 speed grade) | 15.625 | 275   | MHz  |  |  |  |

<sup>(1)</sup> EP1C3 devices do not support the PCI I/O standard. These parameters are only available on row I/O pins.

# Referenced Document

This chapter references the following documents:

- Cyclone Architecture chapter in the Cyclone Device Handbook

- Operating Requirements for Altera Devices Data Sheet

# Document Revision History

Table 4–53 shows the revision history for this chapter.

| Table 4–53. Document Revision History |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| Date and<br>Document<br>Version       | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Summary of Changes |  |  |  |  |

| May 2008<br>v1.7                      | Minor textual and style changes. Added "Referenced Document" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                  |  |  |  |  |

| January 2007<br>v1.6                  | <ul> <li>Added document revision history.</li> <li>Added new row for V<sub>CCA</sub> details in Table 4–1.</li> <li>Updated R<sub>CONF</sub> information in Table 4–3.</li> <li>Added new Note (12) on voltage overdrive information to Table 4–7 and Table 4–8.</li> <li>Updated Note (9) on R<sub>CONF</sub> information to Table 4–3.</li> <li>Updated information in "External I/O Delay Parameters" section.</li> <li>Updated speed grade information in Table 4–46 and Table 4–47.</li> <li>Updated LVDS information in Table 4–51.</li> </ul> | <del>-</del>       |  |  |  |  |

| August 2005<br>v1.5                   | Minor updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                  |  |  |  |  |

| February 2005<br>v1.4                 | <ul> <li>Updated information on Undershoot voltage. Updated Table 4-2.</li> <li>Updated Table 4-3.</li> <li>Updated the undershoot voltage from 0.5 V to 2.0 V in Note 3 of Table 4-16.</li> <li>Updated Table 4-17.</li> </ul>                                                                                                                                                                                                                                                                                                                      | _                  |  |  |  |  |

| January 2004<br>v.1.3                 | <ul> <li>Added extended-temperature grade device information.<br/>Updated Table 4-2.</li> <li>Updated I<sub>CC0</sub> information in Table 4-3.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           | _                  |  |  |  |  |

| October 2003<br>v.1.2                 | <ul> <li>Added clock tree information in Table 4-19.</li> <li>Finalized timing information for EP1C3 and EP1C12 devices.<br/>Updated timing information in Tables 4-25 through 4-26 and<br/>Tables 4-30 through 4-51.</li> <li>Updated PLL specifications in Table 4-52.</li> </ul>                                                                                                                                                                                                                                                                  | _                  |  |  |  |  |