Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 4125                                                          |

| Number of Logic Elements/Cells | 41250                                                         |

| Total RAM Bits                 | 3423744                                                       |

| Number of I/O                  | 624                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 1020-BBGA                                                     |

| Supplier Device Package        | 1020-FBGA (33x33)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx40gf1020c6bn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1–1. Cyclone Device Features (Part 2 of 2) |        |        |        |         |         |  |  |  |  |  |  |

|--------------------------------------------------|--------|--------|--------|---------|---------|--|--|--|--|--|--|

| Feature                                          | EP1C3  | EP1C4  | EP1C6  | EP1C12  | EP1C20  |  |  |  |  |  |  |

| Total RAM bits                                   | 59,904 | 78,336 | 92,160 | 239,616 | 294,912 |  |  |  |  |  |  |

| PLLs                                             | 1      | 2      | 2      | 2       | 2       |  |  |  |  |  |  |

| Maximum user I/O pins (1)                        | 104    | 301    | 185    | 249     | 301     |  |  |  |  |  |  |

Note to Table 1–1:

(1) This parameter includes global clock pins.

Cyclone devices are available in quad flat pack (QFP) and space-saving FineLine<sup>®</sup> BGA packages (see Tables 1–2 through 1–3).

| Table 1-2. ( | Table 1–2. Cyclone Package Options and I/O Pin Counts |                              |                         |                         |                         |                         |  |  |  |  |  |  |

|--------------|-------------------------------------------------------|------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|--|--|--|--|

| Device       | <b>100-Pin TQFP</b> (1)                               | <b>144-Pin TQFP</b> (1), (2) | <b>240-Pin PQFP</b> (1) | 256-Pin<br>FineLine BGA | 324-Pin<br>FineLine BGA | 400-Pin<br>FineLine BGA |  |  |  |  |  |  |

| EP1C3        | 65                                                    | 104                          | _                       | _                       | _                       | _                       |  |  |  |  |  |  |

| EP1C4        | _                                                     | _                            | _                       | _                       | 249                     | 301                     |  |  |  |  |  |  |

| EP1C6        | _                                                     | 98                           | 185                     | 185                     | _                       | _                       |  |  |  |  |  |  |

| EP1C12       | _                                                     | _                            | 173                     | 185                     | 249                     | _                       |  |  |  |  |  |  |

| EP1C20       | _                                                     | _                            | _                       | _                       | 233                     | 301                     |  |  |  |  |  |  |

#### *Notes to Table 1–2:*

- (1) TQFP: thin quad flat pack. PQFP: plastic quad flat pack.

- (2) Cyclone devices support vertical migration within the same package (i.e., designers can migrate between the EP1C3 device in the 144-pin TQFP package and the EP1C6 device in the same package).

Vertical migration means you can migrate a design from one device to another that has the same dedicated pins, JTAG pins, and power pins, and are subsets or supersets for a given package across device densities. The largest density in any package has the highest number of power pins; you must use the layout for the largest planned density in a package to provide the necessary power pins for migration.

For I/O pin migration across densities, cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins can be migrated. The Quartus® II software can automatically cross-reference and place all pins for you when given a device migration list. If one device has power or ground pins, but these same pins are user I/O on a different device that is in the migration path,the Quartus II software ensures the pins are not used as user I/O in the Quartus II software. Ensure that these pins are connected

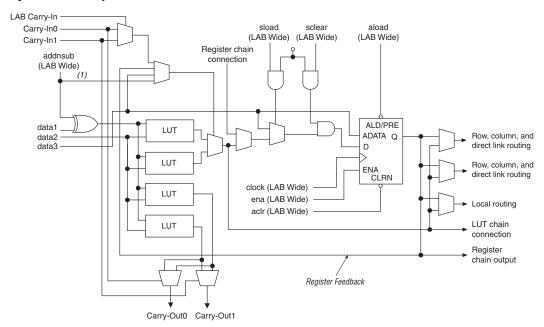

Figure 2-7. LE in Dynamic Arithmetic Mode

Note to Figure 2-7:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within a LAB.

The speed advantage of the carry-select chain is in the parallel pre-computation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Cyclone architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

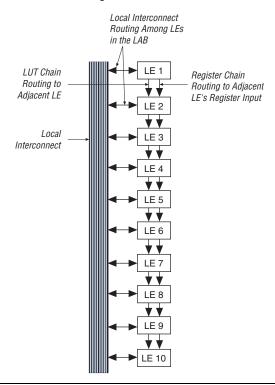

Figure 2–10. LUT Chain and Register Chain Interconnects

The C4 interconnects span four LABs or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from a LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including PLLs, M4K memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–3 and 2–4 summarize the possible M4K RAM block configurations.

| Table 2–3. M4K RAM Block Configurations (Simple Dual-Port) |          |          |          |          |          |          |          |          |          |  |  |

|------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|--|

| Read Port                                                  |          |          |          |          | Write P  | ort      |          |          |          |  |  |

| neau ruii                                                  | 4K × 1   | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 128 × 32 | 512 × 9  | 256 × 18 | 128 × 36 |  |  |

| 4K × 1                                                     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | _        | _        | _        |  |  |

| 2K × 2                                                     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | _        | _        | _        |  |  |

| 1K × 4                                                     | ~        | <b>✓</b> | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> | _        | _        | _        |  |  |

| 512 × 8                                                    | <b>✓</b> | <b>✓</b> | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> | _        | _        | _        |  |  |

| 256 × 16                                                   | ~        | <b>✓</b> | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> | _        | _        | _        |  |  |

| 128 × 32                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> | _        | _        | _        |  |  |

| 512 × 9                                                    | _        | _        | _        | _        | _        | _        | ✓        | ~        | <b>✓</b> |  |  |

| 256 × 18                                                   | _        | _        | _        | _        | _        | _        | <b>✓</b> | ~        | <b>✓</b> |  |  |

| 128 × 36                                                   | <u> </u> | _        | _        | _        | _        | _        | <b>✓</b> | <b>✓</b> | <b>✓</b> |  |  |

| Table 2–4. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |          |  |  |  |  |

|----------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|--|--|--|--|

| Dovt A                                                   |          |          |          | Port B   |          |          |          |  |  |  |  |

| Port A                                                   | 4K × 1   | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |  |  |  |

| 4K × 1                                                   | ✓        | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | _        | _        |  |  |  |  |

| 2K × 2                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓        | _        | _        |  |  |  |  |

| 1K × 4                                                   | ✓        | ✓        | ✓        | ✓        | <b>✓</b> | _        | _        |  |  |  |  |

| 512 × 8                                                  | ✓        | ✓        | ✓        | ✓        | <b>✓</b> | _        | _        |  |  |  |  |

| 256 × 16                                                 | ✓        | ✓        | ✓        | ✓        | <b>✓</b> | _        | _        |  |  |  |  |

| 512 × 9                                                  | _        | _        | _        | _        | _        | <b>✓</b> | <b>✓</b> |  |  |  |  |

| 256 × 18                                                 | _        | _        | _        | _        | _        | ✓        | <b>✓</b> |  |  |  |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits  $(w \times m \times n)$ .

### **Byte Enables**

M4K blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 2–5 summarizes the byte selection.

| Table 2–5. Byte Enable for M4K BlocksNotes (1), (2) |            |            |  |  |  |  |  |  |

|-----------------------------------------------------|------------|------------|--|--|--|--|--|--|

| byteena[30]                                         | datain ×18 | datain ×36 |  |  |  |  |  |  |

| [0] = 1                                             | [80]       | [80]       |  |  |  |  |  |  |

| [1] = 1                                             | [179]      | [179]      |  |  |  |  |  |  |

| [2] = 1                                             | _          | [2618]     |  |  |  |  |  |  |

| [3] = 1                                             | _          | [3527]     |  |  |  |  |  |  |

Notes to Table 2-5:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in ×16 and ×32 modes.

### **Control Signals and M4K Interface**

The M4K blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–15.

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K block local interconnect. The M4K blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 2–16 shows the M4K block to logic array interface.

The eight global clock lines in the global clock network drive throughout the entire device. The global clock network can provide clocks for all resources within the device—IOEs, LEs, and memory blocks. The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin, or DQS signals for DDR SDRAM or FCRAM interfaces. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–22 shows the various sources that drive the global clock network.

DPCLK2 DPCLK3 Cyclone Device Global Clock Network 8 DPCLK1 \_ □ DPCLK4 From logic From logic array array CLK0 [ □ CLK2 PLL2 PLL1 CLK1 (3) □ CLK3 (3) (2) 2 DPCLK0 [ □ DPCLK5 DPCLK7 DPCLK6

Figure 2–22. Global Clock Generation Note (1)

#### *Notes to Figure 2–22:*

- (1) The EP1C3 device in the 100-pin TQFP package has five DPCLK pins (DPCLK2, DPCLK3, DPCLK4, DPCLK6, and DPCLK7).

- (2) EP1C3 devices only contain one PLL (PLL 1).

- (3) The EP1C3 device in the 100-pin TQFP package does not have dedicated clock pins CLK1 and CLK3.

## **Programmable Duty Cycle**

The programmable duty cycle allows PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each PLL post-scale counter (g0, g1, e). The duty cycle setting is achieved by a low- and high-time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

## **Control Signals**

There are three control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and the ability to gate PLL output clocks for low-power applications.

The pllenable signal enables and disables PLLs. When the pllenable signal is low, the clock output ports are driven by ground and all the PLLs go out of lock. When the pllenable signal goes high again, the PLLs relock and resynchronize to the input clocks. An input pin or LE output can drive the pllenable signal.

The areset signals are reset/resynchronization inputs for each PLL. Cyclone devices can drive these input signals from input pins or from LEs. When areset is driven high, the PLL counters will reset, clearing the PLL output and placing the PLL out of lock. When driven low again, the PLL will resynchronize to its input as it relocks.

The pfdena signals control the phase frequency detector (PFD) output with a programmable gate. If you disable the PFD, the VCO will operate at its last set value of control voltage and frequency with some drift, and the system will continue running when the PLL goes out of lock or the input clock disables. By maintaining the last locked frequency, the system has time to store its current settings before shutting down. You can either use their own control signal or gated locked status signals to trigger the pfdena signal.

For more information about Cyclone PLLs, refer to *Using PLLs in Cyclone Devices* chapter in the *Cyclone Device Handbook*.

output pins (nSTATUS and CONF\_DONE) and all the JTAG pins in I/O bank 3 must operate at 2.5 V because the  $V_{CCIO}$  level of SSTL-2 is 2.5 V. I/O banks 1, 2, 3, and 4 support DQS signals with DQ bus modes of  $\times$  8.

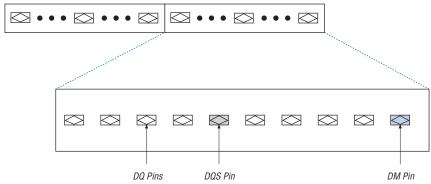

For ×8 mode, there are up to eight groups of programmable DQS and DQ pins, I/O banks 1, 2, 3, and 4 each have two groups in the 324-pin and 400-pin FineLine BGA packages. Each group consists of one DQS pin, a set of eight DQ pins, and one DM pin (see Figure 2–33). Each DQS pin drives the set of eight DQ pins within that group.

Figure 2–33. Cyclone Device DQ and DQS Groups in ×8 Mode Note (1)

Note to Figure 2-33:

(1) Each DQ group consists of one DQS pin, eight DQ pins, and one DM pin.

Table 2–10 shows the number of DQ pin groups per device.

| Table 2–10. DQ Pin Groups (Part 1 of 2) |                      |                                |                       |  |  |  |  |  |

|-----------------------------------------|----------------------|--------------------------------|-----------------------|--|--|--|--|--|

| Device                                  | Package              | Number of × 8 DQ<br>Pin Groups | Total DQ Pin<br>Count |  |  |  |  |  |

| EP1C3                                   | 100-pin TQFP (1)     | 3                              | 24                    |  |  |  |  |  |

|                                         | 144-pin TQFP         | 4                              | 32                    |  |  |  |  |  |

| EP1C4                                   | 324-pin FineLine BGA | 8                              | 64                    |  |  |  |  |  |

|                                         | 400-pin FineLine BGA | 8                              | 64                    |  |  |  |  |  |

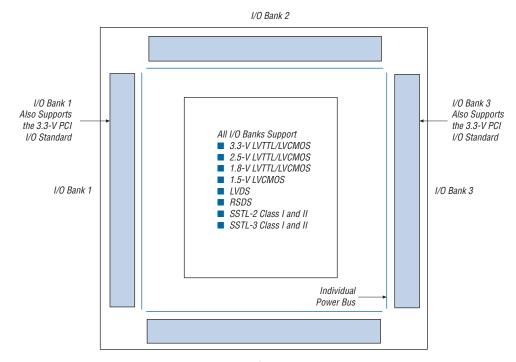

and DM pins to support a DDR SDRAM or FCRAM interface. I/O bank 1 can also support a DDR SDRAM or FCRAM interface, however, the configuration input pins in I/O bank 1 must operate at 2.5 V. I/O bank 3 can also support a DDR SDRAM or FCRAM interface, however, all the JTAG pins in I/O bank 3 must operate at 2.5 V.

**Figure 2–35. Cyclone I/O Banks** Notes (1), (2)

I/O Bank 4

#### *Notes to Figure 2–35:*

- (1) Figure 2–35 is a top view of the silicon die.

- (2) Figure 2–35 is a graphic representation only. Refer to the pin list and the Quartus II software for exact pin locations.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard with different I/O voltages. Each bank also has dual-purpose VREF pins to support any one of the voltage-referenced standards (e.g., SSTL-3) independently. If an I/O bank does not use voltage-referenced standards, the  $V_{\rm REF}$  pins are available as user I/O pins.

The Cyclone  $V_{\rm CCINT}$  pins must always be connected to a 1.5-V power supply. If the  $V_{\rm CCINT}$  level is 1.5 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The  $V_{\rm CCIO}$  pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when  $V_{\rm CCIO}$  pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When  $V_{\rm CCIO}$  pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V or 5.0-V systems. Table 2–14 summarizes Cyclone MultiVolt I/O support.

| Table 2–14. Cyclone MultiVolt I/O Support Note (1) |          |          |              |              |              |              |              |              |          |              |

|----------------------------------------------------|----------|----------|--------------|--------------|--------------|--------------|--------------|--------------|----------|--------------|

| V (V)                                              |          | Ir       | nput Sign    | al           |              |              | 0ι           | ıtput Sigr   | nal      |              |

| V <sub>CCIO</sub> (V)                              | 1.5 V    | 1.8 V    | 2.5 V        | 3.3 V        | 5.0 V        | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V    | 5.0 V        |

| 1.5                                                | <b>✓</b> | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | _            | <b>✓</b>     | _            | _            | _        | _            |

| 1.8                                                | <b>✓</b> | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) | _            | <b>√</b> (3) | <b>✓</b>     | _            | _        | _            |

| 2.5                                                | _        | _        | <b>✓</b>     | <b>✓</b>     | _            | <b>√</b> (5) | <b>√</b> (5) | <b>✓</b>     | _        | _            |

| 3.3                                                | _        | _        | <b>√</b> (4) | <b>✓</b>     | <b>√</b> (6) | <b>√</b> (7) | <b>√</b> (7) | <b>√</b> (7) | <b>✓</b> | <b>√</b> (8) |

#### Notes to Table 2-14:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>.

- (2) When V<sub>CCIO</sub> = 1.5-V or 1.8-V and a 2.5-V or 3.3-V input signal feeds an input pin, higher pin leakage current is expected. Turn on Allow voltage overdrive for LVTTL / LVCMOS input pins in the Assignments > Device > Device and Pin Options > Pin Placement tab when a device has this I/O combinations.

- (3) When  $V_{CCIO} = 1.8$ -V, a Cyclone device can drive a 1.5-V device with 1.8-V tolerant inputs.

- (4) When  $V_{CCIO} = 3.3$ -V and a 2.5-V input signal feeds an input pin, the  $V_{CCIO}$  supply current will be slightly larger than expected.

- (5) When V<sub>CCIO</sub> = 2.5-V, a Cyclone device can drive a 1.5-V or 1.8-V device with 2.5-V tolerant inputs.

- (6) Cyclone devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (7) When V<sub>CCIO</sub> = 3.3-V, a Cyclone device can drive a 1.5-V, 1.8-V, or 2.5-V device with 3.3-V tolerant inputs.

- (8) When  $V_{CCIO} = 3.3$ -V, a Cyclone device can drive a device with 5.0-V LVTTL inputs but not 5.0-V LVCMOS inputs.

## Power Sequencing and Hot Socketing

Because Cyclone devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$  power supplies may be powered in any order.

Signals can be driven into Cyclone devices before and during power up without damaging the device. In addition, Cyclone devices do not drive out during power up. Once operating conditions are reached and the device is configured, Cyclone devices operate as specified by the user.

## 3. Configuration and Testing

C51003-1.4

## IEEE Std. 1149.1 (JTAG) Boundary Scan Support

All Cyclone<sup>®</sup> devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1a-1990 specification. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Cyclone devices can also use the JTAG port for configuration together with either the Quartus<sup>®</sup> II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Cyclone devices support reconfiguring the I/O standard settings on the IOE through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode. Designers can use this ability for JTAG testing before configuration when some of the Cyclone pins drive or receive from other devices on the board using voltage-referenced standards. Since the Cyclone device might not be configured before JTAG testing, the I/O pins might not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows designers to fully test I/O connection to other devices.

The JTAG pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The TDO pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The bank  $V_{\rm CCIO}$  selects whether the JTAG inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

Cyclone devices also use the JTAG port to monitor the operation of the device with the SignalTap® II embedded logic analyzer. Cyclone devices support the JTAG instructions shown in Table 3–1.

| Table 3–1. Cyclone JTAG Instructions (Part 1 of 2) |                  |                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|----------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| JTAG Instruction                                   | Instruction Code | Description                                                                                                                                                                                                                             |  |  |  |  |  |  |

| SAMPLE/PRELOAD                                     | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer. |  |  |  |  |  |  |

| EXTEST (1)                                         | 00 0000 0000     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                     |  |  |  |  |  |  |

| BYPASS                                             | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                             |  |  |  |  |  |  |

| Table 4-2. C   | Table 4–2. Cyclone Device Recommended Operating Conditions (Part 2 of 2) |                                  |         |                   |      |  |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------|----------------------------------|---------|-------------------|------|--|--|--|--|--|--|--|

| Symbol         | Parameter                                                                | Conditions                       | Minimum | Maximum           | Unit |  |  |  |  |  |  |  |

| Vo             | Output voltage                                                           |                                  | 0       | V <sub>CCIO</sub> | V    |  |  |  |  |  |  |  |

| T <sub>J</sub> | Operating junction temperature                                           | For commercial use               | 0       | 85                | ° C  |  |  |  |  |  |  |  |

|                |                                                                          | For industrial use               | -40     | 100               | ° C  |  |  |  |  |  |  |  |

|                |                                                                          | For extended-<br>temperature use | -40     | 125               | ° C  |  |  |  |  |  |  |  |

| Table 4-              | Table 4–3. Cyclone Device DC Operating Conditions   Note (6)                                   |                                                 |         |         |         |      |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------|---------|---------|---------|------|--|--|--|--|--|--|

| Symbol                | Parameter                                                                                      | Conditions                                      | Minimum | Typical | Maximum | Unit |  |  |  |  |  |  |

| I <sub>I</sub>        | Input pin leakage current                                                                      | $V_I = V_{CCIOmax}$ to 0 V (8)                  | -10     | _       | 10      | μΑ   |  |  |  |  |  |  |

| I <sub>OZ</sub>       | Tri-stated I/O pin leakage current                                                             | $V_O = V_{CCIOmax}$ to 0 V (8)                  | -10     | _       | 10      | μА   |  |  |  |  |  |  |

| I <sub>CC0</sub>      | V <sub>CC</sub> supply current (standby) (All M4K blocks in power-down mode) (7)               | EP1C3                                           | _       | 4       | _       | mA   |  |  |  |  |  |  |

|                       |                                                                                                | EP1C4                                           | _       | 6       | _       | mA   |  |  |  |  |  |  |

|                       |                                                                                                | EP1C6                                           | _       | 6       | _       | mA   |  |  |  |  |  |  |

|                       |                                                                                                | EP1C12                                          | _       | 8       | _       | mA   |  |  |  |  |  |  |

|                       |                                                                                                | EP1C20                                          | _       | 12      | _       | mA   |  |  |  |  |  |  |

| R <sub>CONF</sub> (9) |                                                                                                | $V_{I} = 0 \text{ V}; V_{CCI0} = 3.3 \text{ V}$ | 15      | 25      | 50      | kΩ   |  |  |  |  |  |  |

|                       | before and during configuration                                                                | $V_{I} = 0 \text{ V}; V_{CCI0} = 2.5 \text{ V}$ | 20      | 45      | 70      | kΩ   |  |  |  |  |  |  |

|                       |                                                                                                | $V_I = 0 \ V; \ V_{CCI0} = 1.8 \ V$             | 30      | 65      | 100     | kΩ   |  |  |  |  |  |  |

|                       |                                                                                                | $V_I = 0 \ V; \ V_{CCI0} = 1.5 \ V$             | 50      | 100     | 150     | kΩ   |  |  |  |  |  |  |

|                       | Recommended value of I/O pin<br>external pull-down resistor<br>before and during configuration | _                                               | _       | 1       | 2       | kΩ   |  |  |  |  |  |  |

| Table 4-4.        | Table 4–4. LVTTL Specifications |                                                |         |         |      |  |  |  |  |  |  |  |

|-------------------|---------------------------------|------------------------------------------------|---------|---------|------|--|--|--|--|--|--|--|

| Symbol            | Parameter                       | Conditions                                     | Minimum | Maximum | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage           | _                                              | 3.0     | 3.6     | V    |  |  |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage        | _                                              | 1.7     | 4.1     | V    |  |  |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage         | _                                              | -0.5    | 0.7     | V    |  |  |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage       | $I_{OH} = -4 \text{ to } -24 \text{ mA } (11)$ | 2.4     | _       | V    |  |  |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage        | I <sub>OL</sub> = 4 to 24 mA (11)              | _       | 0.45    | V    |  |  |  |  |  |  |  |

| Table 4–5. LVCMOS Specifications |                           |                                              |                         |         |      |  |  |  |  |

|----------------------------------|---------------------------|----------------------------------------------|-------------------------|---------|------|--|--|--|--|

| Symbol                           | Parameter                 | Conditions                                   | Minimum                 | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub>                | Output supply voltage     | _                                            | 3.0                     | 3.6     | V    |  |  |  |  |

| V <sub>IH</sub>                  | High-level input voltage  | _                                            | 1.7                     | 4.1     | V    |  |  |  |  |

| $V_{IL}$                         | Low-level input voltage   | _                                            | -0.5                    | 0.7     | V    |  |  |  |  |

| V <sub>OH</sub>                  | High-level output voltage | $V_{CCIO} = 3.0,$ $I_{OH} = -0.1 \text{ mA}$ | V <sub>CCIO</sub> - 0.2 | _       | V    |  |  |  |  |

| V <sub>OL</sub>                  | Low-level output voltage  | $V_{CCIO} = 3.0,$ $I_{OL} = 0.1 \text{ mA}$  | _                       | 0.2     | V    |  |  |  |  |

| Table 4–6.        | 2.5-V I/O Specifications  |                                                |         |         |      |

|-------------------|---------------------------|------------------------------------------------|---------|---------|------|

| Symbol            | Parameter                 | Conditions                                     | Minimum | Maximum | Unit |

| V <sub>CCIO</sub> | Output supply voltage     | _                                              | 2.375   | 2.625   | V    |

| V <sub>IH</sub>   | High-level input voltage  | _                                              | 1.7     | 4.1     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _                                              | -0.5    | 0.7     | V    |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OH</sub> = -0.1 mA                      | 2.1     | _       | V    |

|                   |                           | $I_{OH} = -1 \text{ mA}$                       | 2.0     | _       | V    |

|                   |                           | $I_{OH} = -2 \text{ to } -16 \text{ mA } (11)$ | 1.7     | _       | V    |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 0.1 mA                       | _       | 0.2     | V    |

|                   |                           | I <sub>OH</sub> = 1 mA                         | _       | 0.4     | V    |

|                   |                           | I <sub>OH</sub> = 2 to 16 mA (11)              |         | 0.7     | V    |

| Table 4–7. 1.8-V I/O Specifications |                           |                                               |                             |                             |      |  |  |  |  |

|-------------------------------------|---------------------------|-----------------------------------------------|-----------------------------|-----------------------------|------|--|--|--|--|

| Symbol                              | Parameter                 | Conditions                                    | Minimum                     | Maximum                     | Unit |  |  |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     | _                                             | 1.65                        | 1.95                        | V    |  |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  | _                                             | 0.65 ×<br>V <sub>CCIO</sub> | 2.25 (12)                   | V    |  |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   | _                                             | -0.3                        | 0.35 ×<br>V <sub>CCIO</sub> | V    |  |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ to } -8 \text{ mA } (11)$ | V <sub>CCIO</sub> - 0.45    | _                           | V    |  |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 to 8 mA (11)              | _                           | 0.45                        | V    |  |  |  |  |

| Table 4–13. SSTL-3 Class I Specifications (Part 2 of 2) |                           |                                |                        |         |                         |      |  |  |

|---------------------------------------------------------|---------------------------|--------------------------------|------------------------|---------|-------------------------|------|--|--|

| Symbol                                                  | Parameter                 | Conditions                     | Minimum                | Typical | Maximum                 | Unit |  |  |

| $V_{REF}$                                               | Reference voltage         | _                              | 1.3                    | 1.5     | 1.7                     | V    |  |  |

| V <sub>IH</sub>                                         | High-level input voltage  | _                              | V <sub>REF</sub> + 0.2 | _       | V <sub>CCIO</sub> + 0.3 | ٧    |  |  |

| $V_{IL}$                                                | Low-level input voltage   | _                              | -0.3                   | _       | V <sub>REF</sub> - 0.2  | ٧    |  |  |

| V <sub>OH</sub>                                         | High-level output voltage | $I_{OH} = -8 \text{ mA } (11)$ | V <sub>TT</sub> + 0.6  | _       | _                       | V    |  |  |

| V <sub>OL</sub>                                         | Low-level output voltage  | I <sub>OL</sub> = 8 mA (11)    | _                      | _       | V <sub>TT</sub> - 0.6   | ٧    |  |  |

| Table 4–14        | Table 4–14. SSTL-3 Class II Specifications |                               |                         |                  |                         |      |  |  |  |

|-------------------|--------------------------------------------|-------------------------------|-------------------------|------------------|-------------------------|------|--|--|--|

| Symbol            | Parameter                                  | Conditions                    | Minimum                 | Typical          | Maximum                 | Unit |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage                      | _                             | 3.0                     | 3.3              | 3.6                     | V    |  |  |  |

| V <sub>TT</sub>   | Termination voltage                        | _                             | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V    |  |  |  |

| V <sub>REF</sub>  | Reference voltage                          | _                             | 1.3                     | 1.5              | 1.7                     | V    |  |  |  |

| V <sub>IH</sub>   | High-level input voltage                   | _                             | V <sub>REF</sub> + 0.2  | _                | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage                    | _                             | -0.3                    | _                | V <sub>REF</sub> - 0.2  | V    |  |  |  |

| V <sub>OH</sub>   | High-level output voltage                  | I <sub>OH</sub> = -16 mA (11) | V <sub>TT</sub> + 0.8   | _                | _                       | V    |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage                   | I <sub>OL</sub> = 16 mA (11)  | _                       | _                | V <sub>TT</sub> – 0.8   | V    |  |  |  |

| Table 4–15. Bus Hold Parameters |                                                |     |     |     |                   |       |      |     |      |      |

|---------------------------------|------------------------------------------------|-----|-----|-----|-------------------|-------|------|-----|------|------|

|                                 |                                                |     |     |     | V <sub>CCIO</sub> | Level |      |     |      |      |

| Parameter                       | Conditions                                     | 1.5 | 5 V | 1.8 | B V               | 2.    | 5 V  | 3.3 | 3 V  | Unit |

|                                 |                                                | Min | Max | Min | Max               | Min   | Max  | Min | Max  |      |

| Low sustaining current          | $V_{IN} > V_{IL}$ (maximum)                    | _   | _   | 30  | _                 | 50    | _    | 70  | _    | μΑ   |

| High sustaining current         | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | _   | _   | -30 | _                 | -50   | _    | -70 | _    | μΑ   |

| Low overdrive current           | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _   | _   | _   | 200               | _     | 300  | _   | 500  | μА   |

| High overdrive current          | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _   | _   | _   | -200              | _     | -300 | _   | -500 | μА   |

| Table 4–16. Cyclone Device Capacitance   Note (14) |                                                                    |         |      |  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|---------|------|--|--|--|--|--|

| Symbol                                             | Parameter                                                          | Typical | Unit |  |  |  |  |  |

| C <sub>IO</sub>                                    | Input capacitance for user I/O pin                                 | 4.0     | pF   |  |  |  |  |  |

| C <sub>LVDS</sub>                                  | Input capacitance for dual-purpose LVDS/user I/O pin               | 4.7     | pF   |  |  |  |  |  |

| C <sub>VREF</sub>                                  | Input capacitance for dual-purpose V <sub>REF</sub> /user I/O pin. | 12.0    | pF   |  |  |  |  |  |

| C <sub>DPCLK</sub>                                 | Input capacitance for dual-purpose DPCLK/user I/O pin.             | 4.4     | pF   |  |  |  |  |  |

| C <sub>CLK</sub>                                   | Input capacitance for CLK pin.                                     | 4.7     | pF   |  |  |  |  |  |

### *Notes to Tables 4–1 through 4–16:*

- (1) Refer to the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.5$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

- (7)  $V_I$  = ground, no load, no toggling inputs.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) R<sub>CONF</sub> is the measured value of internal pull-up resistance when the I/O pin is tied directly to GND. R<sub>CONF</sub> value will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (11) Drive strength is programmable according to values in Cyclone Architecture chapter in the Cyclone Device Handbook.

- (12) Overdrive is possible when a 1.5 V or 1.8 V and a 2.5 V or 3.3 V input signal feeds an input pin. Turn on "Allow voltage overdrive" for LVTTL/LVCMOS input pins in the Assignments > Device > Device and Pin Options > Pin Placement tab when a device has this I/O combination. However, higher leakage current is expected.

- (13) The Cyclone LVDS interface requires a resistor network outside of the transmitter channels.

- (14) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within ±0.5 pF.

Typically, the user-mode current during device operation is lower than the power-up current in Table 4–17. Altera recommends using the Cyclone Power Calculator, available on the Altera web site, to estimate the user-mode  $I_{\text{CCINT}}$  consumption and then select power supplies or regulators based on the higher value.

## **Timing Model**

The DirectDrive technology and MultiTrack interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Cyclone device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

## **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus® II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–18 shows the status of the Cyclone device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 4–18. Cyclone Device Timing Model Status |             |       |  |  |  |  |

|------------------------------------------------|-------------|-------|--|--|--|--|

| Device                                         | Preliminary | Final |  |  |  |  |

| EP1C3                                          | _           | ✓     |  |  |  |  |

| EP1C4                                          | _           | ✓     |  |  |  |  |

| EP1C6                                          | _           | ✓     |  |  |  |  |

| EP1C12                                         | _           | ✓     |  |  |  |  |

| EP1C20                                         | _           | ✓     |  |  |  |  |

|                  |                             |                             | R   | esources U            | sed                     | Performance                |                            |                            |

|------------------|-----------------------------|-----------------------------|-----|-----------------------|-------------------------|----------------------------|----------------------------|----------------------------|

| Resource<br>Used | Design Size and<br>Function | Mode                        | LEs | M4K<br>Memory<br>Bits | M4K<br>Memory<br>Blocks | -6 Speed<br>Grade<br>(MHz) | -7 Speed<br>Grade<br>(MHz) | -8 Speed<br>Grade<br>(MHz) |

| M4K              | RAM 128 × 36 bit            | Single port                 | _   | 4,608                 | 1                       | 256.00                     | 222.67                     | 197.01                     |

| memory<br>block  | RAM 128 × 36 bit            | Simple<br>dual-port<br>mode | _   | 4,608                 | 1                       | 255.95                     | 222.67                     | 196.97                     |

|                  | RAM 256 × 18 bit            | True dual-<br>port mode     | _   | 4,608                 | 1                       | 255.95                     | 222.67                     | 196.97                     |

|                  | FIFO 128 × 36 bit           | _                           | 40  | 4,608                 | 1                       | 256.02                     | 222.67                     | 197.01                     |

|                  | Shift register 9 × 4 × 128  | Shift register              | 11  | 4,536                 | 1                       | 255.95                     | 222.67                     | 196.97                     |

Note to Table 4-20:

## **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–21 through 4–24 describe the Cyclone device internal timing microparameters for LEs, IOEs, M4K memory structures, and MultiTrack interconnects.

| Table 4–21. LE Internal Timing Microparameter Descriptions |                                                    |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Symbol                                                     | Parameter                                          |  |  |  |  |  |

| t <sub>SU</sub>                                            | LE register setup time before clock                |  |  |  |  |  |

| t <sub>H</sub>                                             | LE register hold time after clock                  |  |  |  |  |  |

| t <sub>CO</sub>                                            | LE register clock-to-output delay                  |  |  |  |  |  |

| t <sub>LUT</sub>                                           | LE combinatorial LUT delay for data-in to data-out |  |  |  |  |  |

| t <sub>CLR</sub>                                           | Minimum clear pulse width                          |  |  |  |  |  |

| t <sub>PRE</sub>                                           | Minimum preset pulse width                         |  |  |  |  |  |

| t <sub>CLKHL</sub>                                         | Minimum clock high or low time                     |  |  |  |  |  |

<sup>(1)</sup> The performance numbers for this function are from an EP1C6 device in a 240-pin PQFP package.

| Table 4–40. Cyclone I/O Standard Column Pin Input Delay Adders (Part 2 of 2) |                |      |         |                |     |                |      |

|------------------------------------------------------------------------------|----------------|------|---------|----------------|-----|----------------|------|

| 1/0 04                                                                       | -6 Speed Grade |      | -7 Spee | -7 Speed Grade |     | -8 Speed Grade |      |

| I/O Standard                                                                 | Min            | Max  | Min     | Max            | Min | Max            | Unit |

| SSTL-2 class II                                                              |                | -278 | _       | -320           | _   | -362           | ps   |

| LVDS                                                                         |                | -261 | _       | -301           | _   | -340           | ps   |

| Table 4–41. Cyclone I/O Standard Row Pin Input Delay Adders |                |      |                |      |                |      |      |

|-------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| I/O Standard                                                | -6 Speed Grade |      | -7 Speed Grade |      | -8 Speed Grade |      | IIii |

| I/O Standard                                                | Min            | Max  | Min            | Max  | Min            | Max  | Unit |

| LVCMOS                                                      | _              | 0    | _              | 0    | _              | 0    | ps   |

| 3.3-V LVTTL                                                 | _              | 0    | _              | 0    | _              | 0    | ps   |

| 2.5-V LVTTL                                                 | _              | 27   | _              | 31   | _              | 35   | ps   |

| 1.8-V LVTTL                                                 | _              | 182  | _              | 209  | _              | 236  | ps   |

| 1.5-V LVTTL                                                 | _              | 278  | _              | 319  | _              | 361  | ps   |

| 3.3-V PCI (1)                                               | _              | 0    | _              | 0    | _              | 0    | ps   |

| SSTL-3 class I                                              | _              | -250 | _              | -288 | _              | -325 | ps   |

| SSTL-3 class II                                             | _              | -250 | _              | -288 | _              | -325 | ps   |

| SSTL-2 class I                                              | _              | -278 | _              | -320 | _              | -362 | ps   |

| SSTL-2 class II                                             | _              | -278 | _              | -320 | _              | -362 | ps   |

| LVDS                                                        | _              | -261 | _              | -301 | _              | -340 | ps   |

| Standard    |       | -6 Speed Grade |      | -7 Speed Grade |        | -8 Speed Grade |        | 11-4 |

|-------------|-------|----------------|------|----------------|--------|----------------|--------|------|

|             |       | Min            | Max  | Min            | Max    | Min            | Max    | Unit |

| LVCMOS      | 2 mA  | _              | 0    | _              | 0      | _              | 0      | ps   |

|             | 4 mA  | _              | -489 | _              | -563   | _              | -636   | ps   |

|             | 8 mA  | _              | -855 | _              | -984   | _              | -1,112 | ps   |

|             | 12 mA | _              | -993 | _              | -1,142 | _              | -1,291 | ps   |

| 3.3-V LVTTL | 4 mA  | _              | 0    | _              | 0      | _              | 0      | ps   |

|             | 8 mA  | _              | -347 | _              | -400   | _              | -452   | ps   |

|             | 12 mA | _              | -858 | _              | -987   | _              | -1,116 | ps   |

|             | 16 mA | _              | -819 | _              | -942   | _              | -1,065 | ps   |

|             | 24 mA | _              | -993 | _              | -1,142 | _              | -1,291 | ps   |

| Table 4–44. Cyclone I/O Standard Output Delay Adders for Slow Slew Rate on Column Pins (Part 2 of 2) |      |                |       |                |       |                |       |         |

|------------------------------------------------------------------------------------------------------|------|----------------|-------|----------------|-------|----------------|-------|---------|

| I/O Standard                                                                                         |      | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | II.a.iA |

|                                                                                                      |      | Min            | Max   | Min            | Max   | Min            | Max   | Unit    |

| 1.5-V LVTTL                                                                                          | 2 mA | _              | 6,789 | _              | 7,807 | _              | 8,825 | ps      |

|                                                                                                      | 4 mA | _              | 5,109 | _              | 5,875 | _              | 6,641 | ps      |

|                                                                                                      | 8 mA | _              | 4,793 | _              | 5,511 | _              | 6,230 | ps      |

| SSTL-3 class I                                                                                       |      | _              | 1,390 | _              | 1,598 | _              | 1,807 | ps      |

| SSTL-3 class II                                                                                      |      | _              | 989   | _              | 1,137 | _              | 1,285 | ps      |

| SSTL-2 class I                                                                                       |      | _              | 1,965 | _              | 2,259 | _              | 2,554 | ps      |

| SSTL-2 class II                                                                                      |      | _              | 1,692 | _              | 1,945 |                | 2,199 | ps      |

| LVDS                                                                                                 |      | _              | 802   | _              | 922   | _              | 1,042 | ps      |

|              |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Unit |

|--------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| I/O Standard |       |                |       |                |       |                |       |      |

|              |       | Min            | Max   | Min            | Max   | Min            | Max   |      |

| LVCMOS       | 2 mA  | _              | 1,800 | _              | 2,070 | _              | 2,340 | ps   |

|              | 4 mA  | _              | 1,311 | _              | 1,507 | _              | 1,704 | ps   |

|              | 8 mA  | _              | 945   | _              | 1,086 | _              | 1,228 | ps   |

|              | 12 mA | _              | 807   | _              | 928   | _              | 1,049 | ps   |

| 3.3-V LVTTL  | 4 mA  | _              | 1,831 | _              | 2,105 | _              | 2,380 | ps   |

|              | 8 mA  | _              | 1,484 | _              | 1,705 | _              | 1,928 | ps   |

|              | 12 mA | _              | 973   | _              | 1,118 | _              | 1,264 | ps   |

|              | 16 mA | _              | 1,012 | _              | 1,163 | _              | 1,315 | ps   |

|              | 24 mA | _              | 838   | _              | 963   | _              | 1,089 | ps   |

| 2.5-V LVTTL  | 2 mA  | _              | 2,747 | _              | 3,158 | _              | 3,570 | ps   |

|              | 8 mA  | _              | 1,757 | _              | 2,019 | _              | 2,283 | ps   |

|              | 12 mA | _              | 1,763 | _              | 2,026 | _              | 2,291 | ps   |

|              | 16 mA | _              | 1,623 | _              | 1,865 | _              | 2,109 | ps   |

| 1.8-V LVTTL  | 2 mA  | _              | 5,506 | _              | 6,331 | _              | 7,157 | ps   |

|              | 8 mA  | _              | 4,220 | _              | 4,852 | _              | 5,485 | ps   |

|              | 12 mA | _              | 4,008 | _              | 4,608 | _              | 5,209 | ps   |

| 1.5-V LVTTL  | 2 mA  | _              | 6,789 | _              | 7,807 | _              | 8,825 | ps   |

|              | 4 mA  | _              | 5,109 | _              | 5,875 | _              | 6,641 | ps   |

|              | 8 mA  | _              | 4,793 | _              | 5,511 | _              | 6,230 | ps   |

| 3.3-V PCI    |       | _              | 923   | _              | 1,061 | _              | 1,199 | ps   |

| July 2003<br>v1.1 | Updated timing information. Timing finalized for EP1C6 and EP1C20 devices. Updated performance information. Added PLL Timing section. | _ |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|---|

| May 2003<br>v1.0  | Added document to Cyclone Device Handbook.                                                                                            | _ |