# E·XFL

### NXP USA Inc. - KMPC8280CZUUPEA Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC G2_LE                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 450MHz                                                                  |

| Co-Processors/DSP               | Communications; RISC CPM                                                |

| RAM Controllers                 | DRAM, SDRAM                                                             |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100Mbps (3)                                                          |

| SATA                            | -                                                                       |

| USB                             | USB 2.0 (1)                                                             |

| Voltage - I/O                   | 3.3V                                                                    |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 480-LBGA Exposed Pad                                                    |

| Supplier Device Package         | 480-TBGA (37.5x37.5)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8280czuupea |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Common on-chip processor (COP) test interface

- High-performance (SPEC95 benchmark at 450 MHz; 855 Dhrystones MIPS at 450 MHz)

- Supports bus snooping

- Support for data cache coherency

- Floating-point unit (FPU)

- Separate power supply for internal logic and for I/O

- Separate PLLs for G2\_LE core and for the communications processor module (CPM)

- G2\_LE core and CPM can run at different frequencies for power/performance optimization

- Internal core/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 4.5:1, 5:1, 6:1, 7:1, 8:1

- Internal CPM/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1, 8:1 ratios

- 64-bit data and 32-bit address 60x bus

- Bus supports multiple master designs

- Supports single- and four-beat burst transfers

- 64-, 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller

- Supports data parity or ECC and address parity

- 32-bit data and 18-bit address local bus

- Single-master bus, supports external slaves

- Eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller

- 60x-to-PCI bridge

- Programmable host bridge and agent

- 32-bit data bus, 66.67/83.3/100 MHz, 3.3 V

- Synchronous and asynchronous 60x and PCI clock modes

- All internal address space available to external PCI host

- DMA for memory block transfers

- PCI-to-60x address remapping

- PCI bridge

- PCI Specification Revision 2.2 compliant and supports frequencies up to 66 MHz

- On-chip arbitration

- Support for PCI-to-60x-memory and 60x-memory-to-PCI streaming

- PCI host bridge or peripheral capabilities

- Includes 4 DMA channels for the following transfers:

- PCI-to-60x to 60x-to-PCI

- 60x-to-PCI to PCI-to-60x

- 60x-to-PCI to 60x-to-PCI

**DC Electrical Characteristics**

| Characteristic                      | Symbol          | Min | Max | Unit |

|-------------------------------------|-----------------|-----|-----|------|

| I <sub>OL</sub> = 6.0mA             | V <sub>OL</sub> | —   | 0.4 | V    |

| BR                                  | 02              |     |     |      |

| BG                                  |                 |     |     |      |

| ABB/IRQ2                            |                 |     |     |      |

| TS                                  |                 |     |     |      |

| A[0-31]                             |                 |     |     |      |

| TT[0-4]                             |                 |     |     |      |

| TBST                                |                 |     |     |      |

| TSIZE[0-3]                          |                 |     |     |      |

| AACK                                |                 |     |     |      |

| ARTRY                               |                 |     |     |      |

| DBG                                 |                 |     |     |      |

| DBB/IRQ3                            |                 |     |     |      |

| D[0-63]                             |                 |     |     |      |

| DP(0)/ <u>RSRV/EXT_BR2</u>          |                 |     |     |      |

| DP(1)/IRQ1/EXT_BG2                  |                 |     |     |      |

| DP(2)/TLBISYNC/IRQ2/EXT_DBG2        |                 |     |     |      |

| DP(3)/IRQ3/EXT_BR3/CKSTP_OUT        |                 |     |     |      |

| DP(4)/IRQ4/EXT_BG3/CORE_SREST       |                 |     |     |      |

| DP(5)/TBEN/EXT_DBG3/IRQ5/CINT       |                 |     |     |      |

| DP(6)/CSE(0)/IRQ6                   |                 |     |     |      |

| DP(7)/CSE(1)/IRQ7                   |                 |     |     |      |

| PSDVAL                              |                 |     |     |      |

| TA                                  |                 |     |     |      |

|                                     |                 |     |     |      |

| GBL/IRQ1                            |                 |     |     |      |

|                                     |                 |     |     |      |

| WT/BADDR30/IRQ3<br>L2_HIT/IRQ4      |                 |     |     |      |

|                                     |                 |     |     |      |

| CPU_BG/BADDR31/IRQ5/CINT<br>CPU_DBG |                 |     |     |      |

|                                     |                 |     |     |      |

| CPU_BR<br>IRQ0/NMI_OUT              |                 |     |     |      |

| IRQ7/PCI_RSTINT_OUT/APE             |                 |     |     |      |

| PORESET                             |                 |     |     |      |

| HRESET                              |                 |     |     |      |

| SRESET                              |                 |     |     |      |

| RSTCONF                             |                 |     |     |      |

|                                     |                 |     |     |      |

## Table 5. DC Electrical Characteristics<sup>1</sup> (continued)

#### **DC Electrical Characteristics**

| Characteristic                            | Symbol          | Min | Мах | Unit |

|-------------------------------------------|-----------------|-----|-----|------|

| I <sub>OL</sub> = 5.3mA                   | V <sub>OL</sub> |     | 0.4 | V    |

| <u>ČŠ</u> [0-9]                           | 02              |     |     |      |

| CS(10)/BCTL1                              |                 |     |     |      |

| <u>CS(11)/AP(0)</u>                       |                 |     |     |      |

| BADDR[27-28]                              |                 |     |     |      |

| ALE                                       |                 |     |     |      |

| BCTLO                                     |                 |     |     |      |

| PWE[0-7]/PSDDQM[0-7]/PBS[0-7]             |                 |     |     |      |

| PSDA10/PGPL0                              |                 |     |     |      |

| PSDWE/PGPL1                               |                 |     |     |      |

| POE/PSDRAS/PGPL2                          |                 |     |     |      |

| PSDCAS/PGPL3                              |                 |     |     |      |

| PGTA/PUPMWAIT/PGPL4/PPBS                  |                 |     |     |      |

| PSDAMUX/PGPL5                             |                 |     |     |      |

| LWE[0-3]LSDDQM[0-3]/LBS[0-3]/PCI_CFG[0-3] | l               |     |     |      |

| LSDA10/LGPL0/PCI_MODCKH0                  | 1               |     |     |      |

| LSDWE/LGPL1/PCI_MODCKH1                   | l               |     |     |      |

| LOE/LSDRAS/LGPL2/PCI_MODCKH2              | l               |     |     |      |

| LSDCAS/LGPL3/PCI_MODCKH3                  |                 |     |     |      |

| LGTA/LUPMWAIT/LGPL4/LPBS                  |                 |     |     |      |

| LSDAMUX/LGPL5/PCI_MODCK                   |                 |     |     |      |

| LSDAMOX/LGPL3/PCI_MODCK                   |                 |     |     |      |

|                                           |                 |     |     |      |

| MODCK[1-3]/AP[1-3]/TC[0-2]/BNKSEL[0-2]    |                 |     |     |      |

| $I_{OL} = 3.2mA$                          |                 |     |     |      |

|                                           |                 |     |     |      |

| L_A15/FRAME/SMI                           |                 |     |     |      |

| L_A16/TRDY                                |                 |     |     |      |

| L_A17/IRDY/CKSTP_OUT                      |                 |     |     |      |

| L_A18/STOP                                |                 |     |     |      |

| L_A19/DEVSEL                              |                 |     |     |      |

| L_A20/IDSEL                               |                 |     |     |      |

| L_A21/ <u>PERR</u>                        |                 |     |     |      |

| L_A22/SERR                                |                 |     |     |      |

| L_A23/REQ0                                |                 |     |     |      |

| L_A24/ <u>REQ1</u> /HSEJSW                |                 |     |     |      |

| L_A25/GNT0                                |                 |     |     |      |

| L_A26/GNT1/HSLED                          |                 |     |     |      |

| L_A27/GNT2/HSENUM                         |                 |     |     |      |

| L_A28/RST/CORE_SRESET                     |                 |     |     |      |

| L_A29/INTAL_A30/REQ2                      |                 |     |     |      |

| L_A31                                     | l               |     |     |      |

| LCL_D[0-31)]/AD[0-31]                     | 1               |     |     |      |

| LCL_DP[03]/C/BE[0-3]                      | l               |     |     |      |

| PA[0-31]                                  | l               |     |     |      |

| PB[4-31]                                  | 1               |     |     |      |

| PC[0-31]                                  | l               |     |     |      |

| PD[4-31]                                  | 1               |     |     |      |

| TDO                                       | 1               |     |     |      |

| QREQ                                      | l               |     |     |      |

|                                           | l               |     |     | L    |

## Table 5. DC Electrical Characteristics<sup>1</sup> (continued)

<sup>1</sup> The default configuration of the CPM pins (PA[0–31], PB[4–31], PC[0–31], PD[4–31]) is input. To prevent excessive DC current, either pull unused pins to GND or VDDH or configure them as outputs.

<sup>2</sup> TCK, TRST and PORESET have min VIH = 2.5V.

<sup>3</sup> The leakage current is measured for nominal VDDH,VCCSYN, and VDD.

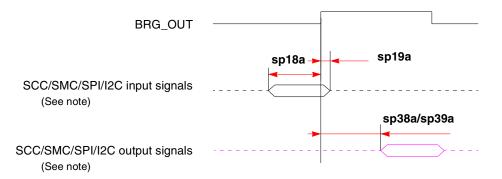

This figure shows the SCC/SMC/SPI/I<sup>2</sup>C internal clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

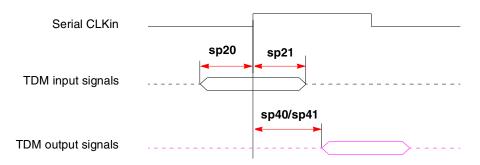

This figure shows TDM input and output signals.

Note: There are four possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

## Figure 7. TDM Signal Diagram

## **NOTE: Conditions**

The following conditions must be met in order to operate the MPC8272 family devices with 133 MHz bus: single PowerQUICC II Bus mode must be used (no external master, BCR[EBM] = 0); data bus must be in Pipeline mode (BRx[DR] = 1); internal arbiter and memory controller must be used. For expected load of above 40 pF, it is recommended that data and address buses be configured to low (25  $\Omega$ ) impedance (SIUMCR[HLBE0] = 1, SIUMCR[HLBE1] = 1).

| Spec N     | umber          |                                                    | Value (ns) |           |            |            |           |           |            |            |  |  |

|------------|----------------|----------------------------------------------------|------------|-----------|------------|------------|-----------|-----------|------------|------------|--|--|

| Setup Hold | Characteristic |                                                    | Se         | tup       |            | Hold       |           |           |            |            |  |  |

|            | Hold           |                                                    | 66<br>MHz  | 83<br>MHz | 100<br>MHz | 133<br>MHz | 66<br>MHz | 83<br>MHz | 100<br>MHz | 133<br>MHz |  |  |

| sp11       | sp10           | AACK/TA/TS/DBG/BG/BR/ARTRY/TEA                     | 6          | 5         | 3.5        | N/A        | 0.5       | 0.5       | 0.5        | N/A        |  |  |

| sp12       | sp10           | Data bus in normal mode                            | 5          | 4         | 3.5        | N/A        | 0.5       | 0.5       | 0.5        | N/A        |  |  |

| sp13       | sp10           | Data bus in pipeline mode (without ECC and PARITY) | N/A        | 4         | 2.5        | 1.5        | N/A       | 0.5       | 0.5        | 0.5        |  |  |

| sp15       | sp10           | All other pins                                     | 5          | 4         | 3.5        | N/A        | 0.5       | 0.5       | 0.5        | N/A        |  |  |

## Table 11. AC Characteristics for SIU Inputs<sup>1</sup>

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

This table lists SIU output characteristics.

Table 12. AC Characteristics for SIU Outputs<sup>1</sup>

| Spec Number |      |                               |     | Value (ns) |            |                  |               |           |            |                |  |  |

|-------------|------|-------------------------------|-----|------------|------------|------------------|---------------|-----------|------------|----------------|--|--|

|             |      | Characteristic                |     | Maximu     | m Delay    | /                | Minimum Delay |           |            |                |  |  |

| Max Min     | Min  |                               |     | 83<br>MHz  | 100<br>MHz | 133<br>MHz       | 66<br>MHz     | 83<br>MHz | 100<br>MHz | 133<br>MHz     |  |  |

| sp31        | sp30 | PSDVAL/TEA/TA                 | 7   | 6          | 5.5        | N/A              | 1             | 1         | 1          | N/A            |  |  |

| sp32        | sp30 | ADD/ADD_atr./BADDR/CI/GBL/WT  | 8   | 6.5        | 5.5        | 4.5 <sup>2</sup> | 1             | 1         | 1          | 1 <sup>2</sup> |  |  |

| sp33        | sp30 | Data bus <sup>3</sup>         | 6.5 | 6.5        | 5.5        | 4.5              | 0.8           | 0.8       | 0.8        | 1              |  |  |

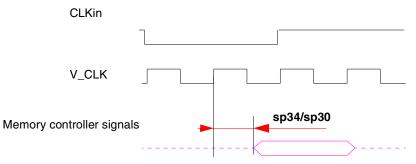

| sp34        | sp30 | Memory controller signals/ALE | 6   | 5.5        | 5.5        | 4.5              | 1             | 1         | 1          | 1              |  |  |

| sp35        | sp30 | All other signals             | 6   | 5.5        | 5.5        | N/A              | 1             | 1         | 1          | N/A            |  |  |

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

<sup>2</sup> Value is for ADD only; other sp32/sp30 signals are not applicable.

<sup>3</sup> To achieve 1 ns of hold time at 66.67/83.33/100 MHZ, a minimum loading of 20 pF is required.

## NOTE

Activating data pipelining (setting BRx[DR] in the memory controller) improves the AC timing.

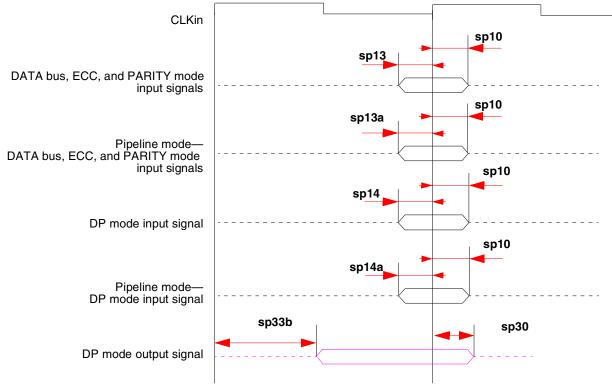

This table lists SIU input characteristics.

| Table 13. AC Characteristics for SIU Inputs <sup>1</sup> |  |

|----------------------------------------------------------|--|

|----------------------------------------------------------|--|

| Spec N | lumber |                                                     | Value (ns) |        |         |        |        |         |  |  |  |

|--------|--------|-----------------------------------------------------|------------|--------|---------|--------|--------|---------|--|--|--|

| Setup  | Hold   | Characteristic                                      |            | Setup  |         |        | Hold   |         |  |  |  |

|        |        |                                                     | 66 MHz     | 83 MHz | 100 MHz | 66 MHz | 83 MHz | 100 MHz |  |  |  |

| sp11   | sp10   | AACK/TA/TS/DBG/BG/BR/ARTRY/<br>TEA                  | 6          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |  |

| sp12   | sp10   | Data bus in normal mode                             | 5          | 4      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |  |

| sp13   | sp10   | Data bus in ECC and PARITY modes                    | 7          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |  |

| sp13a  | sp10   | Pipeline mode—Data bus (with or without ECC/PARITY) | 5          | 4      | 2.5     | 0.5    | 0.5    | 0.5     |  |  |  |

| sp14   | sp10   | DP pins                                             | 7          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |  |

| sp14a  | sp10   | Pipeline mode—DP pins                               | _          | 4      | 2.5     | _      | 0.5    | 0.5     |  |  |  |

| sp15   | sp10   | All other pins                                      | 5          | 4      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |  |

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

This table lists SIU output characteristics.

| Table 14. AC Characte | ristics for SIU | Outputs <sup>1</sup> |

|-----------------------|-----------------|----------------------|

|-----------------------|-----------------|----------------------|

| Spec N | lumber |                               |                              |        | Value   | e (ns) |        |         |  |

|--------|--------|-------------------------------|------------------------------|--------|---------|--------|--------|---------|--|

| Max    | Min    | Characteristic                | Characteristic Maximum Delay |        |         |        |        |         |  |

|        |        |                               | 66 MHz                       | 83 MHz | 100 MHz | 66 MHz | 83 MHz | 100 MHz |  |

| sp31   | sp30   | PSDVAL/TEA/TA                 | 7                            | 6      | 5.5     | 1      | 1      | 1       |  |

| sp32   | sp30   | ADD/ADD_atr./BADDR/CI/GBL/WT  | 8                            | 6.5    | 5.5     | 1      | 1      | 1       |  |

| sp33a  | sp30   | Data bus <sup>2</sup>         | 6.5                          | 6.5    | 5.5     | 0.7    | 0.7    | 0.7     |  |

| sp33b  | sp30   | DP                            | 6                            | 5.5    | 5.5     | 1      | 1      | 1       |  |

| sp34   | sp30   | Memory controller signals/ALE | 6                            | 5.5    | 5.5     | 1      | 1      | 1       |  |

| sp35   | sp30   | All other signals             | 6                            | 5.5    | 5.5     | 1      | 1      | 1       |  |

| sp35a  | sp30   | AP                            | 7                            | 7      | 7       | 1      | 1      | 1       |  |

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

$^2$  To achieve 1 ns of hold time at 66, 83, or 100 MHz, a minimum loading of 20 pF is required.

#### **AC Electrical Characteristics**

This figure shows signal behavior for all parity modes (including ECC, RMW parity, and standard parity).

Figure 10. Parity Mode Diagram

This figure shows signal behavior in MEMC mode.

### NOTE

Generally, all SoC bus and system output signals are driven from the rising edge of the input clock (CLKin). Memory controller signals, however, trigger on four points within a CLKin cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and T3 at the falling edge, of CLKin. However, the spacing of T2 and T4 depends on the PLL clock ratio selected, as shown in Table 15.

|          | Pins       |                        | Clocking Mode | PCI Clock<br>Frequency Range | Reference  |

|----------|------------|------------------------|---------------|------------------------------|------------|

| PCI_MODE | PCI_CFG[0] | PCI_MODCK <sup>1</sup> |               | (MHZ)                        | helefelide |

| 1        |            | _                      | Local bus     | —                            | Table 18   |

| 0        | 0          | 0                      | PCI host      | 50–66                        | Table 19   |

| 0        | 0          | 1                      |               | 25–50                        | Table 20   |

| 0        | 1          | 0                      | PCI agent     | 50–66                        | Table 21   |

| 0        | 1          | 1                      |               | 25–50                        | Table 22   |

Table 17. SoC Clocking Modes

<sup>1</sup> Determines PCI clock frequency range. See Section 7.2, "PCI Host Mode," and Section 7.3, "PCI Agent Mode."

Within each mode, the configuration of bus, core, PCI, and CPM frequencies is determined by seven bits during the power-on reset—three hardware configuration pins (MODCK[1–3]) and four bits from hardware configuration word[28–31] (MODCK\_H). Both the PLLs and the dividers are set according to the selected clock operation mode as described in the following sections.

## 7.1 Local Bus Mode

This table lists clock configurations for the SoC in local bus mode. The frequencies listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device.

### NOTE

Clock configurations change only after PORESET is asserted.

| Mode <sup>2</sup>  | Bus Clock <sup>3</sup><br>(MHz) |       | CPM<br>Multiplication | _        | Clock<br>Hz) | CPU<br>Multiplication | CPU Clock<br>(MHz) |       |  |  |  |  |  |

|--------------------|---------------------------------|-------|-----------------------|----------|--------------|-----------------------|--------------------|-------|--|--|--|--|--|

| MODCK_H-MODCK[1:3] | Low                             | High  | Factor <sup>4</sup>   | Low      | High         | Factor <sup>5</sup>   | Low                | High  |  |  |  |  |  |

|                    | Default Modes (MODCK_H= 0000)   |       |                       |          |              |                       |                    |       |  |  |  |  |  |

| 0000_000           | 37.5                            | 133.3 | 3                     | 112.5    | 400.0        | 4                     | 150.0              | 533.3 |  |  |  |  |  |

| 0000_001           | 33.3                            | 133.3 | 3                     | 100.0    | 400.0        | 5                     | 166.7              | 666.7 |  |  |  |  |  |

| 0000_010           | 37.5                            | 100.0 | 4                     | 150.0    | 400.0        | 4                     | 150.0              | 400.0 |  |  |  |  |  |

| 0000_011           | 30.0                            | 100.0 | 4                     | 120.0    | 400.0        | 5                     | 150.0              | 500.0 |  |  |  |  |  |

| 0000_100           | 60.0                            | 167.0 | 2                     | 120.0    | 334.0        | 2.5                   | 150.0              | 417.5 |  |  |  |  |  |

| 0000_101           | 50.0                            | 167.0 | 2                     | 100.0    | 334.0        | 3                     | 150.0              | 501.0 |  |  |  |  |  |

| 0000_110           | 60.0                            | 160.0 | 2.5                   | 150.0    | 400.0        | 2.5                   | 150.0              | 400.0 |  |  |  |  |  |

| 0000_111           | 50.0                            | 160.0 | 2.5                   | 125.0    | 400.0        | 3                     | 150.0              | 480.0 |  |  |  |  |  |

|                    | •                               |       | Full Configurat       | ion Mode | S            |                       |                    |       |  |  |  |  |  |

| 0001_000           | 50.0                            | 167.0 | 2                     | 100.0    | 334.0        | 4                     | 200.0              | 668.0 |  |  |  |  |  |

Table 18. Clock Configurations for Local Bus Mode<sup>1</sup>

| Mode <sup>3</sup>      | Bus Clock <sup>4</sup><br>(MHz) |       | CPM<br>Multiplication |       | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | ck<br>PCI<br>Division |      | PCI Clock<br>(MHz) |  |

|------------------------|---------------------------------|-------|-----------------------|-------|--------------|-----------------------|-------|--------------|-----------------------|------|--------------------|--|

| MODCK_H-<br>MODCK[1-3] | Low                             | High  | Factor <sup>5</sup>   | Low   | High         | Factor <sup>6</sup>   | Low   | High         | Factor                | Low  | High               |  |

| 0001_001               | 50.0                            | 66.7  | 3                     | 150.0 | 200.0        | 6                     | 300.0 | 400.0        | 3                     | 50.0 | 66.7               |  |

| 0001_010               | 50.0                            | 66.7  | 3                     | 150.0 | 200.0        | 7                     | 350.0 | 466.6        | 3                     | 50.0 | 66.7               |  |

| 0001_011               | 50.0                            | 66.7  | 3                     | 150.0 | 200.0        | 8                     | 400.0 | 533.3        | 3                     | 50.0 | 66.7               |  |

| 0010_000               | 50.0                            | 66.7  | 4                     | 200.0 | 266.6        | 5                     | 250.0 | 333.3        | 4                     | 50.0 | 66.7               |  |

| 0010_001               | 50.0                            | 66.7  | 4                     | 200.0 | 266.6        | 6                     | 300.0 | 400.0        | 4                     | 50.0 | 66.7               |  |

| 0010_010               | 50.0                            | 66.7  | 4                     | 200.0 | 266.6        | 7                     | 350.0 | 466.6        | 4                     | 50.0 | 66.7               |  |

| 0010_011               | 50.0                            | 66.7  | 4                     | 200.0 | 266.6        | 8                     | 400.0 | 533.3        | 4                     | 50.0 | 66.7               |  |

| 0010_100               | 75.0                            | 100.0 | 4                     | 300.0 | 400.0        | 5                     | 375.0 | 500.0        | 6                     | 50.0 | 66.7               |  |

| 0010_101               | 75.0                            | 100.0 | 4                     | 300.0 | 400.0        | 5.5                   | 412.5 | 549.9        | 6                     | 50.0 | 66.7               |  |

| 0010_110               | 75.0                            | 100.0 | 4                     | 300.0 | 400.0        | 6                     | 450.0 | 599.9        | 6                     | 50.0 | 66.7               |  |

|                        |                                 |       |                       |       |              |                       |       |              |                       |      |                    |  |

| 0011_000               | 50.0                            | 66.7  | 5                     | 250.0 | 333.3        | 5                     | 250.0 | 333.3        | 5                     | 50.0 | 66.7               |  |

| 0011_001               | 50.0                            | 66.7  | 5                     | 250.0 | 333.3        | 6                     | 300.0 | 400.0        | 5                     | 50.0 | 66.7               |  |

| 0011_010               | 50.0                            | 66.7  | 5                     | 250.0 | 333.3        | 7                     | 350.0 | 466.6        | 5                     | 50.0 | 66.7               |  |

| 0011_011               | 50.0                            | 66.7  | 5                     | 250.0 | 333.3        | 8                     | 400.0 | 533.3        | 5                     | 50.0 | 66.7               |  |

| 0100_000               |                                 |       |                       |       |              | Reserved              |       |              |                       |      |                    |  |

| 0100_001               | 50.0                            | 66.7  | 6                     | 300.0 | 400.0        | 6                     | 300.0 | 400.0        | 6                     | 50.0 | 66.7               |  |

| 0100_010               | 50.0                            | 66.7  | 6                     | 300.0 | 400.0        | 7                     | 350.0 | 466.6        | 6                     | 50.0 | 66.7               |  |

| 0100_011               | 50.0                            | 66.7  | 6                     | 300.0 | 400.0        | 8                     | 400.0 | 533.3        | 6                     | 50.0 | 66.7               |  |

| 0101 000               | 60.0                            | 66.7  | 2                     | 120.0 | 133.3        | 2.5                   | 150.0 | 166.7        | 2                     | 60.0 | 66.7               |  |

| 0101_001               | 50.0                            | 66.7  | 2                     | 100.0 | 133.3        | 3                     | 150.0 |              | 2                     | 50.0 | 66.7               |  |

| 0101_010               | 50.0                            | 66.7  | 2                     | 100.0 | 133.3        | 3.5                   | 175.0 | 233.3        | 2                     | 50.0 | 66.7               |  |

| 0101_011               | 50.0                            | 66.7  | 2                     | 100.0 |              | 4                     | 200.0 |              | 2                     | 50.0 | 66.7               |  |

| 0101_100               | 50.0                            | 66.7  | 2                     | 100.0 |              | 4.5                   | 225.0 |              | 2                     | 50.0 | 66.7               |  |

| 0110_000               | 60.0                            | 80.0  | 2.5                   | 150.0 | 200.0        | 2.5                   | 150.0 | 200.0        | 3                     | 50.0 | 66.7               |  |

| 0110_000               | 60.0                            | 80.0  | 2.5                   | 150.0 | 200.0        | 3                     | 180.0 |              | 3                     | 50.0 | 66.7               |  |

| 0110_001               | 60.0                            | 80.0  | 2.5                   | 150.0 | 200.0        | 3.5                   | 210.0 |              | 3                     | 50.0 | 66.7               |  |

## Table 19. Clock Configurations for PCI Host Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

**Clock Configuration Modes**

## NOTE: PCI\_MODCK

In PCI mode only, PCI\_MODCK comes from the LGPL5 pin and MODCK\_H[0–3] comes from {LGPL0, LGPL1, LGPL2, LGPL3}.

## **NOTE: Tval (Output Hold)**

The minimum Tval = 2 ns when PCI\_MODCK = 1, and the minimum Tval = 1 ns when PCI\_MODCK = 0. Therefore, designers should use clock configurations that fit this condition to achieve PCI-compliant AC timing.

| Table 21. Clock C | onfigurations | for PCI | Agent Mode | (PCI | _MODCK=0) <sup>1,2</sup> |

|-------------------|---------------|---------|------------|------|--------------------------|

|                   |               |         |            |      |                          |

| Mode <sup>3</sup>      | PCI (<br>(M | Clock<br>Hz) | CPM<br>Multiplication | CPM<br>(M | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | Bus<br>Division |      | Clock<br>Hz) |

|------------------------|-------------|--------------|-----------------------|-----------|--------------|-----------------------|-------|--------------|-----------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low         | High         | Factor <sup>4</sup>   | Low       | High         | Factor <sup>5</sup>   | Low   | High         | Factor          | Low  | High         |

|                        |             |              | De                    | efault N  | lodes (      | MODCK_H=0000          |       |              |                 | •    |              |

| 0000_000               | 60.0        | 66.7         | 2                     | 120.0     | 133.3        | 2.5                   | 150.0 | 166.7        | 2               | 60.0 | 66.7         |

| 0000_001               | 50.0        | 66.7         | 2                     | 100.0     | 133.3        | 3                     | 150.0 | 200.0        | 2               | 50.0 | 66.7         |

| 0000_010               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 3                     | 150.0 | 200.0        | 3               | 50.0 | 66.7         |

| 0000_011               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 4                     | 200.0 | 266.6        | 3               | 50.0 | 66.7         |

| 0000_100               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 3                     | 180.0 | 240.0        | 2.5             | 60.0 | 80.0         |

| 0000_101               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 3.5                   | 210.0 | 280.0        | 2.5             | 60.0 | 80.0         |

| 0000_110               | 50.0        | 66.7         | 4                     | 200.0     | 266.6        | 3.5                   | 233.3 | 311.1        | 3               | 66.7 | 88.9         |

| 0000_111               | 50.0        | 66.7         | 4                     | 200.0     | 266.6        | 3                     | 240.0 | 320.0        | 2.5             | 80.0 | 106.7        |

|                        |             | •            |                       | Full C    | onfigu       | ration Modes          |       |              |                 | •    |              |

| 0001_001               | 60.0        | 66.7         | 2                     | 120.0     | 133.3        | 5                     | 150.0 | 166.7        | 4               | 30.0 | 33.3         |

| 0001_010               | 50.0        | 66.7         | 2                     | 100.0     | 133.3        | 6                     | 150.0 | 200.0        | 4               | 25.0 | 33.3         |

| 0001_011               | 50.0        | 66.7         | 2                     | 100.0     | 133.3        | 7                     | 175.0 | 233.3        | 4               | 25.0 | 33.3         |

| 0001_100               | 50.0        | 66.7         | 2                     | 100.0     | 133.3        | 8                     | 200.0 | 266.6        | 4               | 25.0 | 33.3         |

|                        |             |              |                       |           |              |                       |       |              |                 |      |              |

| 0010_001               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 3                     | 180.0 | 240.0        | 2.5             | 60.0 | 80.0         |

| 0010_010               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 3.5                   | 210.0 | 280.0        | 2.5             | 60.0 | 80.0         |

| 0010_011               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 4                     | 240.0 | 320.0        | 2.5             | 60.0 | 80.0         |

| 0010_100               | 50.0        | 66.7         | 3                     | 150.0     | 200.0        | 4.5                   | 270.0 | 360.0        | 2.5             | 60.0 | 80.0         |

|                        |             |              |                       |           |              |                       |       |              |                 |      |              |

| 0011_000               | Reserved    |              |                       |           |              |                       |       |              |                 |      |              |

| 0011_001               |             | Reserved     |                       |           |              |                       |       |              |                 |      |              |

| 0011_010               | Reserved    |              |                       |           |              |                       |       |              |                 |      |              |

| 0011_011               |             |              |                       |           |              | Reserved              |       |              |                 |      |              |

| 0011_100               |             |              |                       |           |              | Reserved              |       |              |                 |      |              |

**Clock Configuration Modes**

| Table 22. Clock Configurations for I | PCI Agent Mode (PCI | _MODCK=1) <sup>1,2</sup> (continued) |

|--------------------------------------|---------------------|--------------------------------------|

|                                      |                     |                                      |

|                        |                                                                                                                                     |              |                                          |       |       | (                      |             |              |                 |         |              |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------|-------|-------|------------------------|-------------|--------------|-----------------|---------|--------------|

| Mode <sup>3</sup>      |                                                                                                                                     | Clock<br>Hz) | CPM Clock<br>CPM (MHz)<br>Multiplication |       | _     |                        | CPU (<br>(M | Clock<br>Hz) | Bus<br>Division |         | Clock<br>Hz) |

| MODCK_H-<br>MODCK[1-3] | Low                                                                                                                                 | High         | Factor <sup>4</sup>                      | Low   | High  | gh Factor <sup>5</sup> | Low         | High         | Factor          | Low     | High         |

| 1011_010               | 25.0                                                                                                                                | 50.0         | 8                                        | 200.0 | 400.0 | 3                      | 240.0       | 480.0        | 2.5             | 80.0    | 160.0        |

| 1011_011               | 25.0                                                                                                                                | 50.0         | 8                                        | 200.0 | 400.0 | 3.5                    | 280.0       | 560.0        | 2.5             | 80.0    | 160.0        |

| 1011_100               | 25.0                                                                                                                                | 50.0         | 8                                        | 200.0 | 400.0 | 4                      | 320.0       | 640.0        | 2.5             | 80.0    | 160.0        |

| 1100_101               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 4                      | 200.0       | 400.0        | 3               | 50.0    | 100.0        |

| 1100_110               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 4.5                    | 225.0       | 450.0        | 3               | 50.0    | 100.0        |

| 1100_111               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 5                      | 250.0       | 500.0        | 3               | 50.0    | 100.0        |

| 1101_000               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 5.5                    | 275.0       | 550.0        | 3               | 50.0    | 100.0        |

|                        |                                                                                                                                     | •            |                                          |       | •     |                        |             | • • •        |                 | •       |              |

| 1101_001               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 3.5                    | 210.0       | 420.0        | 2.5             | 60.0    | 120.0        |

| 1101_010               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 4                      | 240.0       | 480.0        | 2.5             | 60.0    | 120.0        |

| 1101_011               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 4.5                    | 270.0       | 540.0        | 2.5             | 60.0    | 120.0        |

| 1101_100               | 25.0                                                                                                                                | 50.0         | 6                                        | 150.0 | 300.0 | 5                      | 300.0       | 600.0        | 2.5             | 60.0    | 120.0        |

|                        |                                                                                                                                     |              |                                          |       |       |                        |             |              |                 |         |              |

| 1110_000               | 25.0                                                                                                                                | 50.0         | 5                                        | 125.0 | 250.0 | 2.5                    | 156.3       | 312.5        | 2               | 62.5    | 125.0        |

| 1110_001               | 25.0                                                                                                                                | 50.0         | 5                                        | 125.0 | 250.0 | 3                      | 187.5       | 375.0        | 2               | 62.5    | 125.0        |

| 1110_010               | 25.0                                                                                                                                | 50.0         | 5                                        | 125.0 | 250.0 | 3.5                    | 218.8       | 437.5        | 2               | 62.5    | 125.0        |

| 1110_011               | 25.0                                                                                                                                | 50.0         | 5                                        | 125.0 | 250.0 | 4                      | 250.0       | 500.0        | 2               | 62.5    | 125.0        |

|                        |                                                                                                                                     |              |                                          |       |       |                        |             |              |                 | · · · - |              |

| 1110_100               | 25.0                                                                                                                                | 50.0         | 5                                        | 125.0 | 250.0 | 4                      | 166.7       |              | 3               | 41.7    | 83.3         |

| 1110_101               | 25.0                                                                                                                                | 50.0         | 5                                        | 125.0 | 250.0 | 4.5                    | 187.5       | 375.0        | 3               | 41.7    | 83.3         |

| 1110_110               | 25.0                                                                                                                                | 50.0         | 5                                        |       | 250.0 | 5                      | 208.3       |              | 3               | 41.7    | 83.3         |

| 1110_111               | 25.0         50.0         5         125.0         250.0         5.5         229.2         458.3         3         41.7         83.3 |              |                                          |       |       |                        |             |              |                 |         |              |

| 1100_000               |                                                                                                                                     | Reserved     |                                          |       |       |                        |             |              |                 |         |              |

| 1100_001               |                                                                                                                                     | Reserved     |                                          |       |       |                        |             |              |                 |         |              |

| 1100_010               |                                                                                                                                     |              |                                          |       |       | Reserved               |             |              |                 |         |              |

|                        |                                                                                                                                     |              |                                          |       |       |                        |             |              |                 |         |              |

<sup>1</sup> The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not violate the frequency rating of the user's device. The minimum CPM frequency is 120 MHz. Minimum CPU frequency is determined by the clock mode. For modes with a CPU multiplication factor <= 3, the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. For modes with a CPU multiplication factor >= 3.5: for Rev 0.1 the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices.

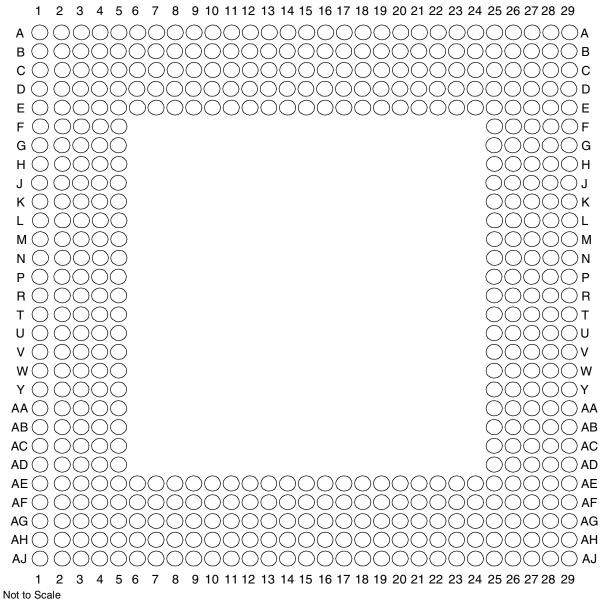

This figure shows the pinout of the ZU and VV packages as viewed from the top surface.

Figure 13. Pinout of the 480 TBGA Package (View from Top)

This table lists the pins of the MPC8280 and MPC8270, and Table 24 defines conventions and acronyms used in this table.

|                 | Ball |

|-----------------|------|

| MPC8280/MPC8270 | Dali |

| BR              | W5   |

| BG              | F4   |

Pinout

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

|                                                           | Dell                                |                   |  |  |

|-----------------------------------------------------------|-------------------------------------|-------------------|--|--|

| MPC8280/MPC8270                                           | MPC8280 only                        | Ball              |  |  |

| TDO                                                       |                                     | AF5               |  |  |

| TRIS                                                      |                                     | AB4               |  |  |

| PORESET <sup>1</sup>                                      |                                     | AG6               |  |  |

| HRESET                                                    |                                     | AH5               |  |  |

| SRESET                                                    |                                     | AF6               |  |  |

| QREQ                                                      |                                     | AA3               |  |  |

| RSTCONF                                                   |                                     | AJ4               |  |  |

| MODCK1/AP1/TC0/BNKSEL0                                    |                                     | W2                |  |  |

| MODCK2/AP2/TC1/BNKSEL1                                    |                                     | W3                |  |  |

| MODCK3/AP3/TC2/BNKSEL2                                    |                                     | W4                |  |  |

| CLKIN1                                                    |                                     | AH4               |  |  |

| PA0/RESTART1/DREQ3                                        | FCC2_UTM_TXADDR2                    | AC29 <sup>2</sup> |  |  |

| PA1/REJECT1/DONE3                                         | FCC2_UTM_TXADDR1                    | AC25 <sup>2</sup> |  |  |

| PA2/CLK20/DACK3                                           | FCC2_UTM_TXADDR0                    | AE28 <sup>2</sup> |  |  |

| PA3/CLK19/DACK4/L1RXD1A2                                  | FCC2_UTM_RXADDR0                    | AG29 <sup>2</sup> |  |  |

| PA4/REJECT2/DONE4                                         | FCC2_UTM_RXADDR1                    | AG28 <sup>2</sup> |  |  |

| PA5/RESTART2/DREQ4                                        | FCC2_UTM_RXADDR2/FCC1_UT_RXPRT<br>Y | AG26 <sup>2</sup> |  |  |

| PA6/FCC2_RXADDR3                                          | L1RSYNCA1                           | AE24 <sup>2</sup> |  |  |

| PA7/SMSYN2/FCC2_TXADDR3                                   | L1TSYNCA1/L1GNTA1                   | AH25 <sup>2</sup> |  |  |

| PA8/SMRXD2/FCC2_TXADDR4                                   | L1RXD0A1/L1RXDA1                    | AF23 <sup>2</sup> |  |  |

| PA9/SMTXD2                                                | L1TXD0A1                            | AH23 <sup>2</sup> |  |  |

| PA10/MSNUM5                                               | FCC1_UT8_RXD0/FCC1_UT16_RXD8        | AE22 <sup>2</sup> |  |  |

| PA11/MSNUM4                                               | FCC1_UT8_RXD1/FCC1_UT16_RXD9        | AH22 <sup>2</sup> |  |  |

| PA12/MSNUM3                                               | FCC1_UT8_RXD2/<br>FCC1_UT16_RXD10   | AJ21 <sup>2</sup> |  |  |

| PA13/MSNUM2                                               | FCC1_UT8_RXD3/<br>FCC1_UT16_RXD11   | AH20 <sup>2</sup> |  |  |

| PA14/FCC1_MII_HDLC_RXD3 FCC1_UT8_RXD4/<br>FCC1_UT16_RXD12 |                                     | AG19 <sup>2</sup> |  |  |

| PA15/FCC1_MII_HDLC_RXD2                                   | FCC1_UT8_RXD5/<br>FCC1_UT16_RXD13   | AF18 <sup>2</sup> |  |  |

| PA16/FCC1_MII_HDLC_RXD1/<br>FCCI_RMII_RXD1                | FCC1_UT8_RXD6/<br>FCC1_UT16_RXD14   | AF17 <sup>2</sup> |  |  |

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Р                                                     | in Name                                                             | Ball              |

|-------------------------------------------------------|---------------------------------------------------------------------|-------------------|

| MPC8280/MPC8270                                       | MPC8280 only                                                        | Dan               |

| PC0/DREQ1/BRGO7/SMSYN2/<br>L1CLKOA2                   |                                                                     | AB26 <sup>2</sup> |

| PC1/DREQ2/BRGO6/L1RQA2/ SPISEL                        |                                                                     | AD29 <sup>2</sup> |

| PC2/FCC3_CD/DONE2                                     | FCC2_UT8_TXD3                                                       | AE29 <sup>2</sup> |

| PC3/FCC3_CTS/DACK2/CTS4/<br>USB_RP                    | FCC2_UT8_TXD2                                                       | AE27 <sup>2</sup> |

| PC4/SI2_L1ST4/FCC2_CD                                 | FCC2_UTM_RXENB/<br>FCC2_UTS_RXENB                                   | AF27 <sup>2</sup> |

| PC5/SI2_L1ST3/FCC2_CTS                                | FCC2_UTM_TXCLAV/<br>FCC2_UTS_TXCLAV                                 | AF24 <sup>2</sup> |

| PC6/FCC1_CD                                           | L1CLKOC1/FCC1_UTM_RXADDR2/<br>FCC1_UTS_RXADDR2/<br>FCC1_UTM_RXCLAV1 | AJ26 <sup>2</sup> |

| PC7/FCC1_CTS                                          | L1RQC1/FCC1_UTM_TXADDR2/<br>FCC1_UTS_TXADDR2/<br>FCC1_UTM_TXCLAV1   | AJ25 <sup>2</sup> |

| PC8/CD4/RENA4/SI2_L1ST2/CTS3/<br>USBRN                | FCC1_UT16_TXD0                                                      | AF22 <sup>2</sup> |

| PC9/CTS4/CLSN4/SI2_L1ST1/<br>L1TSYNCA2/L1GNTA2/USB_RP | FCC1_UT16_TXD1                                                      | AE21 <sup>2</sup> |

| PC10/CD3/RENA3                                        | FCC1_UT16_TXD2/SI1_L1ST4/<br>FCC2_UT8_RXD3                          | AF20 <sup>2</sup> |

| PC11/CTS3/CLSN3/L1TXD3A2                              | L1CLKOD1/FCC2_UT8_RXD2                                              | AE19 <sup>2</sup> |

| PC12/CD2/RENA2                                        | SI1_L1ST3/FCC1_UTM_RXADDR1/<br>FCC1_UTS_RXADDR1                     | AE18 <sup>2</sup> |

| PC13/CTS2/CLSN2                                       | L1RQD1/FCC1_UTM_TXADDR1/<br>FCC1_UTS_TXADDR1                        | AH18 <sup>2</sup> |

| PC14/CD1/RENA1                                        | FCC1_UTM_RXADDR0/<br>FCC1_UTS_RXADDR0                               | AH17 <sup>2</sup> |

| PC15/CTS1/CLSN1/SMTXD2                                | FCC1_UTM_TXADDR0/<br>FCC1_UTS_TXADDR0                               | AG16 <sup>2</sup> |

| PC16/CLK16/TIN4                                       |                                                                     | AF15 <sup>2</sup> |

| PC17/CLK15/TIN3/BRGO8                                 |                                                                     | AJ15 <sup>2</sup> |

| PC18/CLK14/TGATE2                                     | AH14 <sup>2</sup>                                                   |                   |

| PC19/CLK13/BRGO7/SPICLK                               | AG13 <sup>2</sup>                                                   |                   |

| PC20/CLK12/TGATE1/USB_OE                              | AH12 <sup>2</sup>                                                   |                   |

| PC21/CLK11/BRGO6                                      |                                                                     | AJ11 <sup>2</sup> |

| PC22/CLK10/DONE1/FCC1_UT_TXPRT                        | Y                                                                   | AG10 <sup>2</sup> |

| PC23/CLK9/BRGO5/DACK1                                 |                                                                     | AE10 <sup>2</sup> |

## Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Nam                  | e            | Dell |

|--------------------------|--------------|------|

| MPC8275/MPC8270          | MPC8275 only | Ball |

| LSDCAS/LGPL3/PCI_MODCKH3 |              | AD5  |

| LGTA/LUPMWAIT/LGPL4/LPBS |              | AC5  |

| LGPL5/LSDAMUX/PCI_MODCK  |              | AB5  |

| LWR                      |              | AF6  |

| L_A14/PAR                |              | AE13 |

| L_A15/FRAME/SMI          |              | AD15 |

| L_A16/TRDY               |              | AF16 |

| L_A17/IRDY/CKSTP_OUT     |              | AF15 |

| L_A18/STOP               |              | AE15 |

| L_A19/DEVSEL             |              | AE14 |

| L_A20/IDSEL              |              | AC17 |

| L_A21/PERR               |              | AD14 |

| L_A22/SERR               |              | AF13 |

| L_A23/REQ0               |              | AE20 |

| L_A24/REQ1/HSEJSW        |              | AC14 |

| L_A25/GNT0               |              | AC19 |

| L_A26/GNT1/HSLED         |              | AD13 |

| L_A27/GNT2/HSENUM        |              | AF21 |

| L_A28/RST/CORE_SRESET    |              | AF22 |

| L_A29/INTA               |              | AE21 |

| L_A30/REQ2               |              | AB14 |

| L_A31/DLLOUT             |              | AD20 |

| LCL_D0/AD0               |              | AB9  |

| LCL_D1/AD1               |              | AB10 |

| LCL_D2/AD2               |              | AC10 |

| LCL_D3/AD3               |              | AD10 |

| LCL_D4/AD4               |              | AE10 |

| LCL_D5/AD5               |              | AF10 |

| LCL_D6/AD6               |              | AF11 |

| LCL_D7/AD7               |              | AB12 |

| LCL_D8/AD8               |              | AB11 |

| LCL_D9/AD9               |              | AF12 |

| LCL_D10/AD10             |              | AE11 |

Pinout

#### Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

|                                                                                                                         | Ball                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPC8275/MPC8270                                                                                                         | MPC8275 only                      | Dan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PD27/TXD2                                                                                                               | FCC1_UT16_RXD7                    | H22 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PD28/RXD2                                                                                                               | FCC1_UT16_TXD7                    | B22 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PD29/RTS1/TENA1<br>FCC1_UTM_RXADDR3/<br>FCC1_UTS_RXADDR3/<br>FCC1_UTM_RXCLAV2/<br>FCC2_UTM_RXADDR4/<br>FCC2_UTS_RXADDR1 |                                   | D22 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PD30/TXD1                                                                                                               | FCC2_UTM_TXENB/<br>FCC2_UTS_TXENB | C21 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PD31/RXD1                                                                                                               | I                                 | E19 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCCSYN                                                                                                                  |                                   | D19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VCCSYN1                                                                                                                 |                                   | K6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLKIN2                                                                                                                  |                                   | K21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SPARE4 <sup>3</sup>                                                                                                     |                                   | C14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PCI_MODE <sup>4</sup>                                                                                                   |                                   | AD24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SPARE6 <sup>3</sup>                                                                                                     |                                   | B15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| No connect <sup>5</sup>                                                                                                 |                                   | E17, C23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I/O power                                                                                                               |                                   | E6, F6, H6, L5, L6, P6, T6, U6, V5,<br>Y5, AA6, AA8, AA10, AA11, AA14,<br>AA16, AA17, AB19, AB20, W21,<br>U21, T21, P21, N21, M22, J22, H21,<br>F21, F19, F17, E16, F14, E13, E12,<br>F10, E10, E9                                                                                                                                                                                                                                                                                                                           |

| Core Power                                                                                                              |                                   | L3, V4, W3, AC11, AD11, AB15,<br>U25, T24, J24, H25, F23, B19, D17,<br>C17, D10, C10                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ground                                                                                                                  |                                   | B18 <sup>6</sup> , A18 <sup>7</sup> , A2, B1, B2, A5, C5,<br>C18, D4, D6, G2, L4, P1, R1, R4,<br>AC4, AE7, AC23, Y25, N24, J23,<br>A23, D23, D20, E18, A13, A16, K10,<br>K11, K12, K13, K14, K15, K16, K17,<br>L10, L11, L12, L13, L14, L15, L16,<br>L17, M10, M11, M12, M13, M14,<br>M15, M16, M17, N10, N11, N12,<br>N13, N14, N15, N16, N17, P10, P11,<br>P12, P13, P14, P15, P16, P17, R10,<br>R11,R12, R13, R14, R15, R16, R17,<br>T10, T11, T12, T13, T14, T15, T16,<br>T17, U10, U11, U12, U13, U14, U15,<br>U16, U17 |

<sup>1</sup> Should be tied to VDDH via a 2K  $\Omega$  external pull-up resistor.

<sup>2</sup> The default configuration of the CPM pins (PA[0–31], PB[4–31], PC[0–31], PD[4–31]) is input. To prevent excessive DC current, it is recommended to either pull unused pins to GND or VDDH, or to configure them as outputs.

- <sup>3</sup> Must be pulled down or left floating.

- <sup>4</sup> If PCI is not desired, must be pulled up or left floating.

- <sup>5</sup> Sphere is not connected to die.

- <sup>6</sup> GNDSYN (B18): This pin exists as a separate ground signal in MPC826x(A) devices; it does not exist as a separate ground signal on the MPC8275/MPC8270. New designs must connect B18 to GND and follow the suggestions in Section 4.6, "Layout Practices." Old designs in which the MPC8275/MPC8270 is used as a drop-in replacement can leave the pin connected to GND with the noise filtering capacitors.

- <sup>7</sup> XFC (A18) pin: This pin is used in MPC826x(A) devices; it is not used in MPC8275/MPC8270 because there is no need for external capacitor to operate the PLL. New designs should connect A18 (XFC) pin to GND. Old designs in which the MPC8275/MPC8270 is used as a drop-in replacement can leave the pin connected to the current capacitor.

## 9 Package Description

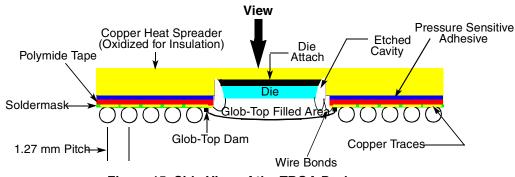

This figure shows the side profile of the TBGA package to indicate the direction of the top surface view.

Figure 15. Side View of the TBGA Package

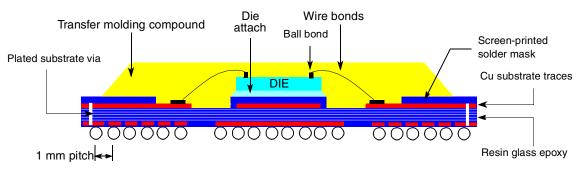

This figure shows the side profile of the PBGA package to indicate the direction of the top surface view.

Figure 16. Side View of the PBGA Package Remove

Package Description

## 9.1 Package Parameters

This table provides package parameters.

## NOTE: Temperature Reflow for the VR Package

In the VR package, sphere composition is lead-free (see Table 2). This requires higher temperature reflow than what is required for other PowerQUICC II packages. Consult "Freescale PowerQUICC II Pb-Free Packaging Information" (MPC8250PBFREEPKG) available on www.freescale.com.

| Package | SoCs                   | Outline<br>(mm) | Туре | Interconnects | Pitch<br>(mm) | Nominal Unmounted<br>Height (mm) |

|---------|------------------------|-----------------|------|---------------|---------------|----------------------------------|

| ZU      | MPC8280<br>MPC8270     | 37.5 × 37.5     | TBGA | 480           | 1.27          | 1.55                             |

| VV      | MPC8280<br>MPC8270     | 37.5 × 37.5     | TBGA | 480           | 1.27          | 1.55                             |

| VR      | MPC8275VR<br>MPC8270VR | 27 × 27         | PBGA | 516           | 1             | 2.25                             |

| ZQ      | MPC8275ZQ<br>MPC8270ZQ | 27 × 27         | PBGA | 516           | 1             | 2.25                             |

| Table 26 | . Package | Parameters |

|----------|-----------|------------|

|----------|-----------|------------|

**Package Description**

## 9.2 Mechanical Dimensions

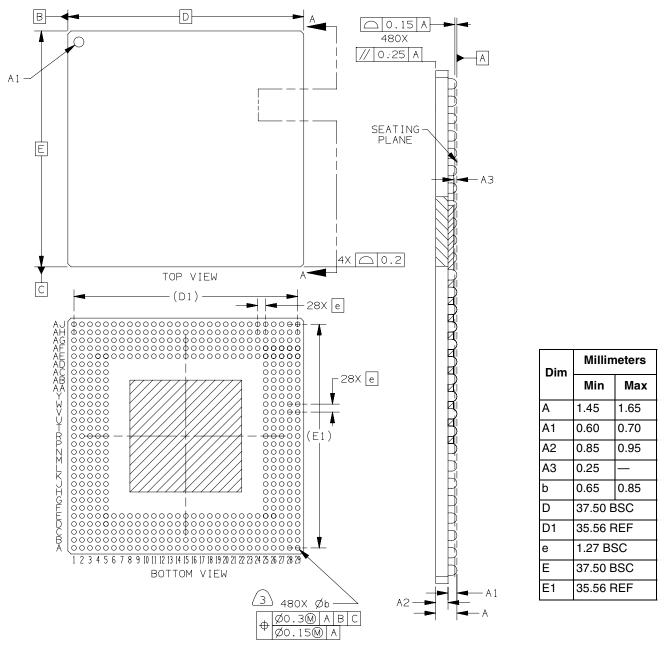

This figure provides the mechanical dimensions and bottom surface nomenclature of the 480 TBGA (ZU/VV) package. See Table 2, "HiP7 PowerQUICC II Device Packages."

#### Notes:

- 1. Dimensions and Tolerancing per ASME Y14.5M-1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is measured at the maximum solder ball diameter, parallel to primary data A.