#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Active                                                                |

| Core Processor                  | PowerPC G2_LE                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 266MHz                                                                |

| Co-Processors/DSP               | Communications; RISC CPM                                              |

| RAM Controllers                 | DRAM, SDRAM                                                           |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100Mbps (3)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 516-BBGA                                                              |

| Supplier Device Package         | 516-PBGA (27x27)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8275vrmiba |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Includes all of the configuration registers (which are automatically loaded from the EPROM and used to configure the MPC8280) required by the PCI standard as well as message and doorbell registers

- Supports the  $I_2O$  standard

- Hot-swap friendly (supports the hot swap specification as defined by PICMG 2.1 R1.0 August 3, 1998)

- Support for 66.67/83.33/100 MHz, 3.3 V specification

- 60x-PCI bus core logic that uses a buffer pool to allocate buffers for each port

- Uses the local bus signals, removing need for additional pins

- System interface unit (SIU)

- Clock synthesizer

- Reset controller

- Real-time clock (RTC) register

- Periodic interrupt timer

- Hardware bus monitor and software watchdog timer

- IEEE 1149.1 JTAG test access port

- 12-bank memory controller

- Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash, and other user-definable peripherals

- Byte write enables and selectable parity generation

- 32-bit address decodes with programmable bank size

- Three user-programmable machines, general-purpose chip-select machine, and page mode pipeline SDRAM machine

- Byte selects for 64-bit bus width (60x) and byte selects for 32-bus width (local)

- Dedicated interface logic for SDRAM

- CPU core can be disabled and the device can be used in slave mode to an external core

- Communications processor module (CPM)

- Embedded 32-bit communications processor (CP) uses a RISC architecture for flexible support for communications protocols

- Interfaces to G2\_LE core through an on-chip 32 KB dual-port data RAM, an on-chip 32 KB dual-port instruction RAM and DMA controller

- Serial DMA channels for receive and transmit on all serial channels

- Parallel I/O registers with open-drain and interrupt capability

- Virtual DMA functionality executing memory-to-memory and memory-to-I/O transfers

- Three fast communications controllers supporting the following protocols:

- 10/100-Mbit Ethernet/IEEE 802.3 CDMA/CS interface through media independent interface (MII) or reduced media independent interface (RMII)

#### **Operating Conditions**

- <sup>2</sup> Caution: VDD/VCCSYN must not exceed VDDH by more than 0.4 V during normal operation. It is recommended that VDD/VCCSYN should be raised before or simultaneous with VDDH during power-on reset. VDD/VCCSYN may exceed VDDH by more than 0.4 V during power-on reset for no more than 100 ms.

- <sup>3</sup> Caution: VDDH can exceed VDD/VCCSYN by 3.3 V during power on reset by no more than 100 mSec. VDDH should not exceed VDD/VCCSYN by more than 2.5 V during normal operation.

- <sup>4</sup> Caution: VIN must not exceed VDDH by more than 2.5 V at any time, including during power-on reset.

This table lists recommended operational voltage conditions.

| Table 4. Recommended | Operating | Conditions <sup>1</sup> |

|----------------------|-----------|-------------------------|

|----------------------|-----------|-------------------------|

| Rating                         | Symbol         | Value              | Unit |

|--------------------------------|----------------|--------------------|------|

| Core supply voltage            | VDD            | 1.45 – 1.60        | V    |

| PLL supply voltage             | VCCSYN         | 1.45 – 1.60        | V    |

| I/O supply voltage             | VDDH           | 3.135 – 3.465      | V    |

| Input voltage                  | VIN            | GND (-0.3) - 3.465 | V    |

| Junction temperature (maximum) | Тј             | 105 <sup>2</sup>   | °C   |

| Ambient temperature            | T <sub>A</sub> | 0-70 <sup>2</sup>  | °C   |

<sup>1</sup> **Caution:** These are the recommended and tested operating conditions. Proper operation outside of these conditions is not guaranteed.

<sup>2</sup> Note that for extended temperature parts the range is  $(-40)_{T_A}$  –  $105_{T_j}$ .

This SoC contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (either GND or  $V_{CC}$ ).

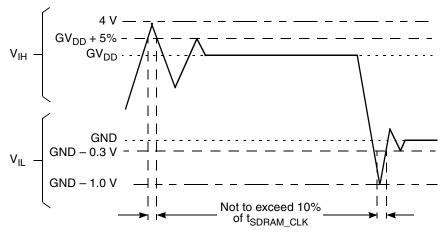

This figure shows the undershoot and overshoot voltage of the 60x and local bus memory interface of the SoC. Note that in PCI mode the I/O interface is different.

Figure 2. Overshoot/Undershoot Voltage

# **3 DC Electrical Characteristics**

This table shows DC electrical characteristics.

| Table 5. DC | Electrical | Characteristics <sup>1</sup> |

|-------------|------------|------------------------------|

|-------------|------------|------------------------------|

| Characteristic                                                                                                                                                                                                       | Symbol           | Min | Max   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage—all inputs except TCK, TRST and PORESET <sup>2</sup>                                                                                                                                              | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage                                                                                                                                                                                                    | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                                                                             | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                                                                              | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>3</sup>                                                                                                                                                           | I <sub>IN</sub>  | _   | 10    | μA   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>3</sup>                                                                                                                                                | I <sub>OZ</sub>  | _   | 10    | μA   |

| Signal low input current, $V_{IL} = 0.8 V^4$                                                                                                                                                                         | ΙL               | _   | 1     | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                                                                                   | Ι <sub>Η</sub>   | _   | 1     | μA   |

| Output high voltage, $I_{OH} = -2 \text{ mA}$<br>except UTOPIA mode, and open drain pins<br>In UTOPIA mode <sup>5</sup> (UTOPIA pins only): $I_{OH} = -8.0\text{mA}$<br>PA[0-31]<br>PB[4-31]<br>PC[0-31]<br>PD[4-31] | V <sub>OH</sub>  | 2.4 | _     | V    |

| In UTOPIA mode <sup>5</sup> (UTOPIA pins only): I <sub>OL</sub> = 8.0mA<br>PA[0-31]<br>PB[4-31]<br>PC[0-31]<br>PD[4-31]                                                                                              | V <sub>OL</sub>  | _   | 0.5   | V    |

# 5 **Power Dissipation**

This table provides preliminary, estimated power dissipation for various configurations. Note that suitable thermal management is required to ensure the junction temperature does not exceed the maximum specified value. Also note that the I/O power should be included when determining whether to use a heat sink. For a complete list of possible clock configurations, see Section 7, "Clock Configuration Modes."

|       | Bus<br>(MHz)CPM<br>Multiplication<br>FactorCPM<br>(MHz)CPU<br>Multiplication<br>FactorCPU<br>(MHz) | ODU     |                | P <sub>INT</sub> (W) <sup>2,3</sup> |      |      |

|-------|----------------------------------------------------------------------------------------------------|---------|----------------|-------------------------------------|------|------|

|       |                                                                                                    |         | Vddl 1.5 Volts |                                     |      |      |

|       |                                                                                                    | Nominal | Maximum        |                                     |      |      |

| 66.67 | 2.5                                                                                                | 166     | 3.5            | 233                                 | 0.95 | 1.0  |

| 66.67 | 2.5                                                                                                | 166     | 4              | 266                                 | 1.0  | 1.05 |

| 66.67 | 3                                                                                                  | 200     | 4              | 266                                 | 1.05 | 1.1  |

| 66.67 | 3.5                                                                                                | 233     | 4.5            | 300                                 | 1.05 | 1.15 |

| 83.33 | 3                                                                                                  | 250     | 4              | 333                                 | 1.25 | 1.35 |

| 83.33 | 3                                                                                                  | 250     | 4.5            | 375                                 | 1.3  | 1.4  |

| 83.33 | 3.5                                                                                                | 292     | 5              | 417                                 | 1.45 | 1.55 |

| 100   | 3                                                                                                  | 300     | 4              | 400                                 | 1.5  | 1.6  |

| 100   | 3                                                                                                  | 300     | 4.5            | 450                                 | 1.55 | 1.65 |

Table 7. Estimated Power Dissipation for Various Configurations<sup>1</sup>

<sup>1</sup> Test temperature =  $105^{\circ}$  C

<sup>2</sup>  $P_{INT} = I_{DD} \times V_{DD}$  Watts

<sup>3</sup> Values do not include I/O. Add the following estimates for active I/O based on the following bus speeds:

66.7 MHz = 0.45 W (nominal), 0.5 W (maximum)

83.3 MHz = 0.5W (nominal), 0.6 W (maximum)

100 MHz = 0.6 W (nominal), 0.7 W (maximum)

## NOTE

Activating data pipelining (setting BRx[DR] in the memory controller) improves the AC timing.

This table lists SIU input characteristics.

| Table 13. AC Characteristics for SIU Inputs <sup>1</sup> |  |

|----------------------------------------------------------|--|

|----------------------------------------------------------|--|

| Spec Number |      |                                                     | Value (ns) |        |         |        |        |         |  |

|-------------|------|-----------------------------------------------------|------------|--------|---------|--------|--------|---------|--|

| Setup       | Hold | Characteristic                                      |            | Setup  |         | Hold   |        |         |  |

|             |      |                                                     | 66 MHz     | 83 MHz | 100 MHz | 66 MHz | 83 MHz | 100 MHz |  |

| sp11        | sp10 | AACK/TA/TS/DBG/BG/BR/ARTRY/<br>TEA                  | 6          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |

| sp12        | sp10 | Data bus in normal mode                             | 5          | 4      | 3.5     | 0.5    | 0.5    | 0.5     |  |

| sp13        | sp10 | Data bus in ECC and PARITY modes                    | 7          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |

| sp13a       | sp10 | Pipeline mode—Data bus (with or without ECC/PARITY) | 5          | 4      | 2.5     | 0.5    | 0.5    | 0.5     |  |

| sp14        | sp10 | DP pins                                             | 7          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |

| sp14a       | sp10 | Pipeline mode—DP pins                               | _          | 4      | 2.5     | _      | 0.5    | 0.5     |  |

| sp15        | sp10 | All other pins                                      | 5          | 4      | 3.5     | 0.5    | 0.5    | 0.5     |  |

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

This table lists SIU output characteristics.

| Table 14. AC Characte | ristics for SIU | Outputs <sup>1</sup> |

|-----------------------|-----------------|----------------------|

|-----------------------|-----------------|----------------------|

| Spec Number |      |                               | Value (ns) |          |         |        |          |         |  |

|-------------|------|-------------------------------|------------|----------|---------|--------|----------|---------|--|

| Max         | Min  | Characteristic                | Ма         | ximum De | lay     | Mi     | nimum De | lay     |  |

|             |      |                               | 66 MHz     | 83 MHz   | 100 MHz | 66 MHz | 83 MHz   | 100 MHz |  |

| sp31        | sp30 | PSDVAL/TEA/TA                 | 7          | 6        | 5.5     | 1      | 1        | 1       |  |

| sp32        | sp30 | ADD/ADD_atr./BADDR/CI/GBL/WT  | 8          | 6.5      | 5.5     | 1      | 1        | 1       |  |

| sp33a       | sp30 | Data bus <sup>2</sup>         | 6.5        | 6.5      | 5.5     | 0.7    | 0.7      | 0.7     |  |

| sp33b       | sp30 | DP                            | 6          | 5.5      | 5.5     | 1      | 1        | 1       |  |

| sp34        | sp30 | Memory controller signals/ALE | 6          | 5.5      | 5.5     | 1      | 1        | 1       |  |

| sp35        | sp30 | All other signals             | 6          | 5.5      | 5.5     | 1      | 1        | 1       |  |

| sp35a       | sp30 | AP                            | 7          | 7        | 7       | 1      | 1        | 1       |  |

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

$^2$  To achieve 1 ns of hold time at 66, 83, or 100 MHz, a minimum loading of 20 pF is required.

#### **Clock Configuration Modes**

- <sup>1</sup> The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not violate the frequency rating of the user's device. The minimum CPM frequency is 120 MHz. Minimum CPU frequency is determined by the clock mode. For modes with a CPU multiplication factor <= 3, the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. For modes with a CPU multiplication factor >= 3.5: for Rev0.1 the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices.

- <sup>2</sup> As Table 17 shows, PCI\_MODCK determines the PCI clock frequency range. See Table 20 for lower configurations.

- <sup>3</sup> MODCK\_H = hard reset configuration word [28–31]. MODCK[1-3] = three hardware configuration pins.

- <sup>4</sup> 60x and local bus frequency. Identical to CLKIN.

- <sup>5</sup> CPM multiplication factor = CPM clock/bus clock

- <sup>6</sup> CPU multiplication factor = Core PLL multiplication factor

| Mode <sup>3</sup>      |                              | Clock <sup>4</sup><br>Hz) | CPM<br>Multiplication | CPM<br>(M | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | PCI<br>Division |      | Clock<br>Hz) |

|------------------------|------------------------------|---------------------------|-----------------------|-----------|--------------|-----------------------|-------|--------------|-----------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low                          | High                      | Factor <sup>5</sup>   | Low       | High         | Factor <sup>6</sup>   | Low   | High         | Factor          | Low  | High         |

|                        | Default Modes (MODCK_H=0000) |                           |                       |           |              |                       |       |              |                 |      |              |

| 0000_000               | 60.0                         | 100.0                     | 2                     | 120.0     | 200.0        | 2.5                   | 150.0 | 250.0        | 4               | 30.0 | 50.0         |

| 0000_001               | 50.0                         | 100.0                     | 2                     | 100.0     | 200.0        | 3                     | 150.0 | 300.0        | 4               | 25.0 | 50.0         |

| 0000_010               | 60.0                         | 120.0                     | 2.5                   | 150.0     | 300.0        | 3                     | 180.0 | 360.0        | 6               | 25.0 | 50.0         |

| 0000_011               | 60.0                         | 120.0                     | 2.5                   | 150.0     | 300.0        | 3.5                   | 210.0 | 420.0        | 6               | 25.0 | 50.0         |

| 0000_100               | 60.0                         | 120.0                     | 2.5                   | 150.0     | 300.0        | 4                     | 240.0 | 480.0        | 6               | 25.0 | 50.0         |

| 0000_101               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 3                     | 150.0 | 300.0        | 6               | 25.0 | 50.0         |

| 0000_110               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 3.5                   | 175.0 | 350.0        | 6               | 25.0 | 50.0         |

| 0000_111               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 4                     | 200.0 | 400.0        | 6               | 25.0 | 50.0         |

|                        |                              |                           |                       | Full Co   | onfigura     | ation Modes           |       |              |                 |      |              |

| 0001_000               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 5                     | 250.0 | 500.0        | 6               | 25.0 | 50.0         |

| 0001_001               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 6                     | 300.0 | 600.0        | 6               | 25.0 | 50.0         |

| 0001_010               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 7                     | 350.0 | 700.0        | 6               | 25.0 | 50.0         |

| 0001_011               | 50.0                         | 100.0                     | 3                     | 150.0     | 300.0        | 8                     | 400.0 | 800.0        | 6               | 25.0 | 50.0         |

|                        |                              |                           |                       |           |              |                       |       |              |                 |      |              |

| 0010_000               | 50.0                         | 100.0                     | 4                     | 200.0     | 400.0        | 5                     | 250.0 | 500.0        | 8               | 25.0 | 50.0         |

| 0010_001               | 50.0                         | 100.0                     | 4                     | 200.0     | 400.0        | 6                     | 300.0 | 600.0        | 8               | 25.0 | 50.0         |

| 0010_010               | 50.0                         | 100.0                     | 4                     | 200.0     | 400.0        | 7                     | 350.0 | 700.0        | 8               | 25.0 | 50.0         |

| 0010_011               | 50.0                         | 100.0                     | 4                     | 200.0     | 400.0        | 8                     | 400.0 | 800.0        | 8               | 25.0 | 50.0         |

|                        |                              |                           | •                     |           |              |                       |       | - I          |                 |      |              |

| 0010_100               | 37.5                         | 75.0                      | 4                     | 150.0     | 300.0        | 5                     | 187.5 | 375.0        | 6               | 25.0 | 50.0         |

| 0010_101               | 37.5                         | 75.0                      | 4                     | 150.0     | 300.0        | 5.5                   | 206.3 | 412.5        | 6               | 25.0 | 50.0         |

#### Table 20. Clock Configurations for PCI Host Mode (PCI\_MODCK=1)<sup>1,2</sup>

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Pin Nar                      | Pall         |      |

|------------------------------|--------------|------|

| MPC8280/MPC8270              | MPC8280 only | Ball |

| D51                          |              | C12  |

| D52                          |              | B10  |

| D53                          |              | A7   |

| D54                          |              | C6   |

| D55                          |              | D5   |

| D56                          |              | B18  |

| D57                          |              | B16  |

| D58                          |              | E14  |

| D59                          |              | D12  |

| D60                          |              | C10  |

| D61                          |              | E8   |

| D62                          |              | D6   |

| D63                          |              | C2   |

| DP0/RSRV/EXT_BR2             |              | B22  |

| IRQ1/DP1/EXT_BG2             |              | A22  |

| IRQ2/DP2/TLBISYNC/EXT_DBG2   |              | E21  |

| IRQ3/DP3/CKSTP_OUT/EXT_BR3   |              | D21  |

| IRQ4/DP4/CORE_SRESET/EXT_BG3 |              | C21  |

| IRQ5/CINT/DP5/TBEN/EXT_DBG3  |              | B21  |

| IRQ6/DP6/CSE0                |              | A21  |

| IRQ7/DP7/CSE1                |              | E20  |

| PSDVAL                       |              | V3   |

| TA                           |              | C22  |

| TEA                          |              | V5   |

| GBL/IRQ1                     |              | W1   |

| CI/BADDR29/IRQ2              |              | U2   |

| WT/BADDR30/IRQ3              |              | U3   |

| L2_HIT/IRQ4                  |              | Y4   |

| CPU_BG/BADDR31/IRQ5/CINT     |              | U4   |

| CPU_DBG                      |              | R2   |

| CPU_BR                       |              | Y3   |

| CSO                          |              | F25  |

| <u>CS1</u>                   |              | C29  |

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Pin Name                     |              |      |

|------------------------------|--------------|------|

| MPC8280/MPC8270              | MPC8280 only | Ball |

| LSDWE/LGPL1/PCI_MODCKH1      |              | C28  |

| LOE/LSDRAS/LGPL2/PCI_MODCKH2 |              | E26  |

| LSDCAS/LGPL3/PCI_MODCKH3     |              | D25  |

| LGTA/LUPMWAIT/LGPL4/LPBS     |              | C26  |

| LGPL5/LSDAMUX/PCI_MODCK      |              | B27  |

| LWR                          |              | D28  |

| L_A14/PAR                    |              | N27  |

| L_A15/FRAME/SMI              |              | T29  |

| L_A16/TRDY                   |              | R27  |

| L_A17/IRDY/CKSTP_OUT         |              | R26  |

| L_A18/STOP                   |              | R29  |

| L_A19/DEVSEL                 |              | R28  |

| L_A20/IDSEL                  |              | W29  |

| L_A21/PERR                   |              | P28  |

| L_A22/SERR                   |              | N26  |

| L_A23/REQ0                   |              | AA27 |

| L_A24/REQ1/HSEJSW            |              | P29  |

| L_A25/GNT0                   |              | AA26 |

| L_A26/GNT1/HSLED             |              | N25  |

| L_A27/GNT2/HSENUM            |              | AA25 |

| L_A28/RST/CORE_SRESET        |              | AB29 |

| L_A29/INTA                   |              | AB28 |

| L_A30/REQ2                   |              | P25  |

| L_A31/DLLOUT                 |              | AB27 |

| LCL_D0/AD0                   |              | H29  |

| LCL_D1/AD1                   |              | J29  |

| LCL_D2/AD2                   |              | J28  |

| LCL_D3/AD3                   |              | J27  |

| LCL_D4/AD4                   |              | J26  |

| LCL_D5/AD5                   |              | J25  |

| LCL_D6/AD6                   |              | K25  |

| LCL_D7/AD7                   |              | L29  |

| LCL_D8/AD8                   |              | L27  |

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Pin Name          |              | D-11 |

|-------------------|--------------|------|

| MPC8280/MPC8270   | MPC8280 only | Ball |

| LCL_D9/AD9        |              | L26  |

| LCL_D10/AD10      |              | L25  |

| LCL_D11/AD11      |              | M29  |

| LCL_D12/AD12      |              | M28  |

| LCL_D13/AD13      |              | M27  |

| LCL_D14/AD14      |              | M26  |

| LCL_D15/AD15      |              | N29  |

| LCL_D16/AD16      |              | T25  |

| LCL_D17/AD17      |              | U27  |

| LCL_D18/AD18      |              | U26  |

| LCL_D19/AD19      |              | U25  |

| LCL_D20/AD20      |              | V29  |

| LCL_D21/AD21      |              | V28  |

| LCL_D22/AD22      |              | V27  |

| LCL_D23/AD23      |              | V26  |

| LCL_D24/AD24      |              | W27  |

| LCL_D25/AD25      |              | W26  |

| LCL_D26/AD26      |              | W25  |

| LCL_D27/AD27      |              | Y29  |

| LCL_D28/AD28      |              | Y28  |

| LCL_D29/AD29      |              | Y25  |

| LCL_D30/AD30      |              | AA29 |

| LCL_D31/AD31      |              | AA28 |

| LCL_DP0/C0/BE0    |              | L28  |

| LCL_DP1/C1/BE1    |              | N28  |

| LCL_DP2/C2/BE2    |              | T28  |

| LCL_DP3/C3/BE3    |              | W28  |

| IRQ0/NMI_OUT      |              | T1   |

| IRQ7/INT_OUT/APE  |              | D1   |

| TRST <sup>1</sup> |              | AH3  |

| тск               |              | AG5  |

| TMS               |              | AJ3  |

| ТОІ               |              | AE6  |

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Pin Name                                                                |                                     | Ball              |

|-------------------------------------------------------------------------|-------------------------------------|-------------------|

| MPC8280/MPC8270                                                         | MPC8280 only                        | Dali              |

| PA17/FCC1_MII_HDLC_RXD0/<br>FCC1_MII_TRAN_RXD/<br>FCCI_RMII_RXD0        | FCC1_UT8_RXD7/<br>FCC1_UT16_RXD15   | AE16 <sup>2</sup> |

| PA18/FCC1_MII_HDLC_TXD0/<br>FCC1_MII_TRAN_TXD/<br>FCC1_RMII_TXD0        | FCC1_UT8_TXD7/FCC1_UT16_TXD15       | AJ16 <sup>2</sup> |

| PA19/FCC1_MII_HDLC_TXD1/<br>FCC1_RMII_TXD1                              | FCC1_UT8_TXD6/FCC1_UT16_TXD14       | AG15 <sup>2</sup> |

| PA20/FCC1_MII_HDLC_TXD2                                                 | FCC1_UT8_TXD5/FCC1_UT16_TXD13       | AJ13 <sup>2</sup> |

| PA21/FCC1_MII_HDLC_TXD3                                                 | FCC1_UT8_TXD4/FCC1_UT16_TXD12       | AE13 <sup>2</sup> |

| PA22                                                                    | FCC1_UT8_TXD3/FCC1_UT16_TXD11       | AF12 <sup>2</sup> |

| PA23                                                                    | FCC1_UT8_TXD2/FCC1_UT16_TXD10       | AG11 <sup>2</sup> |

| PA24/MSNUM1                                                             | FCC1_UT8_TXD1/FCC1_UT16_TXD9        | AH9 <sup>2</sup>  |

| PA25/MSNUM0                                                             | FCC1_UT8_TXD0/FCC1_UT16_TXD8        | AJ8 <sup>2</sup>  |

| PA26/FCC1_RMII_RX_ER                                                    | FCC1_UTM_RXCLAV/<br>FCC1_UTS_RXCLAV | AH7 <sup>2</sup>  |

| PA27/FCC1_MII_RX_DV/<br>FCC1_RMII_CRS_DV                                | FCC1_UT_RXSOC                       | AF7 <sup>2</sup>  |

| PA28/FCC1_MII_TX_EN/<br>FCC1_RMII_TX_EN                                 | FCC1_UTM_RXENB/<br>FCC1_UTS_RXENB   | AD5 <sup>2</sup>  |

| PA29/FCC1_MII_TX_ER                                                     | FCC1_UT_TXSOC                       | AF1 <sup>2</sup>  |

| PA30/FCC1_MII_CRS/FCC1_RTS                                              | FCC1_UTM_TXCLAV/<br>FCC1_UTS_TXCLAV | AD3 <sup>2</sup>  |

| PA31/FCC1_MII_COL                                                       | FCC1_UTM_TXENB/<br>FCC1_UTS_TXENB   | AB5 <sup>2</sup>  |

| PB4/FCC3_MII_HDLC_TXD3/<br>L1RSYNCA2/FCC3_RTS                           | FCC2_UT8_RXD0                       | AD28 <sup>2</sup> |

| PB5/FCC3_MII_HDLC_TXD2/<br>L1TSYNCA2/L1GNTA2                            | FCC2_UT8_RXD1                       | AD26 <sup>2</sup> |

| PB6/FCC3_MII_HDLC_TXD1/<br>FCC3_RMII_TXD1/<br>L1RXDA2/L1RXD0A2          | FCC2_UT8_RXD2                       | AD25 <sup>2</sup> |

| PB7/FCC3_MII_HDLC_TXD0/<br>FCC3_RMII_TXD0/<br>FCC3_TXD/L1TXDA2/L1TXD0A2 | FCC2_UT8_RXD3                       | AE26 <sup>2</sup> |

| PB8/FCC3_MII_HDLC_RXD0/<br>FCC3_RMII_RXD0/<br>FCC3_RXD/TXD3             | FCC2_UT8_TXD3/L1RSYNCD1             | AH27 <sup>2</sup> |

| PB9/FCC3_MII_HDLC_RXD1/<br>FCC3_RMII_RXD1/L1TXD2A2                      | FCC2_UT8_TXD2/L1TSYNCD1/<br>L1GNTD1 | AG24 <sup>2</sup> |

## Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Pin Name                                                                    |                                     | Dell              |

|-----------------------------------------------------------------------------|-------------------------------------|-------------------|

| MPC8280/MPC8270                                                             | MPC8280 only                        | Ball              |

| PB10/FCC3_MII_HDLC_RXD2                                                     | FCC2_UT8_TXD1/L1RXDD1               | AH24 <sup>2</sup> |

| PB11/FCC3_MII_HDLC_RXD3                                                     | FCC2_UT8_TXD0/L1TXDD1               | AJ24 <sup>2</sup> |

| PB12/FCC3_MII_CRS/TXD2                                                      | L1CLKOB1/L1RSYNCC1                  | AG22 <sup>2</sup> |

| PB13/FCC3_MII_COL/L1TXD1A2                                                  | L1RQB1/L1TSYNCC1/L1GNTC1            | AH21 <sup>2</sup> |

| PB14/FCC3_MII_RMII_TX_EN//RXD3                                              | L1RXDC1                             | AG20 <sup>2</sup> |

| PB15/FCC3_MII_TX_ER/RXD2                                                    | L1TXDC1                             | AF19 <sup>2</sup> |

| PB16/FCC3_MII_RMII_RX_ER/CLK18                                              | L1CLKOA1                            | AJ18 <sup>2</sup> |

| PB17/FCC3_MII_RX_DV/CLK17/<br>FCC3_RMII_CRS_DV                              | L1RQA1                              | AJ17 <sup>2</sup> |

| PB18/FCC2_MII_HDLC_RXD3/<br>L1CLKOD2/L1RXD2A2                               | FCC2_UT8_RXD4                       | AE14 <sup>2</sup> |

| PB19FCC2_MII_HDLC_RXD2/<br>L1RQD2/L1RXD3A2                                  | FCC2_UT8_RXD5                       | AF13 <sup>2</sup> |

| PB20/FCC2_MII_HDLC_RMII_RXD1/<br>L1RSYNCD2                                  | FCC2_UT8_RXD6/L1TXD1A1              | AG12 <sup>2</sup> |

| PB21//FCC2_MII_HDLC_RMII_RXD0/<br>FCC2_TRAN_RXD/L1TSYNCD2/<br>L1GNTD2       | FCC2_UT8_RXD7/L1TXD2A1              | AH11 <sup>2</sup> |

| PB22/FCC2_MII_HDLC_TXD0/<br>FCC2_TXD/FCC2_RMII_TXD0/<br>L1RXDD2             | FCC2_UT8_TXD7/L1RXD1A1              | AH16 <sup>2</sup> |

| PB23/FCC2_MII_HDLC_TXD1/<br>L1RXD2A1/L1TXDD2/<br>FCC2_RMII_TXD1             | FCC2_UT8_TXD6/L1RXD2A1              | AE15 <sup>2</sup> |

| PB24/FCC2_MII_HDLC_TXD2/<br>L1RSYNCC2                                       | FCC2_UT8_TXD5/L1RXD3A1              | AJ9 <sup>2</sup>  |

| PB25/FCC2_MII_HDLC_TXD3/<br>L1TSYNCC2/L1GNTC2                               | FCC2_UT8_TXD4/L1TXD3A1              | AE9 <sup>2</sup>  |

| PB26/FCC2_MII_CRS/L1RXDC2                                                   | FCC2_UT8_TXD1                       | AJ7 <sup>2</sup>  |

| PB27/FCC2_MII_COL/L1TXDC2                                                   | FCC2_UT8_TXD0                       | AH6 <sup>2</sup>  |

| PB28/FCC2_MII_RX_ER/<br>FCC2_RMII_RX_ER/FCC2_RTS/<br>L1TSYNCB2/L1GNTB2/TXD1 |                                     | AE3 <sup>2</sup>  |

| PB29/L1RSYNCB2/FCC2_MII_TX_EN/<br>FCC2_RMII_TX_EN                           | FCC2_UTM_RXCLAV/<br>FCC2_UTS_RXCLAV | AE2 <sup>2</sup>  |

| PB30/FCC2_MII_RX_DV/<br>FCC2_RMII_CRS_DV/L1RXDB2                            | FCC2_UT_TXSOC                       | AC5 <sup>2</sup>  |

| PB31/FCC2_MII_TX_ER/L1TXDB2                                                 | FCC2_UT_RXSOC                       | AC4 <sup>2</sup>  |

#### Table 23. MPC8280 and MPC8270 (ZU and VV Packages) Pinout List (continued)

| Pin Name        |              | Ball                                                                                                                                                                                                                                                             |

|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPC8280/MPC8270 | MPC8280 only | Dan                                                                                                                                                                                                                                                              |

| Core power      |              | U28, U29, K28, K29, A9, A19, B19,<br>M1, M2, Y1, Y2, AC1, AC2, AH19,<br>AJ19, AH10, AJ10, AJ5                                                                                                                                                                    |

| Ground          |              | AA5, AB1 <sup>6</sup> , AB2 <sup>7</sup> , AF21, AF14, AF8,<br>AE7, AF11, AE17, AE23, AC26,<br>AB25, Y26, V25, T26, R25, P26,<br>M25, K27, H25, G26, D7, D10, D14,<br>D16, D20, D23, C9, E11, E13, E15,<br>E19, E22, B3, G5, H4, K5, M3, P5,<br>T4, Y5, AA2, AC3 |

<sup>1</sup> Should be tied to VDDH via a 2K  $\Omega$  external pull-up resistor.

- <sup>2</sup> The default configuration of the CPM pins (PA[0–31], PB[4–31], PC[0–31], PD[4–31]) is input. To prevent excessive DC current, it is recommended to either pull unused pins to GND or VDDH, or to configure them as outputs.

- <sup>3</sup> Must be pulled down or left floating.

- <sup>4</sup> If PCI is not desired, must be pulled up or left floating.

- <sup>5</sup> Sphere is not connected to die.

- <sup>6</sup> GNDSYN (AB1): This pin exists as a separate ground signal in MPC826x(A) devices; it does not exist as a separate ground signal on the SoC. New designs must connect AB1 to GND and follow the suggestions in Section 4.6, "Layout Practices." Old designs in which the MPC8280 is used as a drop-in replacement can leave the pin connected to GND with the noise filtering capacitors.

- <sup>7</sup> XFC (AB2) pin: This pin is used in MPC826x(A) devices; it is not used in MPC8280 because there is no need for external capacitor to operate the PLL. New designs should connect AB2 (XFC) pin to GND. Old designs in which the SoC is used as a drop-in replacement can leave the pin connected to the current capacitor.

This table describes symbols used in Table 23.

#### Table 24. Symbol Legend

| Symbol  | Meaning                                                                     |

|---------|-----------------------------------------------------------------------------|

| OVERBAR | Signals with overbars, such as TA, are active low.                          |

| UTM     | Indicates that a signal is part of the UTOPIA master interface.             |

| UTS     | Indicates that a signal is part of the UTOPIA slave interface.              |

| UT8     | Indicates that a signal is part of the 8-bit UTOPIA interface.              |

| UT16    | Indicates that a signal is part of the 16-bit UTOPIA interface.             |

| MII     | Indicates that a signal is part of the media independent interface.         |

| RMII    | Indicates that a signal is part of the reduced media independent interface. |

## 8.2 VR and ZQ Packages—MPC8275 and MPC8270

The following figures and table represent the alternate 516 PBGA package. For information on the standard package for the MPC8280 and the MPC8270, see Section 8.1, "ZU and VV Packages—MPC8280 and MPC8270.

| Pin Name        |              | Dall |

|-----------------|--------------|------|

| MPC8275/MPC8270 | MPC8275 only | Ball |

| A0              |              | D5   |

| A1              |              | E8   |

| A2              |              | C4   |

| A3              |              | B4   |

| A4              |              | A4   |

| A5              |              | D7   |

| A6              |              | D8   |

| A7              |              | C6   |

| A8              |              | B5   |

| A9              |              | B6   |

| A10             |              | C7   |

| A11             |              | C8   |

| A12             |              | A6   |

| A13             |              | D9   |

| A14             |              | F11  |

| A15             |              | B7   |

| A16             |              | B8   |

| A17             |              | C9   |

| A18             |              | A7   |

| A19             |              | B9   |

| A20             |              | E11  |

| A21             |              | A8   |

| A22             |              | D11  |

| A23             |              | B10  |

| A24             |              | C11  |

| A25             |              | A9   |

| A26             |              | B11  |

| A27             |              | C12  |

| A28             |              | D12  |

| A29             |              | A10  |

| A30             |              | B12  |

| A31             |              | B13  |

| ТТО             |              | E7   |

## Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Name        |              | Poll |

|-----------------|--------------|------|

| MPC8275/MPC8270 | MPC8275 only | Ball |

| TT1             |              | B3   |

| TT2             |              | F8   |

| ТТ3             |              | A3   |

| TT4             |              | C3   |

| TBST            |              | F5   |

| TSIZ0           |              | E3   |

| TSIZ1           |              | E2   |

| TSIZ2           |              | E1   |

| TSIZ3           |              | E4   |

| AACK            |              | D3   |

| ARTRY           |              | C2   |

| DBG             |              | A14  |

| DBB/IRQ3        |              | C15  |

| D0              |              | W4   |

| D1              |              | Y1   |

| D2              |              | V1   |

| D3              |              | P4   |

| D4              |              | N3   |

| D5              |              | K5   |

| D6              |              | J4   |

| D7              |              | G1   |

| D8              |              | AB1  |

| D9              |              | U4   |

| D10             |              | U2   |

| D11             |              | N6   |

| D12             |              | N1   |

| D13             |              | L1   |

| D14             |              | J5   |

| D15             |              | G3   |

| D16             |              | AA2  |

| D17             |              | W1   |

| D18             |              | Т3   |

| D19             |              | T1   |

## Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

## Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Name                     |              | 5.4  |

|------------------------------|--------------|------|

| MPC8275/MPC8270              | MPC8275 only | Ball |

| D53                          |              | J2   |

| D54                          |              | H5   |

| D55                          |              | F3   |

| D56                          |              | V3   |

| D57                          |              | R5   |

| D58                          |              | R2   |

| D59                          |              | N5   |

| D60                          |              | L2   |

| D61                          |              | J3   |

| D62                          |              | H1   |

| D63                          |              | F4   |

| DP0/RSRV/EXT_BR2             |              | AB3  |

| IRQ1/DP1/EXT_BG2             |              | W5   |

| IRQ2/DP2/TLBISYNC/EXT_DBG2   |              | AC2  |

| IRQ3/DP3/CKSTP_OUT/EXT_BR3   |              | AA3  |

| IRQ4/DP4/CORE_SRESET/EXT_BG3 |              | AD1  |

| IRQ5/CINT/DP5/TBEN/EXT_DBG3  |              | AC1  |

| IRQ6/DP6/CSE0                |              | AB2  |

| IRQ7/DP7/CSE1                |              | Y3   |

| PSDVAL                       |              | D15  |

| TA                           |              | Y4   |

| TEA                          |              | D16  |

| GBL/IRQ1                     |              | E15  |

| CI/BADDR29/IRQ2              |              | D14  |

| WT/BADDR30/IRQ3              |              | E14  |

| L2_HIT/IRQ4                  |              | A17  |

| CPU_BG/BADDR31/IRQ5/CINT     |              | B14  |

| CPU_DBG                      |              | F13  |

| CPU_BR                       |              | B17  |

| CSO                          |              | AC6  |

| <u>CS1</u>                   |              | AD6  |

| CS2                          |              | AE6  |

| CS3                          |              | AB7  |

## Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Name                     |              | Dell |

|------------------------------|--------------|------|

| MPC8275/MPC8270              | MPC8275 only | Ball |

| CS4                          |              | AF7  |

| CS5                          |              | AC7  |

| <u>CS6</u>                   |              | AD7  |

| CS7                          |              | AF8  |

| CS8                          |              | AE8  |

| CS9                          |              | AD8  |

| CS10/BCTL1                   |              | AC8  |

| CS11/AP0                     |              | AB8  |

| BADDR27                      |              | C13  |

| BADDR28                      |              | A12  |

| ALE                          |              | D13  |

| BCTLO                        |              | AF4  |

| PWE0/PSDDQM0/PBS0            |              | AA5  |

| PWE1/PSDDQM1/PBS1            |              | AE4  |

| PWE2/PSDDQM2/PBS2            |              | AD4  |

| PWE3/PSDDQM3/PBS3            |              | AF3  |

| PWE4/PSDDQM4/PBS4            |              | AB4  |

| PWE5/PSDDQM5/PBS5            |              | AE3  |

| PWE6/PSDDQM6/PBS6            |              | AF2  |

| PWE7/PSDDQM7/PBS7            |              | AD3  |

| PSDA10/PGPL0                 |              | AE2  |

| PSDWE/PGPL1                  |              | AD2  |

| POE/PSDRAS/PGPL2             |              | AE1  |

| PSDCAS/PGPL3                 |              | AC3  |

| PGTA/PUPMWAIT/PGPL4/PPBS     |              | W6   |

| PSDAMUX/PGPL5                |              | AA4  |

| LWE0/LSDDQM0/LBS0/PCI_CFG0   |              | AC9  |

| LWE1/LSDDQM1/LBS1/PCI_CFG1   |              | AD9  |

| LWE2/LSDDQM2/LBS2/PCI_CFG2   |              | AE9  |

| LWE3/LSDDQM3/LBS3/PCI_CFG3   |              | AF9  |

| LSDA10/LGPL0/PCI_MODCKH0     |              | AB6  |

| LSDWE/LGPL1/PCI_MODCKH1      |              | AF5  |

| LOE/LSDRAS/LGPL2/PCI_MODCKH2 |              | AE5  |

## Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Name                  |              | D-II |  |

|---------------------------|--------------|------|--|

| MPC8275/MPC8270           | MPC8275 only | Ball |  |

| LENDCAS/LGPL3/PCI_MODCKH3 |              | AD5  |  |

| LGTA/LUPMWAIT/LGPL4/LPBS  |              | AC5  |  |

| LGPL5/LSDAMUX/PCI_MODCK   |              | AB5  |  |

| LWR                       |              | AF6  |  |

| L_A14/PAR                 |              | AE13 |  |

| L_A15/FRAME/SMI           |              | AD15 |  |

| L_A16/TRDY                |              | AF16 |  |

| L_A17/IRDY/CKSTP_OUT      |              | AF15 |  |

| L_A18/STOP                |              | AE15 |  |

| L_A19/DEVSEL              |              | AE14 |  |

| L_A20/IDSEL               |              | AC17 |  |

| L_A21/PERR                |              | AD14 |  |

| L_A22/SERR                |              | AF13 |  |

| L_A23/REQ0                |              | AE20 |  |

| L_A24/REQ1/HSEJSW         |              | AC14 |  |

| L_A25/GNT0                |              | AC19 |  |

| L_A26/GNT1/HSLED          |              | AD13 |  |

| L_A27/GNT2/HSENUM         |              | AF21 |  |

| L_A28/RST/CORE_SRESET     |              | AF22 |  |

| L_A29/INTA                |              | AE21 |  |

| L_A30/REQ2                |              | AB14 |  |

| L_A31/DLLOUT              |              | AD20 |  |

| LCL_D0/AD0                |              | AB9  |  |

| LCL_D1/AD1                |              | AB10 |  |

| LCL_D2/AD2                |              | AC10 |  |

| LCL_D3/AD3                |              | AD10 |  |

| LCL_D4/AD4                |              | AE10 |  |

| LCL_D5/AD5                |              | AF10 |  |

| LCL_D6/AD6                |              | AF11 |  |

| LCL_D7/AD7                |              | AB12 |  |

| LCL_D8/AD8                |              | AB11 |  |

| LCL_D9/AD9                |              | AF12 |  |

| LCL_D10/AD10              |              | AE11 |  |

- <sup>3</sup> Must be pulled down or left floating.

- <sup>4</sup> If PCI is not desired, must be pulled up or left floating.

- <sup>5</sup> Sphere is not connected to die.

- <sup>6</sup> GNDSYN (B18): This pin exists as a separate ground signal in MPC826x(A) devices; it does not exist as a separate ground signal on the MPC8275/MPC8270. New designs must connect B18 to GND and follow the suggestions in Section 4.6, "Layout Practices." Old designs in which the MPC8275/MPC8270 is used as a drop-in replacement can leave the pin connected to GND with the noise filtering capacitors.

- <sup>7</sup> XFC (A18) pin: This pin is used in MPC826x(A) devices; it is not used in MPC8275/MPC8270 because there is no need for external capacitor to operate the PLL. New designs should connect A18 (XFC) pin to GND. Old designs in which the MPC8275/MPC8270 is used as a drop-in replacement can leave the pin connected to the current capacitor.

## 9 Package Description

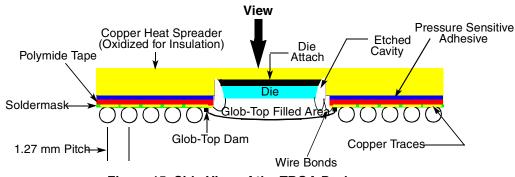

This figure shows the side profile of the TBGA package to indicate the direction of the top surface view.

Figure 15. Side View of the TBGA Package

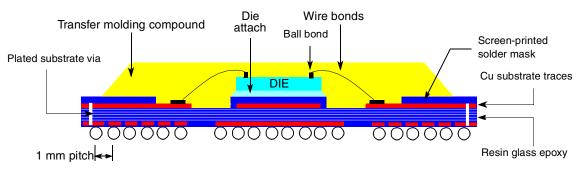

This figure shows the side profile of the PBGA package to indicate the direction of the top surface view.

Figure 16. Side View of the PBGA Package Remove

**Package Description**

## 9.2 Mechanical Dimensions

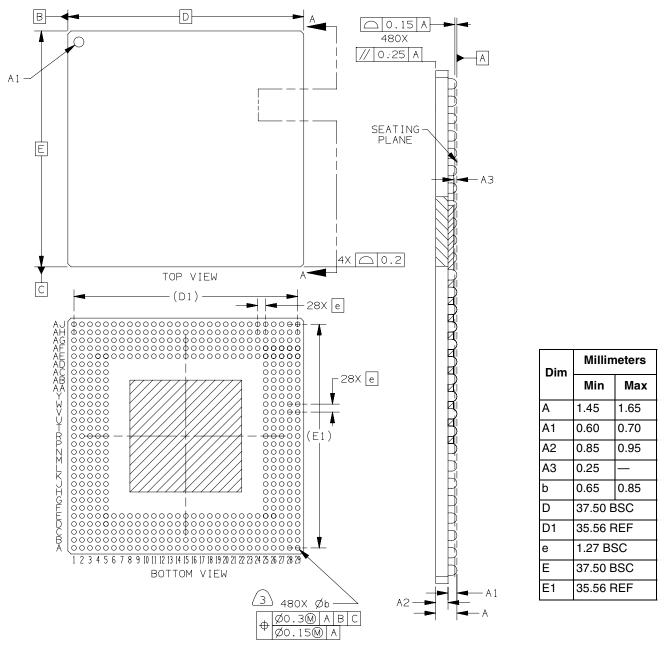

This figure provides the mechanical dimensions and bottom surface nomenclature of the 480 TBGA (ZU/VV) package. See Table 2, "HiP7 PowerQUICC II Device Packages."

#### Notes:

- 1. Dimensions and Tolerancing per ASME Y14.5M-1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is measured at the maximum solder ball diameter, parallel to primary data A.

- 4. Primary data A and the seating plane are defined by the spherical crowns of the solder balls.

### Figure 17. Mechanical Dimensions and Bottom Surface Nomenclature—480 TBGA

**Document Revision History**

| Revision | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.3      | 6/2003  | <ul> <li>Removal of notes stating "no local bus" on VR-package devices. The MPC8270VR and the MPC8275VR have local bus support.</li> <li>References to "G2 core" changed to "G2_LE core." See the <i>G2 Core Reference Manual</i> (G2CORERM/D).</li> <li>Addition of VCCSYN to "Note" below Table 4, and to note 3 of Table 5</li> <li>Figure 2: New</li> <li>Table 5: Addition of note 1</li> <li>Table 10: Addition of various configurations, Modification of values. Addition of note 3.</li> <li>Table 12: Addition of 66 MHZ and 100 MHz values. Addition of sp42a/sp43a.</li> <li>Table 20: Addition of 66 MHZ and 100 MHz values</li> <li>Table 12: sp30 values. sp33b @ 100 MHz value. Removal of previous note 2. Modification of current note 2.</li> <li>Figure 5, Figure 6, Figure 7, and Figure 8: Addition of note 1 concerning minimum operating frequencies</li> <li>Addition of statement before clock tables about selection of clock configuration and input frequency</li> <li>Table 23 and Table 25: Addition of note 1 to CPM pins</li> </ul> |

| 0.2      | 11/2002 | Table 25, "VR Pinout": Addition of C18 to the Ground (GND) pin list (page 63)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0.1      | —       | Initial public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |