# E·XFL

### NXP USA Inc. - MPC8280ZUUPEA Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC G2_LE                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 450MHz                                                                |

| Co-Processors/DSP               | Communications; RISC CPM                                              |

| RAM Controllers                 | DRAM, SDRAM                                                           |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | ·                                                                     |

| Ethernet                        | 10/100Mbps (3)                                                        |

| SATA                            | · .                                                                   |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | · .                                                                   |

| Package / Case                  | 480-LBGA Exposed Pad                                                  |

| Supplier Device Package         | 480-TBGA (37.5x37.5)                                                  |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8280zuupea |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Provides management for BRI devices as general-circuit interface (GCI) controllers in time-division-multiplexed (TDM) channels

- Transparent

- UART (low-speed operation)

- One serial peripheral interface identical to the MPC860 SPI

- One  $I^2C$  controller (identical to the MPC860  $I^2C$  controller)

- Microwire compatible

- Multiple-master, single-master, and slave modes

- Up to eight TDM interfaces (four on the MPC8270)

- Supports two groups of four TDM channels for a total of eight TDMs (one group of four on the MPC8270 and the MPC8275)

- 2,048 bytes of SI RAM

- Bit or byte resolution

- Independent transmit and receive routing, frame synchronization

- Supports T1, CEPT, T1/E1, T3/E3, pulse code modulation highway, ISDN basic rate, ISDN primary rate, Freescale interchip digital link (IDL), general circuit interface (GCI), and user-defined TDM serial interfaces

- Eight independent baud rate generators and 20 input clock pins for supplying clocks to FCCs, SCCs, SMCs, and serial channels

- Four independent 16-bit timers that can be interconnected as two 32-bit timers

- Inverse multiplexing for ATM capabilities (IMA) (MPC8280 only). Supported by eight transfer transmission convergence (TC) layers between the TDMs and FCC2.

- Transmission convergence (TC) layer (MPC8280 only)

# 2 **Operating Conditions**

This table shows the maximum electrical ratings.

### Table 3. Absolute Maximum Ratings<sup>1</sup>

| Rating                           | Symbol           | Value           | Unit |

|----------------------------------|------------------|-----------------|------|

| Core supply voltage <sup>2</sup> | VDD              | -0.3 - 2.25     | V    |

| PLL supply voltage <sup>2</sup>  | VCCSYN           | -0.3 - 2.25     | V    |

| I/O supply voltage <sup>3</sup>  | VDDH             | -0.3 - 4.0      | V    |

| Input voltage <sup>4</sup>       | VIN              | GND(-0.3) - 3.6 | V    |

| Junction temperature             | Тј               | 120             | °C   |

| Storage temperature range        | T <sub>STG</sub> | (–55) – (+150)  | °C   |

<sup>1</sup> Absolute maximum ratings are stress ratings only; functional operation (see Table 4) at the maximums is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage.

Thermal Characteristics

### 4.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application, or a more accurate and complex model of the package can be used in the thermal simulation.

### 4.5 **Experimental Determination**

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$\Psi_{JT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the case to avoid measurement errors caused by cooling effects of the thermocouple wire.

### 4.6 Layout Practices

Each VDD and VDDH pin should be provided with a low-impedance path to the board's power supplies. Each ground pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The VDD and VDDH power supplies should be bypassed to ground using bypass capacitors located as close as possible to the four sides of the package. For filtering high frequency noise, a capacitor of 0.1uF on each VDD and VDDH pin is recommended. Further, for medium frequency noise, a total of 2 capacitors of 47uF for VDD and 2 capacitors of 47uF for VDDH are also recommended. The capacitor leads and associated printed circuit traces connecting to chip VDD, VDDH and ground should be kept to less than half an inch per capacitor lead. Boards should employ separate inner layers for power and GND planes.

All output pins on the SoC have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized to minimize overdamped conditions and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the VDD and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

**AC Electrical Characteristics**

#### **AC Electrical Characteristics** 6

The following sections include illustrations and tables of clock diagrams, signals, and CPM outputs and inputs for 66.67/83.33/100 MHz devices. Note that AC timings are based on a 50-pf load for MAX Delay and 10-pf load for MIN delay. Typical output buffer impedances are shown in this table.

| Output Buffers    | Typical Impedance ( $\Omega$ ) |  |  |  |  |  |  |

|-------------------|--------------------------------|--|--|--|--|--|--|

| 60x bus           | 45 or 27 <sup>2</sup>          |  |  |  |  |  |  |

| Local bus         | 45                             |  |  |  |  |  |  |

| Memory controller | 45 or 27 <sup>2</sup>          |  |  |  |  |  |  |

| Parallel I/O      | 45                             |  |  |  |  |  |  |

| PCI               | 27                             |  |  |  |  |  |  |

| Table 8. | Output | Buffer | Impedances <sup>1</sup> |

|----------|--------|--------|-------------------------|

|----------|--------|--------|-------------------------|

1 These are typical values at 65° C. Impedance may vary by ±25% with process and temperature.

2 On silicon revision 0.0 (mask #: 0K49M), selectable impedance is not available. Impedance is set at 45  $\Omega$ .

On all other revisions, impedance value is selected through the SIUMCR[20,21]. See the SoC reference manual.

#### 6.1 **CPM AC Characteristics**

FCC outputs-external clock (NMSI)

SCC/SMC/SPI/I2C outputs-internal

SCC/SMC/SPI/I2C outputs-external

This table lists CPM output characteristics.

clock (NMSI)

clock (NMSI)

**PIO** outputs

TDM outputs/SI

TIMER/IDMA outputs

| Spec N | lumber | Characteristic                    |        |                             | Value   | e (ns) |        |    |

|--------|--------|-----------------------------------|--------|-----------------------------|---------|--------|--------|----|

| Max    | Min    |                                   | Ма     | Maximum Delay Minimum Delay |         |        | ay     |    |

|        |        |                                   | 66 MHz | 83 MHz                      | 100 MHz | 66 MHz | 83 MHz | 10 |

| sp36a  | sp37a  | FCC outputs—internal clock (NMSI) | 6      | 5.5                         | 5.5     | 0.5    | 0.5    |    |

8

10

8

11

11

11

8

10

8

11

11

11

8

10

8

11

11

11

2

0

2

2.5

0.5

0.5

2

0

2

2.5

0.5

0.5

Table 9. AC Characteristics for CPM Outputs<sup>1</sup>

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

100 MHz

0.5

2

0

2

2.5

0.5

0.5

sp36b

sp38a

sp38b

sp40

sp42

sp42a

sp37b

sp39a

sp39b

sp41

sp43

sp43a

### NOTE

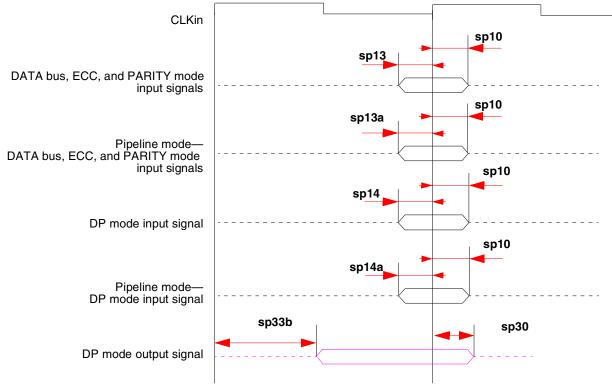

Activating data pipelining (setting BRx[DR] in the memory controller) improves the AC timing.

This table lists SIU input characteristics.

| Table 13. AC Characteristics for SIU Inputs <sup>1</sup> |  |

|----------------------------------------------------------|--|

|----------------------------------------------------------|--|

| Spec Number |      |                                                     | Value (ns) |        |         |        |        |         |  |  |

|-------------|------|-----------------------------------------------------|------------|--------|---------|--------|--------|---------|--|--|

| Setup       | Hold | Characteristic                                      |            | Setup  |         |        | Hold   | old     |  |  |

|             |      |                                                     | 66 MHz     | 83 MHz | 100 MHz | 66 MHz | 83 MHz | 100 MHz |  |  |

| sp11        | sp10 | AACK/TA/TS/DBG/BG/BR/ARTRY/<br>TEA                  | 6          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |

| sp12        | sp10 | Data bus in normal mode                             | 5          | 4      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |

| sp13        | sp10 | Data bus in ECC and PARITY modes                    | 7          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |

| sp13a       | sp10 | Pipeline mode—Data bus (with or without ECC/PARITY) | 5          | 4      | 2.5     | 0.5    | 0.5    | 0.5     |  |  |

| sp14        | sp10 | DP pins                                             | 7          | 5      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |

| sp14a       | sp10 | Pipeline mode—DP pins                               | _          | 4      | 2.5     | _      | 0.5    | 0.5     |  |  |

| sp15        | sp10 | All other pins                                      | 5          | 4      | 3.5     | 0.5    | 0.5    | 0.5     |  |  |

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

This table lists SIU output characteristics.

| Table 14. AC Characte | ristics for SIU | Outputs <sup>1</sup> |

|-----------------------|-----------------|----------------------|

|-----------------------|-----------------|----------------------|

| Spec Number |      |                               | Value (ns) |          |         |               |        |         |  |  |

|-------------|------|-------------------------------|------------|----------|---------|---------------|--------|---------|--|--|

| Max         | Min  | Characteristic                | Ма         | ximum De | lay     | Minimum Delay |        |         |  |  |

|             |      |                               | 66 MHz     | 83 MHz   | 100 MHz | 66 MHz        | 83 MHz | 100 MHz |  |  |

| sp31        | sp30 | PSDVAL/TEA/TA                 | 7          | 6        | 5.5     | 1             | 1      | 1       |  |  |

| sp32        | sp30 | ADD/ADD_atr./BADDR/CI/GBL/WT  | 8          | 6.5      | 5.5     | 1             | 1      | 1       |  |  |

| sp33a       | sp30 | Data bus <sup>2</sup>         | 6.5        | 6.5      | 5.5     | 0.7           | 0.7    | 0.7     |  |  |

| sp33b       | sp30 | DP                            | 6          | 5.5      | 5.5     | 1             | 1      | 1       |  |  |

| sp34        | sp30 | Memory controller signals/ALE | 6          | 5.5      | 5.5     | 1             | 1      | 1       |  |  |

| sp35        | sp30 | All other signals             | 6          | 5.5      | 5.5     | 1             | 1      | 1       |  |  |

| sp35a       | sp30 | AP                            | 7          | 7        | 7       | 1             | 1      | 1       |  |  |

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

$^2$  To achieve 1 ns of hold time at 66, 83, or 100 MHz, a minimum loading of 20 pF is required.

#### **AC Electrical Characteristics**

This figure shows signal behavior for all parity modes (including ECC, RMW parity, and standard parity).

Figure 10. Parity Mode Diagram

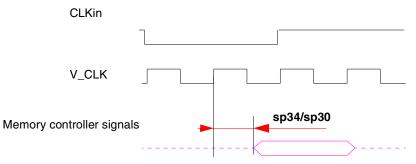

This figure shows signal behavior in MEMC mode.

### NOTE

Generally, all SoC bus and system output signals are driven from the rising edge of the input clock (CLKin). Memory controller signals, however, trigger on four points within a CLKin cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and T3 at the falling edge, of CLKin. However, the spacing of T2 and T4 depends on the PLL clock ratio selected, as shown in Table 15.

|          | Pins       |                        | PCI Clock<br>Frequency Range | Reference |            |

|----------|------------|------------------------|------------------------------|-----------|------------|

| PCI_MODE | PCI_CFG[0] | PCI_MODCK <sup>1</sup> | Clocking Mode                | (MHZ)     | helefelide |

| 1        |            | _                      | Local bus                    | —         | Table 18   |

| 0        | 0          | 0                      | PCI host                     | 50–66     | Table 19   |

| 0        | 0          | 1                      |                              | 25–50     | Table 20   |

| 0        | 1          | 0                      | PCI agent                    | 50–66     | Table 21   |

| 0        | 1          | 1                      |                              | 25–50     | Table 22   |

Table 17. SoC Clocking Modes

<sup>1</sup> Determines PCI clock frequency range. See Section 7.2, "PCI Host Mode," and Section 7.3, "PCI Agent Mode."

Within each mode, the configuration of bus, core, PCI, and CPM frequencies is determined by seven bits during the power-on reset—three hardware configuration pins (MODCK[1–3]) and four bits from hardware configuration word[28–31] (MODCK\_H). Both the PLLs and the dividers are set according to the selected clock operation mode as described in the following sections.

### 7.1 Local Bus Mode

This table lists clock configurations for the SoC in local bus mode. The frequencies listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device.

### NOTE

Clock configurations change only after PORESET is asserted.

| Mode <sup>2</sup>             |      | Clock <sup>3</sup><br>IHz) | CPM CPM Clock (MHz) |          |       | CPU<br>Multiplication | CPU Clock<br>(MHz) |       |  |  |  |

|-------------------------------|------|----------------------------|---------------------|----------|-------|-----------------------|--------------------|-------|--|--|--|

| MODCK_H-MODCK[1:3]            | Low  | High                       | Factor <sup>4</sup> | Low      | High  | Factor <sup>5</sup>   | Low                | High  |  |  |  |

| Default Modes (MODCK_H= 0000) |      |                            |                     |          |       |                       |                    |       |  |  |  |

| 0000_000                      | 37.5 | 133.3                      | 3                   | 112.5    | 400.0 | 4                     | 150.0              | 533.3 |  |  |  |

| 0000_001                      | 33.3 | 133.3                      | 3                   | 100.0    | 400.0 | 5                     | 166.7              | 666.7 |  |  |  |

| 0000_010                      | 37.5 | 100.0                      | 4                   | 150.0    | 400.0 | 4                     | 150.0              | 400.0 |  |  |  |

| 0000_011                      | 30.0 | 100.0                      | 4                   | 120.0    | 400.0 | 5                     | 150.0              | 500.0 |  |  |  |

| 0000_100                      | 60.0 | 167.0                      | 2                   | 120.0    | 334.0 | 2.5                   | 150.0              | 417.5 |  |  |  |

| 0000_101                      | 50.0 | 167.0                      | 2                   | 100.0    | 334.0 | 3                     | 150.0              | 501.0 |  |  |  |

| 0000_110                      | 60.0 | 160.0                      | 2.5                 | 150.0    | 400.0 | 2.5                   | 150.0              | 400.0 |  |  |  |

| 0000_111                      | 50.0 | 160.0                      | 2.5                 | 125.0    | 400.0 | 3                     | 150.0              | 480.0 |  |  |  |

|                               | •    |                            | Full Configurat     | ion Mode | S     |                       |                    |       |  |  |  |

| 0001_000                      | 50.0 | 167.0                      | 2                   | 100.0    | 334.0 | 4                     | 200.0              | 668.0 |  |  |  |

Table 18. Clock Configurations for Local Bus Mode<sup>1</sup>

**Clock Configuration Modes**

### Table 19. Clock Configurations for PCI Host Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>      | Bus Clock <sup>4</sup><br>(MHz) |       | СРМ                                   |       | Clock<br>Hz) | CPU                                     |       | Clock<br>Hz) | PCI                |      | Clock<br>Hz) |

|------------------------|---------------------------------|-------|---------------------------------------|-------|--------------|-----------------------------------------|-------|--------------|--------------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low                             | High  | Multiplication<br>Factor <sup>5</sup> | Low   | High         | - Multiplication<br>Factor <sup>6</sup> | Low   | High         | Division<br>Factor | Low  | High         |

| 0110_011               | 60.0                            | 80.0  | 2.5                                   | 150.0 | 200.0        | 4                                       | 240.0 | 320.0        | 3                  | 50.0 | 66.7         |

| 0110_100               | 60.0                            | 80.0  | 2.5                                   | 150.0 | 200.0        | 4.5                                     | 270.0 | 360.0        | 3                  | 50.0 | 66.7         |

| 0110_101               | 60.0                            | 80.0  | 2.5                                   | 150.0 | 200.0        | 5                                       | 300.0 | 400.0        | 3                  | 50.0 | 66.7         |

| 0110_110               | 60.0                            | 80.0  | 2.5                                   | 150.0 | 200.0        | 6                                       | 360.0 | 480.0        | 3                  | 50.0 | 66.7         |

| 0111_000               |                                 |       |                                       |       |              | Reserved                                |       |              |                    |      |              |

| 0111_001               | 50.0                            | 66.7  | 3                                     | 150.0 | 200.0        | 3                                       | 150.0 | 200.0        | 3                  | 50.0 | 66.7         |

| 0111_010               | 50.0                            | 66.7  | 3                                     | 150.0 | 200.0        | 3.5                                     | 175.0 | 233.3        | 3                  | 50.0 | 66.7         |

| 0111_011               | 50.0                            | 66.7  | 3                                     | 150.0 | 200.0        | 4                                       | 200.0 | 266.6        | 3                  | 50.0 | 66.7         |

| 0111_100               | 50.0                            | 66.7  | 3                                     | 150.0 | 200.0        | 4.5                                     | 225.0 |              | 3                  | 50.0 | 66.7         |

|                        |                                 |       |                                       |       |              |                                         |       |              |                    |      | <u> </u>     |

| 1000_000               |                                 |       |                                       |       |              | Reserved                                |       |              |                    |      |              |

| 1000_001               | 66.7                            | 88.9  | 3                                     | 200.0 | 266.6        | 3                                       | 200.0 | 266.6        | 4                  | 50.0 | 66.7         |

| 1000_010               | 66.7                            | 88.9  | 3                                     | 200.0 | 266.6        | 3.5                                     | 233.3 | 311.1        | 4                  | 50.0 | 66.7         |

| 1000_011               | 66.7                            | 88.9  | 3                                     | 200.0 | 266.6        | 4                                       | 266.7 | 355.5        | 4                  | 50.0 | 66.7         |

| 1000_100               | 66.7                            | 88.9  | 3                                     | 200.0 | 266.6        | 4.5                                     | 300.0 | 400.0        | 4                  | 50.0 | 66.7         |

| 1000_101               | 66.7                            | 88.9  | 3                                     | 200.0 | 266.6        | 6                                       | 400.0 | 533.3        | 4                  | 50.0 | 66.7         |

| 1000_110               | 66.7                            | 88.9  | 3                                     | 200.0 | 266.6        | 6.5                                     | 433.3 | 577.7        | 4                  | 50.0 | 66.7         |

| 1001_000               |                                 |       |                                       |       |              | Deserved                                |       |              |                    |      |              |

|                        |                                 |       |                                       |       |              | Reserved                                |       |              |                    |      |              |

| 1001_001               | <b>F7 4</b>                     | 70.0  | 0.5                                   | 000.0 | 000.0        |                                         | 000.0 | 000.0        | 4                  | 50.0 | 00.7         |

| 1001_010               | 57.1                            | 76.2  | 3.5                                   | 200.0 | 266.6        | 3.5                                     | 200.0 |              | 4                  | 50.0 | 66.7         |

| 1001_011               | 57.1                            | 76.2  | 3.5                                   |       | 266.6        | 4                                       |       | 304.7        | 4                  | 50.0 | 66.7         |

| 1001_100               | 57.1                            | 76.2  | 3.5                                   | 200.0 | 266.6        | 4.5                                     | 257.1 | 342.8        | 4                  | 50.0 | 66.7         |

| 1001_101               | 85.7                            | 114.3 | 3.5                                   | 300.0 | 400.0        | 5                                       | 428.6 | 571.4        | 6                  | 50.0 | 66.7         |

| 1001_110               | 85.7                            | 114.3 | 3.5                                   | 300.0 | 400.0        | 5.5                                     | 471.4 |              | 6                  | 50.0 | 66.7         |

| 1001_111               | 85.7                            | 114.3 | 3.5                                   | 300.0 | 400.0        | 6                                       | 514.3 |              | 6                  | 50.0 | 66.7         |

|                        |                                 |       |                                       |       |              |                                         |       |              |                    |      |              |

| 1010_000               | 75.0                            | 100.0 | 2                                     | 150.0 | 200.0        | 2                                       | 150.0 | 200.0        | 3                  | 50.0 | 66.7         |

| 1010_001               | 75.0                            | 100.0 | 2                                     | 150.0 | 200.0        | 2.5                                     | 187.5 | 250.0        | 3                  | 50.0 | 66.7         |

| 1010_010               | 75.0                            | 100.0 | 2                                     | 150.0 | 200.0        | 3                                       | 225.0 | 300.0        | 3                  | 50.0 | 66.7         |

| Mode <sup>3</sup>      |      | Clock <sup>4</sup><br>Hz) | CPM<br>Multiplication |       | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | k<br>PCI<br>Division |      | Clock<br>Hz) |

|------------------------|------|---------------------------|-----------------------|-------|--------------|-----------------------|-------|--------------|----------------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low  | High                      | Factor <sup>5</sup>   | Low   | High         | Factor <sup>6</sup>   | Low   | High         | Factor               | Low  | High         |

| 0010_110               | 37.5 | 75.0                      | 4                     | 150.0 | 300.0        | 6                     | 225.0 | 450.0        | 6                    | 25.0 | 50.0         |

|                        |      |                           | r                     |       | •            |                       |       |              |                      |      | 1            |

| 0011_000               | 30.0 | 50.0                      | 5                     | 150.0 | 250.0        | 5                     | 150.0 | 250.0        | 5                    | 30.0 | 50.0         |

| 0011_001               | 25.0 | 50.0                      | 5                     | 125.0 | 250.0        | 6                     | 150.0 | 300.0        | 5                    | 25.0 | 50.0         |

| 0011_010               | 25.0 | 50.0                      | 5                     | 125.0 | 250.0        | 7                     | 175.0 | 350.0        | 5                    | 25.0 | 50.0         |

| 0011_011               | 25.0 | 50.0                      | 5                     | 125.0 | 250.0        | 8                     | 200.0 | 400.0        | 5                    | 25.0 | 50.0         |

| 0100_000               |      |                           |                       |       |              | Reserved              |       |              |                      |      |              |

| 0100_001               | 25.0 | 50.0                      | 6                     | 150.0 | 300.0        | 6                     | 150.0 | 300.0        | 6                    | 25.0 | 50.0         |

| 0100_010               | 25.0 | 50.0                      | 6                     | 150.0 | 300.0        | 7                     | 175.0 | 350.0        | 6                    | 25.0 | 50.0         |

| 0100_011               | 25.0 | 50.0                      | 6                     | 150.0 | 300.0        | 8                     | 200.0 | 400.0        | 6                    | 25.0 | 50.0         |

|                        |      |                           | l                     |       |              |                       |       |              |                      |      | 1            |

| 0101_000               | 60.0 | 100.0                     | 2                     | 120.0 | 200.0        | 2.5                   | 150.0 | 250.0        | 4                    | 30.0 | 50.0         |

| 0101_001               | 50.0 | 100.0                     | 2                     | 100.0 | 200.0        | 3                     | 150.0 | 300.0        | 4                    | 25.0 | 50.0         |

| 0101_010               | 50.0 | 100.0                     | 2                     | 100.0 | 200.0        | 3.5                   | 175.0 | 350.0        | 4                    | 25.0 | 50.0         |

| 0101_011               | 50.0 | 100.0                     | 2                     | 100.0 | 200.0        | 4                     | 200.0 | 400.0        | 4                    | 25.0 | 50.0         |

| 0101_100               | 50.0 | 100.0                     | 2                     | 100.0 | 200.0        | 4.5                   | 225.0 | 450.0        | 4                    | 25.0 | 50.0         |

|                        |      |                           |                       |       |              |                       |       |              |                      | •    |              |

| 0110_000               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 2.5                   | 150.0 | 300.0        | 6                    | 25.0 | 50.0         |

| 0110_001               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 3                     | 180.0 | 360.0        | 6                    | 25.0 | 50.0         |

| 0110_010               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 3.5                   | 210.0 | 420.0        | 6                    | 25.0 | 50.0         |

| 0110_011               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 4                     | 240.0 | 480.0        | 6                    | 25.0 | 50.0         |

| 0110_100               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 4.5                   | 270.0 | 540.0        | 6                    | 25.0 | 50.0         |

| 0110_101               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 5                     | 300.0 | 600.0        | 6                    | 25.0 | 50.0         |

| 0110_110               | 60.0 | 120.0                     | 2.5                   | 150.0 | 300.0        | 6                     | 360.0 | 720.0        | 6                    | 25.0 | 50.0         |

|                        |      |                           |                       |       |              |                       |       |              |                      |      |              |

| 0111_000               |      |                           |                       |       |              | Reserved              |       |              |                      |      |              |

| 0111_001               | 50.0 | 100.0                     | 3                     | 150.0 | 300.0        | 3                     | 150.0 | 300.0        | 6                    | 25.0 | 50.0         |

| 0111_010               | 50.0 | 100.0                     | 3                     | 150.0 | 300.0        | 3.5                   | 175.0 | 350.0        | 6                    | 25.0 | 50.0         |

| 0111_011               | 50.0 | 100.0                     | 3                     | 150.0 | 300.0        | 4                     | 200.0 | 400.0        | 6                    | 25.0 | 50.0         |

| 0111_100               | 50.0 | 100.0                     | 3                     | 150.0 | 300.0        | 4.5                   | 225.0 | 450.0        | 6                    | 25.0 | 50.0         |

### Table 20. Clock Configurations for PCI Host Mode (PCI\_MODCK=1)<sup>1,2</sup> (continued)

### Table 20. Clock Configurations for PCI Host Mode (PCI\_MODCK=1)<sup>1,2</sup> (continued)

| Mode                   |      | Clock <sup>4</sup><br>Hz) | CPM<br>Multiplication | CPM Clock<br>(MHz) |       | CPU<br>Multiplication | CPU Clock<br>(MHz) |       |        | PCI Clock<br>(MHz) |      |

|------------------------|------|---------------------------|-----------------------|--------------------|-------|-----------------------|--------------------|-------|--------|--------------------|------|

| MODCK_H-<br>MODCK[1-3] | Low  | High                      | Factor <sup>5</sup>   | Low                | High  | Factor <sup>6</sup>   | Low                | High  | Factor | Low                | High |

| 1000_000               |      |                           |                       |                    |       | Reserved              |                    |       |        |                    |      |

| 1000_001               | 66.7 | 133.3                     | 3                     | 200.0              | 400.0 | 3                     | 200.0              | 400.0 | 8      | 25.0               | 50.0 |

| 1000_010               | 66.7 | 133.3                     | 3                     | 200.0              | 400.0 | 3.5                   | 233.3              | 466.7 | 8      | 25.0               | 50.0 |

| 1000_011               | 66.7 | 133.3                     | 3                     | 200.0              | 400.0 | 4                     | 266.7              | 533.3 | 8      | 25.0               | 50.0 |

| 1000_100               | 66.7 | 133.3                     | 3                     | 200.0              | 400.0 | 4.5                   | 300.0              | 600.0 | 8      | 25.0               | 50.0 |

| 1000_101               | 66.7 | 133.3                     | 3                     | 200.0              | 400.0 | 6                     | 400.0              | 800.0 | 8      | 25.0               | 50.0 |

| 1000_110               | 66.7 | 133.3                     | 3                     | 200.0              | 400.0 | 6.5                   | 433.3              | 866.7 | 8      | 25.0               | 50.0 |

| 1001_000               |      |                           |                       |                    |       | Reserved              |                    |       |        |                    |      |

| 1001_001               |      |                           |                       |                    |       | Reserved              |                    |       |        |                    |      |

| 1001_010               | 57.1 | 114.3                     | 3.5                   | 200.0              | 400.0 | 3.5                   | 200.0              | 400.0 | 8      | 25.0               | 50.0 |

| 1001_011               | 57.1 | 114.3                     | 3.5                   | 200.0              | 400.0 | 4                     | 228.6              | 457.1 | 8      | 25.0               | 50.0 |

| 1001_100               | 57.1 | 114.3                     | 3.5                   | 200.0              | 400.0 | 4.5                   | 257.1              | 514.3 | 8      | 25.0               | 50.0 |

|                        |      |                           |                       |                    |       |                       |                    |       |        |                    |      |

| 1001_101               | 42.9 | 85.7                      | 3.5                   | 150.0              | 300.0 | 5                     | 214.3              | 428.6 | 6      | 25.0               | 50.0 |

| 1001_110               | 42.9 | 85.7                      | 3.5                   | 150.0              | 300.0 | 5.5                   | 235.7              | 471.4 | 6      | 25.0               | 50.0 |

| 1001_111               | 42.9 | 85.7                      | 3.5                   | 150.0              | 300.0 | 6                     | 257.1              | 514.3 | 6      | 25.0               | 50.0 |

| 1010_000               | 75.0 | 150.0                     | 2                     | 150.0              | 300.0 | 2                     | 150.0              | 300.0 | 6      | 25.0               | 50.0 |

| 1010_001               | 75.0 | 150.0                     | 2                     | 150.0              |       | 2.5                   | 187.5              | 375.0 | 6      | 25.0               | 50.0 |

| 1010_010               | 75.0 | 150.0                     | 2                     | 150.0              |       | 3                     | 225.0              | 450.0 | 6      | 25.0               | 50.0 |

| 1010_011               | 75.0 | 150.0                     | 2                     | 150.0              |       | 3.5                   | 262.5              | 525.0 | 6      | 25.0               | 50.0 |

| 1010_100               | 75.0 | 150.0                     | 2                     | 150.0              | 300.0 | 4                     | 300.0              | 600.0 | 6      | 25.0               | 50.0 |

|                        |      |                           |                       |                    |       |                       |                    |       |        |                    |      |

| 1011_000               |      |                           |                       |                    |       | Reserved              |                    |       |        |                    |      |

| 1011_001               | 80.0 | 160.0                     | 2.5                   | 200.0              | 400.0 | 2.5                   | 200.0              | 400.0 | 8      | 25.0               | 50.0 |

| 1011_010               | 80.0 | 160.0                     | 2.5                   | 200.0              | 400.0 | 3                     | 240.0              | 480.0 | 8      | 25.0               | 50.0 |

| 1011_011               | 80.0 | 160.0                     | 2.5                   | 200.0              | 400.0 | 3.5                   | 280.0              | 560.0 | 8      | 25.0               | 50.0 |

| 1011_100               | 80.0 | 160.0                     | 2.5                   | 200.0              | 400.0 | 4                     | 320.0              | 640.0 | 8      | 25.0               | 50.0 |

| 1011_101               | 80.0 | 160.0                     | 2.5                   | 200.0              | 400.0 | 4.5                   | 360.0              | 720.0 | 8      | 25.0               | 50.0 |

| 1101_000               | 50.0 | 100.0                     | 2.5                   | 125.0              | 250.0 | 3                     | 150.0              | 300.0 | 5      | 25.0               | 50.0 |

**Clock Configuration Modes**

| Mode <sup>3</sup>      |      | Clock <sup>4</sup><br>Hz) | CPM<br>Multiplication | YM (MHz) CPU |       | CPU Clock<br>(MHz)  |       | PCI<br>Division |        | PCI Clock<br>(MHz) |      |

|------------------------|------|---------------------------|-----------------------|--------------|-------|---------------------|-------|-----------------|--------|--------------------|------|

| MODCK_H-<br>MODCK[1-3] | Low  | High                      | Factor <sup>5</sup>   | Low          | High  | Factor <sup>6</sup> | Low   | High            | Factor | Low                | High |

| 1101_001               | 50.0 | 100.0                     | 2.5                   | 125.0        | 250.0 | 3.5                 | 175.0 | 350.0           | 5      | 25.0               | 50.0 |

| 1101_010               | 50.0 | 100.0                     | 2.5                   | 125.0        | 250.0 | 4                   | 200.0 | 400.0           | 5      | 25.0               | 50.0 |

| 1101_011               | 50.0 | 100.0                     | 2.5                   | 125.0        | 250.0 | 4.5                 | 225.0 | 450.0           | 5      | 25.0               | 50.0 |

| 1101_100               | 50.0 | 100.0                     | 2.5                   | 125.0        | 250.0 | 5                   | 250.0 | 500.0           | 5      | 25.0               | 50.0 |

|                        |      |                           |                       |              |       |                     |       |                 |        |                    |      |

| 1101_101               | 62.5 | 125.0                     | 2                     | 125.0        | 250.0 | 3                   | 187.5 | 375.0           | 5      | 25.0               | 50.0 |

| 1101_110               | 62.5 | 125.0                     | 2                     | 125.0        | 250.0 | 4                   | 250.0 | 500.0           | 5      | 25.0               | 50.0 |

|                        |      |                           |                       |              |       |                     |       |                 |        |                    |      |

| 1110_000               | 50.0 | 100.0                     | 3                     | 150.0        | 300.0 | 3.5                 | 175.0 | 350.0           | 6      | 25.0               | 50.0 |

| 1110_001               | 50.0 | 100.0                     | 3                     | 150.0        | 300.0 | 4                   | 200.0 | 400.0           | 6      | 25.0               | 50.0 |

| 1110_010               | 50.0 | 100.0                     | 3                     | 150.0        | 300.0 | 4.5                 | 225.0 | 450.0           | 6      | 25.0               | 50.0 |

| 1110_011               | 50.0 | 100.0                     | 3                     | 150.0        | 300.0 | 5                   | 250.0 | 500.0           | 6      | 25.0               | 50.0 |

| 1110_100               | 50.0 | 100.0                     | 3                     | 150.0        | 300.0 | 5.5                 | 275.0 | 550.0           | 6      | 25.0               | 50.0 |

|                        |      |                           |                       |              |       |                     |       | 11              |        | I                  |      |

| 1100_000               |      |                           |                       |              |       | Reserved            |       |                 |        |                    |      |

| 1100_001               |      | Reserved                  |                       |              |       |                     |       |                 |        |                    |      |

| 1100_010               |      | Reserved                  |                       |              |       |                     |       |                 |        |                    |      |

| Table 20. Clock Configurations for PCI Host Mode (PC | PCI_MODCK=1) <sup>1,2</sup> (continued) |

|------------------------------------------------------|-----------------------------------------|

|------------------------------------------------------|-----------------------------------------|

<sup>1</sup> The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not violate the frequency rating of the user's device. The minimum CPM frequency is 120 MHz. Minimum CPU frequency is determined by the clock mode. For modes with a CPU multiplication factor <= 3, the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. For modes with a CPU multiplication factor >= 3.5: for Rev0.1 the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices.

- <sup>2</sup> As Table 17 shows, PCI\_MODCK determines the PCI clock frequency range. See Table 20 for higher configurations.

- <sup>3</sup> MODCK\_H = hard reset configuration word [28–31]. MODCK[1-3] = three hardware configuration pins.

- <sup>4</sup> 60x and local bus frequency. Identical to CLKIN.

- <sup>5</sup> CPM multiplication factor = CPM clock/bus clock

- <sup>6</sup> CPU multiplication factor = Core PLL multiplication factor

### 7.3 PCI Agent Mode

These tables show configurations for PCI agent mode. The frequency values listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. Note that in PCI agent mode the following:

**Clock Configuration Modes**

### NOTE: PCI\_MODCK

In PCI mode only, PCI\_MODCK comes from the LGPL5 pin and MODCK\_H[0–3] comes from {LGPL0, LGPL1, LGPL2, LGPL3}.

### **NOTE: Tval (Output Hold)**

The minimum Tval = 2 ns when PCI\_MODCK = 1, and the minimum Tval = 1 ns when PCI\_MODCK = 0. Therefore, designers should use clock configurations that fit this condition to achieve PCI-compliant AC timing.

| Table 21. Clock C | onfigurations | for PCI | Agent Mode | (PCI | _MODCK=0) <sup>1,2</sup> |

|-------------------|---------------|---------|------------|------|--------------------------|

|                   |               |         |            |      |                          |

| Mode <sup>3</sup>           | PCI (<br>(M              | Clock<br>Hz) | CPM<br>Multiplication | CPM<br>(M | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | Bus<br>Division |      | Clock<br>Hz) |

|-----------------------------|--------------------------|--------------|-----------------------|-----------|--------------|-----------------------|-------|--------------|-----------------|------|--------------|

| MODCK_H-<br>MODCK[1-3]      | Low                      | High         | Factor <sup>4</sup>   | Low       | High         | Factor <sup>5</sup>   | Low   | High         | Factor          | Low  | High         |

| Default Modes (MODCK_H=0000 |                          |              |                       |           |              |                       |       |              |                 |      |              |

| 0000_000                    | 60.0                     | 66.7         | 2                     | 120.0     | 133.3        | 2.5                   | 150.0 | 166.7        | 2               | 60.0 | 66.7         |

| 0000_001                    | 50.0                     | 66.7         | 2                     | 100.0     | 133.3        | 3                     | 150.0 | 200.0        | 2               | 50.0 | 66.7         |

| 0000_010                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 3                     | 150.0 | 200.0        | 3               | 50.0 | 66.7         |

| 0000_011                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 4                     | 200.0 | 266.6        | 3               | 50.0 | 66.7         |

| 0000_100                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 3                     | 180.0 | 240.0        | 2.5             | 60.0 | 80.0         |

| 0000_101                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 3.5                   | 210.0 | 280.0        | 2.5             | 60.0 | 80.0         |

| 0000_110                    | 50.0                     | 66.7         | 4                     | 200.0     | 266.6        | 3.5                   | 233.3 | 311.1        | 3               | 66.7 | 88.9         |

| 0000_111                    | 50.0                     | 66.7         | 4                     | 200.0     | 266.6        | 3                     | 240.0 | 320.0        | 2.5             | 80.0 | 106.7        |

|                             | Full Configuration Modes |              |                       |           |              |                       |       |              |                 |      |              |

| 0001_001                    | 60.0                     | 66.7         | 2                     | 120.0     | 133.3        | 5                     | 150.0 | 166.7        | 4               | 30.0 | 33.3         |

| 0001_010                    | 50.0                     | 66.7         | 2                     | 100.0     | 133.3        | 6                     | 150.0 | 200.0        | 4               | 25.0 | 33.3         |

| 0001_011                    | 50.0                     | 66.7         | 2                     | 100.0     | 133.3        | 7                     | 175.0 | 233.3        | 4               | 25.0 | 33.3         |

| 0001_100                    | 50.0                     | 66.7         | 2                     | 100.0     | 133.3        | 8                     | 200.0 | 266.6        | 4               | 25.0 | 33.3         |

|                             |                          |              |                       |           |              |                       |       |              |                 |      |              |

| 0010_001                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 3                     | 180.0 | 240.0        | 2.5             | 60.0 | 80.0         |

| 0010_010                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 3.5                   | 210.0 | 280.0        | 2.5             | 60.0 | 80.0         |

| 0010_011                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 4                     | 240.0 | 320.0        | 2.5             | 60.0 | 80.0         |

| 0010_100                    | 50.0                     | 66.7         | 3                     | 150.0     | 200.0        | 4.5                   | 270.0 | 360.0        | 2.5             | 60.0 | 80.0         |

|                             |                          |              |                       |           |              |                       |       |              |                 |      |              |

| 0011_000                    |                          |              |                       |           |              | Reserved              |       |              |                 |      |              |

| 0011_001                    |                          |              |                       |           |              | Reserved              |       |              |                 |      |              |

| 0011_010                    |                          | Reserved     |                       |           |              |                       |       |              |                 |      |              |

| 0011_011                    |                          | Reserved     |                       |           |              |                       |       |              |                 |      |              |

| 0011_100                    |                          |              |                       |           |              | Reserved              |       |              |                 |      |              |

| Mode <sup>3</sup>      |      | Clock<br>Hz) | -                   |       | Clock<br>Hz) | CPU<br>Multiplication | CPU Clock<br>(MHz) |       | Bus<br>Division | Bus Clock<br>(MHz) |       |

|------------------------|------|--------------|---------------------|-------|--------------|-----------------------|--------------------|-------|-----------------|--------------------|-------|

| MODCK_H-<br>MODCK[1-3] | Low  | High         | Factor <sup>4</sup> | Low   | High         | Eastar <sup>5</sup>   | Low                | High  | Factor          | Low                | High  |

| 1110_011               | 50.0 | 66.7         | 5                   | 250.0 | 333.3        | 4                     | 500.0              | 666.6 | 2               | 125.0              | 166.7 |

|                        | •    |              |                     | •     |              |                       |                    |       |                 | •                  |       |

| 1110_100               | 50.0 | 66.7         | 5                   | 250.0 | 333.3        | 4                     | 333.3              | 444.4 | 3               | 83.3               | 111.1 |

| 1110_101               | 50.0 | 66.7         | 5                   | 250.0 | 333.3        | 4.5                   | 375.0              | 500.0 | 3               | 83.3               | 111.1 |

| 1110_110               | 50.0 | 66.7         | 5                   | 250.0 | 333.3        | 5                     | 416.7              | 555.5 | 3               | 83.3               | 111.1 |

| 1110_111               | 50.0 | 66.7         | 5                   | 250.0 | 333.3        | 5.5                   | 458.3              | 611.1 | 3               | 83.3               | 111.1 |

|                        |      |              |                     |       |              |                       |                    |       |                 |                    |       |

| 1100_000               |      | Reserved     |                     |       |              |                       |                    |       |                 |                    |       |

| 1100_001               |      | Reserved     |                     |       |              |                       |                    |       |                 |                    |       |

| 1100_010               |      |              |                     |       |              | Reserved              |                    |       |                 |                    |       |

### Table 21. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

<sup>1</sup> The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not violate the frequency rating of the user's device. The minimum CPM frequency is 120 MHz. Minimum CPU frequency is determined by the clock mode. For modes with a CPU multiplication factor <= 3, the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. For modes with a CPU multiplication factor >= 3.5: for Rev 0.1 the minimum CPU frequency is 250 MHz; for Rev A or later the minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices.

<sup>2</sup> As shown in Table 17, PCI\_MODCK determines the PCI clock frequency range. See Table 20 for lower configurations.

<sup>3</sup> MODCK\_H = hard reset configuration word [28–31]. MODCK[1-3] = three hardware configuration pins.

<sup>4</sup> CPM multiplication factor = CPM clock/PCI clock

<sup>5</sup> CPU multiplication factor = Core PLL multiplication factor

### Table 22. Clock Configurations for PCI Agent Mode (PCI\_MODCK=1)<sup>1,2</sup>

| Mode <sup>3</sup>      |      | Clock<br>Hz) | CPM<br>Multiplication | CPM Clock<br>(MHz) |         | CPU<br>Multiplication | CPU Clock<br>(MHz) |       | Bus<br>Division | Bus Clock<br>(MHz) |       |

|------------------------|------|--------------|-----------------------|--------------------|---------|-----------------------|--------------------|-------|-----------------|--------------------|-------|

| MODCK_H-<br>MODCK[1-3] | Low  | High         | Factor <sup>4</sup>   | Low                | High    | Factor <sup>5</sup>   | Low                | High  | Factor          | Low                | High  |

|                        |      |              | De                    | fault M            | odes (N | /IODCK_H=0000)        | L                  |       |                 |                    |       |

| 0000_000               | 30.0 | 50.0         | 4                     | 120.0              | 200.0   | 2.5                   | 150.0              | 250.0 | 2               | 60.0               | 100.0 |

| 0000_001               | 25.0 | 50.0         | 4                     | 100.0              | 200.0   | 3                     | 150.0              | 300.0 | 2               | 50.0               | 100.0 |

| 0000_010               | 25.0 | 50.0         | 6                     | 150.0              | 300.0   | 3                     | 150.0              | 300.0 | 3               | 50.0               | 100.0 |

| 0000_011               | 25.0 | 50.0         | 6                     | 150.0              | 300.0   | 4                     | 200.0              | 400.0 | 3               | 50.0               | 100.0 |

| 0000_100               | 25.0 | 50.0         | 6                     | 150.0              | 300.0   | 3                     | 180.0              | 360.0 | 2.5             | 60.0               | 120.0 |

| 0000_101               | 25.0 | 50.0         | 6                     | 150.0              | 300.0   | 3.5                   | 210.0              | 420.0 | 2.5             | 60.0               | 120.0 |

| 0000_110               | 25.0 | 50.0         | 8                     | 200.0              | 400.0   | 3.5                   | 233.3              | 466.7 | 3               | 66.7               | 133.3 |

- <sup>2</sup> As shown in Table 17, PCI\_MODCK determines the PCI clock range. See Table 20 for higher range configurations.

- <sup>3</sup> MODCK\_H = hard reset configuration word [28–31]. MODCK[1-3] = three hardware configuration pins.

- <sup>4</sup> CPM multiplication factor = CPM clock/PCI clock

- <sup>5</sup> CPU multiplication factor = Core PLL multiplication factor

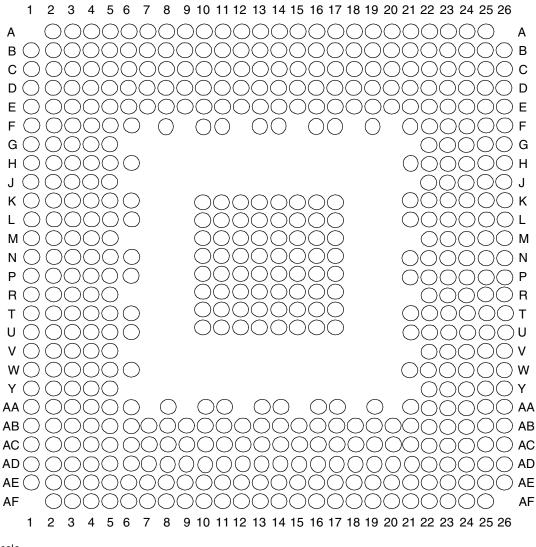

## 8 Pinout

This section provides the pin assignments and pinout lists for both HiP7 PowerQUICC II packages.

### 8.1 ZU and VV Packages—MPC8280 and MPC8270

The following figures and table represent the standard 480 TBGA package. For information on the alternate package, see Section 8.2, "VR and ZQ Packages—MPC8275 and MPC8270."

| Table 23, MPC8280 and MPC8270 ( | ZU and VV Packages) Pinout List (continued) |

|---------------------------------|---------------------------------------------|

|                                 |                                             |

| Pin Na          | me           | Dell |

|-----------------|--------------|------|

| MPC8280/MPC8270 | MPC8280 only | Ball |

| D18             |              | D15  |

| D19             |              | C13  |

| D20             |              | B11  |

| D21             |              | A8   |

| D22             |              | A5   |

| D23             |              | C5   |

| D24             |              | C19  |

| D25             |              | C17  |

| D26             |              | C15  |

| D27             |              | D13  |

| D28             |              | C11  |

| D29             |              | B8   |

| D30             |              | A4   |

| D31             |              | E6   |

| D32             |              | E18  |

| D33             |              | B17  |

| D34             |              | A15  |

| D35             |              | A12  |

| D36             |              | D11  |

| D37             |              | C8   |

| D38             |              | E7   |

| D39             |              | A3   |

| D40             |              | D18  |

| D41             |              | A17  |

| D42             |              | A14  |

| D43             |              | B12  |

| D44             |              | A10  |

| D45             |              | D8   |

| D46             |              | B6   |

| D47             |              | C4   |

| D48             |              | C18  |

| D49             |              | E16  |

| D50             |              | B14  |

This figure shows the pinout of the VR and ZQ packages as viewed from the top surface.

Not to Scale

Figure 14. Pinout of the 516 PBGA Package (View from Top)

This table shows the pinout list of the MPC8275 and MPC8270. Table 24 defines conventions and acronyms used in Table 25.

| Pin N           | Ball |  |

|-----------------|------|--|

| MPC8275/MPC8270 |      |  |

| BR              | C16  |  |

| BG              | D2   |  |

| ABB/IRQ2        | C1   |  |

| TS              | D1   |  |

Pinout

| Pin Name        |              | D-11 |

|-----------------|--------------|------|

| MPC8275/MPC8270 | MPC8275 only | Ball |

| A0              |              | D5   |

| A1              |              | E8   |

| A2              |              | C4   |

| A3              |              | B4   |

| A4              |              | A4   |

| A5              |              | D7   |

| A6              |              | D8   |

| A7              |              | C6   |

| A8              |              | B5   |

| A9              |              | B6   |

| A10             |              | C7   |

| A11             |              | C8   |

| A12             |              | A6   |

| A13             |              | D9   |

| A14             |              | F11  |

| A15             |              | B7   |

| A16             |              | B8   |

| A17             |              | C9   |

| A18             |              | A7   |

| A19             |              | B9   |

| A20             |              | E11  |

| A21             |              | A8   |

| A22             |              | D11  |

| A23             |              | B10  |

| A24             |              | C11  |

| A25             |              | A9   |

| A26             |              | B11  |

| A27             |              | C12  |

| A28             |              | D12  |

| A29             |              | A10  |

| A30             |              | B12  |

| A31             |              | B13  |

| ТТО             |              | E7   |

### Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Name        |              |      |

|-----------------|--------------|------|

| MPC8275/MPC8270 | MPC8275 only | Ball |

| TT1             |              | B3   |

| TT2             |              | F8   |

| ТТ3             |              | A3   |

| TT4             |              | C3   |

| TBST            |              | F5   |

| TSIZ0           |              | E3   |

| TSIZ1           |              | E2   |

| TSIZ2           |              | E1   |

| TSIZ3           |              | E4   |

| AACK            |              | D3   |

| ARTRY           |              | C2   |

| DBG             |              | A14  |

| DBB/IRQ3        |              | C15  |

| D0              |              | W4   |

| D1              |              | Y1   |

| D2              |              | V1   |

| D3              |              | P4   |

| D4              |              | N3   |

| D5              |              | K5   |

| D6              |              | J4   |

| D7              |              | G1   |

| D8              |              | AB1  |

| D9              |              | U4   |

| D10             |              | U2   |

| D11             |              | N6   |

| D12             |              | N1   |

| D13             |              | L1   |

| D14             |              | J5   |

| D15             |              | G3   |

| D16             |              | AA2  |

| D17             |              | W1   |

| D18             |              | Т3   |

| D19             |              | T1   |

### Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

Pinout

### Table 25. MPC8275 and MPC8270 (VR and ZQ Packages) Pinout List (continued)

| Pin Name                                                          |                                                            | D-11              |

|-------------------------------------------------------------------|------------------------------------------------------------|-------------------|

| MPC8275/MPC8270                                                   | MPC8275 only                                               | Ball              |

| PC5/SI2_L1ST3/FCC2_CTS                                            | FCC2_UTM_TXCLAV/<br>FCC2_UTS_TXCLAV                        | AC25 <sup>2</sup> |

| PC6/FCC1_CD                                                       | FCC1_UTM_RXADDR2/<br>FCC1_UTS_RXADDR2/<br>FCC1_UTM_RXCLAV1 | AB25 <sup>2</sup> |

| PC7/FCC1_CTS                                                      | FCC1_UTM_TXADDR2/<br>FCC1_UTS_TXADDR2/<br>FCC1_UTM_TXCLAV1 | AA24 <sup>2</sup> |

| PC8/ <del>CD4</del> /RENA4/SI2_L1ST2/ <del>CTS3</del> /<br>USB_RN | FCC1_UT16_TXD0                                             | Y24 <sup>2</sup>  |

| PC9/CTS4/CLSN4/SI2_L1ST1/<br>L1TSYNCA2/L1GNTA2/USB_RP             | FCC1_UT16_TXD1                                             | U22 <sup>2</sup>  |

| PC10/CD3/RENA3                                                    | FCC1_UT16_TXD2/FCC2_UT8_RXD3                               | V23 <sup>2</sup>  |

| PC11/CTS3/CLSN3/L1TXD3A2                                          | FCC2_UT8_RXD2                                              | U23 <sup>2</sup>  |

| PC12/CD2/RENA2                                                    | FCC1_UTM_RXADDR1/<br>FCC1_UTS_RXADDR1                      | T26 <sup>2</sup>  |

| PC13/CTS2/CLSN2                                                   | FCC1_UTM_TXADDR1/<br>FCC1_UTS_TXADDR1                      | R26 <sup>2</sup>  |

| PC14/CD1/RENA1                                                    | FCC1_UTM_RXADDR0/<br>FCC1_UTS_RXADDR0                      | P26 <sup>2</sup>  |

| PC15/CTS1/CLSN1/SMTXD2                                            | FCC1_UTM_TXADDR0/<br>FCC1_UTS_TXADDR0                      | P24 <sup>2</sup>  |

| PC16/CLK16/TIN4                                                   |                                                            | M26 <sup>2</sup>  |

| PC17/CLK15/TIN3/BRGO8                                             |                                                            | L26 <sup>2</sup>  |

| PC18/CLK14/TGATE2                                                 |                                                            | M24 <sup>2</sup>  |

| PC19/CLK13/BRGO7/SPICLK                                           |                                                            | L22 <sup>2</sup>  |

| PC20/CLK12/TGATE1/USB_OE                                          |                                                            | K25 <sup>2</sup>  |

| PC21/CLK11/BRGO6                                                  |                                                            | J25 <sup>2</sup>  |

| PC22/CLK10/DONE1                                                  | FCC1_UT_TXPRTY                                             | G26 <sup>2</sup>  |

| PC23/CLK9/BRGO5/DACK1                                             |                                                            | F26 <sup>2</sup>  |

| PC24/CLK8/TOUT4                                                   | FCC2_UT8_TXD3                                              | G24 <sup>2</sup>  |

| PC25/CLK7/BRGO4                                                   | FCC2_UT8_TXD2                                              | E25 <sup>2</sup>  |

| PC26/CLK6/TOUT3/TMCLK                                             |                                                            | G23 <sup>2</sup>  |

| PC27/FCC3_TXD/FCC3_MII_TXD0/<br>FCC3_RMII_TXD0/CLK5/BRGO3         |                                                            | B23 <sup>2</sup>  |

| PC28/CLK4/TIN1/TOUT2/CTS2/CLSN2                                   | FCC2_UT_RXADDR4                                            | E22 <sup>2</sup>  |

| PC29/CLK3/TIN2/BRGO2/CTS1/CLSN1                                   |                                                            | E21 <sup>2</sup>  |

| PC30/CLK2/TOUT1                                                   | FCC2_UT8_TXD3                                              | D21 <sup>2</sup>  |

**Package Description**

### 9.2 Mechanical Dimensions

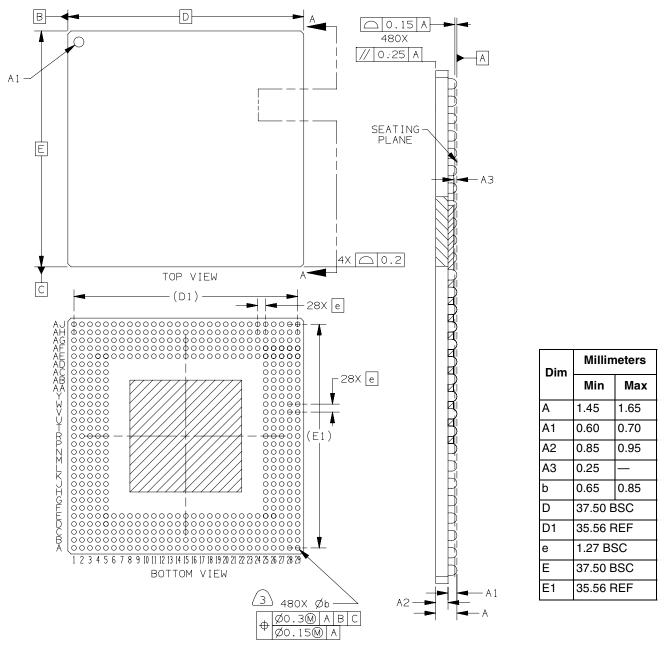

This figure provides the mechanical dimensions and bottom surface nomenclature of the 480 TBGA (ZU/VV) package. See Table 2, "HiP7 PowerQUICC II Device Packages."

#### Notes:

- 1. Dimensions and Tolerancing per ASME Y14.5M-1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is measured at the maximum solder ball diameter, parallel to primary data A.

- 4. Primary data A and the seating plane are defined by the spherical crowns of the solder balls.

### Figure 17. Mechanical Dimensions and Bottom Surface Nomenclature—480 TBGA

| Revision | Date   | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|