Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

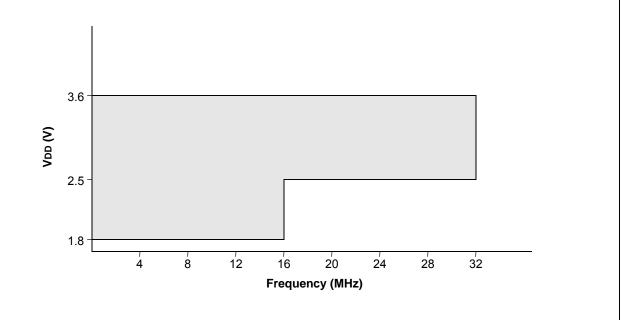

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 23x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

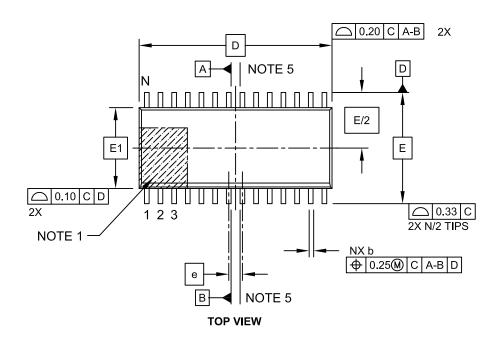

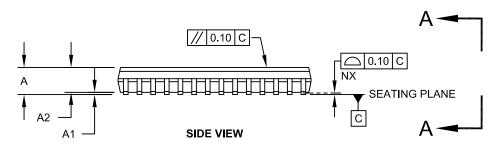

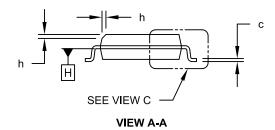

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1566-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                           | 11  |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                                                    | 20  |

| 3.0   | Memory Organization                                                       | 22  |

| 4.0   | Device Configuration                                                      | 58  |

| 5.0   | Oscillator Module                                                         | 63  |

| 6.0   | Resets                                                                    | 71  |

| 7.0   | Interrupts                                                                | 79  |

| 8.0   | Power-Down Mode (Sleep)                                                   | 89  |

| 9.0   | Watchdog Timer (WDT)                                                      | 91  |

| 10.0  | Flash Program Memory Control                                              | 95  |

| 11.0  |                                                                           |     |

| 12.0  |                                                                           |     |

|       | Fixed Voltage Reference (FVR)                                             |     |

| 14.0  | Temperature Indicator Module                                              | 137 |

| 15.0  | Analog-to-Digital Converter (ADC) Module                                  | 139 |

| 16.0  | Hardware Capacitive Voltage Divider (CVD) Module                          | 153 |

|       | Timer0 Module                                                             |     |

| 18.0  | Timer1 Module with Gate Control                                           | 182 |

| 19.0  | Timer2/4 Modules                                                          |     |

| 20.0  |                                                                           |     |

| 21.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 255 |

| 22.0  | Pulse-Width Modulation (PWM) Module                                       | 282 |

| 23.0  | In-Circuit Serial Programming™ (ICSP™)                                    | 289 |

| 24.0  | Instruction Set Summary                                                   | 291 |

| 25.0  | Electrical Specifications                                                 | 305 |

| 26.0  | DC and AC Characteristics Graphs and Charts                               | 328 |

| 27.0  | a car a carrier                                                           |     |

| 28.0  | Packaging Information                                                     | 333 |

| Appe  | endix A: Data Sheet Revision History                                      | 352 |

| The I | Microchip Website                                                         | 353 |

| Custo | omer Change Notification Service                                          | 353 |

| Custo | omer Support                                                              | 353 |

| Prod  | uct Identification System                                                 | 354 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

The PIC16LF1566/1567 devices are described within this data sheet. The block diagram of these devices is shown in Figure 1-1, the available peripherals are shown in Table 1-1 and the pinout descriptions are shown in Table 1-2 and Table 1-3.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                                      |          | PIC16LF1566 | PIC16LF1567 |

|---------------------------------------------------------------------------------|----------|-------------|-------------|

| Analog-to-Digital Converter (ADC)                                               |          |             |             |

|                                                                                 | ADC1     | •           | •           |

|                                                                                 | ADC2     | •           | •           |

| Hardware Capacitive Voltage Divid                                               | er (CVD) | •           | •           |

| Enhanced Universal<br>Synchronous/Asynchronous<br>Receiver/Transmitter (EUSART) | •        | •           |             |

| Fixed Voltage Reference (FVR)                                                   | •        | •           |             |

| Temperature Indicator                                                           | •        | •           |             |

| Master Synchronous Serial Ports                                                 |          |             |             |

|                                                                                 | MSSP1    | •           | •           |

|                                                                                 | MSSP2    | •           | •           |

| PWM Modules                                                                     |          |             |             |

|                                                                                 | PWM1     | •           | •           |

|                                                                                 | PWM2     | •           | •           |

| Timers                                                                          |          |             |             |

|                                                                                 | Timer0   | •           | •           |

|                                                                                 | Timer1   | •           | •           |

|                                                                                 | Timer2   | •           | •           |

|                                                                                 | Timer4   | •           | •           |

TABLE 3-3: PIC16LF1566 MEMORY MAP, BANKS 0-7

|          | BANK 0                          |      | BANK 1             |      | BANK 2             |      | BANK 3            |           | BANK 4                |      | BANK 5    |      | BANK 6             |      | BANK 7             |

|----------|---------------------------------|------|--------------------|------|--------------------|------|-------------------|-----------|-----------------------|------|-----------|------|--------------------|------|--------------------|

| 000h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 001h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 002h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 003h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 004h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 005h     |                                 |      |                    |      |                    |      | CPLI Core Registe | r see Ta  | ble 3-2 for specifics |      |           |      |                    |      |                    |

| 006h     |                                 |      |                    |      |                    |      | or o oore registe | ,, 300 Ta | ibic 0-2 for apcomes  |      |           |      |                    |      |                    |

| 007h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 008h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 009h     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 00Ah     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 00Bh     |                                 |      |                    |      |                    |      |                   |           |                       |      |           |      |                    |      |                    |

| 00Ch     | PORTA                           | 08Ch | TRISA              | 10Ch | LATA               | 18Ch | ANSELA            | 20Ch      | _                     | 28Ch |           | 30Ch |                    | 38Ch | _                  |

| 00Dh     | PORTB                           | 08Dh | TRISB              | 10Dh | LATB               | 18Dh | ANSELB            | 20Dh      | WPUB                  | 28Dh | _         | 30Dh | 1                  | 38Dh | _                  |

| 00Eh     | PORTC                           | 08Eh | TRISC              | 10Eh | LATC               | 18Eh | ANSELC            | 20Eh      | _                     | 28Eh | _         | 30Eh |                    | 38Eh | _                  |

| 00Fh     | _                               | 08Fh | _                  | 10Fh | _                  | 18Fh | _                 | 20Fh      | _                     | 28Fh | _         | 30Fh |                    | 38Fh | _                  |

| 010h     | PORTE                           | 090h | _                  | 110h | _                  | 190h | _                 | 210h      | WPUE                  | 290h | _         | 310h |                    | 390h | _                  |

| 011h     | PIR1                            | 091h | PIE1               | 111h | _                  | 191h | PMADRL            | 211h      | SSP1BUF               | 291h | _         | 311h | I                  | 391h | _                  |

| 012h     | PIR2                            | 092h | PIE2               | 112h | _                  | 192h | PMADRH            | 212h      | SSP1ADD               | 292h | _         | 312h | _                  | 392h | _                  |

| 013h     | _                               | 093h | _                  | 113h | _                  | 193h | PMDATL            | 213h      | SSP1MSK               | 293h | _         | 313h | _                  | 393h | _                  |

| 014h     | _                               | 094h | _                  | 114h | _                  | 194h | PMDATH            | 214h      | SSP1STAT              | 294h | _         | 314h | _                  | 394h | IOCBP              |

| 015h     | TMR0                            | 095h | OPTION_REG         | 115h | _                  | 195h | PMCON1            | 215h      | SSP1CON1              | 295h | _         | 315h | _                  | 395h | IOCBN              |

| 016h     | TMR1L                           | 096h | PCON               | 116h | BORCON             | 196h | PMCON2            | 216h      | SSP1CON2              | 296h | _         | 316h | _                  | 396h | IOCBF              |

| 017h     | TMR1H                           | 097h | WDTCON             | 117h | FVRCON             | 197h | _                 | 217h      | SSP1CON3              | 297h | _         | 317h | _                  | 397h | _                  |

| 018h     | T1CON                           | 098h | _                  | 118h | _                  | 198h | _                 | 218h      | SSPLVL                | 298h | _         | 318h | _                  | 398h | _                  |

| 019h     | T1GCON                          | 099h | OSCCON             | 119h | _                  | 199h | RCREG             | 219h      | SSP2BUF               | 299h | _         | 319h | _                  | 399h | _                  |

| 01Ah     | TMR2                            | 09Ah | OSCSTAT            | 11Ah | _                  | 19Ah | TXREG             | 21Ah      | SSP2ADD               | 29Ah | _         | 31Ah | _                  | 39Ah | _                  |

| 01Bh     | PR2                             | 09Bh | ADRESL/            | 11Bh | _                  | 19Bh | SPBRGL            | 21Bh      | SSP2MSK               | 29Bh | _         | 31Bh | _                  | 39Bh | _                  |

| 01Ch     | T2CON                           | 09Ch | ADRESH             | 11Ch | _                  | 19Ch | SPBRGH            | 21Ch      | SSP2STAT              | 29Ch | _         | 31Ch | _                  | 39Ch | _                  |

| 01Dh     | _                               | 09Dh | ADCON0             | 11Dh | APFCON             | 19Dh | RCSTA             | 21Dh      | SSP2CON1              | 29Dh | _         | 31Dh | _                  | 39Dh | _                  |

| 01Eh     | _                               | 09Eh | ADCON1             | 11Eh | _                  | 19Eh | TXSTA             | 21Eh      | SSP2CON2              | 29Eh | _         | 31Eh | _                  | 39Eh | _                  |

| 01Fh     | _                               | 09Fh | ADCON2             | 11Fh | _                  | 19Fh | BAUDCON           | 21Fh      | SSP2CON3              | 29Fh | _         | 31Fh | _                  | 39Fh | _                  |

| 020h     |                                 | 0A0h |                    | 120h |                    | 1A0h |                   | 220h      |                       | 2A0h |           | 320h |                    | 3A0h |                    |

|          |                                 |      |                    |      |                    |      | General           |           | General               |      | General   |      |                    |      |                    |

|          |                                 |      | General<br>Purpose |      | General<br>Purpose |      | Purpose           |           | Purpose               |      | Purpose   |      | General<br>Purpose |      | General<br>Purpose |

|          | General                         |      | Register           |      | Register           |      | Register          |           | Register              |      | Register  |      | Register           |      | Register           |

|          | Purpose<br>Register<br>96 Bytes |      | 80 Bytes           |      | 80 Bytes           |      | 80 Bytes          |           | 80 Bytes              |      | 80 Bytes  |      | 80 Bytes           |      | 80 Bytes           |

| 06Fh     |                                 | 0EFh |                    | 16Fh |                    | 1EFh |                   | 26Fh      |                       | 2EFh |           | 36Fh |                    | 3EFh |                    |

| 070h     |                                 | 0F0h |                    | 170h |                    | 1F0h |                   | 270h      |                       | 2F0h |           | 370h | _                  | 3F0h |                    |

|          |                                 |      | Accesses           | •    | Accesses           |      | Accesses          |           | Accesses              |      | Accesses  |      | Accesses           |      | Accesses           |

| 07Fh     |                                 | 0FFh | 70h – 7Fh          | 17Fh | 70h – 7Fh          | 1FFh | 70h – 7Fh         | 27Fh      | 70h – 7Fh             | 2FFh | 70h – 7Fh | 37Fh | 70h – 7Fh          | 3FFh | 70h – 7Fh          |

| <u> </u> |                                 | - L  |                    |      |                    | . I  |                   | . L       |                       |      |           |      |                    | _ L  |                    |

**Legend:** = Unimplemented data memory locations, read as '0'.

Note 1: These ADC registers are the same as the registers in Bank 14.

### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| U-0   | R-0/q | U-0 | R-0/q  | U-0 | U-0 | R-0/q  | R-0/q  |

|-------|-------|-----|--------|-----|-----|--------|--------|

| _     | PLLSR | _   | HFIOFR | _   | _   | LFIOFR | HFIOFS |

| bit 7 |       |     |        |     |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Conditional

bit 7 **Unimplemented:** Read as '0'

bit 6 PLLSR: 4x PLL Ready bit

1 = 4x PLL is ready 0 = 4x PLL is not ready

bit 5 **Unimplemented:** Read as '0'

bit 4 HFIOFR: High-Frequency Internal Oscillator Ready bit

1 = 16 MHz Internal Oscillator (HFINTOSC) is ready

0 = 16 MHz Internal Oscillator (HFINTOSC) is not ready

bit 3-2 **Unimplemented:** Read as '0'

bit 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit

1 = 31 kHz Internal Oscillator (LFINTOSC) is ready 0 = 31 kHz Internal Oscillator (LFINTOSC) is not ready

bit 0 HFIOFS: High-Frequency Internal Oscillator Stable bit

1 = 16 MHz Internal Oscillator (HFINTOSC) is stable

0 = 16 MHz Internal Oscillator (HFINTOSC) is not yet stable

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register on Page |

|---------|--------|-------|-------|--------|-------|-------|--------|--------|------------------|

| OSCCON  | SPLLEN |       | IRCF  | <3:0>  |       | _     | SCS-   | 69     |                  |

| OSCSTAT |        | PLLSR | _     | HFIOFR | -     | 1     | LFIOFR | HFIOFS | 70               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|------------------|

| CONFICA | 13:8 | _       | _       | _        | _        | CLKOUTEN | BORE     | V<1:0>  | _       |                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   | 1        | FOSC    | C<1:0>  | 59               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

## 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

## 6.14 Register Definitions: Power Control

### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:                               |                      |                                                       |  |  |  |  |  |

|---------------------------------------|----------------------|-------------------------------------------------------|--|--|--|--|--|

| HC = Bit is cleared by hardy          | vare                 | HS = Bit is set by hardware                           |  |  |  |  |  |

| R = Readable bit                      | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |  |  |

| u = Bit is unchanged                  | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |  |

| '1' = Bit is set                      | '0' = Bit is cleared | q = Value depends on condition                        |  |  |  |  |  |

|                                       |                      |                                                       |  |  |  |  |  |

| bit 7 STKOVF: Stack Overflow Flag bit |                      |                                                       |  |  |  |  |  |

| 1 = A Stack Overflow occurred 0 = A Stack Overflow has not occurred or cleared by firmware  bit 6  STKUNF: Stack Underflow Flag bit 1 = A Stack Underflow occurred 0 = A Stack Underflow has not occurred or cleared by firmware  bit 5  Unimplemented: Read as '0'  bit 4  RWDT: Watchdog Timer Reset Flag bit 1 = A Watchdog Timer Reset has not occurred or set by firmware 0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3  RMCLR: MCLR Reset Flag bit 1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit 1 = A RESET instruction Flag bit 1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Brown-out Reset Occurred 0 = A Brown-out Reset occurred 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out R |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| bit 6  STKUNF: Stack Underflow Flag bit  1 = A Stack Underflow occurred 0 = A Stack Underflow has not occurred or cleared by firmware  bit 5  Unimplemented: Read as '0'  bit 4  RWDT: Watchdog Timer Reset Flag bit  1 = A Watchdog Timer Reset has not occurred or set by firmware 0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3  RMCLR: MCLR Reset Flag bit  1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit  1 = A RESET instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred for a Power-on Reset Occurred for a Power-on Reset Status bit 1 = No Brown-out Reset Status bit 1 = No Brown-out Reset Status bit 1 = No Brown-out Reset Occurred                                                                                                                                                                                                                                 |      |

| 1 = A Stack Underflow occurred 0 = A Stack Underflow has not occurred or cleared by firmware  bit 5  Unimplemented: Read as '0'  bit 4  RWDT: Watchdog Timer Reset Flag bit  1 = A Watchdog Timer Reset has not occurred or set by firmware 0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3  RMCLR: MCLR Reset Flag bit  1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit 1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred 0 = A Power-on Reset Status bit 1 = No Brown-out Reset Status bit 1 = No Brown-out Reset Status bit 1 = No Brown-out Reset Occurred                                                                                                                                                                                                                                                                                      |      |

| bit 5  Unimplemented: Read as '0'  bit 4  RWDT: Watchdog Timer Reset Flag bit  1 = A Watchdog Timer Reset has not occurred or set by firmware 0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3  RMCLR: MCLR Reset Flag bit 1 = A MCLR Reset Flag bit 1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit 1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset Occurred                                                                                                                                                                                                                                                                                                         |      |

| bit 5 bit 4 RWDT: Watchdog Timer Reset Flag bit  1 = A Watchdog Timer Reset has not occurred or set by firmware 0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3 RMCLR: MCLR Reset Flag bit  1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has not occurred (cleared by hardware)  bit 2 RI: RESET Instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1 POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0 BOR: Brown-out Reset Status bit 1 = No Brown-out Reset Status bit 1 = No Brown-out Reset Occurred                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| bit 4  RWDT: Watchdog Timer Reset Flag bit  1 = A Watchdog Timer Reset has not occurred or set by firmware  0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3  RMCLR: MCLR Reset Flag bit  1 = A MCLR Reset has not occurred or set by firmware  0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware  0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit  1 = No Power-on Reset occurred  0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 1 = A Watchdog Timer Reset has not occurred or set by firmware 0 = A Watchdog Timer Reset has occurred (cleared by hardware)  bit 3  RMCLR: MCLR Reset Flag bit 1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit 1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset Occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| bit 3  RMCLR: MCLR Reset Flag bit  1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| bit 3  RMCLR: MCLR Reset Flag bit  1 = A MCLR Reset has not occurred or set by firmware  0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware  0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit  1 = No Power-on Reset occurred  0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1 = A MCLR Reset has not occurred or set by firmware 0 = A MCLR Reset has occurred (cleared by hardware)  bit 2  RI: RESET Instruction Flag bit 1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| bit 2  RI: RESET Instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| bit 2  RI: RESET Instruction Flag bit  1 = A RESET instruction has not been executed or set by firmware  0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit  1 = No Power-on Reset occurred  0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)  bit 1  POR: Power-on Reset Status bit 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| bit 1  POR: Power-on Reset Status bit  1 = No Power-on Reset occurred  0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| bit 1  POR: Power-on Reset Status bit  1 = No Power-on Reset occurred  0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  bit 0  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 1 = No Power-on Reset occurred 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) bit 0  BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| bit 0  Description:  0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| bit 0  BOR: Brown-out Reset Status bit  1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 1 = No Brown-out Reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 0 - Λ Prown out Poset occurred (must be set in software after a Power on Poset or Prown out P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| occurs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | eset |

### REGISTER 7-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | R/W-0/0 | U-0 | U-0 | R/W-0/0 | U-0    | U-0    | U-0   |

|-------|---------|-----|-----|---------|--------|--------|-------|

| _     | AD2IF   | _   | _   | BCL1IF  | BCL2IF | TMR4IF | _     |

| bit 7 |         |     |     |         |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **Unimplemented:** Read as '0' bit 6 **AD2IF:** ADC 2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 5-4 **Unimplemented:** Read as '0'

bit 3 BCL1IF: MSSP1 Bus Collision Interrupt Flag bit

1 = A Bus Collision was detected (must be cleared in software)

0 = No Bus Collision was detected

bit 2 BCL2IF: MSSP2 Bus Collision Interrupt Flag bit

1 = A Bus Collision was detected (must be cleared in software)

0 = No Bus Collision was detected

bit 1 TMR4IF: TMR4 to PR4 Match Interrupt Flag bit

1 = TMR4 to PR4 postscaled match occurred

0 = No TMR4 to PR4 match occurred

bit 0 **Unimplemented:** Read as '0'

Note:

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|------------|---------|--------|--------|--------|--------|--------|--------|--------|------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 84               |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    |        | 181    |        |                  |

| PIE1       | TMR1GIE | AD1IE  | RCIE   | TXIE   | SSP1IE | SSP2IE | TMR2IE | TMR1IE | 85               |

| PIE2       | 1       | AD2IE  | _      | 1      | BCL1IE | BCL2IE | TMR4IE | 1      | 86               |

| PIR1       | TMR1GIF | AD1IF  | RCIF   | TXIF   | SSP1IF | SSP2IF | TMR2IF | TMR1IF | 87               |

| PIR2       | _       | AD2IF  | _      | 1      | BCL1IF | BCL2IF | TMR4IF | _      | 88               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

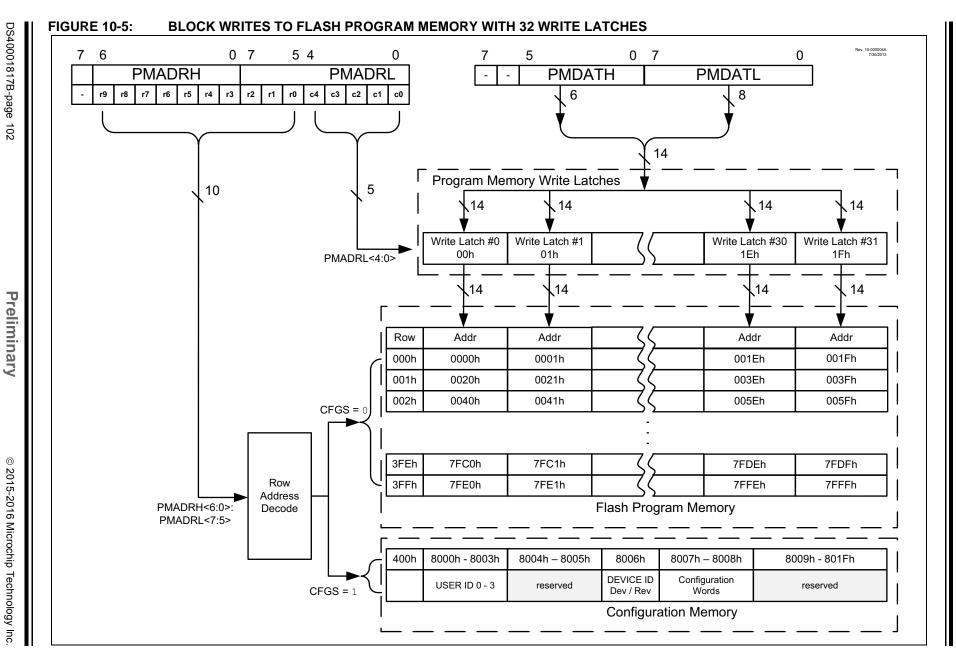

### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|------------|---------|---------|---------|---------|---------|---------|

|         | PMADR<7:0> |         |         |         |         |         |         |

| bit 7   |            |         |         |         |         | bit 0   |         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PMADR<7:0>**: Specifies the Least Significant bits for program memory address

### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| _     |         |         |         | PMADR<14:8 | >       |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **Unimplemented:** Read as '1'

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

### 11.9 PORTD Registers

### 11.9.1 DATA REGISTER

PORTD is a 8-bit wide, bidirectional port, for PIC16LF1567 only. The corresponding data direction register is TRISD (Register 11-12). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., disable the output driver). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTD register (Register 11-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATD).

### 11.9.2 DIRECTION CONTROL

The TRISD register (Register 11-12) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.9.3 ANALOG CONTROL

The ANSELD register (Register 11-18) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note:

The ANSELD bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSELx bits must be initialized to '0' by user software.

# 11.9.4 PORTD FUNCTIONS AND OUTPUT PRIORITIES

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-8.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the output priority list. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the output priority list.

**TABLE 11-10: PORTD OUTPUT PRIORITY**

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RD0      | RD0                              |

| RD1      | RD1                              |

| RD2      | RD2                              |

| RD3      | RD3                              |

| RD4      | RD4                              |

| RD5      | RD5                              |

| RD6      | RD6                              |

| RD7      | RD7                              |

Note 1: Priority listed from highest to lowest.

## 11.10 Register Definitions: PORTD

## REGISTER 11-15: PORTD<sup>(1)</sup>: PORTD REGISTER

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| RD7         | RD6     | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     |

| bit 7 bit 0 |         |         |         |         |         |         |         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RD<7:0>: PORTD General Purpose I/O Pin bits

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

Note 1: Functions not available on PIC16LF1566.

## REGISTER 11-16: TRISD<sup>(1)</sup>: PORTD TRI-STATE REGISTER

| TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| bit 7  | TRISDO | TRISDS | TRISD4 | IKISDS | TRISDZ | IKISDI | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISD<7:0>: PORTD Tri-State Control bits

1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

Note 1: Functions not available on PIC16LF1566.

### REGISTER 15-6: ADXRESxL: ADC RESULT REGISTER LOW (ADXRESxL) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<1:0> |         | _       |         | _       | _       | _       | _       |

| bit 7      |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 ADRES<1:0>: ADC Result Register bits

Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

## REGISTER 15-7: ADXRESXH: ADC RESULT REGISTER HIGH (ADXRESXH) ADFM = 1

| R/W-x/u    | R/W-x/u |

|---------|---------|---------|---------|---------|---------|------------|---------|

| _       | _       | _       | _       | _       | _       | ADRES<9:8> |         |

| bit 7   |         |         |         |         |         |            | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-2 **Reserved**: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits

Upper two bits of 10-bit conversion result

### REGISTER 15-8: ADXRESxL: ADC RESULT REGISTER LOW (ADXRESxL) ADFM = 1

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|------------|---------|---------|---------|---------|---------|---------|

|         | ADRES<7:0> |         |         |         |         |         |         |

| bit 7   |            |         |         |         |         | bit 0   |         |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 **ADRES<7:0>**: ADC Result Register bits Lower eight bits of 10-bit conversion result

### REGISTER 16-13: ADCTX: COMMON ADC TX CONTROL REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----|---------|---------|---------|

| _     | A2TX2   | A2TX1   | A2TX0   |     | A1TX2   | A1TX1   | A1TX0   |

| bit 7 |         |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **Unimplemented:** Read as '0'

bit 6-4 A2TXx: ADC 2 TX CH x Output Enable. Only valid if A1TXx is not enabled (A1TXx has priority).

1 = TX function on channel x enabled (ANx) 0 = TX function on channel x disabled (ANx)

bit 3 **Unimplemented:** Read as '0'

bit 2-0 A1TXx: ADC 1 TX CH x Output Enable

1 = TX function on channel x enabled (ANx) 0 = TX function on channel x disabled (ANx)

#### REGISTER 16-14: AD1TX0: ADC 1 TX CONTROL REGISTER 0

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TX17    | TX16    | TX15    | TX14    | TX13    | TX12    | TX11    | TX10    |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **TXx:** ADC 1 TX CH x Output Enable

1 = TX function on channel x enabled (ANx)

0 = TX function on channel x disabled (ANx)

### REGISTER 16-15: AD1TX1: ADC 1 TX CONTROL REGISTER 1

|   | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0 | R/W-0/0 |

|---|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------|---------|

|   | TX35 <sup>(1)</sup> | TX34 <sup>(1)</sup> | TX33 <sup>(1)</sup> | TX32 <sup>(1)</sup> | TX31 <sup>(1)</sup> | TX30 <sup>(1)</sup> | TX19    | TX18    |

| b | it 7                |                     |                     |                     |                     |                     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **TXx:** ADC 1 TX CH x Output Enable

1 = TX function on channel x enabled (ANx)

0 = TX function on channel x disabled (ANx)

Note 1: PIC16LF1567 only.

# 17.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION REG register.

**Note:** The Watchdog Timer (WDT) uses its own independent prescaler.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

#### 17.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

**Note:** The Timer0 interrupt cannot wake the processor from Sleep since the timer is frozen during Sleep.

# 17.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 25.0 "Electrical Specifications"**.

### 17.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

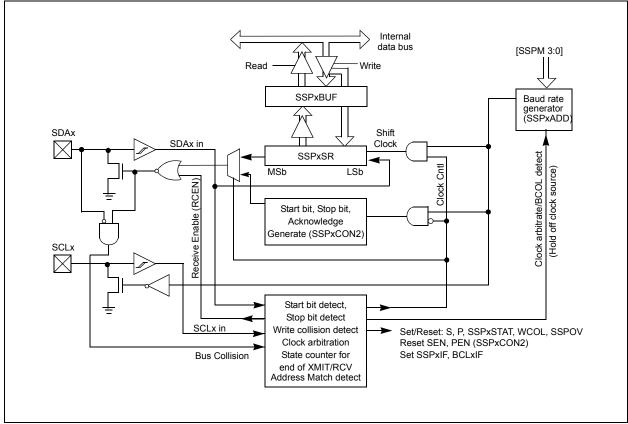

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- · Slave mode

- · Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- · Clock stretching

- · Bus collision detection

- · General call address matching

- · Address masking

- · Address Hold and Data Hold modes

- · Selectable SDAx hold times

Figure 20-2 is a block diagram of the I<sup>2</sup>C Interface module in Master mode. Figure 20-3 is a diagram of the I<sup>2</sup>C interface module in Slave mode.

The PIC12LF1552 has two MSSP modules, MSSP1 and MSSP2, each module operating independently from the other.

- Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSP1CON1 and SSP1CON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

- 2: Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

FIGURE 20-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

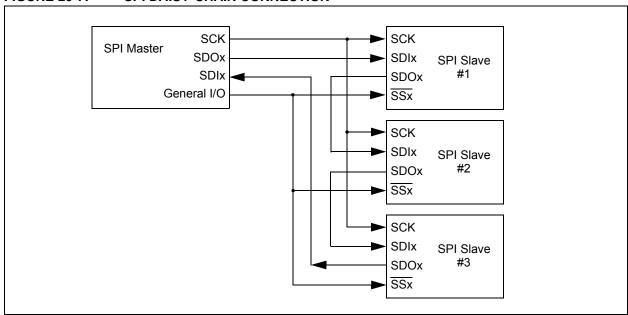

FIGURE 20-7: SPI DAISY-CHAIN CONNECTION

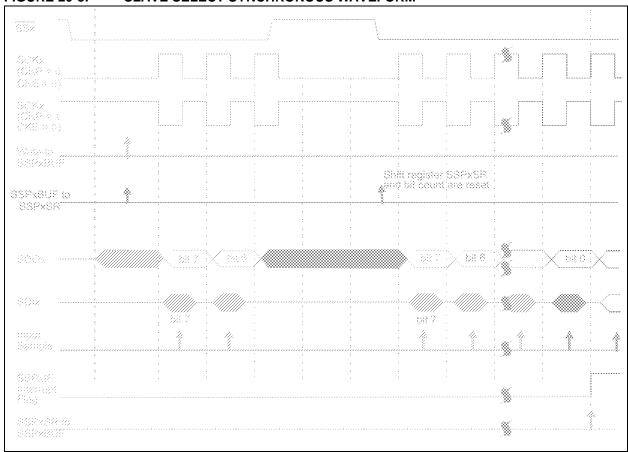

## FIGURE 20-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

## 20.6 I<sup>2</sup>C MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDAx and SCLx lines.

The following events will cause the SSPx Interrupt Flag bit, SSPxIF, to be set (SSPx interrupt, if enabled):

- · Start condition detected

- · Stop condition detected

- · Data transfer byte transmitted/received

- · Acknowledge transmitted/received

- · Repeated Start generated

- Note 1: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: Master mode suspends Start/Stop detection when sending the Start/Stop condition by means of the SEN/PEN control bits. The SSPIF bit is set at the end of the Start/Stop generation when hardware clears the control bit.

### 20.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCLx. See **Section 20.7 "Baud Rate Generator"** for more detail.

| CALL             | Call Subroutine                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                  |

| Operation:       | $ \begin{array}{l} (PC)+\ 1\rightarrow TOS, \\ k\rightarrow PC<10:0>, \\ (PCLATH<6:3>)\rightarrow PC<14:11> \end{array} $                                                                                             |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Call Subroutine. First, return address (PC + 1) is pushed onto the stack. The 11-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a 2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CLRWDT                                                                                                                                                                                                                         |

| Operands:        | None                                                                                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT} \\ \text{0} \rightarrow \underline{\text{WDT}} \text{ prescaler,} \\ \text{1} \rightarrow \overline{\underline{\text{TO}}} \\ \text{1} \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                                                   |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set.                                                                            |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |