#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 23x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1566-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER                                                  | 3-2.0303                                                                                                                               | TAL USCILL                                                                                                                                   | AIUR SIAI | 03 KEGI31       | EK .             |                  |              |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|------------------|------------------|--------------|--|--|

| U-0                                                       | R-0/q                                                                                                                                  | U-0                                                                                                                                          | R-0/q     | U-0             | U-0              | R-0/q            | R-0/q        |  |  |

| _                                                         | PLLSR                                                                                                                                  | _                                                                                                                                            | HFIOFR    | _               | _                | LFIOFR           | HFIOFS       |  |  |

| bit 7                                                     | •                                                                                                                                      |                                                                                                                                              |           |                 |                  |                  | bit 0        |  |  |

|                                                           |                                                                                                                                        |                                                                                                                                              |           |                 |                  |                  |              |  |  |

| Legend:                                                   |                                                                                                                                        |                                                                                                                                              |           |                 |                  |                  |              |  |  |

| R = Readat                                                | ole bit                                                                                                                                | W = Writable                                                                                                                                 | bit       | U = Unimpler    | nented bit, read | l as '0'         |              |  |  |

| u = Bit is ur                                             | nchanged                                                                                                                               | x = Bit is unkr                                                                                                                              | nown      | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is s                                            | et                                                                                                                                     | '0' = Bit is cle                                                                                                                             | ared      | q = Condition   | al               |                  |              |  |  |

|                                                           |                                                                                                                                        |                                                                                                                                              |           |                 |                  |                  |              |  |  |

| bit 7                                                     | Unimplemen                                                                                                                             | ted: Read as '                                                                                                                               | 0'        |                 |                  |                  |              |  |  |

| bit 6                                                     | PLLSR: 4x P                                                                                                                            | ,                                                                                                                                            |           |                 |                  |                  |              |  |  |

|                                                           | 1 = 4x PLL i                                                                                                                           | · · · · <b>,</b>                                                                                                                             |           |                 |                  |                  |              |  |  |

| L:1 F                                                     | 0 = 4x PLL i                                                                                                                           | ,                                                                                                                                            | 01        |                 |                  |                  |              |  |  |

| bit 5                                                     | -                                                                                                                                      | ted: Read as '                                                                                                                               |           |                 |                  |                  |              |  |  |

| bit 4                                                     | 0                                                                                                                                      | h-Frequency Ir                                                                                                                               |           | -               |                  |                  |              |  |  |

|                                                           |                                                                                                                                        | Internal Oscilla<br>Internal Oscilla                                                                                                         |           |                 |                  |                  |              |  |  |

| bit 3-2                                                   |                                                                                                                                        | ited: Read as '                                                                                                                              | -         | o) is not ready |                  |                  |              |  |  |

|                                                           | •                                                                                                                                      |                                                                                                                                              |           | . De este bit   |                  |                  |              |  |  |

| bit 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit |                                                                                                                                        |                                                                                                                                              |           |                 |                  |                  |              |  |  |

|                                                           | <ul> <li>1 = 31 kHz Internal Oscillator (LFINTOSC) is ready</li> <li>0 = 31 kHz Internal Oscillator (LFINTOSC) is not ready</li> </ul> |                                                                                                                                              |           |                 |                  |                  |              |  |  |

| bit 0                                                     |                                                                                                                                        |                                                                                                                                              |           |                 |                  |                  |              |  |  |

|                                                           | 0                                                                                                                                      | 1 7                                                                                                                                          |           |                 |                  |                  |              |  |  |

|                                                           |                                                                                                                                        | <ul> <li>1 = 16 MHz Internal Oscillator (HFINTOSC) is stable</li> <li>0 = 16 MHz Internal Oscillator (HFINTOSC) is not yet stable</li> </ul> |           |                 |                  |                  |              |  |  |

|                                                           |                                                                                                                                        |                                                                                                                                              |           |                 |                  |                  |              |  |  |

## REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5     | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|-------|-----------|--------|-------|-------|--------|--------|---------------------|

| OSCCON  | SPLLEN |       | IRCF<3:0> |        |       |       | SCS    | <1:0>  | 69                  |

| OSCSTAT |        | PLLSR |           | HFIOFR |       |       | LFIOFR | HFIOFS | 70                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3   | Bit 10/2 | Bit 9/1    | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|------------|----------|------------|---------|---------------------|

|         | 13:8 |         | _       | _        | _        | - CLKOUTEN |          | BOREN<1:0> |         | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | 「E<1:0>    | _        | FOSC       | C<1:0>  | 59                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable (GIE) bit is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

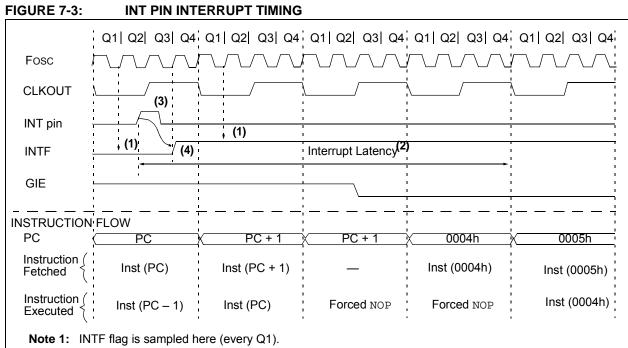

# PIC16LF1566/1567

- 2: Asynchronous interrupt latency = 3-5 TCY. Synchronous latency = 3-4 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- **3:** For minimum width of INT pulse, refer to AC specifications in **Section 25.0 "Electrical Specifica-tions**".

- 4: INTF is enabled to be set any time during the Q4-Q1 cycles.

## 7.6 Register Definitions: Interrupt Control

| REGISTER           | 7-1: INTCO                          | ON: INTERRU                         | JPT CONTR       | OL REGISTE     | R                |                  |                      |

|--------------------|-------------------------------------|-------------------------------------|-----------------|----------------|------------------|------------------|----------------------|

| R/W-0/0            | R/W-0/0                             | R/W-0/0                             | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R-0/0                |

| GIE <sup>(1)</sup> | PEIE <sup>(2)</sup>                 | TMR0IE                              | INTE            | IOCIE          | TMR0IF           | INTF             | IOCIF <sup>(3)</sup> |

| bit 7              |                                     |                                     |                 |                |                  |                  | bit (                |

| Legend:            |                                     |                                     |                 |                |                  |                  |                      |

| R = Readab         | le bit                              | W = Writable                        | bit             | U = Unimpler   | mented bit, read | l as '0'         |                      |

| u = Bit is un      | changed                             | x = Bit is unk                      | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets          |

| '1' = Bit is se    | et                                  | '0' = Bit is cle                    | ared            |                |                  |                  |                      |

|                    |                                     |                                     |                 |                |                  |                  |                      |

| bit 7              |                                     | Interrupt Enable                    |                 |                |                  |                  |                      |

|                    |                                     | all active interr                   | upts            |                |                  |                  |                      |

| hit C              |                                     | all interrupts<br>ieral Interrupt E | nabla hit(2)    |                |                  |                  |                      |

| bit 6              |                                     | all active peripl                   |                 | 5              |                  |                  |                      |

|                    |                                     | all peripheral in                   |                 |                |                  |                  |                      |

| bit 5              | TMROIE: Tin                         | ner0 Overflow I                     | nterrupt Enabl  | e bit          |                  |                  |                      |

|                    |                                     | the Timer0 inte                     |                 |                |                  |                  |                      |

|                    |                                     | the Timer0 inte                     | •               |                |                  |                  |                      |

| bit 4              |                                     | xternal Interrup<br>the INT externa |                 |                |                  |                  |                      |

|                    |                                     | the INT extern                      | •               |                |                  |                  |                      |

| bit 3              | IOCIE: Interr                       | upt-on-Change                       | Enable bit      |                |                  |                  |                      |

|                    |                                     | the interrupt-or                    |                 |                |                  |                  |                      |

|                    |                                     | the interrupt-or                    | -               |                |                  |                  |                      |

| bit 2              |                                     | ner0 Overflow li<br>gister has over |                 | bit            |                  |                  |                      |

|                    |                                     | gister did not o                    |                 |                |                  |                  |                      |

| bit 1              | INTF: INT EX                        | kternal Interrup                    | t Flag bit      |                |                  |                  |                      |

|                    |                                     | external interru                    |                 |                |                  |                  |                      |

|                    |                                     | external interru                    |                 |                |                  |                  |                      |

| bit 0              |                                     | upt-on-Change<br>least one of the   |                 |                | anged state      |                  |                      |

|                    |                                     | the interrupt-on                    | •               | • •            | •                |                  |                      |

|                    | Interrupt flag bits                 |                                     |                 |                |                  |                  |                      |

|                    | enable bit or the appropriate inter | •                                   |                 |                | •                | er soπware sho   | uid ensure th        |

| <b>2</b> .         | Dit DEIE of the IN                  |                                     | r must ha aat t | o onoblo onv n | oriphoral interr | unt              |                      |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

- **2:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

- **3:** The IOCIF flag bit is read-only and cleared when all the interrupt-on-change flags in the IOCxF registers have been cleared by software.

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|---------|---------|---------|---------------------|

| ANSELA     | ANSA7  | ANSA6  | ANSA5  | ANSA4  | ANSA3  | ANSA2   | ANSA1   | ANSA0   | 116                 |

| APFCON     |        | _      | SSSEL  |        |        | _       | GRDBSEL | GRDASEL | 113                 |

| LATA       | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2   | LATA1   | LATA0   | 116                 |

| OPTION_REG | WPUEN  | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |         |         | 181                 |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2     | RA1     | RA0     | 115                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1  | TRISA0  | 115                 |

TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         |         |          |          | CLKOUTEN | BORE     | N<1:0>  |         | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WD.      | TE<1:0>  | _        | FOS     | C<2:0>  | 59                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

### 11.5 PORTB Registers (PIC16LF1567 Only)

### 11.5.1 DATA REGISTER

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-7). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-6) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

### 11.5.2 DIRECTION CONTROL

The TRISB register (Register 11-7) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 11.5.3 ANALOG CONTROL

The ANSELB register (Register 11-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSELx bits        |

|       | must be initialized to '0' by user software. |

### 11.5.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below in Table 11-5.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RB0      | INT<br>PWM20<br>RB0              |

| RB1      | PWM21<br>RB1                     |

| RB2      | PWM22<br>RB2                     |

| RB3      | PWM23<br>RB3                     |

| RB4      | ADxGRDA<br>RB4                   |

| RB5      | ADxGRDA<br>RB5                   |

| RB6      | ICSPCLK<br>ADxGRDB<br>RB6        |

| RB7      | ICSPDAT<br>ADxGRDB<br>RB7        |

### TABLE 11-5: PORTB OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

## **15.1 ADC Configuration**

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

### 15.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRISx and ANSELx bits. Refer to **Section 11.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 15.1.2 CHANNEL SELECTION

There are 24 channel selections available for PIC16LF1566 and 35 for PIC16LF1567. Three channels (AN0, AN1 and AN2) can be selected by both ADC1 and ADC2. The following channels can be selected by either of the ADCs:

- AN<2:0> pins

- Temperature Indicator

- FVR Buffer 1

- VREFH

The CHS bits of the ADxCON0 register determine which channel is connected to the sample and hold circuit of ADCx.

When changing channels, a delay (TACQ) is required before starting the next conversion. Refer to **Section 15.2.6 "Individual ADC Conversion Procedure"** for more information.

### 15.1.3 ADC VOLTAGE REFERENCE

The ADC module uses a positive and a negative voltage reference. The positive reference is labeled VREFH and the negative reference is labeled VREFL.

The positive voltage reference (VREFH) is selected by the ADPREF bits in the ADCON1 register. The positive voltage reference source can be:

- VREF+ pin

- Vdd

- The negative voltage reference (VREFL) source is:

- Vss

### 15.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (internal RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 15-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 25.0 "Electrical Specifications"** for more information. Table 15-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

| REGISTER 1       | 6-8: AADX      | CON3: HARL                          | WARE CVD         | CONTROL            | REGISTER 3        |                  |                |

|------------------|----------------|-------------------------------------|------------------|--------------------|-------------------|------------------|----------------|

| R/W-0/0          | R/W-0/0        | U-0                                 | U-0              | U-0                | U-0               | R/W-0/0          | R/W-0/0        |

| ADxEPPOL         | ADxIPPOL       | —                                   | _                | _                  |                   | ADxIPEN          | ADxDSEN        |

| bit 7            |                |                                     |                  | ÷                  |                   |                  | bit 0          |

|                  |                |                                     |                  |                    |                   |                  |                |

| Legend:          |                |                                     |                  |                    |                   |                  |                |

| R = Readable     | bit            | W = Writable                        | bit              | U = Unimpler       | mented bit, read  | d as '0'         |                |

| u = Bit is unch  | nanged         | x = Bit is unkr                     | nown             | -n/n = Value a     | at POR and BC     | R/Value at all   | other Resets   |

| '1' = Bit is set |                | '0' = Bit is cle                    | ared             |                    |                   |                  |                |

|                  |                |                                     |                  |                    |                   |                  |                |

| bit 7            | ADxEPPOL:      | External Prech                      | arge Polarity b  | oit <sup>(1)</sup> |                   |                  |                |

|                  | 1 = Selected   | l channel is cor                    | nected to VDD    | olo during prech   | narge time        |                  |                |

|                  | 0 = Selected   | I channel is cor                    | nected to Vss    | during precha      | rge time          |                  |                |

| bit 6            | ADxIPPOL:      | Internal Precha                     | rge Polarity bit | <sub>t</sub> (1)   |                   |                  |                |

|                  |                | s shorted to VR                     |                  |                    |                   |                  |                |

|                  | 0 = CHOLD is   | s shorted to VR                     | EFL during pred  | charge time        |                   |                  |                |

| bit 5-2          | Unimplemer     | nted: Read as '                     | 0'               |                    |                   |                  |                |

| bit 1            | ADxIPEN: A     | DC Invert Polar                     | ity Enable bit   |                    |                   |                  |                |

|                  | If ADxDSEN     |                                     |                  |                    |                   |                  |                |

|                  |                | ut value of the A<br>econd conversi |                  | DxIPPOL, and C     | GRDxPOL bits (    | used by the AD   | C are inverted |

|                  |                | and ADC conversion                  |                  | s like the first   |                   |                  |                |

|                  | If ADxDSEN     |                                     |                  |                    |                   |                  |                |

|                  | This bit has r | no effect.                          |                  |                    |                   |                  |                |

| bit 0            | ADxDSEN: A     | ADC Double Sa                       | mple Enable b    | bit                |                   |                  |                |

|                  |                | <u>C i</u> mmediately s             |                  |                    |                   | onversion.       |                |

|                  |                | NEx bit is not au                   |                  |                    |                   |                  |                |

|                  |                | erates in the tra                   | uluonal, single  | e conversion mo    | oue               |                  |                |

|                  |                | EN = 1 and A                        |                  |                    | is output is inve | erted for the se | econd          |

| cor              | nversion time. | The stored bit v                    | alue does not    | change.            |                   |                  |                |

## REGISTER 16-8: AADxCON3: HARDWARE CVD CONTROL REGISTER 3

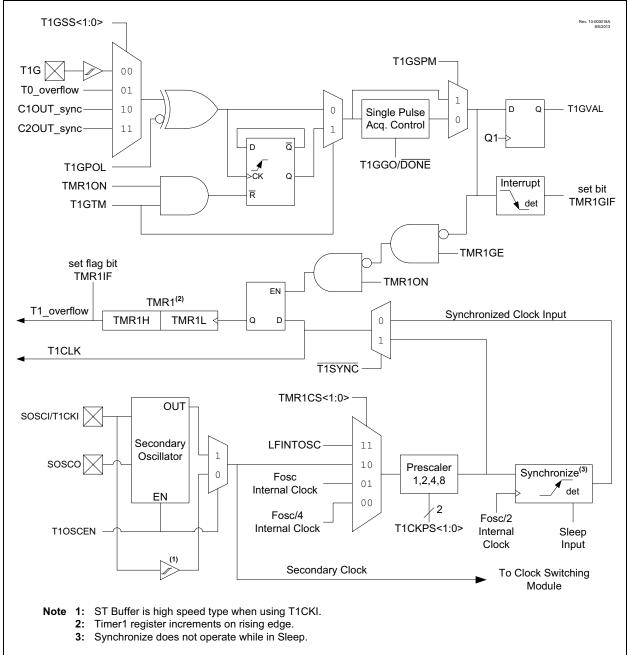

## 18.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- Gate Value Status

- · Gate Event Interrupt

Figure 18-1 is a block diagram of the Timer1 module.

## FIGURE 18-1: TIMER1 BLOCK DIAGRAM

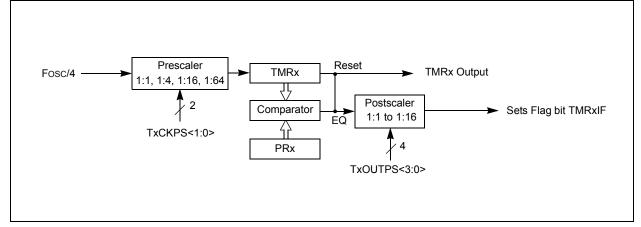

## 19.0 TIMER2/4 MODULES

There are up to five identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2 and Timer4 (also Timer2/4).

| Note: | The 'x' variable used in this section is |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | used to designate Timer2 or Timer4. For  |  |  |  |  |  |

|       | example, TxCON references T2CON or       |  |  |  |  |  |

|       | T4CON. PRx references PR2 or PR4.        |  |  |  |  |  |

The Timer2/4 modules incorporate the following features:

- 8-bit Timer and Period registers (TMR2/4 and PR2/4, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2/4 match with PR2/4, respectively

- Optional use as the shift clock for the MSSPx modules (Timer2 only)

See Figure 19-1 for a block diagram of Timer2/4.

#### 20.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSPx clock is much faster than the system clock.

In Slave mode, when MSSPx interrupts are enabled, after the master completes sending data, an MSSPx interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSPx interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSPx interrupt flag bit will be set and if enabled, will wake the device.

| Name     | Bit 7     | Bit 6           | Bit 5         | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-----------|-----------------|---------------|--------|--------|--------|--------|--------|---------------------|

| INTCON   | GIE       | PEIE            | TMR0IE        | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 84                  |

| PIE1     | TMR1GIE   | ADIE            | RCIE          | TXIE   | SSP1IE | SSP2IE | TMR2IE | TMR1IE | 85                  |

| PIR1     | TMR1GIF   | AD1IF           | RCIF          | TXIF   | SSP1IF | SSP2IF | TMR2IF | TMR1IF | 87                  |

| SSP1BUF  | MSSPx Rec | eive Buffer/Tra | ansmit Regist | er     |        |        |        |        | 201*                |

| SSP2BUF  | MSSPx Rec | eive Buffer/Tra | ansmit Regist | er     |        |        |        |        | 201*                |

| SSP1CON1 | WCOL      | SSPOV           | SSPEN         | CKP    |        | SSPM   | <3:0>  |        | 248                 |

| SSP2CON1 | WCOL      | SSPOV           | SSPEN         | CKP    |        | SSPM   | <3:0>  |        | 248                 |

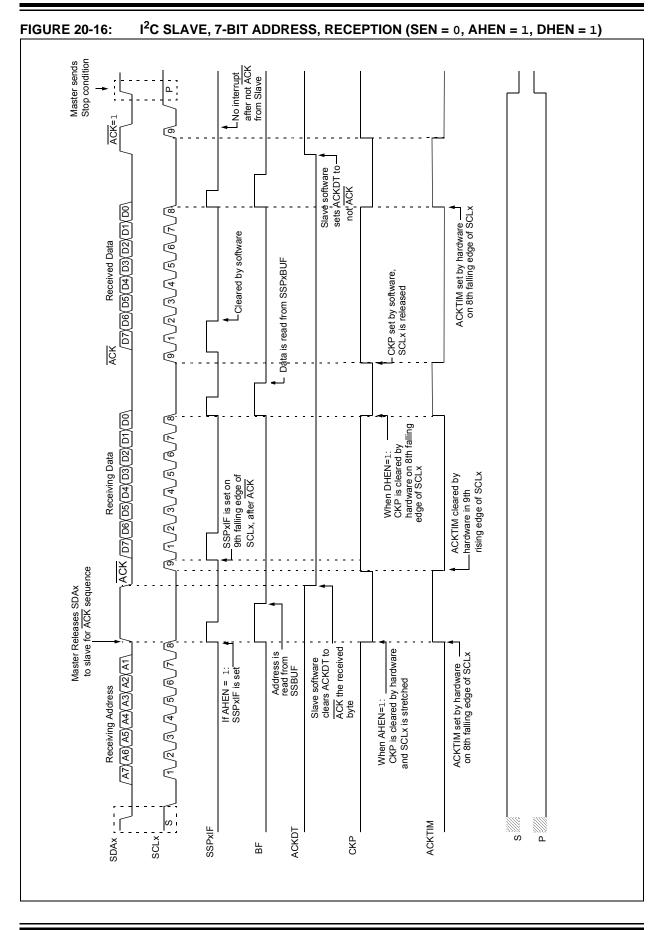

| SSP1CON3 | ACKTIM    | PCIE            | SCIE          | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN   | 251                 |

| SSP2CON3 | ACKTIM    | PCIE            | SCIE          | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN   | 251                 |

| SSP1STAT | SMP       | CKE             | D/A           | Р      | S      | R/W    | UA     | BF     | 246                 |

| SSP2STAT | SMP       | CKE             | D/A           | Р      | S      | R/W    | UA     | BF     | 246                 |

| TRISC    | TRISC7    | TRISC6          | TRISC5        | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 123                 |

| TRISD    | TRISD7    | TRISD6          | TRISD5        | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 126                 |

### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx in SPI mode.

\* Page provides register information.

## PIC16LF1566/1567

# PIC16LF1566/1567

© 2015-2016 Microchip Technology Inc.

|                   |                               |        |        | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-------------------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON           | ABDOVF                        | RCIDL  |        | SCKP   | BRG16  | _      | WUE    | ABDEN  | 266                 |

| INTCON            | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 84                  |

| PIE1 1            | TMR1GIE                       | AD1IE  | RCIE   | TXIE   | SSP1IE | SSP2IE | TMR2IE | TMR1IE | 85                  |

| PIR1 <sup>1</sup> | TMR1GIF                       | AD1IF  | RCIF   | TXIF   | SSP1IF | SSP2IF | TMR2IF | TMR1IF | 87                  |

| RCSTA             | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 265                 |

| SPBRGL            |                               |        |        | BRG    | <7:0>  |        |        |        | 267*                |

| SPBRGH            |                               |        |        | BRG<   | :15:8> |        |        |        | 267*                |

| TRISB             | TRISB7                        | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 119                 |

| TXREG             | EUSART Transmit Data Register |        |        |        |        |        |        |        |                     |

| TXSTA             | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 264                 |

### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission.

\* Page provides register information.

### 21.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSELx bit must be       |

|       | cleared for the receiver to function.      |

### 21.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| If the device is configured as a slave and  |            |                                              |                                                   |                                                                |  |  |  |  |  |

|---------------------------------------------|------------|----------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|

| the TX/CK function is on an analog pin, the |            |                                              |                                                   |                                                                |  |  |  |  |  |

| 1 0                                         | ANSELx     | bit                                          | must                                              | be                                                             |  |  |  |  |  |

|                                             | TX/CK func | TX/CK function is on ar<br>responding ANSELx | TX/CK function is on an ana responding ANSELx bit | TX/CK function is on an analog pin, responding ANSELx bit must |  |  |  |  |  |

### 21.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

### 21.5.1.8 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

## 21.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH:SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

### 22.1 **PWMx** Pin Configuration

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRISx bits.

Note: Clearing the PWMxOE bit will relinquish control of the PWMx pin.

### 22.1.1 FUNDAMENTAL OPERATION

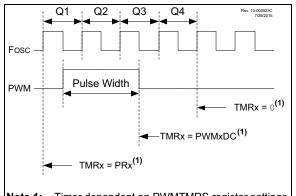

The PWM module produces a 10-bit resolution output. PWMTMRS selects TMRx and PRx which set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

| Note: | The Timer2/4 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

|       | update rate at a different frequency than                                                                                   |

|       | the PWM output.                                                                                                             |

All PWM outputs associated with Timer2/4 are set when TMRx is cleared. Each PWMx is cleared when TMRx is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PRx, the PWM output is never cleared (100% duty cycle).

| Note: | The PWMxDCH and PWMxDCL registers        |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | are double buffered. The buffers are     |  |  |  |  |  |  |

|       | updated when TMRx matches PRx. Care      |  |  |  |  |  |  |

|       | should be taken to update both registers |  |  |  |  |  |  |

|       | before the timer match occurs.           |  |  |  |  |  |  |

### 22.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

### 22.1.3 PWM PERIOD

The PWM period is specified by the PRx register of the timer selected by PWMTMRS. The PWM period can be calculated using the formula of Equation 22-1.

### EQUATION 22-1: PWM PERIOD

$PWM Period = [(PRx) + 1]^{2} 4^{2} TOSC^{2}$ (TMRx Prescale Value)

Note: Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

- TMRx is cleared

- The PWM output is active (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2/4 postscaler has no effect on |

|-------|------------------------------------------|

|       | the PWM operation.                       |

### 22.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 22-2 is used to calculate the PWM pulse width.

Equation 22-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 22-2: PULSE WIDTH

$Pulse Width = (PWMxDCH:PWMxDCL<7:6>) \bullet$

TOSC • (TMRx Prescale Value)

Note: Tosc = 1/Fosc

## EQUATION 22-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PRx+1)}$$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/Fosc, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

Figure 22-2 shows a waveform of the PWM signal when the duty cycle is set for the smallest possible pulse.

### FIGURE 22-2: PWM OUTPUT

Note 1: Timer dependent on PWMTMRS register settings.

# PIC16LF1566/1567

| Mnen     | nonic, | Description                                   | Cualaa |     | 14-Bit | Status | Notes |          |       |

|----------|--------|-----------------------------------------------|--------|-----|--------|--------|-------|----------|-------|

| Operands |        | Description                                   | Cycles | MSb |        |        | LSb   | Affected | Notes |

|          |        | CONTROL OPER/                                 | ATIONS |     |        |        |       |          |       |

| BRA      | k      | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk  |          |       |

| BRW      | -      | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011  |          |       |

| CALL     | k      | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk  |          |       |

| CALLW    | -      | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010  |          |       |

| GOTO     | k      | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk  |          |       |

| RETFIE   | -      | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001  |          |       |

| RETLW    | k      | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk  |          |       |

| RETURN   | -      | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000  |          |       |

|          |        | INHERENT OPER                                 | ATIONS |     |        |        |       |          |       |

| CLRWDT   | -      | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100  | TO, PD   |       |

| NOP      | -      | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000  |          |       |

| OPTION   | -      | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010  |          |       |

| RESET    | _      | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001  |          |       |

| SLEEP    | -      | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011  | TO, PD   |       |

| TRIS     | f      | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf  |          |       |

|          |        | C-COMPILER OPT                                | IMIZED |     |        |        |       |          |       |

| ADDFSR   | n, k   | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk  |          |       |

| MOVIW    | n mm   | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm  | Z        | 2, 3  |

|          |        | modifier, mm                                  |        |     |        |        | kkkk  |          |       |

|          | k[n]   | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | 1nmm  | Z        | 2     |

| MOVWI    | n mm   | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | kkkk  |          | 2, 3  |

|          |        | modifier, mm                                  |        |     |        |        |       |          |       |

|          | k[n]   | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   |       |          | 2     |

### TABLE 24-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See Table in the MOVIW and MOVWI instruction descriptions.

### TABLE 25-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                         |      |       |      |       |                             |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------|------|-------|------|-------|-----------------------------|--|--|--|

| Param.<br>No.                                                                                                            | Sym. | Characteristic                          | Min. | Тур.† | Max. | Units | Conditions                  |  |  |  |

| OS01                                                                                                                     | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | _     | 0.5  | MHz   | EC Oscillator mode (low)    |  |  |  |

|                                                                                                                          |      |                                         | DC   | —     | 4    | MHz   | EC Oscillator mode (medium) |  |  |  |

|                                                                                                                          |      |                                         | DC   | —     | 20   | MHz   | EC Oscillator mode (high)   |  |  |  |

| OS02                                                                                                                     | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | —     | 8    | ns    | EC mode                     |  |  |  |

| OS03                                                                                                                     | Тсү  | Instruction Cycle Time <sup>(1)</sup>   | 200  | _     | DC   | ns    | Tcy = Fosc/4                |  |  |  |

| 0303                                                                                                                     | _    | narameters are characterized h          |      |       | DC   | 115   | 101 - 1030/4                |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

### TABLE 25-8:OSCILLATOR PARAMETERS

|               | Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                       |      |       |      |       |                                                             |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-------|------|-------|-------------------------------------------------------------|--|--|--|--|

| Param.<br>No. | Sym.                                                                                                                     | Characteristic                                        | Min. | Тур.† | Max. | Units | Conditions                                                  |  |  |  |  |

| OS08          | HFosc                                                                                                                    | Internal Calibrated HFINTOSC Frequency <sup>(1)</sup> | —    | 16.0  |      | MHz   | $0^{\circ}C \le TA \le +85^{\circ}C$                        |  |  |  |  |

| OS08A         | HFTOL                                                                                                                    | Frequency Tolerance                                   | —    | ±3    | —    | %     | 25°C, 16 MHz                                                |  |  |  |  |

|               |                                                                                                                          |                                                       | —    | ±6    | _    | %     | $0^{\circ}C \leq TA \leq \textbf{+85}^{\circ}C, \ 16 \ MHz$ |  |  |  |  |

| OS09          | LFosc                                                                                                                    | Internal LFINTOSC Frequency                           | —    | 31    | _    | kHz   | $-40^\circ C \le T A \le +125^\circ C$                      |  |  |  |  |

| 0010*         | TAMODA                                                                                                                   | HFINTOSC<br>Wake-up from Sleep Start-up Time          | —    | 5     | 15   | μS    |                                                             |  |  |  |  |

| OS10*         | Twarm                                                                                                                    | LFINTOSC<br>Wake-up from Sleep Start-up Time          | —    | 0.5   | —    | ms    |                                                             |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

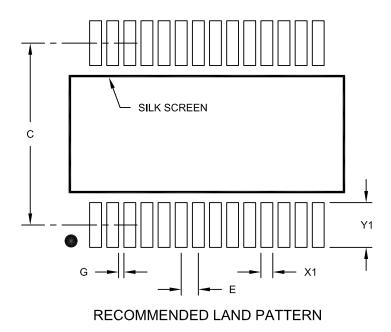

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |      | MILLIMETERS |      |  |

|--------------------------|-------|------|-------------|------|--|

| Dimension Limits         |       | MIN  | NOM         | MAX  |  |

| Contact Pitch            | E     |      | 0.65 BSC    |      |  |

| Contact Pad Spacing      | С     |      | 7.20        |      |  |

| Contact Pad Width (X28)  | X1    |      |             | 0.45 |  |

| Contact Pad Length (X28) | Y1    |      |             | 1.75 |  |

| Distance Between Pads    | G     | 0.20 |             |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

## THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support