Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 34x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1567-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr. | Name                  | Bit 7        | Bit 6           | Bit 5           | Bit 4           | Bit 3          | Bit 2        | Bit 1           | Bit 0        | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|-----------------------|--------------|-----------------|-----------------|-----------------|----------------|--------------|-----------------|--------------|-----------------------|---------------------------------|

| Bank  |                       | -            |                 |                 |                 |                |              |                 |              | •                     |                                 |

| 280h  | INDF0 <sup>(1)</sup>  | Addressing t | his location us | ses contents of | f FSR0H/FSR     | OL to addres   | s data memor | y (not a physic | al register) | XXXX XXXX             | uuuu uuuu                       |

| 281h  | INDF1 <sup>(1)</sup>  | Addressing t | his location us |                 |                 |                |              | y (not a physic | al register) | XXXX XXXX             | uuuu uuuu                       |

| 282h  | PCL <sup>(1)</sup>    |              | -               | Program C       | Counter (PC)    | Least Signific | ant Byte     | -               |              | 0000 0000             | 0000 0000                       |

| 283h  | STATUS <sup>(1)</sup> | _            | —               | —               | TO              | PD             | Z            | DC              | С            | 1 1000                | q quuu                          |

| 284h  | FSR0L <sup>(1)</sup>  |              |                 | Indirect Da     | ata Memory A    | ddress 0 Lov   | v Pointer    |                 |              | 0000 0000             | uuuu uuuu                       |

| 285h  | FSR0H <sup>(1)</sup>  |              |                 | Indirect Da     | ata Memory A    | ddress 0 Hig   | h Pointer    |                 |              | 0000 0000             | 0000 0000                       |

| 286h  | FSR1L <sup>(1)</sup>  |              |                 | Indirect Da     | ata Memory A    | ddress 1 Lov   | v Pointer    |                 |              | 0000 0000             | uuuu uuuu                       |

| 287h  | FSR1H <sup>(1)</sup>  |              |                 | Indirect Da     | ata Memory A    | ddress 1 Hig   | h Pointer    |                 |              | 0000 0000             | 0000 0000                       |

| 288h  | BSR <sup>(1)</sup>    | _            | _               | _               |                 |                | BSR<4:0>     |                 |              | 0 0000                | 0 0000                          |

| 289h  | WREG <sup>(1)</sup>   |              |                 |                 | Working F       | Register       |              |                 |              | 0000 0000             | uuuu uuuu                       |

| 28Ah  | PCLATH <sup>(1)</sup> | —            |                 | Write B         | uffer for the u | oper 7 bits of | the Program  | Counter         |              | -000 0000             | -000 0000                       |

| 28Bh  | INTCON <sup>(1)</sup> | GIE          | PEIE            | TMR0IE          | INTE            | IOCIE          | TMR0IF       | INTF            | IOCIF        | 0000 0000             | 0000 0000                       |

| 28Ch  | _                     |              | •               | •               | Unimpler        | nented         | •            | •               | •            | _                     | _                               |

| 28Dh  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 28Eh  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 28Fh  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 290h  | _                     |              |                 |                 | Unimpler        | mented         |              |                 |              | _                     | _                               |

| 291h  | _                     |              |                 |                 | Unimpler        | mented         |              |                 |              | _                     | _                               |

| 292h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 293h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 294h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 295h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 296h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 297h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 298h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 299h  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 29Ah  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | _                               |

| 29Bh  | —                     |              |                 |                 | Unimpler        | mented         |              |                 |              | _                     | —                               |

| 29Ch  | —                     |              |                 |                 | Unimpler        | mented         |              |                 |              | _                     | —                               |

| 29Dh  | —                     |              |                 |                 | Unimpler        | mented         |              |                 |              | _                     | —                               |

| 29Eh  | _                     |              |                 |                 | Unimpler        | nented         |              |                 |              | _                     | —                               |

| 29Fh  | —                     | l l          |                 |                 | Unimpler        | mented         |              |                 |              | _                     | _                               |

### TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.Note1:These registers can be accessed from any bank.

2: PIC16LF1567.

3: These registers/bits are available at two address locations, in Bank 1 and Bank 14.

4: PIC16LF1566 only.

5: Unimplemented, read as '1'.

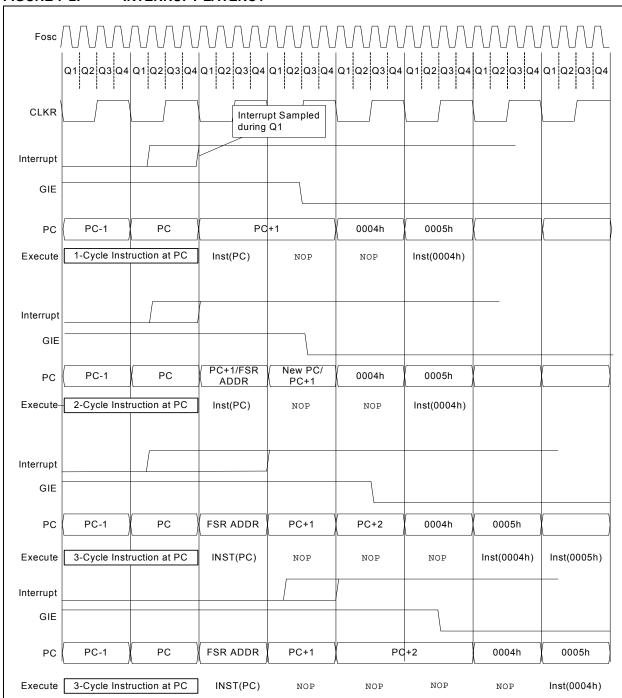

### 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

FIGURE 7-2: INTERRUPT LATENCY

### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0      | R/W-0/0 | R/W-0/0        | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|--------------|---------|----------------|---------|--------------|------------------|---------|---------|

|              |         |                | PMAD    | R<7:0>       |                  |         |         |

| bit 7        |         |                |         |              |                  |         | bit 0   |

|              |         |                |         |              |                  |         |         |

| Legend:      |         |                |         |              |                  |         |         |

|              |         |                |         |              |                  |         |         |

| R = Readable | bit     | W = Writable I | bit     | U = Unimplem | nented bit, read | as '0'  |         |

bit 7-0 **PMADR<7:0>**: Specifies the Least Significant bits for program memory address

'0' = Bit is cleared

### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| —     |         |         |         | PMADR<14:8 | }>      |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

'1' = Bit is set

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

| REGISTE       | R 10-5: PMC                      | ON1: PROGR                            | AM MEMOR        | Y CONTROL       | . 1 REGISTE      | र                |                 |

|---------------|----------------------------------|---------------------------------------|-----------------|-----------------|------------------|------------------|-----------------|

| U-1           | R/W-0/0                          | R/W-0/0                               | R/W/HC-0/0      | R/W/HC-x/q      | R/W-0/0          | R/S/HC-0/0       | R/S/HC-0/0      |

|               | CFGS                             | LWLO                                  | FREE            | WRERR           | WREN             | WR               | RD              |

| bit 7         |                                  |                                       |                 |                 |                  |                  | bit 0           |

| Legend:       |                                  |                                       |                 |                 |                  |                  |                 |

| R = Read      | able bit                         | W = Writable                          | bit             | U = Unimpler    | mented bit, read | d as '0'         |                 |

| S = Bit ca    | n only be set                    | x = Bit is unk                        | nown            | -n/n = Value a  | at POR and BC    | R/Value at all c | ther Resets     |

| '1' = Bit is  | set                              | '0' = Bit is cle                      | ared            | HC = Bit is cl  | eared by hardw   | /are             |                 |

|               |                                  |                                       |                 |                 |                  |                  |                 |

| bit 7         | Unimpleme                        | nted: Read as                         | '1'             |                 |                  |                  |                 |

| bit 6         | CFGS: Con                        | figuration Selec                      | t bit           |                 |                  |                  |                 |

|               |                                  | Configuration,                        |                 | evice ID Regist | ters             |                  |                 |

|               |                                  | Flash program                         | -               |                 |                  |                  |                 |

| bit 5         |                                  | d Write Latches                       |                 |                 |                  |                  | -               |

|               |                                  | e addressed pro<br>dressed progran    |                 |                 |                  |                  |                 |

|               |                                  | tches will be init                    | •               |                 | •                |                  | grammenner      |

| bit 4         | FREE: Prog                       | ram Flash Eras                        | e Enable bit    |                 |                  |                  |                 |

|               | 1 = Perform                      | ns an erase ope                       | ration on the n |                 |                  | cleared upon c   | ompletion)      |

|               |                                  | ns a write opera                      |                 | t WR comman     | ld               |                  |                 |

| bit 3         |                                  | ogram/Erase E                         | •               |                 |                  |                  |                 |

|               |                                  | on indicates an<br>tically on any se  |                 |                 |                  | mpt or termina   | tion (bit is se |

|               |                                  | gram or erase of                      |                 |                 |                  |                  |                 |

| bit 2         | -                                | gram/Erase Ena                        |                 | 5               |                  |                  |                 |

|               | 1 = Allows                       | program/erase                         | cycles          |                 |                  |                  |                 |

|               | 0 = Inhibits                     | programming/e                         | rasing of progr | am Flash        |                  |                  |                 |

| bit 1         | WR: Write C                      |                                       |                 |                 |                  |                  |                 |

|               |                                  | a program Flas<br>eration is self-tir |                 |                 | hardwara anaa    | oporation is as  | malata          |

|               |                                  | R bit can only be                     |                 |                 |                  | operation is co  | inplete.        |

|               |                                  | n/erase operation                     | · ·             | ,               |                  |                  |                 |

| bit 0         | RD: Read C                       | ontrol bit                            |                 |                 |                  |                  |                 |

|               |                                  | a program Flas                        |                 | takes one cycle | e. RD is cleared | d in hardware. 1 | he RD bit car   |

|               |                                  | set (not cleared                      |                 | d               |                  |                  |                 |

| Note 1:       |                                  | ot initiate a prog                    |                 |                 | vation (EDEE -   | - 1)             |                 |

| NULE 1.<br>2. | The LWLO bit is<br>The WRERR bit |                                       |                 |                 |                  |                  | oration is      |

### REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

2: The WRERR bit is automatically set by hardware when a program memory write or erase operation is started (WR = 1).

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

| LATD7            | LATD6   | LATD5             | LATD4   | LATD3          | LATD2            | LATD1            | LATD0        |

| bit 7            |         |                   |         |                |                  | •                | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

### **REGISTER 11-17: LATD<sup>(1)</sup>: PORTD DATA LATCH REGISTER**

### bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(2)</sup>

Note 1: Functions not available on PIC16LF1566.

2: Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

### REGISTER 11-18: ANSELD<sup>(1)</sup>: PORTD ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on pins RD<7:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

Note 1: Functions not available on PIC16LF1566.

2: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name                  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELD <sup>(1)</sup> | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3  | ANSD2  | ANSD1  | ANSD0  | 127                 |

| LATD <sup>(1)</sup>   | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 127                 |

| PORTD <sup>(1)</sup>  | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | 126                 |

| TRISD <sup>(1)</sup>  | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 126                 |

#### TABLE 11-11: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

Note 1: Functions not available on PIC16LF1566.

### 15.2.6 INDIVIDUAL ADC CONVERSION PROCEDURE

This is an example procedure for using the ADCx to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRISx register)

- Configure pin as analog (Refer to the ANSELx register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register)

- 2. Configure the ADCx module:

- Select ADCx conversion clock

- Configure voltage reference

- Select ADCx input channel

- Turn on ADCx module

- 3. Configure ADCx interrupt (optional):

- · Clear ADCx interrupt flag

- · Enable ADCx interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONEx bit.

- 6. Wait for ADCx conversion to complete by one of the following:

- Polling the GO/DONEx bit

- Waiting for the ADCx interrupt (interrupts enabled)

- 7. Read ADCx Result.

- 8. Clear the ADCx interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 15.4 "ADC Acquisition Requirements".

### EXAMPLE 15-1: ADC CONVERSION

;This code block configures the ADC1 ;for polling, Vdd and Vss references, FRC ;oscillator and AN0 input.

;Conversion start and polling for completion ;are included.

| '       |              |                      |

|---------|--------------|----------------------|

| BANKSEL | ADCON1       | ;                    |

| MOVLW   | B'11110000'  | ;Right justify, FRC  |

|         |              | ;oscillator          |

| MOVWF   | ADCON1       | ;VDD is VREFH        |

| BANKSEL | TRISA        | ;                    |

| BSF     | TRISA,0      | ;Set RAO to input    |

| BANKSEL | ANSELA       | ;                    |

| BSF     | ANSELA,0     | ;Set RAO to analog   |

| BANKSEL | WPUA         |                      |

| BCF     | wpua,0       | ;Disable RA0 weak    |

|         |              | pull-up              |

| BANKSEL | ADCON0       | ;                    |

| MOVLW   | B'0000001'   | ;Select channel AN0  |

| MOVWF   | ADCON0       | ;Turn ADC On         |

| MOVLW   | .5           |                      |

| MOVWF   | AAD1ACQ      | ;Acquisiton delay    |

| BSF     | ADCON0, ADGO | ;Start conversion    |

| BTFSC   | ADCON0, ADGO | ;Is conversion done? |

| GOTO    | \$-1         | ;No, test again      |

| BANKSEL | AD1RESOH     | ;                    |

| MOVF    | AD1RESOH,W   | ;Read upper 2 bits   |

| MOVWF   | RESULTHI     | ;store in GPR space  |

| BANKSEL | AD1RESOL     | ;                    |

| MOVF    | AD1RES0L,W   | ;Read lower 8 bits   |

| MOVWF   | RESULTLO     | ;Store in GPR space  |

|         |              |                      |

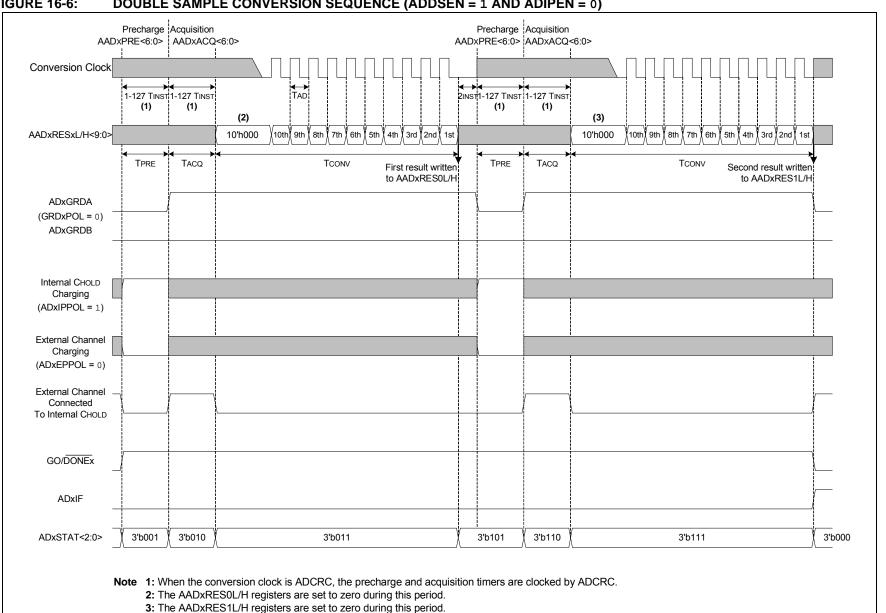

#### **FIGURE 16-6:** DOUBLE SAMPLE CONVERSION SEQUENCE (ADDSEN = 1 AND ADIPEN = 0)

### 18.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 18.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

### 18.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 18-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

### 18.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 18-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 18-6 for timing details.

### 18.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 18.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| FIGURE 18-5:   | TIMER1 GATE SINGLE-PU                  | ULSE MODE                                     |                   |

|----------------|----------------------------------------|-----------------------------------------------|-------------------|

| TMR1GE         |                                        |                                               | _                 |

| T1GPOL         |                                        |                                               | _                 |

| T1GSPM         |                                        |                                               | _                 |

| T1GGO/<br>DONE | Set by software<br>Counting enabled on | Cleared by hardware on falling edge of T1GVAL |                   |

| t1g_in         | rising edge of T1G                     |                                               | _                 |

| т1СКІ          |                                        |                                               | _                 |

| T1GVAL         | T                                      |                                               | -                 |

| Timer1         | N                                      | N + 1 N + 2                                   | -<br>-            |

| TMR1GIF        | — Cleared by software                  | ← Set by hardware on falling edge of T1GVAL   | ared by<br>ftware |

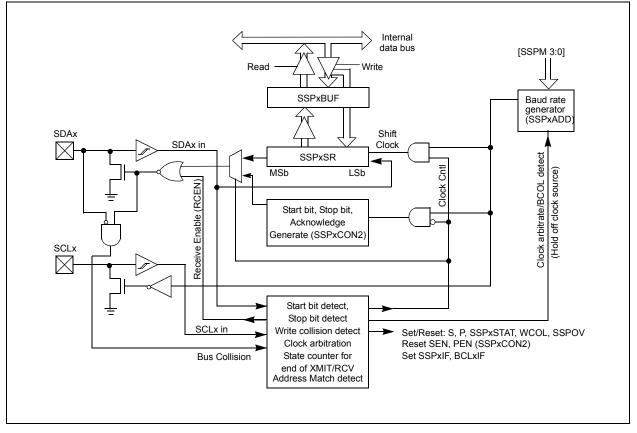

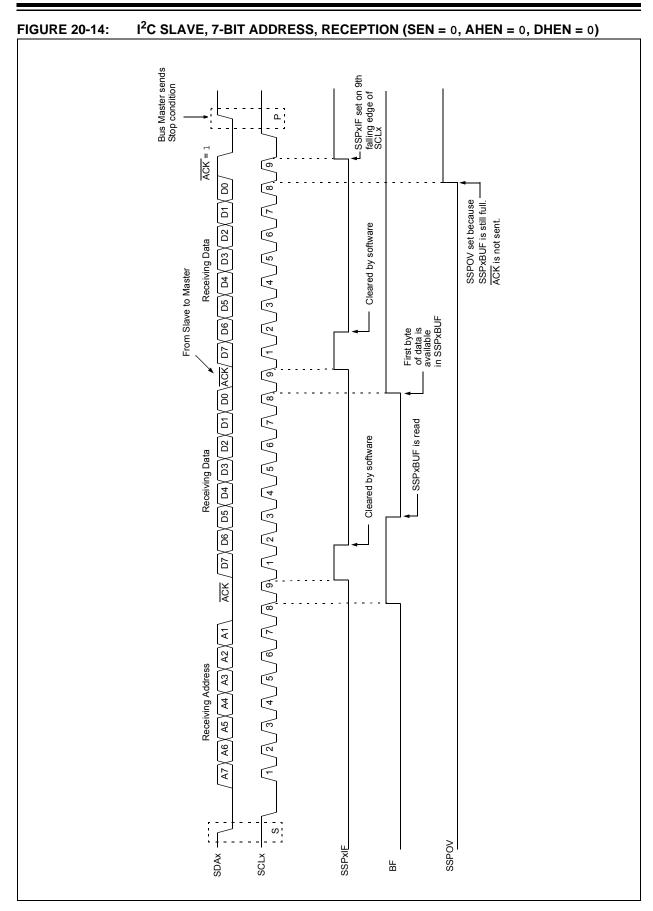

The  $\mathrm{I}^2\mathrm{C}$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- General call address matching

- · Address masking

- · Address Hold and Data Hold modes

- · Selectable SDAx hold times

Figure 20-2 is a block diagram of the  $I^2C$  Interface module in Master mode. Figure 20-3 is a diagram of the  $I^2C$  interface module in Slave mode.

The PIC12LF1552 has two MSSP modules, MSSP1 and MSSP2, each module operating independently from the other.

- Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSP1CON1 and SSP1CON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

- 2: Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

### FIGURE 20-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

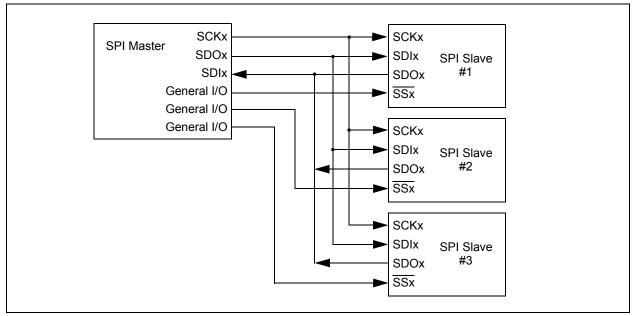

#### 20.2.1 SPI MODE REGISTERS

The MSSPx module has five registers for SPI mode operation. These are:

- MSSPx STATUS register (SSPxSTAT)

- MSSPx Control register 1 (SSPxCON1)

- MSSPx Control register 3 (SSPxCON3)

- MSSPx Data Buffer register (SSPxBUF)

- MSSPx Address register (SSPxADD)

- MSSPx Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 20.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

#### 20.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- · Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSPx Enable bit, SSPEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONx registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDIx must have corresponding TRIS bit set

- SDOx must have corresponding TRIS bit cleared

- SCKx (Master mode) must have corresponding TRIS bit cleared

- SCKx (Slave mode) must have corresponding TRIS bit set

- SSx must have corresponding TRIS bit set

© 2015-2016 Microchip Technology Inc.

Preliminary

### REGISTER 20-5: SSPxMSK: SSPx MASK REGISTER

| R/W-1/1                  | R/W-1/1   | R/W-1/1                            | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|--------------------------|-----------|------------------------------------|---------|----------------|------------------|------------------|--------------|

|                          |           |                                    | MSK     | <7:0>          |                  |                  |              |

| bit 7                    |           |                                    |         |                |                  |                  | bit C        |

|                          |           |                                    |         |                |                  |                  |              |

| Legend:                  |           |                                    |         |                |                  |                  |              |

| R = Readable             | bit       | W = Writable                       | bit     | U = Unimpler   | nented bit, read | 1 as '0'         |              |

| u = Bit is unchanged x = |           | x = Bit is unkr                    | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set         |           | '0' = Bit is cle                   | ared    |                |                  |                  |              |

|                          |           |                                    |         |                |                  |                  |              |

| bit 7-1                  | MSK<7:1>: | Mask bits                          |         |                |                  |                  |              |

|                          |           | eived address b<br>eived address b |         |                |                  |                  | atch         |

bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address

I<sup>2</sup>C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):

1 = The received address bit 0 is compared to SSPxADD<0> to detect  $I^2C$  address match

0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

### 21.3 Register Definitions: EUSART Control

### REGISTER 21-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0         | R/W-0/0                                                                                               | R/W-0/0                                                                                          | R/W-0/0         | R/W-0/0        | R/W-0/0          | R-1/1          | R/W-0/0      |

|----------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|----------------|--------------|

| CSRC           | TX9                                                                                                   | TXEN <sup>(1)</sup>                                                                              | SYNC            | SENDB          | BRGH             | TRMT           | TX9D         |

| bit 7          |                                                                                                       |                                                                                                  |                 |                | •                |                | bit (        |

|                |                                                                                                       |                                                                                                  |                 |                |                  |                |              |

| Legend:        |                                                                                                       |                                                                                                  |                 |                |                  |                |              |

| R = Readal     |                                                                                                       | W = Writable                                                                                     |                 | -              | mented bit, read |                |              |

| u = Bit is ur  | -                                                                                                     | x = Bit is unk                                                                                   | nown            | -n/n = Value   | at POR and BOI   | R/Value at all | other Resets |

| '1' = Bit is s | set                                                                                                   | '0' = Bit is cle                                                                                 | ared            |                |                  |                |              |

| bit 7          | Asynchronou<br>Don't care<br>Synchronous<br>1 = Master                                                |                                                                                                  | nerated interr  |                | )                |                |              |

| bit 6          | <b>TX9:</b> 9-bit Tr<br>1 = Selects                                                                   | ansmit Enable  <br>9-bit transmiss<br>8-bit transmiss                                            | bit<br>ion      | ,              |                  |                |              |

| bit 5          | 1 = Transmi                                                                                           | <b>TXEN:</b> Transmit Enable bit <sup>(1)</sup><br>1 = Transmit enabled<br>0 = Transmit disabled |                 |                |                  |                |              |

| bit 4          | SYNC: EUS<br>1 = Synchro<br>0 = Asynchr                                                               |                                                                                                  | ect bit         |                |                  |                |              |

| bit 3          | Asynchronou<br>1 = Send Sy                                                                            | nc Break on ne<br>eak transmissic                                                                | ext transmissio | on (cleared by | hardware upon o  | completion)    |              |

| bit 2          | BRGH: High<br><u>Asynchronou</u><br>1 = High spe<br>0 = Low spe<br><u>Synchronous</u><br>Unused in th | eed<br>ed<br><u>s mode:</u>                                                                      | ect bit         |                |                  |                |              |

| bit 1          | <b>TRMT:</b> Trans<br>1 = TSR em                                                                      | <b>TRMT:</b> Transmit Shift Register Status bit<br>1 = TSR empty<br>0 = TSR full                 |                 |                |                  |                |              |

| bit 0          | TX9D: Ninth                                                                                           | hit of Tronomit                                                                                  | Data            |                |                  |                |              |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                    |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| IORLW            | Inclusive OR literal with W                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |

| Operands:        | $0 \leq k \leq 255$                                                                                          |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                            |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| INCF             | Increment f                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                         |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW            | Subtract W        | / from literal                                                                 |

|------------------|-------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] SL        | JBLW k                                                                         |

| Operands:        | $0 \le k \le 255$ |                                                                                |

| Operation:       | $k -(W) \to (W$   | )                                                                              |

| Status Affected: | C, DC, Z          |                                                                                |

| Description:     | complement        | er is subtracted (2's<br>method) from the 8-bit<br>e result is placed in the W |

|                  | <b>C</b> = 0      | W > k                                                                          |

|                  | <b>C</b> = 1      | $W \leq k$                                                                     |

DC = 0

DC = 1

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit, $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |

| SUBWF            | Subtract W from f                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |  |  |  |  |  |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f. |  |  |  |  |  |  |  |  |  |

|                  | C = 0 W > f                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| <b>C</b> = 0 | W > f               |

|--------------|---------------------|

| <b>C =</b> 1 | $W \leq f$          |

| DC = 0       | W<3:0> > f<3:0>     |

| DC = 1       | $W<3:0> \le f<3:0>$ |

W<3:0> > k<3:0>

$W<3:0> \le k<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |  |  |  |  |  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |  |  |

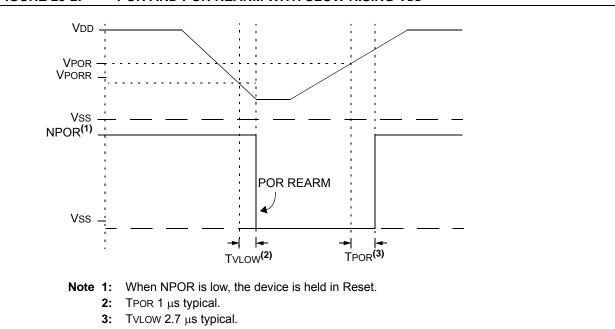

#### FIGURE 25-2: POR AND POR REARM WITH SLOW RISING VDD

### TABLE 25-2: SUPPLY CURRENT (IDD)

| PIC16LF                                | 1566/1567       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |       |       |            |                                         |  |  |  |  |

|----------------------------------------|-----------------|------------------------------------------------------|-------|-------|-------|------------|-----------------------------------------|--|--|--|--|

| Param. Device                          |                 | Trend                                                |       | Unite |       | Conditions |                                         |  |  |  |  |

| No.                                    | Characteristics | Min.                                                 | Тур.† | Max.  | Units | Vdd        | Note                                    |  |  |  |  |

| Supply Current (IDD) <sup>(1, 2)</sup> |                 |                                                      |       |       |       |            |                                         |  |  |  |  |

| D010                                   |                 |                                                      | 2.5   | 18    | μA    | 1.8        | Fosc = 31 kHz                           |  |  |  |  |

|                                        |                 |                                                      | 4     | 20    | μA    | 3.0        | LFINTOSC mode                           |  |  |  |  |

| D011                                   |                 | _                                                    | 0.35  | 0.70  | mA    | 1.8        | Fosc = 8 MHz                            |  |  |  |  |

|                                        |                 | _                                                    | 0.55  | 1.10  | mA    | 3.0        | HFINTOSC mode                           |  |  |  |  |

| D012                                   |                 | _                                                    | 0.5   | 1.2   | mA    | 1.8        | Fosc = 16 MHz                           |  |  |  |  |

|                                        |                 | _                                                    | 0.8   | 1.75  | mA    | 3.0        | HFINTOSC mode                           |  |  |  |  |

| D013                                   |                 | —                                                    | 1.5   | 3.5   | mA    | 3.0        | Fosc = 32 MHz<br>HFINTOSC mode with PLL |  |  |  |  |

| D014                                   |                 | _                                                    | 3     | 17    | μA    | 1.8        | Fosc = 32 kHz                           |  |  |  |  |

|                                        |                 | —                                                    | 5     | 20    | μA    | 3.0        | ECL mode                                |  |  |  |  |

| D015                                   |                 | —                                                    | 12    | 40    | μA    | 1.8        | Fosc = 500 kHz                          |  |  |  |  |

|                                        |                 |                                                      | 18    | 60    | μA    | 3.0        | ECL mode                                |  |  |  |  |

| D016                                   |                 |                                                      | 25    | 65    | μA    | 1.8        | Fosc = 1 MHz                            |  |  |  |  |

|                                        |                 |                                                      | 40    | 100   | μA    | 3.0        | ECM mode                                |  |  |  |  |

† Data in "Typ." column is at 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: CLKIN = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

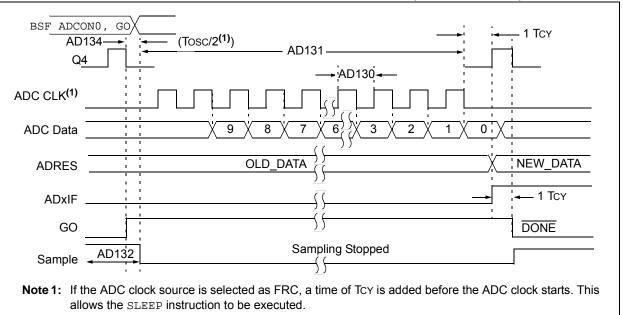

### TABLE 25-13: PIC16LF1566/1567 ADC CONVERSION REQUIREMENTS

Standard Operating Conditions (unless otherwise stated) Operating temperature  $-40^{\circ}C < Ta < +125^{\circ}C$

| Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                 |                    |       |               |                |                                                                                                                         |  |  |

|---------------------------------------------------------------|------|-----------------------------------------------------------------|--------------------|-------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No.                                                 | Sym. | Characteristic                                                  | Min.               | Тур.† | Max.          | Units          | Conditions                                                                                                              |  |  |

| AD130*                                                        | TAD  | ADC Clock Period                                                | 0.25<br>0.7<br>0.7 |       | 25<br>25<br>8 | μs<br>μs<br>μs | Tosc-based, -40°C to +85°C, VREF $\ge$ 2.4V<br>Tosc-based, -40°C to +85°C, VREF $<$ 2.4V<br>Tosc-based, +86°C to +125°C |  |  |

|                                                               |      | ADC Internal FRC Oscillator<br>Period                           | 1.0                | 1.6   | 6.0           | μS             | ADCS<1:0> = 11 (ADFRC mode)                                                                                             |  |  |

| AD131                                                         | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | -                  | 11    | —             | Tad            | Set GO/DONEx bit to conversion complete                                                                                 |  |  |

| AD132*                                                        | TACQ | Acquisition Time                                                | —                  | 5.0   |               | μS             |                                                                                                                         |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

### FIGURE 25-9: PIC16LF1566/1567 ADC CONVERSION TIMING (NORMAL MODE)

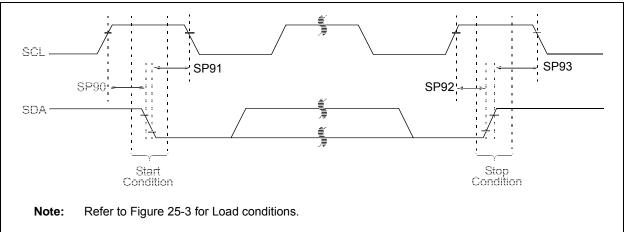

### FIGURE 25-17: I<sup>2</sup>C BUS START/STOP BITS TIMING

### TABLE 25-17: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |         |                 |              |      |      |      |       |                                                       |  |

|---------------------------------------------------------|---------|-----------------|--------------|------|------|------|-------|-------------------------------------------------------|--|

| Param.<br>No.                                           | Symbol  | Characteristic  |              | Min. | Тур. | Max. | Units | Conditions                                            |  |

| SP90*                                                   | TSU:STA | Start condition | 100 kHz mode | 4700 | —    |      | ns    | Only relevant for Repeated                            |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | —    | —    |       | Start condition                                       |  |

| SP91*                                                   | THD:STA | Start condition | 100 kHz mode | 4000 | _    |      | ns    | After this period, the first clock pulse is generated |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | -    | _    |       |                                                       |  |

| SP92*                                                   | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _    | _    | ns    |                                                       |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | -    | _    |       |                                                       |  |

| SP93                                                    | THD:STO | Stop condition  | 100 kHz mode | 4000 | _    |      | ns    |                                                       |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | _    |      |       |                                                       |  |

\* These parameters are characterized but not tested.

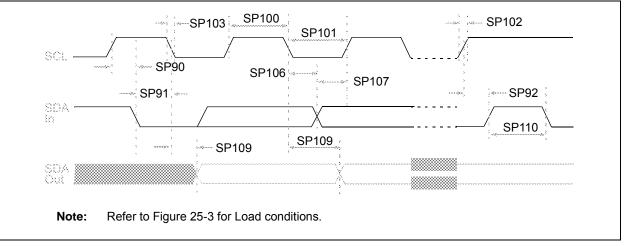

### FIGURE 25-18: I<sup>2</sup>C BUS DATA TIMING

| Param.<br>No. | Symbol<br>Thigh | Charact               | Min.         | Max.       | Units | Conditions                               |                                             |

|---------------|-----------------|-----------------------|--------------|------------|-------|------------------------------------------|---------------------------------------------|

| SP100*        |                 | Clock high time       | 100 kHz mode | 4.0        |       | μS                                       | Device must operate at a minimum of 1.5 MHz |

|               |                 |                       | 400 kHz mode | 0.6        | _     | μS                                       | Device must operate at a minimum of 10 MHz  |

|               |                 |                       | SSP module   | 1.5TCY     |       |                                          |                                             |

| SP101*        | SP101* TLOW     | Clock low time        | 100 kHz mode | 4.7        | _     | μS                                       | Device must operate at a minimum of 1.5 MHz |

|               |                 |                       | 400 kHz mode | 1.3        | _     | μS                                       | Device must operate at a minimum of 10 MHz  |

|               |                 | SSP module            | 1.5TCY       | _          |       |                                          |                                             |

| SP102*        |                 | SDA and SCL rise time | 100 kHz mode | —          | 1000  | ns                                       |                                             |

|               |                 |                       | 400 kHz mode | 20 + 0.1Св | 300   | ns                                       | CB is specified to be from 10-400 pF        |

| SP103*        | TF              | SDA and SCL fall      | 100 kHz mode | —          | 250   | ns                                       |                                             |

|               | time            | 400 kHz mode          | 20 + 0.1Св   | 250        | ns    | CB is specified to be from 10-400 pF     |                                             |

| SP106*        | THD:DAT         | Data input hold time  | 100 kHz mode | 0          |       | ns                                       |                                             |

|               |                 |                       | 400 kHz mode | 0          | 0.9   | μs                                       |                                             |

| SP107*        | TSU:DAT         | Data input setup time | 100 kHz mode | 250        | _     | ns                                       | (Note 2)                                    |

|               |                 |                       | 400 kHz mode | 100        | —     | ns                                       |                                             |

| SP109*        | ΤΑΑ             | Output valid from     | 100 kHz mode | —          | 3500  | ns                                       | (Note 1)                                    |

|               | clock           | 400 kHz mode          | —            |            | ns    |                                          |                                             |

| SP110*        | TBUF            | Bus free time         | 100 kHz mode | 4.7        | —     | μs                                       | Time the bus must be free                   |

|               |                 | 400 kHz mode          | 1.3          | _          | μS    | before a new transmis-<br>sion can start |                                             |

| SP111         | Св              | Bus capacitive load   | ing          | _          | 400   | pF                                       |                                             |

### TABLE 25-18: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.