Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 34x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

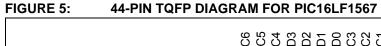

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1567t-i-pt |

### **PIN ALLOCATION TABLES**

TABLE 2: 28-PIN ALLOCATION TABLE (PIC16LF1566)

|     | : Z:                   |             | ,              | CATION TAE                                       | (      | 1021 1000, |        |                             |            |         |                   |

|-----|------------------------|-------------|----------------|--------------------------------------------------|--------|------------|--------|-----------------------------|------------|---------|-------------------|

| O/I | 28-Pin SPDIP/SOIC/SSOP | 28-Pin UQFN | Analog Channel | ADC and CVD                                      | Timers | MWd        | EUSART | MSSP                        | Interrupt  | Pull-up | Basic             |

| RA0 | 2                      | 27          | AN20           | _                                                | -      | PWM10      | _      | SS1 <sup>(1)</sup>          | -          | _       | _                 |

| RA1 | 3                      | 28          | AN10           | _                                                | _      | PWM11      | _      | SS2                         | _          | _       |                   |

| RA2 | 4                      | 1           | AN0            | VREF-                                            | -      | PWM12      |        | _                           | _          | _       | _                 |

| RA3 | 5                      | 2           | AN1            | VREF+                                            | 1      | PWM13      |        | _                           | 1          | _       | _                 |

| RA4 | 6                      | 3           | AN2            | _                                                | T0CKI  | _          | _      | _                           | _          | _       | _                 |

| RA5 | 7                      | 4           | AN21           | _                                                | _      | _          | _      | SS1 <sup>(1)</sup>          | _          |         | _                 |

| RA6 | 10                     | 7           | AN22           | ADTRIG                                           | 1      | _          | 1      | _                           | 1          | _       | CLKOUT            |

| RA7 | 9                      | 6           | AN11           | _                                                | 1      | _          |        | _                           | 1          | _       | CLKIN             |

| RB0 | 21                     | 18          | AN16           | _                                                | _      | PWM20      | _      | _                           | INT<br>IOC | Y       | _                 |

| RB1 | 22                     | 19          | AN27           | _                                                |        | PWM21      |        | _                           | IOC        | Υ       | _                 |

| RB2 | 23                     | 20          | AN17           | _                                                | 1      | PWM22      | _      | _                           | IOC        | Υ       | _                 |

| RB3 | 24                     | 21          | AN28           | _                                                | -      | PWM23      | _      | _                           | IOC        | Υ       | _                 |

| RB4 | 25                     | 22          | AN18           | AD1GRDA <sup>(1)</sup><br>AD2GRDA <sup>(1)</sup> | I      |            | 1      | _                           | IOC        | Y       | _                 |

| RB5 | 26                     | 23          | AN29           | AD1GRDA <sup>(1)</sup><br>AD2GRDA <sup>(1)</sup> | T1G    | _          | -      |                             | IOC        | Y       | _                 |

| RB6 | 27                     | 24          | AN19           | AD1GRDB <sup>(1)</sup><br>AD2GRDB <sup>(1)</sup> | _      | _          | _      | _                           | IOC        | Y       | ICSPCLK<br>ICDCLK |

| RB7 | 28                     | 25          | AN40           | AD1GRDB <sup>(1)</sup><br>AD2GRDB <sup>(1)</sup> | _      | _          | _      | _                           | IOC        | Y       | ICSPDAT<br>ICDDAT |

| RC0 | 11                     | 8           | AN12           | _                                                | T1CKI  | _          | -      | SDO2                        | _          | _       | _                 |

| RC1 | 12                     | 9           | AN23           | _                                                | _      | PWM2       | _      | SCL2<br>SCK2                | _          | _       | _                 |

| RC2 | 13                     | 10          | AN13           | _                                                | _      | PWM1       | _      | SDA2<br>SDI2                | _          | _       | _                 |

| RC3 | 14                     | 11          | AN24           | _                                                | _      | _          | _      | SCL1<br>SCK1                | _          | _       | _                 |

| RC4 | 15                     | 12          | AN14           | _                                                | _      | _          | _      | SDA1<br>SDI1                | _          | _       | _                 |

| RC5 | 16                     | 13          | AN25           | _                                                | _      | _          | _      | SDO1<br>I <sup>2</sup> CLVL | _          | _       | _                 |

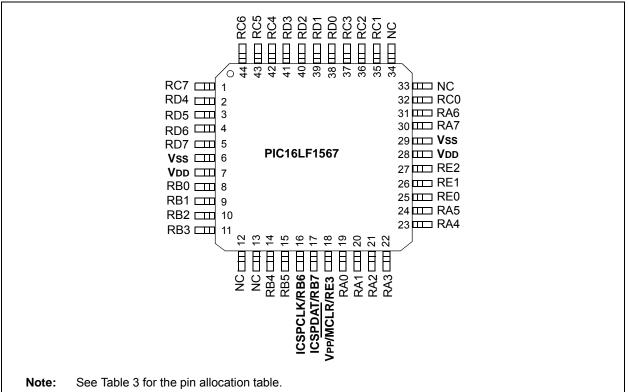

FIGURE 1-1: PIC16LF1566/1567 BLOCK DIAGRAM<sup>(1,2)</sup>

### TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                                     |                       |               |                                                                                                        |                |                 |                |              | ,               |              |                       |                                 |

|-------------------------------------|-----------------------|---------------|--------------------------------------------------------------------------------------------------------|----------------|-----------------|----------------|--------------|-----------------|--------------|-----------------------|---------------------------------|

| Addr.                               | Name                  | Bit 7         | Bit 6                                                                                                  | Bit 5          | Bit 4           | Bit 3          | Bit 2        | Bit 1           | Bit 0        | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank                                | Banks 9-11            |               |                                                                                                        |                |                 |                |              |                 |              |                       |                                 |

| x00h/<br>x80h                       | INDF0 <sup>(1)</sup>  | Addressing t  | his location us                                                                                        | ses contents o | f FSR0H/FSR     | OL to addres   | s data memor | y (not a physic | al register) | xxxx xxxx             | uuuu uuuu                       |

| x00h/<br>x81h                       | INDF1 <sup>(1)</sup>  | Addressing t  | Addressing this location uses contents of FSR1H/FSR1L to address data memory (not a physical register) |                |                 |                |              |                 | al register) | xxxx xxxx             | uuuu uuuu                       |

| x02h/<br>x82h                       | PCL <sup>(1)</sup>    |               | Program Counter (PC) Least Significant Byte                                                            |                |                 |                |              |                 |              | 0000 0000             | 0000 0000                       |

| x03h/<br>x83h                       | STATUS <sup>(1)</sup> |               |                                                                                                        |                |                 |                |              | 1 1000          | q quuu       |                       |                                 |

| x04h/<br>x84h                       | FSR0L <sup>(1)</sup>  |               | Indirect Data Memory Address 0 Low Pointer                                                             |                |                 |                |              |                 |              | 0000 0000             | uuuu uuuu                       |

| x05h/<br>x85h                       | FSR0H <sup>(1)</sup>  |               | Indirect Data Memory Address 0 High Pointer                                                            |                |                 |                |              |                 | 0000 0000    | 0000 0000             |                                 |

| x06h/<br>x86h                       | FSR1L <sup>(1)</sup>  |               | Indirect Data Memory Address 1 Low Pointer                                                             |                |                 |                |              |                 | 0000 0000    | uuuu uuuu             |                                 |

| x07h/<br>x87h                       | FSR1H <sup>(1)</sup>  |               |                                                                                                        | Indirect Da    | ata Memory A    | ddress 1 Higl  | h Pointer    |                 |              | 0000 0000             | 0000 0000                       |

| x08h/<br>x88h                       | BSR <sup>(1)</sup>    | _             | _                                                                                                      | _              |                 |                | BSR<4:0>     |                 |              | 0 0000                | 0 0000                          |

| x09h/<br>x89h                       | WREG <sup>(1)</sup>   |               |                                                                                                        |                | Working F       | Register       |              |                 |              | 0000 0000             | uuuu uuuu                       |

| x0Ah/<br>x8Ah                       | PCLATH <sup>(1)</sup> | _             |                                                                                                        | Write B        | uffer for the u | pper 7 bits of | the Program  | Counter         |              | -000 0000             | -000 0000                       |

| x0Bh/<br>x8Bh                       | INTCON <sup>(1)</sup> | GIE           | PEIE                                                                                                   | TMR0IE         | INTE            | IOCIE          | TMR0IF       | INTF            | IOCIF        | 0000 0000             | 0000 000u                       |

| x0Ch/<br>x8Ch<br>—<br>x1Fh/<br>x9Fh | _                     | Unimplemented |                                                                                                        |                |                 |                |              |                 | _            | _                     |                                 |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These registers can be accessed from any bank.

- 2: PIC16I F1567

- 3: These registers/bits are available at two address locations, in Bank 1 and Bank 14.

- 4: PIC16LF1566 only.

- 5: Unimplemented, read as '1'.

### 5.4 Register Definitions: Oscillator Control

### REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0  | R/W-0/0  | R/W-0/0 |

|---------|---------|---------|---------|---------|------|----------|---------|

| SPLLEN  |         | IRCF    | <3:0>   | _       | SCS- | SCS<1:0> |         |

| bit 7   |         |         |         |         |      | •        | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 **SPLLEN:** Software PLL Enable bit 1 = 4x PLL Is enabled 0 = 4x PLL is disabled bit 6-3 IRCF<3:0>: Internal Oscillator Frequency Select bits 1111 = 16 MHz 1110 = 8 MHz1101 = 4 MHz1100 = 2 MHz1011 = 1 MHz $1010 = 500 \text{ kHz}^{(1)}$ 1001 = 250 kHz<sup>(1)</sup>  $1000 = 125 \text{ kHz}^{(1)}$ 0111 = 500 kHz (default upon Reset) 0110 = 250 kHz0101 = **125** kHz 0100 = 62.5 kHz001x = 31.25 kHz000x = 31 kHz (LFINTOSC)bit 2 Unimplemented: Read as '0' bit 1-0 SCS<1:0>: System Clock Select bits 1x = Internal oscillator block 01 = Reserved 00 = Clock determined by FOSC<1:0> in Configuration Words

Note 1: Duplicate frequency derived from HFINTOSC.

### 10.6 Register Definitions: Flash Program Memory Control

### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PMDA    | T<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PMDAT<7:0>**: Read/write value for Least Significant bits of program memory

### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | PMDA    | T<13:8> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **PMDAT<13:8>**: Read/write value for Most Significant bits of program memory

### 12.6 Register Definitions: Interrupt-on-Change Control

### REGISTER 12-1: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 IOCBP<7:0>: Interrupt-on-Change PORTB Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-2: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   | •       | •       |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 IOCBN<7:0>: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-3: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HS - Bit is set in hardware

bit 7-0 IOCBF<7:0>: Interrupt-on-Change PORTB Flag bits

1 = An enabled change was detected on the associated pin. Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

0 = No change was detected, or the user cleared the detected change.

### REGISTER 16-7: ADxCON2: ADC CONTROL REGISTER 2<sup>(1)</sup>

| U-0   | R/W-0/0 | R/W-0/0      | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|-------|---------|--------------|---------|-----|-----|-----|-------|

| _     | -       | TRIGSEL<2:0> |         | _   | _   | _   | _     |

| bit 7 |         |              |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **Unimplemented:** Read as '0'

bit 6-4 TRIGSEL<2:0>: Auto-Conversion Trigger Selection bits

111 = ADTRIG Falling Edge 110 = ADTRIG Rising Edge 101 = TMR2 match to PR2<sup>(1)</sup> 100 = Timer1 Overflow<sup>(1)</sup> 011 = Timer0 Overflow<sup>(1)</sup>

001 = Reserved

000 = No Auto Conversion Trigger selected

bit 3-0 **Unimplemented:** Read as '0'

Note 1: Signal also sets its corresponding interrupt flag.

010 = TMR4 match to PR4

### 18.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

### 18.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 18.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

# 18.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

### 18.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 18.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 18-3 for timing details.

TABLE 18-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK    | T1GPOL | T1G | Timer1 Operation |

|----------|--------|-----|------------------|

| <b>↑</b> | 0      | 0   | Counts           |

| <b>↑</b> | 0      | 1   | Holds Count      |

| <b>↑</b> | 1      | 0   | Holds Count      |

| <b>↑</b> | 1      | 1   | Counts           |

# 18.5.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 18-4. Source selection is controlled by the T1GSS bit of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 18-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                 |  |  |

|-------|--------------------------------------------------------------------|--|--|

| 0     | Timer1 Gate pin (T1G)                                              |  |  |

| 1     | Overflow of Timer0 (T0_overflow) (TMR0 increments from FFh to 00h) |  |  |

### 18.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 18.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

### 18.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 18-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |

|-------|---------------------------------------------|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |

|       | indeterminate operation.                    |  |  |  |

# 18.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 18-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 18-6 for timing details.

### 18.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 18.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

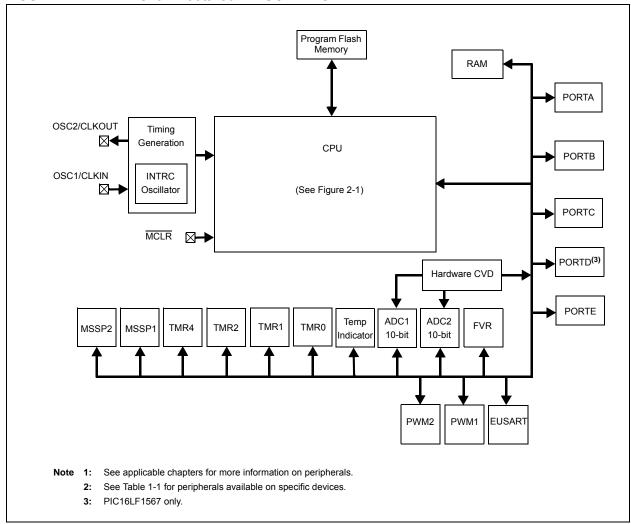

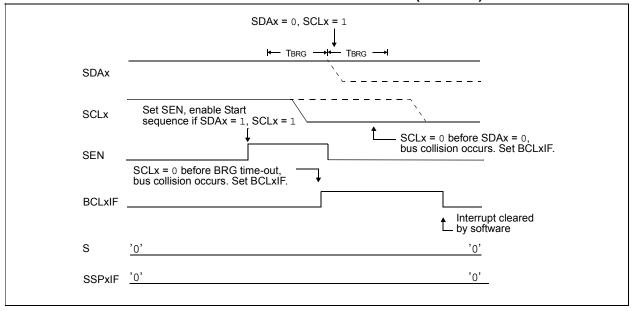

### 20.4.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDAx from a high to a low state while SCLx line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 20-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDAx line low before asserting it low. This does not conform to the I<sup>2</sup>C Specification that states no bus collision can occur on a Start.

### 20.4.6 STOP CONDITION

A Stop condition is a transition of the SDAx line from low-to-high state while the SCLx line is high.

**Note:** At least one SCLx low time must appear before a Stop is valid, therefore, if the SDAx line goes low then high again while the SCLx line stays high, only the Start condition is detected.

#### 20.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 20-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

### 20.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

### 20.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 20-4.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 20.2.3 "SPI Master Mode"** for more detail.

### 20.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an I<sup>2</sup>C slave in 7-bit Addressing mode. Figure 20-14 and Figure 20-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish I<sup>2</sup>C communication.

- 1. Start bit detected.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit clear is received.

- The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- Software clears the SSPxIF bit.

- Software reads received address from SSPxBUF clearing the BF flag.

- If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

### 20.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus™ that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for I<sup>2</sup>C communication. Figure 20-16 displays a module using both address and data holding. Figure 20-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to determine if the SSPxIF was after or before the ACK.

- Slave reads the address value from SSPxBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCLx for a received data byte.

- Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

# 20.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 20-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- Slave software clears SSPxIF.

- Slave software reads the <u>ACKTIM</u> bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the ACK value from the slave.

- Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

**Note:** SSPxBUF cannot be loaded until after the ACK.

- 13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an  $\overline{ACK}$  value on the ninth SCLx pulse.

- 15. Slave hardware copies the  $\overline{ACK}$  value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not  $\overline{ACK}$  on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

### 20.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCLx line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCLx.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. Setting CKP will release SCLx and allow more communication.

### 20.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the ninth falling edge of SCLx.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the ninth falling edge of SCLx. It is now always cleared for read requests.

### 20.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCLx is stretched without CKP being cleared. SCLx is released immediately after a write to SSPxADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

### 20.5.6.3 Byte NACKing

When the AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the eighth falling edge of SCLx for a received matching address byte. When the DHEN bit of SSPxCON3 is set; CKP is cleared after the eighth falling edge of SCLx for received data.

Stretching after the eighth falling edge of SCLx allows the slave to look at the received address or data and decide if it wants to ACK the received data.

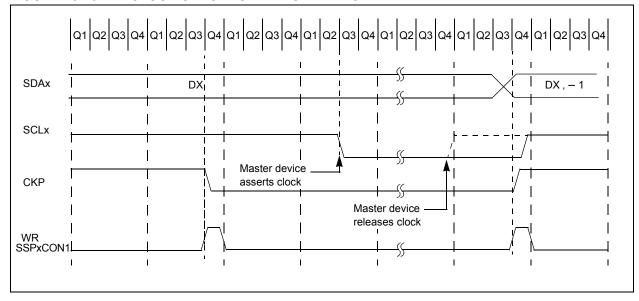

# 20.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external I<sup>2</sup>C master device has already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the I<sup>2</sup>C bus have released SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 20-23).

### 20.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 20-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

**Note:** The MSSPx module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

### 20.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

### 20.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

### 20.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### 20.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the master clocks in a byte from the slave.

- After the eighth falling edge of SCLx, SSPxIF and BF are set.

- Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- Masters ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not  $\overline{ACK}$  or Stop to end communication.

FIGURE 20-34: BUS COLLISION DURING START CONDITION (SCLX = 0)

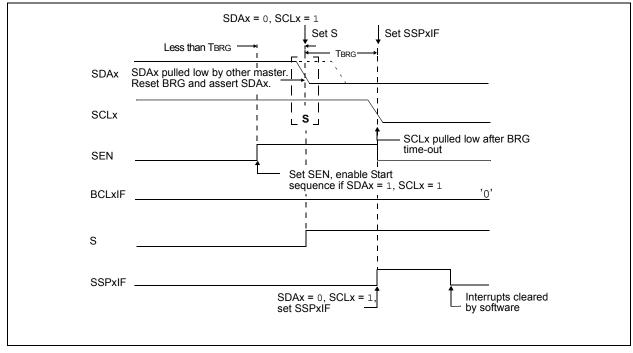

FIGURE 20-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

### 25.3 DC Characteristics

### **TABLE 25-1: SUPPLY VOLTAGE**

| PIC16LF1566/1567 |                      | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                      |                  |             |        |                                                                                                                                                     |

|------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.    | Sym.                 | Characteristic                                                                                                                                                                                                                     | Min.                 | Тур.†            | Max.        | Units  | Conditions                                                                                                                                          |

| D001             | VDD                  | Supply Voltage (VDDMIN, VDDMAX)                                                                                                                                                                                                    |                      |                  |             |        |                                                                                                                                                     |

|                  |                      |                                                                                                                                                                                                                                    | 1.8<br>2.5           | _                | 3.6<br>3.6  | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz                                                                                                                     |

| D002*            | VDR                  | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                                                                                          | 1.5                  | _                | _           | V      | Device in Sleep mode                                                                                                                                |

| D002A*           | VPOR*                | Power-on Reset Release Voltage                                                                                                                                                                                                     | _                    | 1.6              | _           | V      |                                                                                                                                                     |

| D002B*           | VPORR*               | Power-on Reset Rearm Voltage                                                                                                                                                                                                       | _                    | 0.8              | _           | V      |                                                                                                                                                     |

| D003             | VADFVR               | Fixed Voltage Reference Voltage for ADC, Initial Accuracy                                                                                                                                                                          | -7<br>-8<br>-7<br>-8 | _<br>_<br>_<br>_ | 6<br>6<br>6 | %      | $1.024V$ , VDD $\geq 2.5V$ , $85^{\circ}C$ (Note 2) $1.024V$ , VDD $\geq 2.5V$ , $125^{\circ}C$ (Note 2) $2.048V$ , VDD $\geq 2.5V$ , $85^{\circ}C$ |

|                  |                      |                                                                                                                                                                                                                                    |                      |                  |             |        | 2.048V, VDD ≥ 2.5V, 125°C                                                                                                                           |

| D003C*           | TCVFVR               | Temperature Coefficient, Fixed Voltage Reference                                                                                                                                                                                   | _                    | -130             | _           | ppm/°C |                                                                                                                                                     |

| D003D*           | ΔVFVR/<br>ΔVIN       | Line Regulation, Fixed Voltage Reference                                                                                                                                                                                           | _                    | 0.270            | _           | %/V    |                                                                                                                                                     |

| D004*            | SVDD                 | VDD Rise Rate to ensure internal Power-on Reset signal                                                                                                                                                                             | 0.05                 | _                | _           | V/ms   | See Section 6.1 "Power-on Reset (POR)" for details.                                                                                                 |

| D005*            | VI <sup>2</sup> CLVL | I <sup>2</sup> CLVL Voltage                                                                                                                                                                                                        | TBD                  |                  | Vdd         | V      | _                                                                                                                                                   |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>2:</sup> For proper operation, the minimum value of the ADC positive voltage reference must be 1.8V or greater. When selecting the FVR or the VREF+ pin as the source of the ADC positive voltage reference, be aware that the voltage must be 1.8V or greater.

### **TABLE 25-6: THERMAL CHARACTERISTICS**

Standard Operating Conditions (unless otherwise stated) Operating temperature  $-40^{\circ}C \le TA \le +125^{\circ}C$

| Param.<br>No. | Sym.      | Characteristic                      | Тур. | Units | Conditions                                               |

|---------------|-----------|-------------------------------------|------|-------|----------------------------------------------------------|

| TH01          | θЈА       | Thermal Resistance Junction to      | 60.0 | °C/W  | 28-pin SPDIP package                                     |

|               |           | Ambient                             | 80.3 | °C/W  | 28-pin SOIC package                                      |

|               |           |                                     | 90.0 | °C/W  | 28-pin SSOP package                                      |

|               |           |                                     | 48.0 | °C/W  | 28-pin UQFN (4x4 mm) package                             |

|               |           |                                     | 47.2 | °C/W  | 40-pin PDIP package                                      |

|               |           |                                     | 46.0 | °C/W  | 44-pin TQFP package                                      |

|               |           |                                     | 41.0 | °C/W  | 40-pin UQFN (5x5 mm) package                             |

| TH02          | θЈС       | Thermal Resistance Junction to Case | 31.4 | °C/W  | 28-pin SPDIP package                                     |

|               |           |                                     | 24.0 | °C/W  | 28-pin SOIC package                                      |

|               |           |                                     | 24.0 | °C/W  | 28-pin SSOP package                                      |

|               |           |                                     | 12.0 | °C/W  | 28-pin UQFN (4x4 mm) package                             |

|               |           |                                     | 24.7 | °C/W  | 40-pin PDIP package                                      |

|               |           |                                     | 14.5 | °C/W  | 44-pin TQFP package                                      |

|               |           |                                     | 50.5 | °C/W  | 40-pin UQFN (5x5 mm) package                             |

| TH03          | ТЈМАХ     | Maximum Junction Temperature        | 150  | °C    |                                                          |

| TH04          | PD        | Power Dissipation                   | I    | W     | PD = PINTERNAL + PI/O                                    |

| TH05          | PINTERNAL | Internal Power Dissipation          | I    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06          | Pı/o      | I/O Power Dissipation               |      | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07          | PDER      | Derated Power                       | _    | W     | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

<sup>2:</sup> TA = Ambient Temperature; TJ = Junction Temperature.

### 25.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т                                          |        |

|--------------------------------------------|--------|

| F Frequency                                | T Time |

| Lowercase letters (pp) and their meanings: |        |

| nn                                         |        |

| рр |               |     |          |

|----|---------------|-----|----------|

| СС | CCP1          | osc | CLKIN    |

| ck | CLKOUT        | rd  | RD       |

| cs | <del>CS</del> | rw  | RD or WR |

| di | SDIx          | sc  | SCKx     |

| do | SDO           | SS  | SS       |

| dt | Data in       | t0  | T0CKI    |

| io | I/O PORT      | t1  | T1CKI    |

| mc | MCLR          | wr  | WR       |

Uppercase letters and their meanings:

| S |                          |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (High-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

### FIGURE 25-3: LOAD CONDITIONS

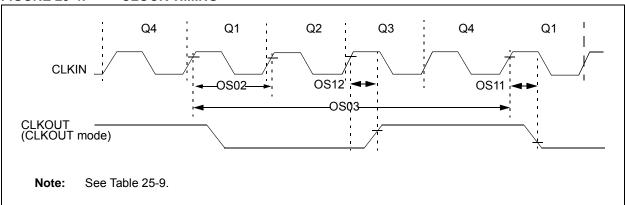

### FIGURE 25-4: CLOCK TIMING

### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Addre

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511

Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880 China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533

Fax: 86-21-5407-5066 China - Shenyang

Tel: 86-24-2334-2829

Fax: 86-24-2334-2393 China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770

Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857

Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828

Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe

Tel: 49-721-625370 Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

UK - Wokingham

Tel: 44-118-921-5800 Fax: 44-118-921-5820