Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f064h-50i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

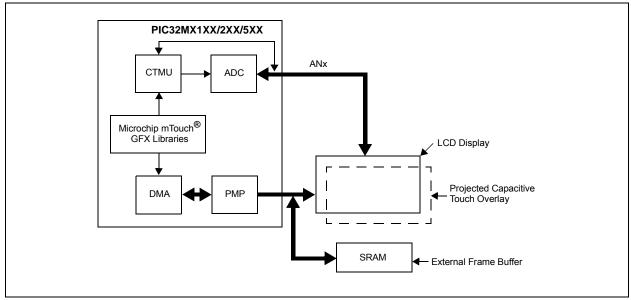

## FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

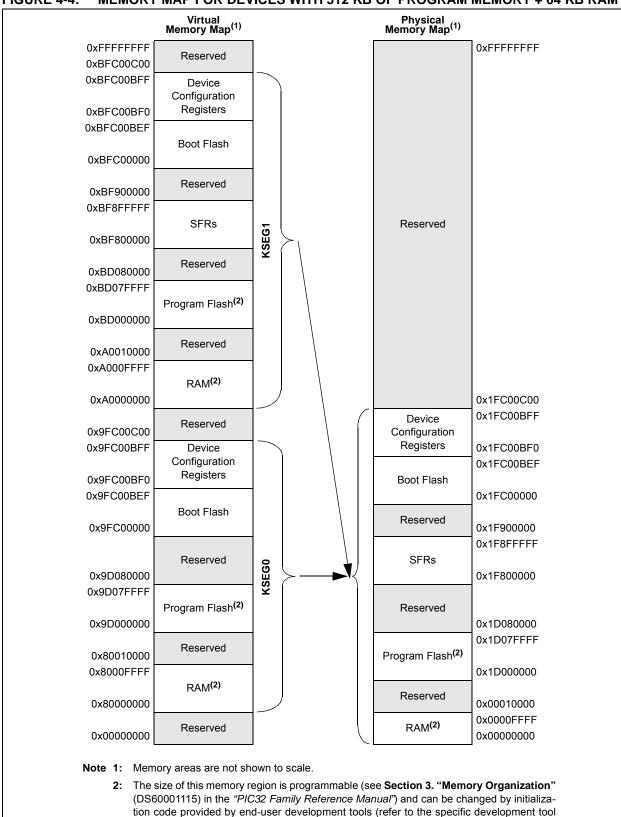

#### FIGURE 4-4: MEMORY MAP FOR DEVICES WITH 512 KB OF PROGRAM MEMORY + 64 KB RAM

© 2014-2016 Microchip Technology Inc.

documentation for information).

|              | LOISTER 4-3. DIMADODDA: DATA RAIN COER DATA DAGE ADDREGG REGISTER |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 04.04        | U-0                                                               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                                                                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |

| 00.40        | U-0                                                               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                                                                 | —                 | _                 | _                 | _                 | —                 | —                | —                |  |

| 45.0         | R/W-0                                                             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |

| 15:8         | 15:8 BMXDUDBA<15:8>                                               |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0                                                               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                                                                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

### Legend:

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

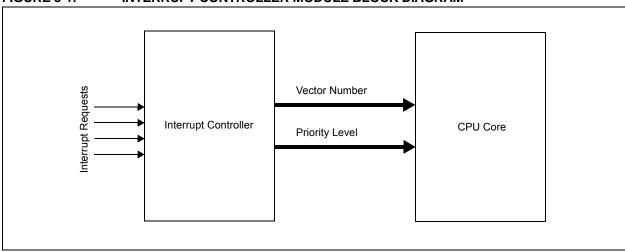

#### 5.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupt Controller"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX/5XX 64/100-pin interrupt module includes the following features:

- Up to 76 interrupt sources

- Up to 46 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Software can generate any interrupt

- User-configurable interrupt vector table location

- User-configurable interrupt vector spacing

Note: The dedicated shadow register set is not available on these devices.

#### FIGURE 5-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | -                 | —                 |                   | —                 | _                 | —                 | -                | _                |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | -                 | —                 | —                 | _                 |                   |                  | —                |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          |                   |                   |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |

#### REGISTER 5-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| zogonal                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-13 Unimplemented: Read as '0'

#### bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Runge        |                   |                   |                   |                   |                   |                   |                  |                  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        |                   | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT<7:0>       |                   |                   |                  |                  |

#### REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

#### Legend:

| =ogona.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

<u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused.

#### 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

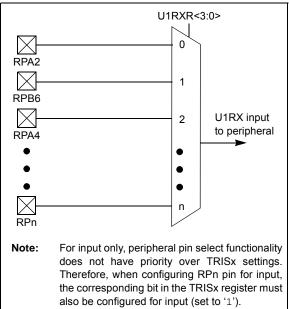

#### 11.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

### FIGURE 11-2: REI

REMAPPABLE INPUT EXAMPLE FOR U1RX

#### TABLE 11-1: INPUT PIN SELECTION

| [pin name]R SFR      | [pin name]R bits                                                                                                                                                                                                                                                                                                                                                                               | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| INT3R                | INT3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0000 = RPD2<br>0001 = RPG8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| T2CKR                | T2CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0010 = RPF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| IC3R                 | IC3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| U1RXR                | U1RXR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0101 = RPB9<br>0110 = RPB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| U2RXR                | U2RXR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0111 = RPC14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| U5CTSR               | U5CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                    | 1000 = RPB5 <sup>(7)</sup><br>1001 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| SDI3R                | SDI3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 1010 = RPC1 <sup>(3)</sup><br>1011 = RPD14 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SDI4R                | SDI4R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 1100 = RPG1 <sup>(3)</sup><br>1101 = RPA14 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| REFCLKIR             | REFCLKIR<3:0>                                                                                                                                                                                                                                                                                                                                                                                  | 1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| INT4R                | INT4R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0000 <b>= RPD3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| T5CKR                | T5CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0001 = RPG7<br>0010 = RPF5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 0011 = RPD11<br>0100 = RPF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 0101 = RPB1<br>0110 = RPE5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 0111 = RPC13<br>1000 = RPB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 1001 = RPF12 <sup>(3)</sup><br>1010 = RPC4 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| C1RXR <sup>(5)</sup> | C1RXR<3:0> <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                      | 1110 = R(F2(2)<br>1111 = RPF7 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| INT2R                | INT2R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0000 = RPD9<br>0001 = RPG6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| T4CKR                | T4CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0010 = RPB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| IC2R                 | IC2R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| IC5R                 | IC5R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 0101 = RPB0<br>0110 = RPE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| U1CTSR               | U1CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                    | 0111 = RPB7<br>1000 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| U2CTSR               | U2CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                    | 1001 = RPF12 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| SS1R                 | SS1R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 1010 = RPD12 <sup>(3)</sup><br>1011 = RPF8 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SS3R                 | SS1R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 1100 = RPC3 <sup>(3)</sup><br>1101 = RPE9 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SS3R                 | SS3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 1110 = RPD14 <sup>(3)</sup><br>1111 = RPB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                      | INT3R           T2CKR           IC3R           U1RXR           U2RXR           U5CTSR           SDI3R           SDI4R           REFCLKIR           INT4R           U3RXR           U4CTSR           SDI1R           SDI2R           U4CTSR           SDI2R           U1RXR <sup>(5)</sup> INT2R           INT2R           U1CTSR           U2RXR           U2RXR           SS1R           SS1R | INT3R         INT3R           IZCKR         T2CKR           IC3R         IC3R           IC3R         IC3R           U1RXR         U1RXR           U2RXR         U2RXR           U5CTSR         U5CTSR           SDI3R         SDI3R           SDI3R         SDI3R           SDI4R         SDI4R           SDI4R         SDI4R           SDI4R         SDI4R           INT4R         INT4R           INT4R         INT4R           INT4R         INT4R           INT4R         INT4R           INT4R         IAT4           INT4R         IAT4           IV3RXR         U3RXR           U3RXR         U3RXR           U4CTSR         U4CTSR           U4CTSR         SDI1R           U4CTSR         SDI2R           SDI2R         SDI2R           SDI2R         SDI2R           SDI2R         SDI2R           INT2R         INT2R           INT2R         IC2R           IC2R         IC2R           IC2R         IC2R           IC5R         IC5R           IV1CTSR |  |  |

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

**3:** This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

#### TABLE 11-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(3)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0101 = Reserved                              |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 <b>= SDO1</b>                           |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(3)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(3)</sup> | RPD12R   | RPD12R<3:0> | 1011 = OC5<br>1100 = Reserved                |

| RPF8 <sup>(3)</sup>  | RPF8R    | RPF8R<3:0>  | 1101 = C1OUT                                 |

| RPC3 <sup>(3)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 <b>=</b> <del>SS3</del>                 |

| RPE9 <sup>(3)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = SS4 <sup>(3)</sup>                    |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(3)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(1)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(2)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(3)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(3)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(3)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(1)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

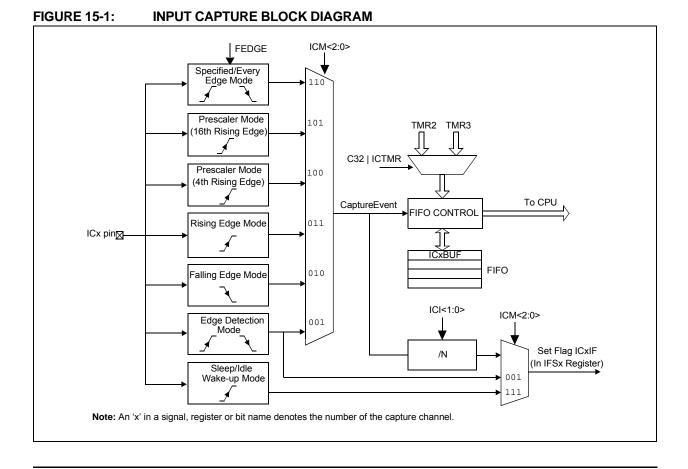

### 15.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

The other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

|              |                                                                                                                                               | PIxCON: SF                                                                                                                                                      |                                                                                                                |                                                                                                   |                                                                                  | D:/               | <b>D</b> **      | D:"                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                             | Bit<br>30/22/14/6                                                                                                                                               | Bit<br>29/21/13/5                                                                                              | Bit<br>28/20/12/4                                                                                 | Bit<br>27/19/11/3                                                                | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 31.24        | FRMEN                                                                                                                                         | FRMSYNC                                                                                                                                                         | FRMPOL                                                                                                         | MSSEN                                                                                             | FRMSYPW                                                                          | F                 | RMCNT<2:0        | )>                   |

| 23:16        | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | U-0                                                                                                            | U-0                                                                                               | U-0                                                                              | U-0               | R/W-0            | R/W-0                |

| 23.10        | MCLKSEL <sup>(2)</sup>                                                                                                                        | _                                                                                                                                                               | _                                                                                                              | —                                                                                                 | _                                                                                | —                 | SPIFE            | ENHBUF <sup>(2</sup> |

| 15:8         | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 15.0         | ON <sup>(1)</sup>                                                                                                                             | _                                                                                                                                                               | SIDL                                                                                                           | DISSDO                                                                                            | MODE32                                                                           | MODE16            | SMP              | CKE <sup>(3)</sup>   |

| 7.0          | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 7:0          | SSEN                                                                                                                                          | CKP <sup>(4)</sup>                                                                                                                                              | MSTEN                                                                                                          | DISSDI                                                                                            | STXISE                                                                           | L<1:0>            | SRXIS            | EL<1:0>              |

| Legend:      |                                                                                                                                               |                                                                                                                                                                 |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |

| R = Read     | lable hit                                                                                                                                     |                                                                                                                                                                 | W = Writable                                                                                                   | a hit                                                                                             |                                                                                  | mented bit, rea   | ad as '0'        |                      |

| -n = Valu    |                                                                                                                                               |                                                                                                                                                                 | '1' = Bit is se                                                                                                |                                                                                                   | '0' = Bit is cle                                                                 |                   | x = Bit is un    | known                |

|              | e al POR                                                                                                                                      |                                                                                                                                                                 |                                                                                                                | ÷l                                                                                                |                                                                                  | areu              | x = bit is un    | IKHOWH               |

| bit 31       | 0 = Framed S                                                                                                                                  | SPI support is<br>SPI support is                                                                                                                                | enabled (SS<br>disabled                                                                                        | _                                                                                                 | S FSYNC input                                                                    |                   |                  |                      |

| bit 30       | FRMSYNC: F<br>1 = Frame sy<br>0 = Frame sy                                                                                                    | nc pulse inpu                                                                                                                                                   | it (Slave mod                                                                                                  | e)                                                                                                | SSx pin bit (Fra                                                                 | amed SPI mo       | de only)         |                      |

| bit 29       | <b>FRMPOL:</b> Fra<br>1 = Frame pu<br>0 = Frame pu                                                                                            | ame Sync Po<br>Ilse is active-                                                                                                                                  | larity bit (Frar<br>high                                                                                       |                                                                                                   | e only)                                                                          |                   |                  |                      |

| bit 28       | MSSEN: Mas<br>1 = Slave sele                                                                                                                  | ter Mode Sla<br>ect SPI suppo<br>ode. Polarity i                                                                                                                | ve Select Ena<br>ort enabled. T<br>s determined                                                                | he <u>SS</u> pin is a by the FRMF                                                                 | automatically o<br>POL bit.                                                      | driven during t   | transmission     | in                   |