Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f064h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                                                                                                                                                              | Pin N                    | umber           |             |                |                                                          |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|-------------|----------------|----------------------------------------------------------|--|--|--|--|

| Pin Name                                                                                                                                                     | 64-pin<br>QFN/<br>TQFP   | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                              |  |  |  |  |

| PMA2                                                                                                                                                         | 8                        | 14              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA3                                                                                                                                                         | 6                        | 12              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA4                                                                                                                                                         | 5                        | 11              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA5                                                                                                                                                         | 4                        | 10              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA6                                                                                                                                                         | 16                       | 29              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA7                                                                                                                                                         | 22                       | 28              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA8                                                                                                                                                         | 32                       | 50              | 0           | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) or |  |  |  |  |

| PMA9                                                                                                                                                         | 31                       | 49              | 0           | TTL/ST         | Address/Data (Multiplexed Master modes)                  |  |  |  |  |

| PMA10                                                                                                                                                        | 28                       | 42              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA11                                                                                                                                                        | 27                       | 41              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA12                                                                                                                                                        | 24                       | 35              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA13                                                                                                                                                        | 23                       | 34              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA14                                                                                                                                                        | 45                       | 71              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA15                                                                                                                                                        | 44                       | 70              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMCS1                                                                                                                                                        | 45                       | 71              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMCS2                                                                                                                                                        | 44                       | 70              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMD0                                                                                                                                                         | 60                       | 93              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD1                                                                                                                                                         | 61                       | 94              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD2                                                                                                                                                         | 62                       | 98              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD3                                                                                                                                                         | 63                       | 99              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD4                                                                                                                                                         | 64                       | 100             | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD5                                                                                                                                                         | 1                        | 3               | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD6                                                                                                                                                         | 2                        | 4               | I/O         | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) o  |  |  |  |  |

| PMD7                                                                                                                                                         | 3                        | 5               | I/O         | TTL/ST         | Address/Data (Multiplexed Master modes)                  |  |  |  |  |

| PMD8                                                                                                                                                         | _                        | 90              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD9                                                                                                                                                         |                          | 89              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD10                                                                                                                                                        | _                        | 88              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD11                                                                                                                                                        | _                        | 87              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD12                                                                                                                                                        | —                        | 79              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMD13                                                                                                                                                        | —                        | 80              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMD14                                                                                                                                                        | —                        | 83              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMD15                                                                                                                                                        | —                        | 84              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMRD                                                                                                                                                         | 53                       | 82              | 0           | —              | Parallel Master Port Read Strobe                         |  |  |  |  |

| PMWR                                                                                                                                                         | 52                       | 81              | 0           | —              | Parallel Master Port Write Strobe                        |  |  |  |  |

| VBUS <sup>(2)</sup>                                                                                                                                          | 34                       | 54              | Ι           | Analog         | USB Bus Power Monitor                                    |  |  |  |  |

| •                                                                                                                                                            | CMOS = CM<br>ST = Schmit | t Trigger inp   | ut with (   | CMOS level     | ls TTL = TTL input buffer P = Power                      |  |  |  |  |

| <ul> <li>Note 1: This pin is only available on devices without a USB module.</li> <li>2: This pin is only available on devices with a USB module.</li> </ul> |                          |                 |             |                |                                                          |  |  |  |  |

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

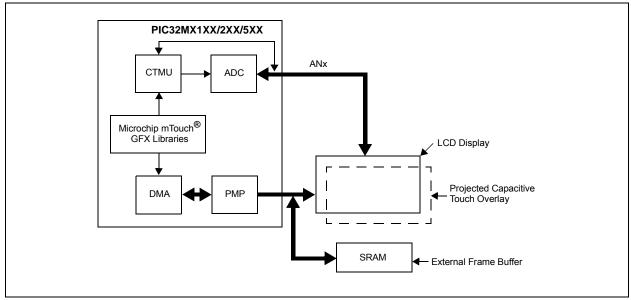

# FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

# 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX1XX/2XX/5XX 64/100-pin devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX1XX/2XX/5XX 64/100-pin devices, the Flash page size is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 |                   | —                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | _                 | _                 | _                 | _                 |                  | —                |

## REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

**Note:** While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                 |                   |                   | _                 |                  | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 |                   |                   | _                 |                  | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | _                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | —                | VBUSVDIE         |

# REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | dable bit W = Writable bit |                      | ead as '0'         |

|-------------------|----------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt enabled

- 0 = ID interrupt disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt enabled

- 0 = 1 millisecond timer interrupt disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt enabled

- 0 = Line state interrupt disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt enabled

- 0 = ACTIVITY interrupt disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt enabled

- 0 = Session valid interrupt disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt enabled

- 0 = B-session end interrupt disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt enabled

- 0 = A-VBUS valid interrupt disabled

#### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

| 51.24        |                   | _                 | _                 | _                 | _                 | _                 | _                     | —                       |

| 23:16        | U-0                   | U-0                     |

| 23.10        |                   | _                 | _                 | _                 | _                 | _                 | _                     | —                       |

| 15:8         | U-0                   | U-0                     |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                       |

|              | R/W-0                 | R/W-0                   |

| 7:0 5        | STALLIE           | LIE ATTACHIE F    | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              |                   |                   |                   |                   | IRNIE             |                   |                       | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       | 1 = STALL interrupt enabled                   |

|       | 0 = STALL interrupt disabled                  |

### bit 6 **ATTACHIE:** ATTACH Interrupt Enable bit 1 = ATTACH interrupt enabled

0 = ATTACH interrupt disabled

#### bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt enabled

- 0 = RESUME interrupt disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt enabled

- 0 = Idle interrupt disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt enabled

- 0 = TRNIF interrupt disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt enabled

- 0 = SOFIF interrupt disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt enabled

- 0 = USB Error interrupt disabled

- bit 0 **URSTIE:** USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt enabled

- 0 = URSTIF interrupt disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt enabled

- 0 = DATTCHIF interrupt disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 |                   | _                 |                   |                  |                  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 |                   | -                 |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 |                   | -                 |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | _                 |                   |                   | FRMH<2:0>        |                  |

### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

## Legend:

| J                 |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

- 0001 = OUT (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 1101 = SETUP (TX) token type transaction

- Note: All other values are reserved and must not be used.

- bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

**Note 1:** All other values are reserved and must not be used.

## TABLE 11-10: PORTE REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 | 0         |       |       |       |       |       |       |      | E    | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6400                        | ANSELE                          | 31:16     | —     | _     | —     | —     | _     | —     |      | -    | —            | —            | —            | —            | _            | _            |              | _            | 0000          |

| 0400                        | ANSELE                          | 15:0      | —     | -     |       | —     | -     | _     |      |      | ANSELE7      | ANSELE6      | ANSELE5      | ANSELE4      | _            | ANSELE2      |              | _            | 03F4          |

| 6410                        | TRISE                           | 31:16     | _     | _     |       | _     | _     | _     |      |      | _            |              |              |              | _            | _            |              | -            | 0000          |

| 0410                        | TRIBL                           | 15:0      | —     | _     | —     | —     | _     | —     | _    | _    | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | OOFF          |

| 6420                        | PORTE                           | 31:16     | _     | _     |       | _     | _     | _     |      |      | _            |              |              |              | _            | _            |              | -            | 0000          |

| 0420                        | FORTE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 6440                        | LATE                            | 31:16     | _     | -     | -     | _     | -     | _     |      |      | _            |              | -            |              | _            | -            |              | _            | 0000          |

| 0440                        | LAIL                            | 15:0      | —     | -     |       | —     | -     | _     |      |      | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 6440                        | ODCE                            | 31:16     | —     | -     |       | —     | -     | _     |      |      | -            |              |              |              | _            | _            |              | -            | 0000          |

| 0440                        | ODOL                            | 15:0      | —     | _     | —     | —     | _     | —     | —    | -    | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 6450                        | CNPUE                           | 31:16     | —     | _     | —     | —     | _     | —     | —    | -    | —            | _            | _            | —            | _            | —            | —            | —            | 0000          |

| 0400                        |                                 | 15:0      | —     | —     | —     | —     | —     | —     | _    | _    | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPDE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 6460                        | CNPDE                           | 31:16     | —     | —     | _     | —     | —     | —     |      | _    |              |              |              |              | —            | —            | _            |              | 0000          |

| 0400                        | ONT DE                          | 15:0      | —     | —     | _     | —     | —     | —     |      | _    | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 6470                        | CNCONE                          | 31:16     | —     | —     | —     | —     | —     | —     |      | _    |              |              |              |              | —            | —            |              |              | 0000          |

| 0470                        | ONCOME                          | 15:0      | ON    | —     | SIDL  | —     | —     | —     |      | _    |              |              |              |              | —            | —            |              |              | 0000          |

| 6480                        | CNENE                           | 31:16     | —     | —     | —     | —     | —     | —     | _    | _    | —            | _            | _            | _            | —            | —            | _            | —            | 0000          |

| 0700                        | ONLINE                          | 15:0      | —     | —     | —     | —     | —     | —     | _    | _    | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | 0000          |

|                             |                                 | 31:16     | —     | _     | —     | —     | _     | —     |      |      | —            | -            | -            | 1            | —            | —            |              | —            | 0000          |

| 6490                        | CNSTATE                         | 15:0      | —     | _     |       | _     | _     | _     |      |      | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | —                 | -                    | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | _                 | —                 | _                    | —                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

### **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

### bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

# **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

# REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit</li> <li>1 = High-Speed mode – 4x baud clock enabled</li> <li>0 = Standard Speed mode – 16x baud clock enabled</li> </ul>                                                                                          |

| bit 2-1 | <pre>PDSEL&lt;1:0&gt;: Parity and Data Selection bits 11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity</pre>                                                                                  |

| bit 0   | STSEL: Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                              |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## 19.2 Timing Diagrams

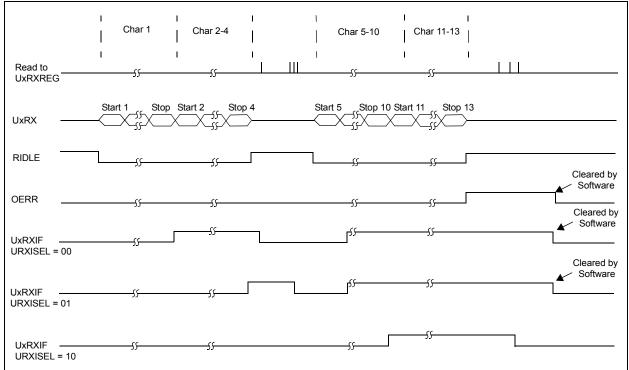

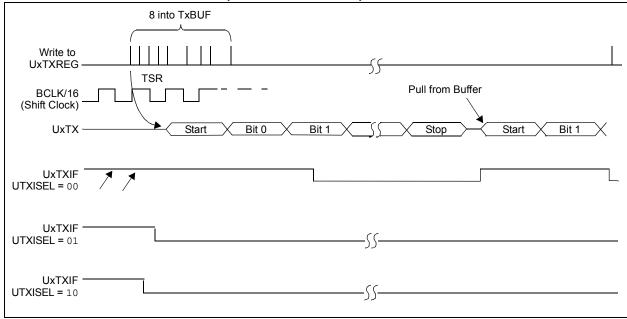

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

# FIGURE 19-2: UART RECEPTION

### FIGURE 19-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

#### 22.1 **Control Registers**

# TABLE 22-1: ADC REGISTER MAP

| ess                         |                             | Ċ,            |                  |                  |                  |                  |                  |                  |                 | Bi              | ts              |                 |                 |                 |                 |                 |                 |                 | 6          |

|-----------------------------|-----------------------------|---------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name            | Bit Range     | 31/15            | 30/14            | 29/13            | 28/12            | 27/11            | 26/10            | 25/9            | 24/8            | 23/7            | 22/6            | 21/5            | 20/4            | 19/3            | 18/2            | 17/1            | 16/0            | All Resets |

|                             | AD1CON1 <sup>(1)</sup>      | 31:16         | —                | -                | —                | —                | _                |                  | —               | —               |                 | —               | —               | —               | _               | —               | _               | _               | 0000       |

| 3000                        | ADICONT                     | 15:0          | ON               |                  | SIDL             | —                | —                |                  | FORM<2:0>       | •               |                 | SSRC<2:0>       | <b>.</b>        | CLRASAM         | —               | ASAM            | SAMP            | DONE            | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup>      | 31:16         | —                | —                | —                | —                | _                | _                | —               | _               | _               | _               | —               | —               | —               | —               | —               | —               | 0000       |

|                             |                             | 15:0          | · ·              | VCFG<2:0>        | ><br>            | OFFCAL           |                  | CSCNA            | —               |                 | BUFS            |                 |                 | SMPI            | <3:0>           |                 | BUFM            | ALTS            | 0000       |

| 9020                        | AD1CON3(1)                  | 31:16         | _                | _                | —                | —                | —                | _                | —               |                 | —               | —               | —               | —               | —               | —               | —               | —               | 0000       |

|                             |                             | 15:0          | ADRC             | —                | _                |                  |                  | SAMC<4:0         | >               |                 | 0110114         |                 |                 | ADCS            |                 | = 0 (2)         |                 |                 | 0000       |

| 9040                        | AD1CHS(1)                   | 31:16         | CH0NB            |                  |                  |                  | CH0SB            | <5:0>(2)         |                 |                 | CH0NA           |                 |                 |                 | CH0SA           | <5:0>(2)        |                 |                 | 0000       |

|                             |                             | 15:0          | -                | -                | -                | —<br>CSSL28      | -                | —<br>CSSL26      | -               | —<br>CSSL24     | -               | —<br>CSSL22     |                 | CSSL20          | —<br>CSSL19     | —<br>CSSL18     | —<br>CSSL17     | -               | 0000       |

| 9050                        | AD1CSSL <sup>(1,3)</sup>    | 31:16<br>15:0 | CSSL31<br>CSSL15 | CSSL30<br>CSSL14 | CSSL29<br>CSSL13 | CSSL28<br>CSSL12 | CSSL27<br>CSSL11 | CSSL26<br>CSSL10 | CSSL25<br>CSSL9 | CSSL24<br>CSSL8 | CSSL23<br>CSSL7 | CSSL22<br>CSSL6 | CSSL21<br>CSSL5 | CSSL20<br>CSSL4 | CSSL19<br>CSSL3 | CSSL18<br>CSSL2 | CSSL17<br>CSSL1 | CSSL16<br>CSSL0 | 0000       |

|                             |                             |               | -                | C33L14           | C33L13           | -                |                  | C33L10           | -               | COOLO           | 033L7           | COOLO           |                 | -               |                 | CSSL2           | CSSL49          | CSSL48          | 0000       |

| 9060                        | 060 AD1CSSL2 <sup>(1)</sup> | 31:16<br>15:0 | CSSL47           | CSSL46           | CSSL45           | CSSL44           | CSSL43           | CSSL42           | CSSL41          | CSSL40          | CSSL39          | CSSL38          | CSSL37          | CSSL36          | CSSL35          | CSSL34          | CSSL33          | CSSL32          | 0000       |

|                             |                             | 31:16         | 000211           | OCCLIC           | OCCL 10          | OCCLI            | OCCLIC           | 000212           |                 |                 |                 |                 | 000201          | 000200          | CCCLCC          | 000201          | 000200          | 000202          | 0000       |

| 9070                        | ADC1BUF0                    | 15:0          |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 0      | (ADC1BUF        | 0<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

|                             |                             | 31:16         |                  |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | 0000       |

| 9080                        | ADC1BUF1                    | 15:0          |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 1      | (ADC1BUF        | 1<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

| 9090                        | ADC1BUF2                    | 31:16         |                  |                  |                  |                  |                  |                  |                 | ult Word 2      |                 | 2~21.0~)        |                 |                 |                 |                 |                 |                 | 0000       |

| 9090                        | ADCIBUEZ                    | 15:0          |                  |                  |                  |                  |                  |                  | ADC Res         |                 | (ADC IBUF       | 2~31.0~)        |                 |                 |                 |                 |                 |                 | 0000       |

| 90A0                        | ADC1BUF3                    | 31:16         |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 3      |                 | 3<31.0>)        |                 |                 |                 |                 |                 |                 | 0000       |

| 00710                       | 7.0010010                   | 15:0          |                  |                  |                  |                  |                  |                  | 7.201.00        |                 | (//201201       | 0.01.0.)        |                 |                 |                 |                 |                 |                 | 0000       |

| 90B0                        | ADC1BUF4                    | 31:16         |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 4      | (ADC1BUF        | 4<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

|                             |                             | 15:0          |                  |                  |                  |                  |                  |                  |                 |                 |                 | /               |                 |                 |                 |                 |                 |                 | 0000       |

| 90C0                        | ADC1BUF5                    | 31:16         |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 5      | (ADC1BUF        | 5<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

|                             |                             | 15:0          |                  |                  |                  |                  |                  |                  |                 |                 | -               |                 |                 |                 |                 |                 |                 |                 | 0000       |

| 90D0                        | ADC1BUF6                    | 31:16<br>15:0 |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 6      | (ADC1BUF        | 6<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

|                             |                             | 31:16         |                  |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | 0000       |

| 90E0                        | ADC1BUF7                    | 15:0          |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 7      | (ADC1BUF        | 7<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

|                             |                             | 31:16         |                  |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | 0000       |

| 90F0                        | ADC1BUF8                    | 15:0          |                  |                  |                  |                  |                  |                  | ADC Res         | ult Word 8      | (ADC1BUF        | 8<31:0>)        |                 |                 |                 |                 |                 |                 | 0000       |

| L                           |                             |               |                  |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |            |

Legend: 3:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV registers" for details. Note 1: For 64-pin devices, the MSB of these bits is not available. 2:

For 64-pin devices, only the CSSL30:CSSL0 bits are available.

DS60001290D-page 233

Preliminary

## REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER (CONTINUED)

```

bit 21-16 CH0SA<5:0>: Positive Input Select bits for Sample A Multiplexer Setting

For 64-pin devices:

011110 = Channel 0 positive input is Open<sup>(1)</sup>

011101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

011100 = Channel 0 positive input is IVREF<sup>(3)</sup>

011011 = Channel 0 positive input is AN27

000001 = Channel 0 positive input is AN1

000000 = Channel 0 positive input is AN0

For 100-pin devices:

110010 = Channel 0 positive input is Open<sup>(1)</sup>

110001 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

110000 = Channel 0 positive input is IVREF<sup>(3)</sup>

101111 = Channel 0 positive input is AN47

0000001 = Channel 0 positive input is AN1

0000000 = Channel 0 positive input is AN0

bit 15-0

Unimplemented: Read as '0'

```

- Note 1: This selection is only used with CTMU capacitive and time measurement.

- 2: See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

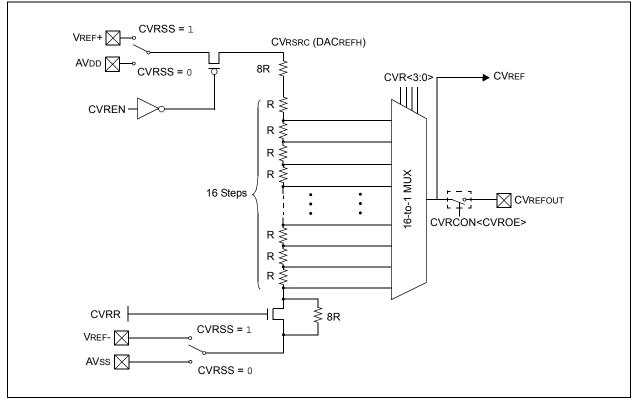

# 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|           | Indicates the status of Edge 1 and can be written to control edge source                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|           | 1 = Edge 1 has occurred                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|           | 0 = Edge 1 has not occurred                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|           | 1 = Input is edge-sensitive                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|           | 0 = Input is level-sensitive                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|           | 1 = Edge 2 programmed for a positive edge response                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|           | 0 = Edge 2 programmed for a negative edge response                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| bit 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|           | 1111 = IC4 Capture Event is selected                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|           | 1110 = C2OUT pin is selected                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|           | 1101 = C1OUT pin is selected                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|           | 1100 = PBCLK clock is selected                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|           | 1011 = IC3 Capture Event is selected                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|           | 1010 = IC2 Capture Event is selected                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|           | 1001 = IC1 Capture Event is selected                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|           | 1000 = CTED13 pin is selected<br>0111 = CTED12 pin is selected                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|           | 0110 = CTED12 pin is selected                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           | 0101 = CTED10 pin is selected                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           | 0100 = CTED9 pin is selected                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|           | 0011 = CTED1 pin is selected                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|           | 0010 = CTED2 pin is selected                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|           | 0001 = OC1 Compare Event is selected                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|           | 0000 = Timer1 Event is selected                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| bit 17-16 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| bit 15    | ON: ON Enable bit                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|           | 1 = Module is enabled                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|           | 0 = Module is disabled                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|           | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           | 0 = Continue module operation in Idle mode                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| bit 12    | TGEN: Time Generation Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|           | 1 = Enables edge delay generation                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|           | 0 = Disables edge delay generation                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| bit 11    | EDGEN: Edge Enable bit                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|           | 1 = Edges are not blocked                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|           | 0 = Edges are blocked                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Note 1:   | When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.                                                                                                                                                                                                    |  |  |  |  |  |  |

| 2:        | The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion                                                                                                                                                                                                               |  |  |  |  |  |  |

|           | cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor |  |  |  |  |  |  |

|           | array.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| -         |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

## TABLE 32-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS | TICS                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |  |