Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f064ht-i-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| NOTES: |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

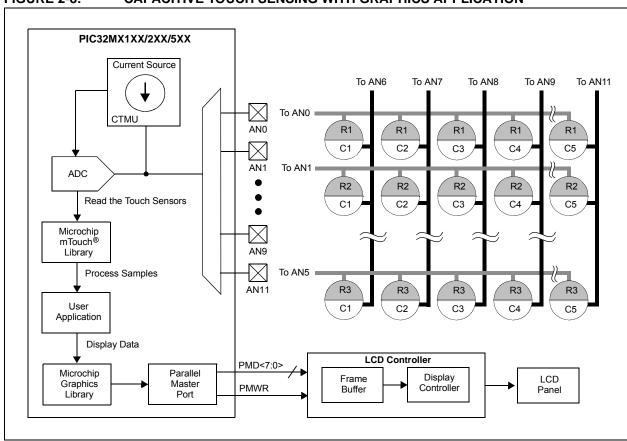

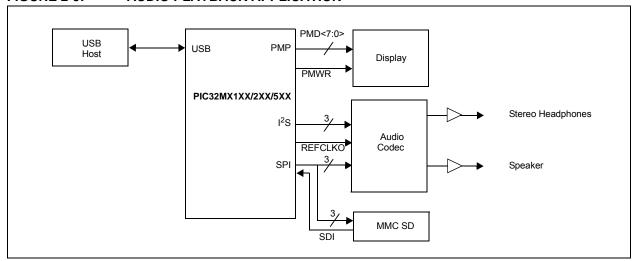

# 2.10 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-8, Figure 2-9, and Figure 2-10.

FIGURE 2-8: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

#### FIGURE 2-9: AUDIO PLAYBACK APPLICATION

### 4.0 MEMORY ORGANIZATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "**Memory Organization**" (DS60001115) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX/5XX 64/100-pin devices to execute from data memory.

The key features include:

- · 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

### 4.1 Memory Layout

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX/5XX 64/ 100-pin devices are illustrated in Figure 4-1 through Figure 4-4.

#### REGISTER 6-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | NVMDATA<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00:40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | NVMDATA<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

### REGISTER 6-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | 31:24 NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMSRCADDR<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                         |                   |                   | NVMSRCA           | ADDR<15:8>        |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                         |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

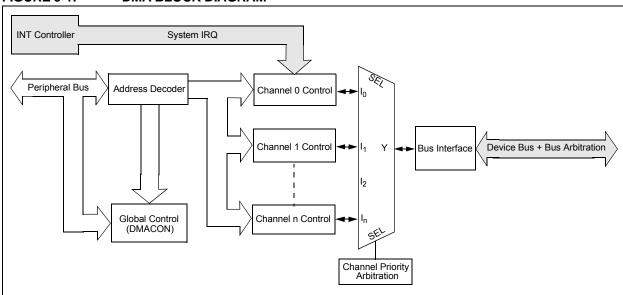

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 31.** "**Direct Memory Access (DMA) Controller**" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

The following are some of the key features of the DMA controller module:

- · Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- · Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- · Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt)

DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

#### FIGURE 9-1: DMA BLOCK DIAGRAM

TABLE 11-16: PORTG REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 | 0         |       |       |       |       |       |       |              | Ві           | ts           |              |      |      |                    |                    |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1 | 16/0 | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    |      | 0000          |

| 0000                        | ANOLLO                          | 15:0      | -     | _     | _     | _     | _     | -     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | _    | _    | _                  | _                  | _    | -    | 03C0          |

| 6610                        | TRISG                           | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            |      | _    | _                  | _                  |      | _    | 0000          |

| 0010                        | 111100                          | 15:0      | _     | _     | _     | _     | _     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | _    | TRISG3             | TRISG2             | _    | _    | 03CC          |

| 6620                        | PORTG                           | 31:16     |       | _     | _     | _     | _     |       | _            | _            | _            | _            |      | _    | -                  | -                  |      |      | 0000          |

| 0020                        | 1 01110                         | 15:0      | _     | _     | _     | _     | _     | _     | RG9          | RG8          | RG7          | RG6          | _    | _    | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | _    | _    | xxxx          |

| 6630                        | LATG                            | 31:16     |       | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    |      | 0000          |

| -                           | 27.1.0                          | 15:0      | 1     | _     | _     | _     | _     | -     | LATG9        | LATG8        | LATG7        | LATG6        | _    | _    | LATG3              | LATG2              | _    | -    | xxxx          |

| 6640                        | ODCG                            | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0010                        | 0000                            | 15:0      | _     | _     | _     | _     | _     | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | _    | _    | 0000          |

| 6650                        | CNPUG                           | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0000                        | 0111 00                         | 15:0      | _     | _     | _     | _     | _     | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | CNPUG3             | CNPUG2             | _    | _    | 0000          |

| 6660                        | CNPDG                           | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0000                        | 0111 00                         | 15:0      | _     | _     | _     | _     | _     | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | _    | CNPDG3             | CNPDG2             | _    | _    | 0000          |

| 6670                        | CNCONG                          | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0070                        | 01100110                        | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 6680                        | CNENG                           | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            |      | _    | _                  | _                  |      | _    | 0000          |

| 0000                        | ONLINO                          | 15:0      | _     | _     | _     | _     | _     | _     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       |      | _    | CNIEG3             | CNIEG2             |      | _    | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            |              | _            |      |      | _                  | _                  |      |      | 0000          |

| 6690                        | CNSTATG                         | 15:0      |       |       | -     |       | _     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | -    | _    | CN<br>STATG3       | CN<br>STATG2       | -    | _    | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

2: This bit is only available on devices without a USB module.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| PIC32WX1XX/2XX/5XX 64/100-PIN FAWILY |  |  |  |  |  |  |  |  |  |

|--------------------------------------|--|--|--|--|--|--|--|--|--|

| NOTES:                               |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

| PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY |  |  |  |  |  |  |  |  |  |

|--------------------------------------|--|--|--|--|--|--|--|--|--|

| NOTES:                               |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

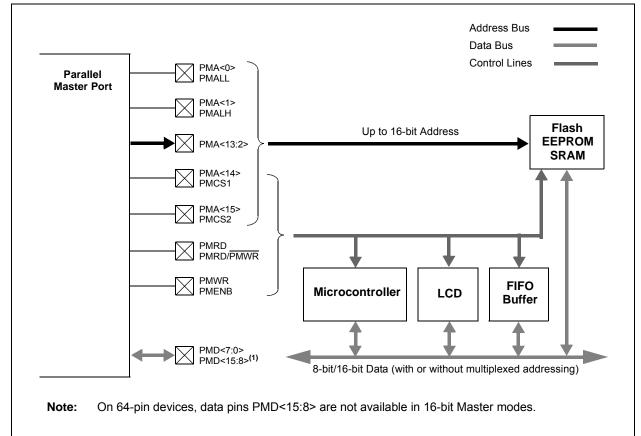

# 20.0 PARALLEL MASTER PORT (PMP)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 13. "Parallel Master Port (PMP)"** (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PMP is a parallel 8-bit or 16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. The following are the key features of the PMP module:

- · 8-bit.16-bit interface

- · Up to 16 programmable address lines

- · Up to two Chip Select lines

- Programmable strobe options:

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Selectable polarity

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- Programmable polarity on control signals

- · Parallel Slave Port support:

- Legacy addressable

- Address support

- · Read and Write 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- · Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- · Freeze option for in-circuit debugging

**Note:** On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

```

WAITM<3:0>: Data Read/Write Strobe Wait States bits(1)

1111 = Wait of 16 TPB

0001 = Wait of 2 TPB

0000 = Wait of 1 TPB (default)

WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits(1)

bit 1-0

11 = Wait of 4 TPB

10 = Wait of 3 TPB

01 = Wait of 2 TPB

00 = Wait of 1 TPB (default)

For Read operations:

```

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- Note 1: Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

#### **REGISTER 22-2:** AD1CON2: ADC CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 13.6         |                   | VCFG<2:0>         |                   | OFFCAL            | _                 | CSCNA             | _                | _                |

| 7:0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | BUFS              |                   |                   | SMP               | I<3:0>            | BUFM              | ALTS             |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |  |  |  |  |

|-----|--------------------|--------------------|--|--|--|--|

| 000 | AVDD               | AVss               |  |  |  |  |

| 001 | External VREF+ pin | AVss               |  |  |  |  |

| 010 | AVdd               | External VREF- pin |  |  |  |  |

| 011 | External VREF+ pin | External VREF- pin |  |  |  |  |

| 1xx | AVDD               | AVss               |  |  |  |  |

bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

bit 11 Unimplemented: Read as '0'

bit 10 **CSCNA:** Input Scan Select bit

1 = Scan inputs

0 = Do not scan inputs

bit 9-8 Unimplemented: Read as '0'

bit 7 BUFS: Buffer Fill Status bit Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

bit 6 Unimplemented: Read as '0'

bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

bit 1 BUFM: ADC Result Buffer Mode Select bit

1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

bit 0 **ALTS:** Alternate Input Sample Mode Select bit

> 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

0 = Always use Sample A input multiplexer settings

TABLE 23-1: CAN1 REGISTER SUMMARY (CONTINUED)

| ess                         |                                 | 0             |                             |                          |       |       |       |           |          | Bits      | 1    |        |        |       |          |            |          |                | ·s         |

|-----------------------------|---------------------------------|---------------|-----------------------------|--------------------------|-------|-------|-------|-----------|----------|-----------|------|--------|--------|-------|----------|------------|----------|----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                       | 30/14                    | 29/13 | 28/12 | 27/11 | 26/10     | 25/9     | 24/8      | 23/7 | 22/6   | 21/5   | 20/4  | 19/3     | 18/2       | 17/1     | 16/0           | All Resets |

| B340                        |                                 | 31:16<br>15:0 |                             | C1FIFOBA<31:0> 0000 0000 |       |       |       |           |          |           |      |        |        |       |          |            |          |                |            |

| P250                        | C1FIFOCONn                      | 31:16         | _                           | _                        | _     | _     | -     | _         | _        | _         | -    | _      | _      |       |          | FSIZE<4:0> |          |                | 0000       |

| B330                        | (n = 0-15)                      | 15:0          | _                           | FRESET                   | UINC  | DONLY | -     | _         | _        | _         | TXEN | TXABAT | TXLARB | TXERR | TXREQ    | RTREN      | TXPRI    | <1:0>          | 0000       |

| B360                        | C1EIEOINIT <sub>2</sub>         | 31:16         | _                           | _                        | _     | _     | -     | TXNFULLIE | TXHALFIE | TXEMPTYIE | _    | _      | _      | _     | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| D300                        | (n = 0-15)                      | 15:0          | _                           | -                        | _     | -     | _     | TXNFULLIF | TXHALFIF | TXEMPTYIF | _    | _      | -      | _     | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000       |

| B370                        | C1FIFOUAn<br>(n = 0-15)         | 31:16<br>15:0 | C1FIFOUA<31:0> 0000<br>0000 |                          |       |       |       |           |          |           |      |        |        |       |          |            |          |                |            |

| B380                        | C1FIFOCIn                       | 31:16         | _                           | _                        | _     | _     | 1     | _         | _        | _         | _    | _      | _      | _     | _        | _          | _        | _              | 0000       |

| D380                        | (n = 0-15)                      | 15:0          | _                           |                          |       |       |       |           |          |           |      |        |        |       |          |            |          |                |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = Length is 8 x TQ

.

000 = Length is 1 x TQ

bit 7-6 SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

11 = Length is 4 x TQ

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = Length is 1 x TQ

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

111111 = TQ = (2 x 64)/SYSCLK

111110 = TQ = (2 x 63)/SYSCLK

.

000001 = TQ = (2 x 2)/SYSCLK

000000 = TQ = (2 x 1)/SYSCLK

```

- **Note 1:** SEG2PH ≤ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

- 2: 3 Time bit sampling is not allowed for BRP < 2.

- 3:  $SJW \leq SEG2PH$ .

- 4: The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHA        | ARACTER   | ISTICS                                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industria $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |       |       |            |  |  |  |  |

|---------------|-----------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------|--|--|--|--|

| Param.<br>No. | Symbol    | Characteristics                                                  | Min.                                                                                                                                                                                                                                          | Тур. | Max.  | Units | Conditions |  |  |  |  |

| Operati       | ng Voltag | e                                                                |                                                                                                                                                                                                                                               |      |       |       |            |  |  |  |  |

| DC10          | VDD       | Supply Voltage (Note 2)                                          | 2.3                                                                                                                                                                                                                                           | _    | 3.6   | V     | _          |  |  |  |  |

| DC12          | VDR       | RAM Data Retention Voltage (Note 1)                              | 1.75                                                                                                                                                                                                                                          | -    | -     | V     | _          |  |  |  |  |

| DC16          | VPOR      | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                                                                                                                                                                                                          | _    | 2.1   | V     | _          |  |  |  |  |

| DC17          | SVDD      | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005                                                                                                                                                                                                                                       | _    | 0.115 | V/μs  | _          |  |  |  |  |

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

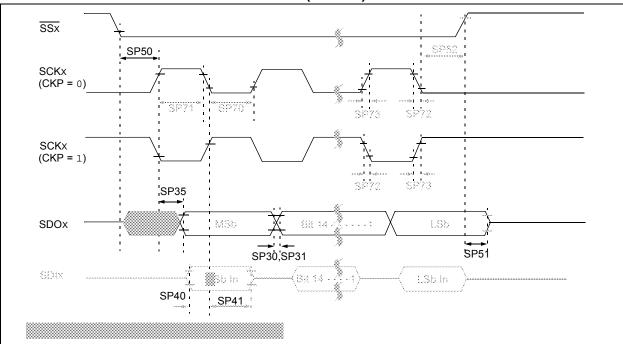

FIGURE 31-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 31-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS             | TICS                                            | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                     |      |       |                    |  |  |  |

|---------------|-----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                  | Min.                                                                                                                                                                                                                                           | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                    | Tsck/2                                                                                                                                                                                                                                         | _                   | _    | ns    | _                  |  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                   | Tsck/2                                                                                                                                                                                                                                         | _                   | _    | ns    | _                  |  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                            | _                                                                                                                                                                                                                                              | _                   | _    | ns    | See parameter DO32 |  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                            | _                                                                                                                                                                                                                                              | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)             | _                                                                                                                                                                                                                                              | _                   | _    | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)             | _                                                                                                                                                                                                                                              | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2DoV,             | SDOx Data Output Valid after                    | _                                                                                                                                                                                                                                              | _                   | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2doV              | SCKx Edge                                       |                                                                                                                                                                                                                                                | _                   | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge      | 10                                                                                                                                                                                                                                             |                     | -    | ns    | _                  |  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge       | 10                                                                                                                                                                                                                                             | _                   | _    | ns    | _                  |  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx Input                   | 175                                                                                                                                                                                                                                            | _                   | _    | ns    | _                  |  |  |  |

| SP51          | TssH2DoZ              | SSx ↑ to SDOx Output<br>High-Impedance (Note 3) | 5                                                                                                                                                                                                                                              | _                   | 25   | ns    | _                  |  |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                             | Tsck + 20                                                                                                                                                                                                                                      | _                   | _    | ns    | _                  |  |  |  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.

#### 32.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX/5XX 64/100-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 31.0 "40 MHz Electrical Characteristics"**, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 31.0** "**40 MHz Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX/5XX 64/100-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                   | 40°C to +85°C            |

|----------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                              | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                               | 0.3V to +4.0V            |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)         | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq$ 2.3V (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)      | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to Vusb3v3                                  | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                              | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                                | 300 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                         | 300 mA                   |

| Maximum output current sunk by any I/O pin                                       | 15 mA                    |

| Maximum output current sourced by any I/O pin                                    | 15 mA                    |

| Maximum current sunk by all ports                                                | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                    | 200 mA                   |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.

TABLE 32-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Indus |                        |      | erwise stated) |            |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|----------------|------------|--|--|

| Parameter<br>No.                                                                                                                                                                     | Typical <sup>(2)</sup> | Max. | Units          | Conditions |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1)                                                                                                                       |                        |      |                |            |  |  |

| MDC34a                                                                                                                                                                               | 9.5                    | 24   | mA             | 50 MHz     |  |  |

- **Note 1:** The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- **2:** Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 32-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

|                                   |                        |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |            |                                                 |  |  |

|-----------------------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max. | Units                                                                                                                                                                  | Conditions |                                                 |  |  |

| Power-Down Current (IPD) (Note 1) |                        |      |                                                                                                                                                                        |            |                                                 |  |  |

| MDC40k                            | 50                     | 150  | μА                                                                                                                                                                     | -40°C      | Base Power-Down Current                         |  |  |

| MDC40n                            | 250                    | 650  | μΑ                                                                                                                                                                     | +85°C      | Base Fower-Down Current                         |  |  |

| Module Differential Current       |                        |      |                                                                                                                                                                        |            |                                                 |  |  |

| MDC41e                            | 15                     | 55   | μА                                                                                                                                                                     | 3.6V       | Watchdog Timer Current: ∆IWDT (Note 3)          |  |  |

| MDC42e                            | 34                     | 55   | μА                                                                                                                                                                     | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |

| MDC43d                            | 1100                   | 1800 | μА                                                                                                                                                                     | 3.6V       | ADC: ∆IADC (Notes 3,4)                          |  |  |

- **Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The Δ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

| PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY |  |  |  |  |  |

|--------------------------------------|--|--|--|--|--|

| NOTES:                               |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

|                                      |  |  |  |  |  |

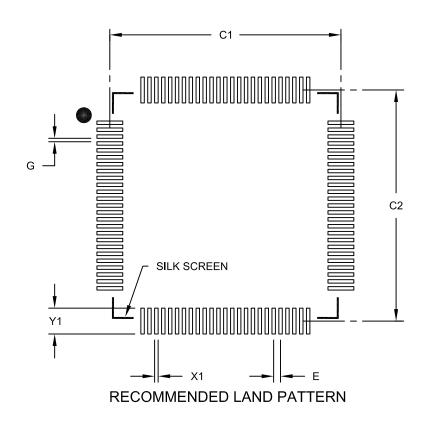

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units            | MILLIMETERS |       |      |  |

|---------------------------|------------------|-------------|-------|------|--|

| Dimension                 | Dimension Limits |             |       | MAX  |  |

| Contact Pitch             | Е                | 0.40 BSC    |       |      |  |

| Contact Pad Spacing       | C1               |             | 13.40 |      |  |

| Contact Pad Spacing       | C2               |             | 13.40 |      |  |

| Contact Pad Width (X100)  | X1               |             |       | 0.20 |  |

| Contact Pad Length (X100) | Y1               |             |       | 1.50 |  |

| Distance Between Pads     | G                | 0.20        |       |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B