Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f064ht-v-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

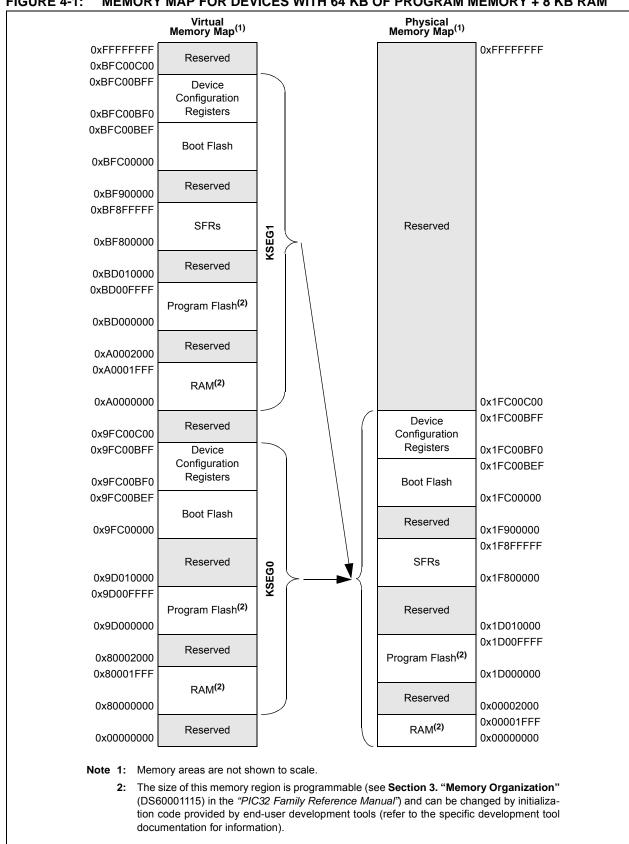

#### FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 64 KB OF PROGRAM MEMORY + 8 KB RAM

| Interrupt Source <sup>(1)</sup> IRQ # Vector Interrupt Bit Location |       |      |               |              |              |              |           |  |

|---------------------------------------------------------------------|-------|------|---------------|--------------|--------------|--------------|-----------|--|

|                                                                     | IRQ # | #    | Flag          | Enable       | Priority     | Sub-priority | Interrupt |  |

| CNA – PORTA Input Change Interrupt                                  | 44    | 33   | IFS1<12>      | IEC1<12>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| CNB – PORTB Input Change Interrupt                                  | 45    | 33   | IFS1<13>      | IEC1<13>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| CNC – PORTC Input Change Interrupt                                  | 46    | 33   | IFS1<14>      | IEC1<14>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| CND – PORTD Input Change Interrupt                                  | 47    | 33   | IFS1<15>      | IEC1<15>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| CNE – PORTE Input Change Interrupt                                  | 48    | 33   | IFS1<16>      | IEC1<16>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| CNF – PORTF Input Change Interrupt                                  | 49    | 33   | IFS1<17>      | IEC1<17>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| CNG – PORTG Input Change Interrupt                                  | 50    | 33   | IFS1<18>      | IEC1<18>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |

| PMP – Parallel Master Port                                          | 51    | 34   | IFS1<19>      | IEC1<19>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |  |

| PMPE – Parallel Master Port Error                                   | 52    | 34   | IFS1<20>      | IEC1<20>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |  |

| SPI2E – SPI2 Fault                                                  | 53    | 35   | IFS1<21>      | IEC1<21>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |  |

| SPI2RX – SPI2 Receive Done                                          | 54    | 35   | IFS1<22>      | IEC1<22>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |  |

| SPI2TX – SPI2 Transfer Done                                         | 55    | 35   | IFS1<23>      | IEC1<23>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |  |

| U2E – UART2 Error                                                   | 56    | 36   | IFS1<24>      | IEC1<24>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |  |

| U2RX – UART2 Receiver                                               | 57    | 36   | IFS1<25>      | IEC1<25>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |  |

| U2TX – UART2 Transmitter                                            | 58    | 36   | IFS1<26>      | IEC1<26>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |  |

| I2C2B – I2C2 Bus Collision Event                                    | 59    | 37   | IFS1<27>      | IEC1<27>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |  |

| I2C2S – I2C2 Slave Event                                            | 60    | 37   | IFS1<28>      | IEC1<28>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |  |

| I2C2M – I2C2 Master Event                                           | 61    | 37   | IFS1<29>      | IEC1<29>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |  |

| U3E – UART3 Error                                                   | 62    | 38   | IFS1<30>      | IEC1<30>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |  |

| U3RX – UART3 Receiver                                               | 63    | 38   | IFS1<31>      | IEC1<31>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |  |

| U3TX – UART3 Transmitter                                            | 64    | 38   | IFS2<0>       | IEC2<0>      | IPC9<20:18>  | IPC9<17:16>  | Yes       |  |

| U4E – UART4 Error                                                   | 65    | 39   | IFS2<1>       | IEC2<1>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |  |

| U4RX – UART4 Receiver                                               | 66    | 39   | IFS2<2>       | IEC2<2>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |  |

| U4TX – UART4 Transmitter                                            | 67    | 39   | IFS2<3>       | IEC2<3>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |  |

| U5E – UART5 Error <sup>(2)</sup>                                    | 68    | 40   | IFS2<4>       | IEC2<4>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |  |

| U5RX – UART5 Receiver <sup>(2)</sup>                                | 69    | 40   | IFS2<5>       | IEC2<5>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |  |

| U5TX – UART5 Transmitter <sup>(2)</sup>                             | 70    | 40   | IFS2<6>       | IEC2<6>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |  |

| CTMU – CTMU Event <sup>(2)</sup>                                    | 71    | 41   | IFS2<7>       | IEC2<7>      | IPC10<12:10> | IPC10<9:8>   | Yes       |  |

| DMA0 – DMA Channel 0                                                | 72    | 42   | IFS2<8>       | IEC2<8>      | IPC10<20:18> | IPC10<17:16> | No        |  |

| DMA1 – DMA Channel 1                                                | 73    | 43   | IFS2<9>       | IEC2<9>      | IPC10<28:26> | IPC10<25:24> | No        |  |

| DMA2 – DMA Channel 2                                                | 74    | 44   | IFS2<10>      | IEC2<10>     | IPC11<4:2>   | IPC11<1:0>   | No        |  |

| DMA3 – DMA Channel 3                                                | 75    | 45   | IFS2<11>      | IEC2<11>     | IPC11<12:10> | IPC11<9:8>   | No        |  |

| CMP3 – Comparator 3 Interrupt                                       | 76    | 46   | IFS2<12>      | IEC2<12>     | IPC11<20:18> | IPC11<17:16> | No        |  |

| CAN1 – CAN1 Event                                                   | 77    | 47   | IFS2<13>      | IEC2<13>     | IPC11<28:26> | IPC11<25:24> | Yes       |  |

| SPI3E – SPI3 Fault                                                  | 78    | 48   | IFS2<14>      | IEC2<14>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |  |

| SPI3RX – SPI3 Receive Done                                          | 79    | 48   | IFS2<15>      | IEC2<15>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |  |

| SPI3TX – SPI3 Transfer Done                                         | 80    | 48   | IFS2<16>      | IEC2<16>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |  |

| SPI4E – SPI4 Fault <sup>(2)</sup>                                   | 81    | 49   | IFS2<17>      | IEC2<17>     | IPC12<12:10> | IPC12<9:8>   | Yes       |  |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>                           | 82    | 49   | IFS2<18>      | IEC2<18>     | IPC12<12:10> | IPC12<9:8>   | Yes       |  |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup>                          | 83    | 49   | IFS2<19>      | IEC2<19>     | IPC12<12:10> | IPC12<9:8>   | Yes       |  |

|                                                                     | •     | Lowe | st Natural Or | der Priority |              |              |           |  |

### TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |       |                     |                      |                       |                        |       |        |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------------|----------------------|-----------------------|------------------------|-------|--------|-------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |       |                     |                      |                       |                        |       |        | -     |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24.24 | U-0   | U-0                 | U-0                  | U-0                   | U-0                    | U-0   | U-0    | U-0   |

| 23:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31:24 | _     | —                   | _                    | —                     | _                      | —     | _      | —     |

| Image: Normal system         Image: No | 00:16 | U-0   | U-0                 | U-0                  | U-0                   | U-0                    | U-0   | U-0    | U-0   |

| 15:8         WR         WREN <sup>(1)</sup> WRERR <sup>(2)</sup> LVDERR <sup>(2)</sup> LVDSTAT <sup>(2)</sup> —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         _         _         _         _         _         _         _         _         _         _         _         _         _ <td>23.10</td> <td>—</td> <td>—</td> <td>—</td> <td>—</td> <td>_</td> <td>—</td> <td>—</td> <td>—</td>                                                                                                                                                                                                                                                                                                                                                                 | 23.10 | —     | —                   | —                    | —                     | _                      | —     | —      | —     |

| WR         WREN''         WRER''         LVDERR''         LVDSTAT''         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         Image: Main Main Main Main Main Main Main Main                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45.0  | R/W-0 | R/W-0               | R-0                  | R-0                   | -                      |       | U-0    | U-0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15:8  | WR    | WREN <sup>(1)</sup> | WRERR <sup>(2)</sup> | LVDERR <sup>(2)</sup> | LVDSTAT <sup>(2)</sup> |       | _      | —     |

| 1.0 — — — — NVMOP<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7:0   | U-0   | U-0                 | U-0                  | U-0                   | R/W-0                  | R/W-0 | R/W-0  | R/W-0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7:0   | _     | —                   | -                    | —                     |                        | NVMOF | P<3:0> |       |

#### **REGISTER 6-1:** NVMCON: PROGRAMMING CONTROL REGISTER

## Legend:

| Logonal           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------|

| bit 15    | WR: Write Control bit                                                                                             |

|           | This bit is writable when WREN = 1 and the unlock sequence is followed.                                           |

|           | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                             |

|           | 0 = Flash operation complete or inactive                                                                          |

| bit 14    | WREN: Write Enable bit <sup>(1)</sup>                                                                             |

|           | 1 = Enable writes to WR bit and enables LVD circuit                                                               |

|           | 0 = Disable writes to WR bit and disables LVD circuit                                                             |

|           | This is the only bit in this register reset by a device Reset.                                                    |

| bit 13    | WRERR: Write Error bit <sup>(2)</sup>                                                                             |

|           | This bit is read-only and is automatically set by hardware.                                                       |

|           | 1 = Program or erase sequence did not complete successfully                                                       |

|           | 0 = Program or erase sequence completed normally                                                                  |

| bit 12    | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(2)</sup>                                 |

|           | This bit is read-only and is automatically set by hardware.                                                       |

|           | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                              |

|           | 0 = Voltage level is acceptable for programming                                                                   |

| bit 11    | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(2)</sup>                               |

|           | This bit is read-only and is automatically set, and cleared, by hardware.                                         |

|           | 1 = Low-voltage event active                                                                                      |

|           | 0 = Low-voltage event NOT active                                                                                  |

| bit 10-4  | Unimplemented: Read as '0'                                                                                        |

| bit 3-0   | NVMOP<3:0>: NVM Operation bits                                                                                    |

|           | These bits are writable when WREN = $0$ .                                                                         |

|           | 1111 =Reserved                                                                                                    |

|           | •                                                                                                                 |

|           | •                                                                                                                 |

|           | •                                                                                                                 |

|           | 0111 = Reserved                                                                                                   |

|           | 0110 =No operation<br>0101 =Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected |

|           | 0100 =Page erase operation: erases page selected by NVMADDR, if it is not write-protected                         |

|           | 0011 =Row program operation: programs row selected by NVMADDR, if it is not write-protected                       |

|           | 0010 =No operation                                                                                                |

|           | 0001 =Word program operation: programs word selected by NVMADDR, if it is not write-protected                     |

|           | 0000 = No operation                                                                                               |

|           |                                                                                                                   |

| Note 1:   | This bit is cleared by any reset (i.e., POR, BOR, WDT, MCLR, SWR).                                                |

| -         |                                                                                                                   |

2: This bit is only cleared by setting NVMOP = 0000, and initiating a Flash WR operation or a POR. Any other kind of reset (i.e., BOR, WDT, MCLR) does not clear this bit.

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The PIC32MX1XX/2XX/5XX 64/100-pin oscillator system has the following modules and features:

- A Total of four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

NOTES:

# TABLE 11-8: PORTD REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | _     | —     | _     |               | —             | —            |              | _            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0000                        | THOLLD                          | 15:0      | —     | —     | —     | —     |               |               | —            | _            | _            | —            | _            |              | ANSELD3      | ANSELD2      | ANSELD1      | —            | 000E          |

| 6310                        | TRISD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | _            |              | —            | _            |              | —            |              |              | 0000          |

| 0310                        | TRIOD                           | 15:0      | —     | —     | —     | _     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | OFFF          |

| 5320                        | PORTD                           | 31:16     | —     | _     | _     | _     | _             | _             | —            | _            | _            | _            | _            |              | _            | —            |              | _            | 0000          |

| 3320                        | TORID                           | 15:0      | —     | —     | —     | _     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | 30 LATD                         | 31:16     | —     | —     | —     | _     | —             | —             | _            | _            | _            | —            | _            | -            | —            | —            | _            | _            | 0000          |

| 0330                        | LAID                            | 15:0      | -     | _     | _     | _     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0340                        | 0 ODCD                          | 15:0      | Ι     |       |       | -     | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 6350                        | CNPUD                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0330                        | CINFUD                          | 15:0      | -     | _     | _     | _     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 6360                        | CNPDD                           | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0300                        | CNFDD                           | 15:0      |       | _     | -     |       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 6270                        | CNCOND                          | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0370                        | CINCOIND                        | 15:0      | ON    | _     | SIDL  |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 6380                        | CNEND                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0300                        | CNEND                           | 15:0      | Ι     | -     | -     | Ι     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | _     | _             | _             | _            | —            | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | _     | _     | -     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

| PIC32MX170F512H DEVICES ONLY |                                 |           |       |       |       |       |       |       |      |      |      |              |              |              |              |              |              |              |               |

|------------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                          |                                 |           |       |       |       |       |       |       |      | Bi   | ts   |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#)  | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                         | TRISF                           | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | -    | —            |              | _            | _            | _            | —            | —            | 0000          |

| 0010                         | INIO                            | 15:0      | —     | _     | _     | _     | _     | _     | -    | _    | _    | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 007F          |

| 6520                         | PORTF                           | 31:16     | —     | —     | —     |       | —     | _     |      |      |      |              | —            |              | —            | —            | —            | —            | 0000          |

| 0020                         | 1 OKI                           | 15:0      | —     | —     | —     |       | —     | _     | _    |      |      | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                         | LATF                            | 31:16     | —     | _     | _     | _     | _     | _     | -    | _    | _    | —            | —            | -            | —            | _            | —            | —            | 0000          |

| 0000                         | L/(II                           | 15:0      | —     | —     | —     |       | —     | _     | _    |      |      | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                         | ODCF                            | 31:16     | —     | —     | —     | _     | —     | _     | —    |      | —    |              | —            | _            | —            | —            | —            | —            | 0000          |

| 0010                         | 0201                            | 15:0      | —     | —     | —     | _     | —     | _     | —    |      | —    | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                         | CNPUF                           | 31:16     | —     | _     | —     | —     | —     | —     | _    | —    | _    |              | —            | —            | —            | —            | —            | —            | 0000          |

| 0000                         |                                 | 15:0      | —     | _     | —     | —     | —     | —     | _    | —    | _    | CNPUF6       | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       |               |

| 6560                         | CNPDF                           | 31:16     | —     | —     | —     | _     | —     | _     | —    |      | —    |              | —            | —            | —            | —            | —            | —            | 0000          |

|                              | 0.11 51                         | 15:0      | —     | —     | —     | _     | —     | —     | -    | —    | -    | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                         | CNCONF                          | 31:16     | —     | —     | —     | _     | —     | —     | -    | —    | -    | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                              | 0.10011                         | 15:0      | ON    | —     | SIDL  | _     | —     | —     | -    | —    | -    | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 6580                         | CNENF                           | 31:16     | —     | —     | —     | _     | —     | —     | -    | —    | -    |              | —            | —            | —            | —            | —            | —            | 0000          |

|                              | -                               | 15:0      | —     | —     | —     | _     | —     | —     | -    | —    | -    | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                              |                                 | 31:16     | —     | —     | —     | —     | —     | —     | _    | —    | _    |              | —            | —            | —            | —            | —            | —            | 0000          |

| 6590                         | CNSTATF                         | 15:0      | —     | —     | —     | -     | —     | -     | -    | —    | _    | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

# TABLE 11-13: PORTF REGISTER MAP FOR PIC32MX120F064H, PIC32MX130F128H, PIC32MX150F256H, AND PIC32MX170F512H DEVICES ONLY

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

NOTES:

# 21.1 Control Registers

## TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | 6         |           |       |         |          |             |       |        | l            | Bits     |          |              |        |         |         |         |       | s         |

|-----------------------------|---------------------------------|-----------|-----------|-------|---------|----------|-------------|-------|--------|--------------|----------|----------|--------------|--------|---------|---------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14 | 29/13   | 28/12    | 27/11       | 26/10 | 25/9   | 24/8         | 23/7     | 22/6     | 21/5         | 20/4   | 19/3    | 18/2    | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON                          | 31:16     | _         | _     |         | —        | _           |       |        |              |          |          | CAL<         | 9:0>   |         |         |         |       | 0000      |

| 0200                        | RICCON                          | 15:0      | ON        | _     | SIDL    | —        | _           | _     |        | —            | RTSECSEL | RTCCLKON | _            | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000      |

| 0210                        | RTCALRM                         | 31:16     | —         | _     | _       | —        | _           | _     |        | —            | _        | —        | _            | _      | —       | —       | —       | —     | 0000      |

| 0210                        | RICALKI                         | 15:0      | ALRMEN    | CHIME | PIV     | ALRMSYNC | AMASK<3:0>  |       |        |              |          |          | ARP1         | ۲<7:0> |         |         |         | 0000  |           |

| 0220                        | RTCTIME                         | 31:16     | HR10<3:0> |       |         |          | HR01<3:0>   |       |        |              |          | MIN10<   | 3:0>         |        |         | MIN01   | <3:0>   |       | xxxx      |

| 0220                        |                                 | 15:0      |           | SEC1  | 0<3:0>  |          | SEC01<3:0>  |       |        | _            | —        | _        | _            | —      | —       | —       | —       | xx00  |           |

| 0230                        | RTCDATE                         | 31:16     |           | YEAR  | 10<3:0> |          | YEAR01<3:0> |       |        | MONTH10<3:0> |          |          | MONTH01<3:0> |        |         |         | xxxx    |       |           |

| 0230                        | RIODALE                         | 15:0      |           | DAY1  | 0<3:0>  |          |             | DAY01 | 1<3:0> |              | _        | —        | _            | _      |         | WDAY0   | 1<3:0>  |       | xx00      |

| 0240                        | ALRMTIME                        | 31:16     |           | HR10  | 0<3:0>  |          |             | HR01  | <3:0>  |              |          | MIN10<   | 3:0>         |        |         | MIN01   | <3:0>   |       | xxxx      |

| 0240                        |                                 | 15:0      |           | SEC1  | 0<3:0>  |          |             | SEC07 | 1<3:0> |              | _        | —        | _            | _      | —       | —       | —       | —     | xx00      |

| 0250                        | ALRMDATE                        | 31:16     | —         | —     | _       | —        | —           | -     | —      | —            |          | MONTH10  | <3:0>        |        |         | MONTH   | 01<3:0> |       | 00xx      |

| 0200                        |                                 | 15:0      |           | DAY1  | 0<3:0>  |          |             | DAY01 | 1<3:0> |              | —        | —        | _            | _      |         | WDAY0   | 1<3:0>  |       | xx0x      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| 31:24         U-0         U-0         U-0         U-0         U-0         U-0         R/W-0         R/W-0 |       |                         |          |       |       |                        |         |                        |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|----------|-------|-------|------------------------|---------|------------------------|------------------|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _     | -                       |          |       |       |                        |         |                        | Bit<br>24/16/8/0 |

| -         -         -         -         -         CAL<9:8>           23:16         RW-0         U-0                                                                       | 21.24 | U-0                     | U-0      | U-0   | U-0   | U-0                    | U-0     | R/W-0                  | R/W-0            |

| 23:16         CAL<7:0>           15:8         R/W-0         U-0         R/W-0         U-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R/W-0         R/W-0         R-0         R/W-0         R/W-0         R/W-0         R-0         R/W-0                                                       | 31.24 | —                       | —        | _     | —     | —                      | —       | CAL<9                  | ):8>             |

| CAL<7:0>           15:8         R/W-0         U-0         R/W-0         U-0         U-0         U-0         U-0         U-0           15:8         R/W-0         R-0         SIDL         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td>22.16</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td>                        | 22.16 | R/W-0                   | R/W-0    | R/W-0 | R/W-0 | R/W-0                  | R/W-0   | R/W-0                  | R/W-0            |

| 15:8         ON <sup>(1,2)</sup> —         SIDL         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         #         #         #         #         #         #         #         #                                                                                                                                                               | 23.10 |                         |          |       | CAL<  | :7:0>                  |         |                        |                  |

| ON(1,2)         —         SIDL         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         … <th…< td=""><td>15.0</td><td>R/W-0</td><td>U-0</td><td>R/W-0</td><td>U-0</td><td>U-0</td><td>U-0</td><td>U-0</td><td>U-0</td></th…<>                                 | 15.0  | R/W-0                   | U-0      | R/W-0 | U-0   | U-0                    | U-0     | U-0                    | U-0              |

| 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10.0  | ON <sup>(1,2)</sup>     | —        | SIDL  | —     | —                      | —       | —                      | -                |

| <sup>7.0</sup> RTSECSEL <sup>(3)</sup> RTCCLKON — RTCWREN <sup>(4)</sup> RTCSYNC HALFSEC <sup>(5)</sup> RTCOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7.0   |                         | -        | U-0   |       | -                      | R-0     | R-0                    | R/W-0            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7:0   | RTSECSEL <sup>(3)</sup> | RTCCLKON | _     | _     | RTCWREN <sup>(4)</sup> | RTCSYNC | HALFSEC <sup>(5)</sup> | RTCOE            |

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          | J |

|-------------------|------------------|---------------------------|--------------------|---|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |   |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute ON: RTCC On bit<sup>(1,2)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode 0 = Continue normal operation in Idle mode Unimplemented: Read as '0' bit 12-8 bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup> 1 = RTCC Seconds Clock is selected for the RTCC pin 0 = RTCC Alarm Pulse is selected for the RTCC pin bit 6 RTCCLKON: RTCC Clock Enable Status bit 1 = RTCC Clock is actively running 0 = RTCC Clock is not running bit 5-4 Unimplemented: Read as '0' **Note 1:** The ON bit is only writable when RTCWREN = 1. 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active. 4: The RTCWREN bit can be set only when the write sequence is enabled. 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>). Note: This register is reset only on a Power-on Reset (POR).

| REGISTE  | R 23-3:        | C1INT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                                 |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | 1 = A bus      | CAN Bus Activity Wake-up Interrupt Flag bit<br>s wake-up activity interrupt has occurred<br>s wake-up activity interrupt has not occurred |

| bit 13   | 1 = A CAI      | CAN Bus Error Interrupt Flag bit<br>N bus error has occurred<br>N bus error has not occurred                                              |

| bit 12   | SERRIF:        | System Error Interrupt Flag bit <sup>(1)</sup>                                                                                            |

|          |                | tem error occurred (typically an illegal address was presented to the system bus) tem error has not occurred                              |

| bit 11   | <b>RBOVIF:</b> | Receive Buffer Overflow Interrupt Flag bit                                                                                                |

|          |                | eive buffer overflow has occurred<br>eive buffer overflow has not occurred                                                                |

| bit 10-4 | Unimpler       | mented: Read as '0'                                                                                                                       |

| bit 3    | MODIF: 0       | CAN Mode Change Interrupt Flag bit                                                                                                        |

|          |                | N module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP)<br>N module mode change has not occurred                      |

| bit 2    | CTMRIF:        | CAN Timer Overflow Interrupt Flag bit                                                                                                     |

|          |                | N timer (CANTMR) overflow has occurred<br>N timer (CANTMR) overflow has not occurred                                                      |

| bit 1    | RBIF: Re       | ceive Buffer Interrupt Flag bit                                                                                                           |

|          |                | eive buffer interrupt is pending<br>eive buffer interrupt is not pending                                                                  |

| bit 0    | TBIF: Tra      | nsmit Buffer Interrupt Flag bit                                                                                                           |

|          | 1 = A tran     | nsmit buffer interrupt is pending                                                                                                         |

- 0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (C1CON<15>).

# REGISTER 23-11: C1FLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED) bit 20-16 FSEL6<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN5: Filter 17 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL5<1:0>: Filter 5 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL5<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN4: Filter 4 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL4<1:0>: Filter 4 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected FSEL4<4:0>: FIFO Selection bits bit 4-0 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|--|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |  |  |  |  |  |  |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | _                 | —                 |                        |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 7.0          | ITRIM<5:0>        |                   |                   |                     |                   |                   |                        | IRNG<1:0>        |  |  |  |  |  |  |

### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

#### Legend:

| 8                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

# 0000 = Timer1 Event is selected

# bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 **FCKSM<1:0>:** Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator disabled

- 10 = HS Oscillator mode selected

- 01 = XT Oscillator mode selected

- 00 = External Clock mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

# 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.