Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

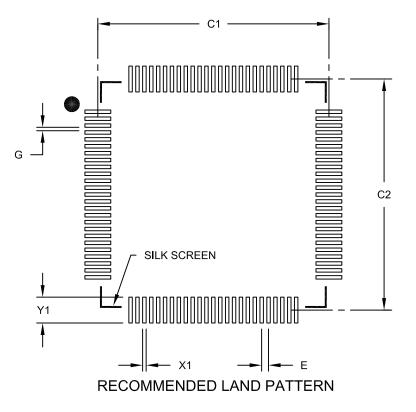

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f064ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 3 and MPLAB REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide"* DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer or debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements

# 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

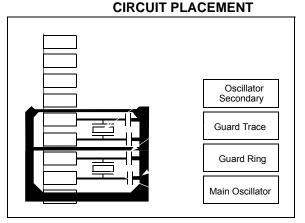

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

# FIGURE 2-3: SUGGESTED OSCILLATOR

<sup>© 2014-2016</sup> Microchip Technology Inc.

# 4.2 Special Function Register Maps

# TABLE 4-2: BUS MATRIX REGISTER MAP

|                             |                         | 200       |                 |       |       |       |       |           |      |      |      |              |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|-----------------|-------|-------|-------|-------|-----------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| ress                        | _                       | Ð         |                 |       |       | -     |       |           |      |      |      | Bits         |      | -         |           |           | -          | _        |               |

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15           | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | _               |       |       | _     |       | BMXCHEDMA |      | _    |      | _            |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 041F          |

| 2000                        | BWXCON                  | 15:0      | -               | _     | _     | _     | _     | _         | _    | _    | _    | BMXWSDRM     | _    | _         | —         | В         | MXARB<2:0> |          | 0047          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | _               |       | _     | _     | -     | _         | _    | _    | -    | _            | _    | _         | _         | _         |            | _        | 0000          |

| 2010                        | DIVINDREDA              | 15:0      |                 |       |       |       |       |           |      |      | BM   | XDKPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _               | _     | _     |       | _     | —         | _    | —    | _    | —            | _    | —         | —         | _         | _          | —        | 0000          |

| 2020                        |                         | 15:0      |                 |       |       |       |       |           |      |      | BM   | XDUDBA<15:0> |      |           |           |           |            |          | 0000          |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | —               | —     | —     |       | —     | —         | —    | —    | —    | —            | —    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |                 |       |       |       |       |           |      |      | BM   | XDUPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |                 |       |       |       |       |           |      |      | BM   | XDRMSZ<31:0> |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |                 |       |       |       |       |           |      |      |      |              |      |           |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —               | _     | —     |       | -     | —         | _    | -    | _    | —            | -    | —         |           | BMXPUPBA  | <19:16>    |          | 0000          |

|                             |                         | 15:0      |                 |       |       |       |       |           |      |      | BM   | XPUPBA<15:0> |      |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |                 |       |       |       |       |           |      |      | BM   | XPFMSZ<31:0> |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |                 |       |       |       |       |           |      |      |      |              |      |           |           |           |            |          |               |

| 2070                        | BMXBOOTSZ               | 31:16     | BMXBOOTSZ<31:0> |       |       |       |       |           |      |      |      |              |      |           |           |           |            |          |               |

|                             |                         | 15:0      |                 |       |       |       |       |           |      |      |      |              |      |           |           |           |            |          | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Interment Course (1)                       | 100 # | Vector |               | Interru      | pt Bit Location |              | Persistent |

|--------------------------------------------|-------|--------|---------------|--------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>            | IRQ # | #      | Flag          | Enable       | Priority        | Sub-priority | Interrupt  |

| CNA – PORTA Input Change Interrupt         | 44    | 33     | IFS1<12>      | IEC1<12>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNB – PORTB Input Change Interrupt         | 45    | 33     | IFS1<13>      | IEC1<13>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNC – PORTC Input Change Interrupt         | 46    | 33     | IFS1<14>      | IEC1<14>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CND – PORTD Input Change Interrupt         | 47    | 33     | IFS1<15>      | IEC1<15>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNE – PORTE Input Change Interrupt         | 48    | 33     | IFS1<16>      | IEC1<16>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNF – PORTF Input Change Interrupt         | 49    | 33     | IFS1<17>      | IEC1<17>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNG – PORTG Input Change Interrupt         | 50    | 33     | IFS1<18>      | IEC1<18>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| PMP – Parallel Master Port                 | 51    | 34     | IFS1<19>      | IEC1<19>     | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMPE – Parallel Master Port Error          | 52    | 34     | IFS1<20>      | IEC1<20>     | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| SPI2E – SPI2 Fault                         | 53    | 35     | IFS1<21>      | IEC1<21>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2RX – SPI2 Receive Done                 | 54    | 35     | IFS1<22>      | IEC1<22>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2TX – SPI2 Transfer Done                | 55    | 35     | IFS1<23>      | IEC1<23>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| U2E – UART2 Error                          | 56    | 36     | IFS1<24>      | IEC1<24>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2RX – UART2 Receiver                      | 57    | 36     | IFS1<25>      | IEC1<25>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2TX – UART2 Transmitter                   | 58    | 36     | IFS1<26>      | IEC1<26>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| I2C2B – I2C2 Bus Collision Event           | 59    | 37     | IFS1<27>      | IEC1<27>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2S – I2C2 Slave Event                   | 60    | 37     | IFS1<28>      | IEC1<28>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2M – I2C2 Master Event                  | 61    | 37     | IFS1<29>      | IEC1<29>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U3E – UART3 Error                          | 62    | 38     | IFS1<30>      | IEC1<30>     | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U3RX – UART3 Receiver                      | 63    | 38     | IFS1<31>      | IEC1<31>     | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U3TX – UART3 Transmitter                   | 64    | 38     | IFS2<0>       | IEC2<0>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U4E – UART4 Error                          | 65    | 39     | IFS2<1>       | IEC2<1>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U4RX – UART4 Receiver                      | 66    | 39     | IFS2<2>       | IEC2<2>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U4TX – UART4 Transmitter                   | 67    | 39     | IFS2<3>       | IEC2<3>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U5E – UART5 Error <sup>(2)</sup>           | 68    | 40     | IFS2<4>       | IEC2<4>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69    | 40     | IFS2<5>       | IEC2<5>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70    | 40     | IFS2<6>       | IEC2<6>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| CTMU – CTMU Event <sup>(2)</sup>           | 71    | 41     | IFS2<7>       | IEC2<7>      | IPC10<12:10>    | IPC10<9:8>   | Yes        |

| DMA0 – DMA Channel 0                       | 72    | 42     | IFS2<8>       | IEC2<8>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA1 – DMA Channel 1                       | 73    | 43     | IFS2<9>       | IEC2<9>      | IPC10<28:26>    | IPC10<25:24> | No         |

| DMA2 – DMA Channel 2                       | 74    | 44     | IFS2<10>      | IEC2<10>     | IPC11<4:2>      | IPC11<1:0>   | No         |

| DMA3 – DMA Channel 3                       | 75    | 45     | IFS2<11>      | IEC2<11>     | IPC11<12:10>    | IPC11<9:8>   | No         |

| CMP3 – Comparator 3 Interrupt              | 76    | 46     | IFS2<12>      | IEC2<12>     | IPC11<20:18>    | IPC11<17:16> | No         |

| CAN1 – CAN1 Event                          | 77    | 47     | IFS2<13>      | IEC2<13>     | IPC11<28:26>    | IPC11<25:24> | Yes        |

| SPI3E – SPI3 Fault                         | 78    | 48     | IFS2<14>      | IEC2<14>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI3RX – SPI3 Receive Done                 | 79    | 48     | IFS2<15>      | IEC2<15>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI3TX – SPI3 Transfer Done                | 80    | 48     | IFS2<16>      | IEC2<16>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81    | 49     | IFS2<17>      | IEC2<17>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82    | 49     | IFS2<18>      | IEC2<18>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83    | 49     | IFS2<19>      | IEC2<19>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

|                                            | •     | Lowe   | st Natural Or | der Priority |                 | 1            |            |

# TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

# 6.1 Control Registers

# TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a         |                  |       |       |        |         |       |      | Bi        | ts      |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|------------------|-------|-------|--------|---------|-------|------|-----------|---------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15            | 30/14 | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8      | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _                | —     | —     | —      | _       |       | —    |           | —       | —    | —    | —    |      |      | —      | —    | 0000       |

| 1400                        |                        | 15:0      | WR               | WREN  | WRERR | LVDERR | LVDSTAT |       | _    | -         | _       | _    | _    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |                  |       |       |        |         |       |      | NVMKE     | /<31.0> |      |      |      |      |      |        |      | 0000       |

|                             |                        | 15:0      |                  |       |       |        |         |       |      |           | 1501.02 |      |      |      |      |      |        |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |                  |       |       |        |         |       |      | NVMADE    | P<31.05 |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |                  |       |       |        |         |       |      | INVIVIADE | K~51.02 |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     | NVMDATA<31:0>    |       |       |        |         |       |      |           |         |      |      |      |      |      |        |      |            |

| 1430                        | NVINDAIA               | 15:0      | NVMDATA<51.0>    |       |       |        |         |       |      |           |         |      |      |      |      |      |        |      |            |

| F440                        | NVMSRC                 | 31:16     |                  |       |       |        |         |       | ,    |           |         |      |      |      |      |      |        |      | 0000       |

| F440                        | ADDR                   | 15:0      | NVMSRCADDR<31:0> |       |       |        |         |       |      |           |         |      |      |      |      |      |        |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

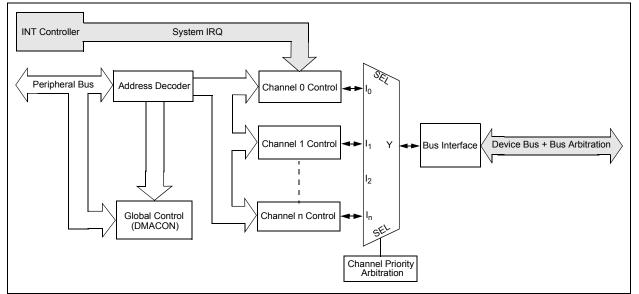

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

The following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

# FIGURE 9-1: DMA BLOCK DIAGRAM

| Bit Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24          |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |

| 00.10          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16          |                   | CHSSA<23:16>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 45-0           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8           |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |  |  |  |

| 7.0            | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0 CHSSA<7:0> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\text{Note:}}$  This must be the physical address of the destination.

NOTES:

|              |                         | -                        | -                  |                         |                   |                   |                  |                  |  |

|--------------|-------------------------|--------------------------|--------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0                     | U-0                      | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                       | _                        | —                  | —                       | —                 |                   | _                | —                |  |

| 22:46        | U-0                     | U-0                      | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                       | _                        | —                  | —                       | —                 | _                 | —                | —                |  |

| 45.0         | R/W-0                   | R/W-0                    | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup>     | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> |                   | AMASK             | <3:0> <b>(3)</b> |                  |  |

| 7.0          | R/W-0                   | R/W-0                    | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                         | ARPT<7:0> <sup>(3)</sup> |                    |                         |                   |                   |                  |                  |  |

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER

## Legend:

| R = Readable bit  | dable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |  |

|-------------------|----------------------------|----------------------|------------------------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

#### bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(3)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved; do not use

- 1011 = Reserved; do not use

- 11xx = Reserved; do not use

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| REGISTE      | REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2 |                   |                   |                   |                   |                   |                  |  |

|--------------|------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 |  |

| 31:24        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              |  |

| 31.24        | —                                              | —                 | —                 | —                 | —                 | —                 | —                |  |

| 23:16        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              |  |

| 23.10        | —                                              | —                 | —                 | —                 | —                 |                   | —                |  |

| 15:8         | R/W-0                                          | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              |  |

| 10.0         |                                                | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                |  |

| 7:0          | R-0                                            | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            |  |

| 7.0          | BUFS                                           |                   |                   | SMP               | <3:0>             |                   | BUFM             |  |

#### F

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVdd               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

- 1 = Enable Offset Calibration mode

- Positive and negative inputs of the sample and hold amplifier are connected to VREFL

- 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

#### bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each  $16^{th}$  sample/convert sequence 1110 = Interrupts at the completion of conversion for each  $15^{th}$  sample/convert sequence

- 0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

Bit 24/16/8/0 U-0

U-0

U-0

R/W-0 ALTS

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | CH0NB             | _                 |                   |                   | CH0S              | B<5:0>            |                  |                  |

| 00.40        | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CH0NA             | —                 |                   |                   | CH0S              | A<5:0>            |                  |                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   |                   |                   | _                 | _                 |                   |                  |                  |

#### REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 **CHONB:** Negative Input Select bit for Sample B 1 = Channel 0 negative input is AN1 0 = Channel 0 negative input is VREFL bit 30 **Unimplemented:** Read as '0'

bit 29-24 CH0SB<5:0>: Positive Input Select bits for Sample B

For 64-pin devices:

- 110001 = Channel 0 positive input is CTMU temperature sensor  $(CTMUT)^{(2)}$

- 110000 = Channel 0 positive input is IVREF<sup>(3)</sup>

- 101111 = Channel 0 positive input is AN47

- .

- 0000001 = Channel 0 positive input is AN1

- 0000000 = Channel 0 positive input is AN0

bit 23 CH0NA: Negative Input Select bit for Sample A Multiplexer Setting<sup>(3)</sup>

- 1 = Channel 0 negative input is AN1 0 = Channel 0 negative input is VREFL

- bit 22 Unimplemented: Read as '0'

Note 1: This selection is only used with CTMU capacitive and time measurement.

- 2: See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

# REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

- bit 10-8 **PRSEG<2:0>:** Propagation Time Segment bits<sup>(4)</sup> 111 = Length is  $8 \times TQ$  $000 = \text{Length is } 1 \times TQ$ SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup> bit 7-6 11 = Length is  $4 \times TQ$  $10 = \text{Length is } 3 \times TQ$ 01 = Length is 2 x TQ  $00 = \text{Length is } 1 \times TQ$ bit 5-0 BRP<5:0>: Baud Rate Prescaler bits 111111 = Tq = (2 x 64)/SYSCLK 111110 = TQ = (2 x 63)/SYSCLK • 000001 = TQ = (2 x 2)/SYSCLK  $000000 = TQ = (2 \times 1)/SYSCLK$ Note 1: SEG2PH  $\leq$  SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. 2: 3 Time bit sampling is not allowed for BRP < 2.

- **3:** SJW  $\leq$  SEG2PH.

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

NOTES:

| Bit<br>31/23/15/7 | Bit<br>30/22/14/6         | Bit<br>29/21/13/5                                                                                                                                                 | Bit<br>28/20/12/4                                                                                                                                                                                                                                | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                               | Bit<br>26/18/10/2                                                                                                                                                                                         | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R                 | R                         | R                                                                                                                                                                 | R                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                   | VER<                      | :3:0> <sup>(1)</sup>                                                                                                                                              |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                 | DEVID<27                                                                                                                                                                                                  | 7:24> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| R                 | R                         | R                                                                                                                                                                 | R                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                   |                           |                                                                                                                                                                   | DEVID<2                                                                                                                                                                                                                                          | 3:16> <b>(1)</b>                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| R                 | R                         | R                                                                                                                                                                 | R                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                   |                           |                                                                                                                                                                   | DEVID<                                                                                                                                                                                                                                           | 15:8> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| R                 | R                         | R                                                                                                                                                                 | R                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DEVID<7:0>(1)     |                           |                                                                                                                                                                   |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                   | 31/23/15/7<br>R<br>R<br>R | 31/23/15/7         30/22/14/6           R         R           R         R           R         R           R         R           R         R           R         R | 31/23/15/7         30/22/14/6         29/21/13/5           R         R         R           R         R         R           R         R         R           R         R         R           R         R         R           R         R         R | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         DEVID<2 | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3           R         R         R         R         R           VER<3:0> <sup>(1)</sup> VER<3:0> <sup>(1)</sup> VER< | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3         26/18/10/2           R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3         26/18/10/2         25/17/9/1           R         R         R         R         R         R         R         R           VER<3:0> <sup>(1)</sup> VER<3:0> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R           DEVID<5:8> <sup>(1)</sup> T         T         T         T         T |  |

# REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Logonan                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

|               | ARACTER |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)                                                                                                                      |                        |            |            |                                                   |  |  |  |

|---------------|---------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|------------|---------------------------------------------------|--|--|--|

|               |         |                                                         | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |            |                                                   |  |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                                                                                                                                                                                       | Typical <sup>(1)</sup> | Units      | Conditions |                                                   |  |  |  |

|               | VIL     | Input Low Voltage                                       |                                                                                                                                                                                            |                        |            |            |                                                   |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                                                                                                                                                                                        | —                      | 0.15 Vdd   | V          |                                                   |  |  |  |