Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

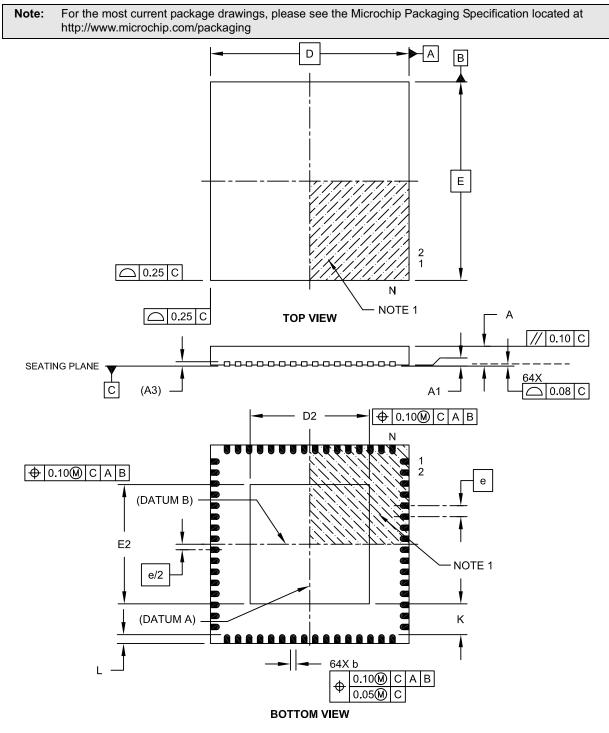

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128h-50i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|              | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |

#### **BMXDRMSZ: DATA RAM SIZE REGISTER REGISTER 4-5:**

| Legend:           |                              |                      |                    |

|-------------------|------------------------------|----------------------|--------------------|

| R = Readable bit  | eadable bit W = Writable bit |                      | ad as '0'          |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00002000 = Device has 8 KB RAM 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

#### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | _                 | _                 | BMXPUPBA<19:16>   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |

| 15:8         | BMXPUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

### bit 10-0 BMXPUPBA<10:0>: Read-Only bits Value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|--|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |  |

| 31:24        | —                   | —                 | —                 | _                 | —                 | _                 | _                | _                     |  |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |  |

| 23:16        | —                   | —                 | —                 | -                 | —                 | —                 | _                | —                     |  |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |  |

| 15:8         | CHBUSY              | _                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |  |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |  |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | —                 | CHEDET            | CHPF             | RI<1:0>               |  |

### REGISTER 9-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

#### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

#### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

#### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   |                   | —                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   | —                 |                   |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | _                 |                   |                   | —                 |                   | _                | —                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7:0          | ENDPT<3:0>        |                   |                   |                   | DIR               | PPBI              |                  | —                |

# Legend:

| R = Readable bit  | W = Writable bit | bit U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|----------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last BD Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 **PPBI:** Ping-Pong BD Pointer Indicator bit

- 1 = The last transaction was to the ODD BD bank

- 0 = The last transaction was to the EVEN BD bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | —                 | _                 | —                 | _                 | _                 | _                | -                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |

# REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

### Legend:

| 9                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive enabled

- 0 = Endpoint n receive disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit enabled

- 0 = Endpoint n transmit disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake enabled

- 0 = Endpoint Handshake disabled (typically used for isochronous endpoints)

# 11.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

# 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin, regardless of the output function including PPS remapped output functions to act as an open-drain output. The only exception is the  $l^2C$  pins that are open drain by default.

The open-drain feature allows the presence of outputs higher than  $V_{DD}$  (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default. The ANSELx register bit, when cleared, disables the corresponding digital input buffer pin(s).

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module. The TRISx bits only control the corresponding digital output buffer pin(s).

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level; i.e., when ANSELx = 1; TRISx = x).

Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be an NOP.

# 11.1.4 INPUT CHANGE NOTIFICATION

The input Change Notification (CN) function of the I/O ports allows the PIC32MX1XX/2XX/5XX 64/100-pin devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

### 11.1.5 INTERNALLY SELECTABLE PULL-UPS AND PULL-DOWNS

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it, which are independent of any other I/O pin functionality (i.e., PPS, Open Drain, or CN). The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

An additional control register (CNCONx) is shown in Register 11-3.

# 11.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

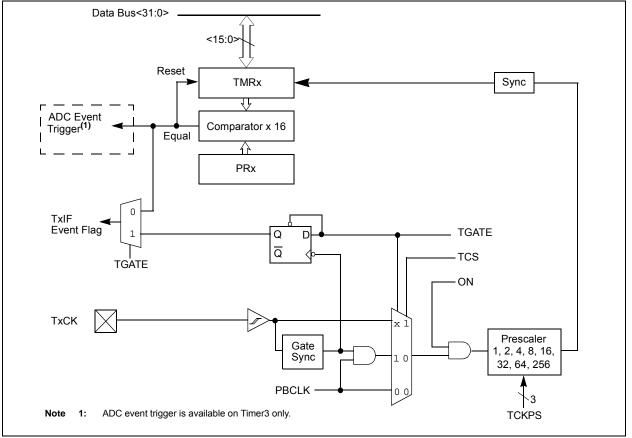

# 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

- Note: In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

# 13.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

# FIGURE 13-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

NOTES:

| ILE OIOTE    |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH01<3:0>      |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01<3:0>        |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   | _                 | _                 | _                 |                   | WDAY0             | 1<3:0>           |                  |  |  |

# REGISTER 21-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 **DAY10<3:0>:** Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9 bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

# Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

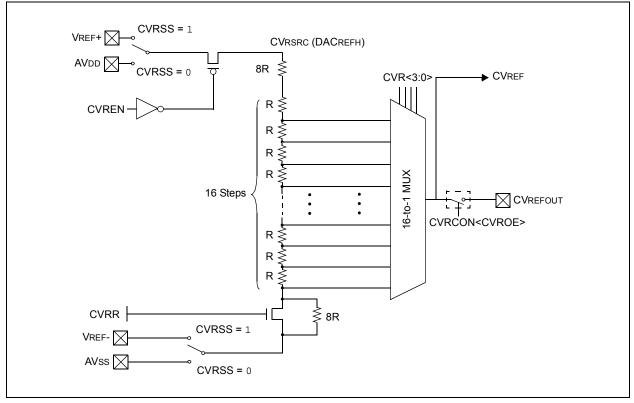

# 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

#### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

|              | BISTER 20-3. CI OCOR. COM IOURATION CONTROL REGISTER |                   |                       |                        |                   |                   |                  |                  |  |  |

|--------------|------------------------------------------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | U-0                                                  | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                                                    | _                 | _                     | _                      | _                 | —                 | _                | _                |  |  |

| 00.40        | U-0                                                  | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                                                    | —                 | -                     | _                      | _                 | —                 | _                | —                |  |  |

| 45.0         | U-0                                                  | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                                                    |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> |                   | —                 |                  | _                |  |  |

| 7.0          | U-0                                                  | U-0               | U-0                   | U-0                    | R/W-0             | U-0               | U-0              | R/W-1            |  |  |

| 7:0          | _                                                    |                   |                       | _                      | JTAGEN            | _                 | _                | TDOEN            |  |  |

# REGISTER 28-5: CFGCON: CONFIGURATION CONTROL REGISTER

# Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed

- bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2-1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# 31.0 40 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX/5XX 64/100-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 32.0** "**50 MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX/5XX 64/100-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | -0.3V to +3.6V           |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               |                          |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

3: See the "Device Pin Tables" section for the 5V tolerant pins.

# TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS                   |                   |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |       |            |  |  |

|--------------------------------------|-------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------|--|--|

| Param.<br>No. Symbol Characteristics |                   |                                                                  | Min.                                                                                                                                                                                                                                                                                 | Тур. | Max.  | Units | Conditions |  |  |

| Operati                              | Operating Voltage |                                                                  |                                                                                                                                                                                                                                                                                      |      |       |       |            |  |  |

| DC10                                 | Vdd               | Supply Voltage (Note 2)                                          | 2.3                                                                                                                                                                                                                                                                                  | _    | 3.6   | V     | —          |  |  |

| DC12                                 | Vdr               | RAM Data Retention Voltage<br>(Note 1)                           | 1.75                                                                                                                                                                                                                                                                                 | _    | —     | V     | _          |  |  |

| DC16                                 | VPOR              | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                                                                                                                                                                                                                                                 | _    | 2.1   | V     | _          |  |  |

| DC17                                 | SVDD              | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005                                                                                                                                                                                                                                                                              | —    | 0.115 | V/µs  | _          |  |  |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

| DC CHARACTERISTICS |        |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |            |                                               |  |

|--------------------|--------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------|-----------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min.                                                                                                                                                                                                                                                                                | Typical <sup>(1)</sup> | Max. | Units      | Conditions                                    |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |                                                                                                                                                                                                                                                                                     |                        |      |            |                                               |  |

| D130               | Eр     | Cell Endurance                       | 20,000                                                                                                                                                                                                                                                                              | —                      | _    | E/W        | _                                             |  |

| D131               | Vpr    | VDD for Read                         | 2.3                                                                                                                                                                                                                                                                                 | —                      | 3.6  | V          | _                                             |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.3                                                                                                                                                                                                                                                                                 | —                      | 3.6  | V          | _                                             |  |

| D134               | TRETD  | Characteristic Retention             | 20                                                                                                                                                                                                                                                                                  | _                      | —    | Year       | Provided no other specifications are violated |  |

| D135               | IDDP   | Supply Current during<br>Programming | _                                                                                                                                                                                                                                                                                   | 10                     | —    | mA         | _                                             |  |

|                    | Tww    | Word Write Cycle Time                | —                                                                                                                                                                                                                                                                                   | 411                    | _    | FRC Cycles | See Note 4                                    |  |

| D136               | Trw    | Row Write Cycle Time                 | —                                                                                                                                                                                                                                                                                   | 6675                   | _    | FRC Cycles | See Note 2,4                                  |  |

| D137               | TPE    | Page Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 20011                  | _    | FRC Cycles | See Note 4                                    |  |

|                    | TCE    | Chip Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 80180                  | _    | FRC Cycles | See Note 4                                    |  |

### TABLE 31-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 31-19) and FRC tuning values (See Register 8-2).

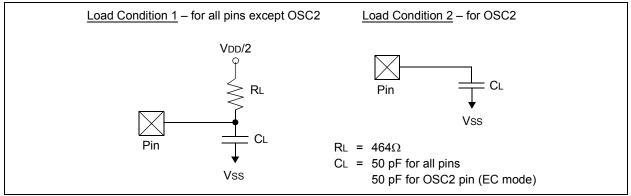

# 31.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX1XX/2XX/5XX 64/100-pin AC characteristics and timing parameters.

### FIGURE 31-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 31-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       | (unles                                            | s otherwise | e stated | <b>l)</b><br>∙40°C ≤ | <b>Ins: 2.3V to 3.6V</b><br>$C \le TA \le +85^{\circ}C$ for Industrial<br>$C \le TA \le +105^{\circ}C$ for V-temp |  |  |  |

|--------------------|--------|-----------------------|---------------------------------------------------|-------------|----------|----------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No.      | Symbol | Characteristics       | Min. Typical <sup>(1)</sup> Max. Units Conditions |             |          |                      |                                                                                                                   |  |  |  |

| DO50               | Cosco  | OSC2 pin              | _                                                 | _           | 15       | pF                   | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1                                           |  |  |  |

| DO50a              | Csosc  | SOSCI/SOSCO pins      | _                                                 | 33          | _        | pF                   | Epson P/N: MC-306 32.7680K-<br>A0:ROHS                                                                            |  |  |  |

| DO56               | Сю     | All I/O pins and OSC2 | _                                                 | —           | 50       | pF                   | EC mode                                                                                                           |  |  |  |

| DO58               | Св     | SCLx, SDAx            | —                                                 | —           | 400      | pF                   | In I <sup>2</sup> C mode                                                                                          |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

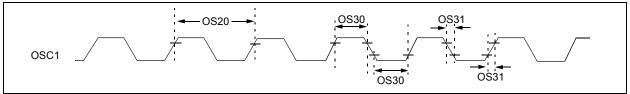

#### FIGURE 31-2: EXTERNAL CLOCK TIMING

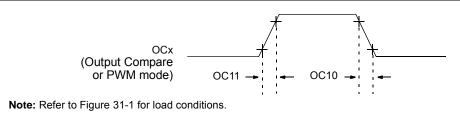

# FIGURE 31-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

# TABLE 31-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

|               |        |                                | (unless                   | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                    |  |  |

|---------------|--------|--------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min.                      | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                               | Max. | Units | Conditions         |  |  |

| OC10          | TccF   | OCx Output Fall Time           | —                         | —                                                                                                                                                                                                                                                                                    | _    | ns    | See parameter DO32 |  |  |

| OC11          | TccR   | OCx Output Rise Time           | — — — ns See parameter DO |                                                                                                                                                                                                                                                                                      |      |       |                    |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

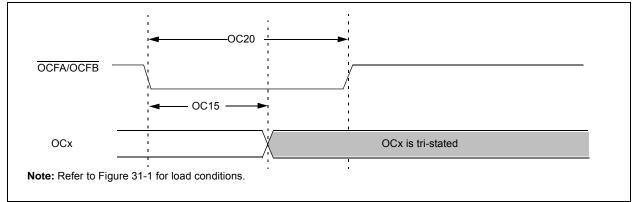

### FIGURE 31-9: OCx/PWM MODULE TIMING CHARACTERISTICS

# TABLE 31-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

|              |        |                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |     |       |            |  |  |

|--------------|--------|--------------------------------|-------------------------------------------------------|---|-----|-------|------------|--|--|

| Param<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min Typical <sup>(2)</sup>                            |   | Max | Units | Conditions |  |  |

| OC15         | Tfd    | Fault Input to PWM I/O Change  | —                                                     | — | 50  | ns    | _          |  |  |

| OC20         | TFLT   | Fault Input Pulse Width        | 50                                                    | — |     | ns    | _          |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

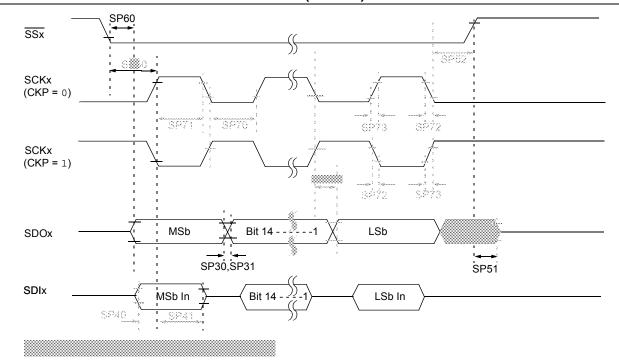

### FIGURE 31-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

# TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |

|--------------------|-----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                               | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)                                              | Тѕск/2                                                                                                                                                                                                                                                                             | _                      |      | ns    | _                  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2                                                                                                                                                                                                                                                                             | —                      | _    | ns    | —                  |

| SP72               | TscF                  | SCKx Input Fall Time                                                      | —                                                                                                                                                                                                                                                                                  | 5                      | 10   | ns    | —                  |

| SP73               | TscR                  | SCKx Input Rise Time                                                      | —                                                                                                                                                                                                                                                                                  | 5                      | 10   | ns    | —                  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —                                                                                                                                                                                                                                                                                  | —                      | _    | ns    | See parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —                                                                                                                                                                                                                                                                                  | —                      | _    | ns    | See parameter DO31 |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                 |                                                                                                                                                                                                                                                                                    | _                      | 20   | ns    | VDD > 2.7V         |

|                    |                       |                                                                           |                                                                                                                                                                                                                                                                                    | _                      | 30   | ns    | VDD < 2.7V         |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10                                                                                                                                                                                                                                                                                 | —                      | _    | ns    | —                  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10                                                                                                                                                                                                                                                                                 | —                      |      | ns    | —                  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                                                                                                                                                                                                                                                | —                      |      | ns    | —                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

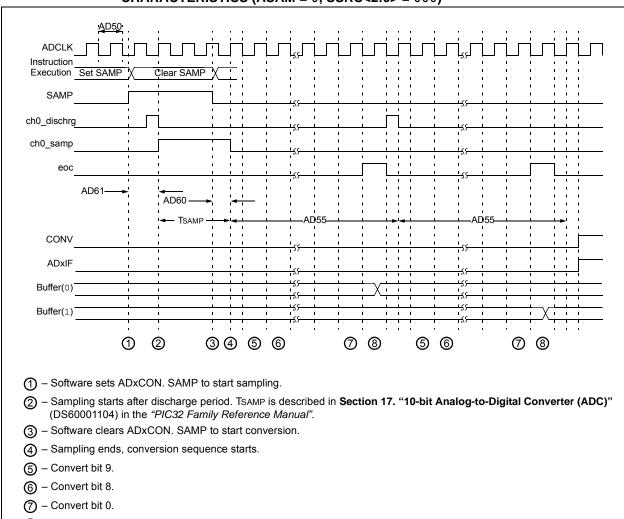

# FIGURE 31-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

(8) – One TAD for end of conversion.

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2