Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| roduct Status            | Active                                                                         |

|                          |                                                                                |

| ore Processor            | MIPS32® M4K™                                                                   |

| ore Size                 | 32-Bit Single-Core                                                             |

| peed                     | 40MHz                                                                          |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| umber of I/O             | 53                                                                             |

| rogram Memory Size       | 128KB (128K x 8)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| EPROM Size               | -                                                                              |

| AM Size                  | 16K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ta Converters            | A/D 28x10b                                                                     |

| cillator Type            | Internal                                                                       |

| perating Temperature     | -40°C ~ 85°C (TA)                                                              |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 64-TQFP                                                                        |

| ipplier Device Package   | 64-TQFP (10x10)                                                                |

| ırchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128h-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                    |     |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    | 25  |

| 3.0   | CPU                                                | 35  |

| 4.0   | Memory Organization                                | 39  |

| 5.0   | Interrupt Controller                               | 53  |

| 6.0   | Flash Program Memory                               | 63  |

| 7.0   | Resets                                             |     |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 85  |

| 10.0  | USB On-The-Go (OTG)                                | 105 |

| 11.0  | I/O Ports                                          | 129 |

| 12.0  | Timer1                                             |     |

| 13.0  | Timer2/3, Timer4/5                                 | 163 |

| 14.0  | Watchdog Timer (WDT)                               | 169 |

| 15.0  | Input Capture                                      | 173 |

| 16.0  | Output Compare                                     | 177 |

|       | Serial Peripheral Interface (SPI)                  |     |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        | 191 |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 199 |

| 20.0  | Parallel Master Port (PMP)                         | 207 |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 231 |

| 23.0  | Controller Area Network (CAN)                      | 243 |

| 24.0  | Comparator                                         | 271 |

| 25.0  | Comparator Voltage Reference (CVREF)               | 275 |

| 26.0  | Charge Time Measurement Unit (CTMU)                | 279 |

|       | Power-Saving Features                              |     |

| 28.0  | Special Features                                   | 291 |

|       | Instruction Set                                    |     |

| 30.0  | Development Support                                | 305 |

|       | 40 MHz Electrical Characteristics                  |     |

| 32.0  | 50 MHz Electrical Characteristics                  | 353 |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

|       | Microchip Web Site                                 |     |

|       | omer Change Notification Service                   |     |

| Custo | omer Support                                       |     |

| Produ | uct Identification System                          | 378 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin N                  | umber             |             |                |                                   |

|----------|------------------------|-------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP   | Pin<br>Type | Buffer<br>Type | Description                       |

| RF0      | 58                     | 87                | I/O         | ST             |                                   |

| RF1      | 59                     | 88                | I/O         | ST             |                                   |

| RF2      | 34(3)                  | 52                | I/O         | ST             |                                   |

| RF3      | 33                     | 51                | I/O         | ST             |                                   |

| RF4      | 31                     | 49                | I/O         | ST             |                                   |

| RF5      | 32                     | 50                | I/O         | ST             | PORTF is a bidirectional I/O port |

| RF6      | 35 <sup>(1)</sup>      | 55 <sup>(1)</sup> | I/O         | ST             |                                   |

| RF7      | _                      | 54(4)             | I/O         | ST             |                                   |

| RF8      | _                      | 53                | I/O         | ST             |                                   |

| RF12     | _                      | 40                | I/O         | ST             |                                   |

| RF13     | _                      | 39                | I/O         | ST             |                                   |

| RG0      | _                      | 90                | I/O         | ST             |                                   |

| RG1      | _                      | 89                | I/O         | ST             |                                   |

| RG2      | 37(1)                  | 57 <sup>(1)</sup> | I/O         | ST             |                                   |

| RG3      | 36 <sup>(1)</sup>      | 56 <sup>(1)</sup> | I/O         | ST             |                                   |

| RG6      | 4                      | 10                | I/O         | ST             |                                   |

| RG7      | 5                      | 11                | I/O         | ST             | DODTO : hidira eti l 1/O et       |

| RG8      | 6                      | 12                | I/O         | ST             | PORTG is a bidirectional I/O port |

| RG9      | 8                      | 14                | I/O         | ST             |                                   |

| RG12     |                        | 96                | I/O         | ST             |                                   |

| RG13     | _                      | 97                | I/O         | ST             |                                   |

| RG14     | _                      | 95                | I/O         | ST             |                                   |

| RG15     | _                      | 1                 | I/O         | ST             |                                   |

| T1CK     | 48                     | 74                | ı           | ST             | Timer1 External Clock Input       |

| T2CK     | PPS                    | PPS               | I           | ST             | Timer2 External Clock Input       |

| T3CK     | PPS                    | PPS               | I           | ST             | Timer3 External Clock Input       |

| T4CK     | PPS                    | PPS               | I           | ST             | Timer4 External Clock Input       |

| T5CK     | PPS                    | PPS               | I           | ST             | Timer5 External Clock Input       |

| U1CTS    | PPS                    | PPS               | I           | ST             | UART1 Clear to Send               |

| U1RTS    | PPS                    | PPS               | 0           |                | UART1 Ready to Send               |

| U1RX     | PPS                    | PPS               | I           | ST             | UART1 Receive                     |

| U1TX     | PPS                    | PPS               | 0           | _              | UART1 Transmit                    |

| U2CTS    | PPS                    | PPS               | I           | ST             | UART2 Clear to Send               |

| U2RTS    | PPS                    | PPS               | 0           |                | UART2 Ready to Send               |

| U2RX     | PPS                    | PPS               | I           | ST             | UART2 Receive                     |

| U2TX     | PPS                    | PPS               | 0           | _              | UART2 Transmit                    |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levelsAnalog = Analog input<br/>TTL = TTL input bufferI = Input<br/>P = Power

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices with a USB module.

- **4:** This pin is only available on 100-pin devices without a USB module.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32  $^{\otimes}$  architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration register 1.                                                |

| 16                 | Config2                 | Configuration register 2.                                                |

| 16                 | Config3                 | Configuration register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

**Note 1:** Registers used in exception processing.

2: Registers used during debug.

#### 4.3 Control Registers

Register 4-1 through Register 4-8 are used for setting the RAM and Flash memory partitions for data and code.

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 |                   | BMX               | BMX               | BMX               | BMX              | BMX              |

|              |                   |                   | _                 | ERRIXI            | ERRICD            | ERRDMA            | ERRDS            | ERRIS            |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | BMXARB<2:0       | >                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-21 Unimplemented: Read as '0'

bit 20 BMXERRIXI: Enable Bus Error from IXI bit

1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus

0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus

bit 19 BMXERRICD: Enable Bus Error from ICD Debug Unit bit

1 = Enable bus error exceptions for unmapped address accesses initiated from ICD

0 = Disable bus error exceptions for unmapped address accesses initiated from ICD

bit 18 **BMXERRDMA:** Bus Error from DMA bit

1 = Enable bus error exceptions for unmapped address accesses initiated from DMA

0 = Disable bus error exceptions for unmapped address accesses initiated from DMA

bit 17 BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)

1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access

0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access

bit 16 BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)

1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access

0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access

bit 15-7 Unimplemented: Read as '0'

bit 6 BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit

1 = Data RAM accesses from CPU have one wait state for address setup

0 = Data RAM accesses from CPU have zero wait states for address setup

bit 5-3 **Unimplemented:** Read as '0'

bit 2-0 BMXARB<2:0>: Bus Matrix Arbitration Mode bits

111 = Reserved (using these configuration modes will produce undefined behavior)

:

011 = Reserved (using these configuration modes will produce undefined behavior)

010 = Arbitration Mode 2

001 = Arbitration Mode 1 (default)

000 = Arbitration Mode 0

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 22:46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes:

0x00010000 = Device has 64 KB Flash

0x00020000 = Device has 128 KB Flash

0x00040000 = Device has 256 KB Flash

0x00080000 = Device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 22.46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 BMXBOOTSZ<31:0>: Boot Flash Memory (BFM) Size bits

Static value that indicates the size of the Boot PFM in bytes:

0x00000C00 = Device has 3 KB Boot Flash

#### 7.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

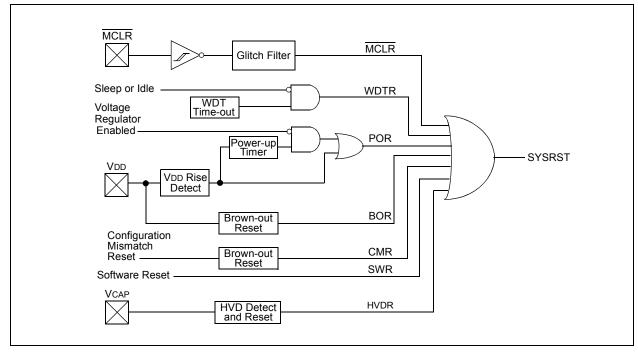

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · MCLR: Master Clear Reset pin

- · SWR: Software Reset

- · WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- · CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 7-1.

FIGURE 7-1: SYSTEM RESET BLOCK DIAGRAM

# 8.0 OSCILLATOR CONFIGURATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 6. "Oscillator Configuration"** (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32MX1XX/2XX/5XX 64/100-pin oscillator system has the following modules and features:

- A Total of four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- · Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | 1                 | -                 | -                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 |                   | -                 | -                 | -                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

1 = Direct connection to a low-speed device enabled

0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

bit 6 RETRYDIS: Retry Disable bit (Host mode and U1EP0 only)

1 = Retry NAKed transactions disabled

0 = Retry NAKed transactions enabled; retry done in hardware

bit 5 **Unimplemented:** Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers, TX and RX transfers also allowed

Otherwise, this bit is ignored.

bit 3 EPRXEN: Endpoint Receive Enable bit

1 = Endpoint n receive enabled

0 = Endpoint n receive disabled

bit 2 **EPTXEN:** Endpoint Transmit Enable bit

1 = Endpoint n transmit enabled

0 = Endpoint n transmit disabled

bit 1 EPSTALL: Endpoint Stall Status bit

1 = Endpoint n was stalled

0 = Endpoint n was not stalled

bit 0 EPHSHK: Endpoint Handshake Enable bit

1 = Endpoint Handshake enabled

0 = Endpoint Handshake disabled (typically used for isochronous endpoints)

TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                  |               |       |       |            |       |       |       |      | Bi   | ts   |      |      |      |      |            |            |      |            |

|-----------------------------|------------------|---------------|-------|-------|------------|-------|-------|-------|------|------|------|------|------|------|------|------------|------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13      | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2       | 17/1       | 16/0 | All Resets |

| FB38                        | RPA14R           | 31:16         | _     | _     | _          | _     | _     | _     | _    | _    | _    | 1    | _    | _    | _    | _          | _          | _    | 0000       |

| 1 000                       | 101701410        | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA14      | 1<3:0>     |      | 0000       |

| FB3C                        | RPA15R           | 31:16         | _     |       | _          | _     |       | _     | _    |      |      |      | _    | _    | _    | _          | _          | _    | 0000       |

| . 500                       |                  | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA1       | 5<3:0>     |      | 0000       |

| FB40                        | RPB0R            | 31:16         | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |            | _          | _    | 0000       |

|                             |                  | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB0       | <3:0>      |      | 0000       |

| FB44                        | RPB1R            | 31:16         |       | _     | _          | _     |       | _     | _    |      |      |      | _    | _    | _    |            |            |      | 0000       |

|                             |                  | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    | _    |      | _    | _    |      | RPB1       | <3:0>      |      | 0000       |

| FB48                        | RPB2R            | 31:16         |       |       |            |       |       |       | _    |      |      |      |      | _    | _    | _          | _          |      | 0000       |

|                             |                  | 15:0          |       |       | _          |       | _     | _     |      | _    |      |      | _    |      |      | RPB2       | <3:0>      |      | 0000       |

| FB4C RPB3                   | RPB3R            | 31:16         | _     |       | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |            |            |      | 0000       |

|                             |                  | 15:0<br>31:16 | _     |       |            | _     | _     | _     | _    | _    | _    |      | _    | _    |      | RPB3       | <3:0>      |      | 0000       |

| FB54                        | RPB5R            |               | _     | _     | _          | _     | _     | _     | _    |      | _    |      | _    | _    | _    | RPB5       |            |      | 0000       |

|                             |                  | 15:0<br>31:16 |       |       | _          |       | _     |       | _    |      |      |      | _    |      |      | — RPB0     |            |      | 0000       |

| FB58                        | RPB6R            | 15:0          | _     |       |            | _     |       |       | _    | _    |      |      |      | _    |      | RPB6       | -<br><3:0> |      | 0000       |

|                             |                  | 31:16         |       |       |            |       |       |       |      |      |      |      |      |      | _    | _          | _          | _    | 0000       |

| FB5C                        | RPB7R            | 15:0          |       |       |            |       |       |       |      |      |      |      |      |      | _    | RPB7       |            |      | 0000       |

|                             |                  | 31:16         | _     | _     | _          | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _          | _          | _    | 0000       |

| FB60                        | RPB8R            | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    |      |      | _    | _    |      | RPB8       |            |      | 0000       |

|                             |                  | 31:16         | _     | _     | _          | _     | _     | _     | _    |      |      |      | _    | _    | _    | -          | _          |      | 0000       |

| FB64                        | RPB9R            | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    |      | _    | _    | _    |      | RPB9       | <3:0>      |      | 0000       |

|                             |                  | 31:16         | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _          | _          | _    | 0000       |

| FB68                        | RPB10R           | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    | _    |      | _    | _    |      | RPB10      | )<3:0>     |      | 0000       |

|                             | DDD 4 4 D        | 31:16         | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _          | _          | _    | 0000       |

| FB78                        | RPB14R           | 15:0          | _     | _     | RPB14<3:0> |       | 0000  |       |      |      |      |      |      |      |      |            |            |      |            |

| ED76                        | DDD45D           | 31:16         | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _          | _          | _    | 0000       |

| FB7C                        | RPB15R           | 15:0          | _     | _     | _          | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB15<3:0> |            |      | 0000       |

| ED04                        | DDC4D            | 31:16         | _     | _     | _          | _     | -     | _     | _    | _    | _    |      | _    | _    | -    | _          | _          | _    | 0000       |

| FB84 RPC                    | RPC1R            | 15:0          | _     | -     | _          | _     | -     | _     | _    | _    | _    | _    | _    | _    |      | RPC1       | <3:0>      |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

### 15.1 Control Registers

#### TABLE 15-1: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 5 REGISTER MAP

| ess                         |                       |                                                                                     |                                                                |                        |       |       |       |       |       | Bit    | ts     |      |      |      |       |      |          |      | <b>1</b>   |

|-----------------------------|-----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range                                                                           | 31/15                                                          | 30/14                  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16                                                                               | _                                                              | _                      | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | IC ICON'              | 15:0                                                                                | :0 ON - SIDL FEDGE C32 ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> 0000 |                        |       |       |       |       |       |        |        |      | 0000 |      |       |      |          |      |            |

| 2010                        | IC1BUF                | 31:16<br>15:0                                                                       |                                                                | IC1BUF<31:0> xxxx xxxx |       |       |       |       |       |        |        |      |      |      |       |      |          |      |            |

| 0000                        | 100001(1)             | 31:16                                                                               | _                                                              | _                      | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2200                        | IC2CON <sup>(1)</sup> | 2CON <sup>(1)</sup> 15:0 ON — SIDL — — FEDGE C32 ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> |                                                                |                        |       |       |       |       |       | 0000   |        |      |      |      |       |      |          |      |            |

| 2210                        | IC2BUF                | 31:16<br>15:0                                                                       |                                                                |                        |       |       |       |       |       | IC2BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 0.400                       | 100001(1)             | 31:16                                                                               | _                                                              | _                      | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2400                        | IC3CON <sup>(1)</sup> | 15:0                                                                                | ON                                                             | _                      | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2410                        | IC3BUF                | 31:16<br>15:0                                                                       |                                                                |                        |       |       |       |       |       | IC3BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16                                                                               | _                                                              | _                      | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | IC4CON 7              | 15:0                                                                                | ON                                                             | _                      | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2610                        | IC4BUF                | 4BUF                                                                                |                                                                |                        |       |       |       |       |       |        | xxxx   |      |      |      |       |      |          |      |            |

| 2000                        | 10500N(1)             | 31:16                                                                               | _                                                              | _                      | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | IC5CON <sup>(1)</sup> | 15:0                                                                                | ON                                                             | _                      | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2810                        | IC5BUF                | 31:16<br>15:0                                                                       | ICSRUEZ31:0S                                                   |                        |       |       |       |       |       |        |        |      |      |      |       |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more

#### REGISTER 19-1: UxMODE: UARTX MODE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | ı                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL<1:0>        |                  | STSEL            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: UARTx Enable bit(1)

1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue operation when device enters Idle mode

0 = Continue operation in Idle mode

bit 12 IREN: IrDA Encoder and Decoder Enable bit

1 = IrDA is enabled

0 = IrDA is disabled

bit 11 RTSMD: Mode Selection for UxRTS Pin bit

$1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

$0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

bit 10 Unimplemented: Read as '0'

bit 9-8 **UEN<1:0>:** UARTx Enable bits

11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

01 = UxTX, UxRX and  $\overline{\text{UxRTS}}$  pins are enabled and used;  $\overline{\text{UxCTS}}$  pin is controlled by corresponding bits in the PORTx register

00 = UxTX and UxRX pins are enabled and used;  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}/\text{UxBCLK}$  pins are controlled by corresponding bits in the PORTx register

bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

1 = Wake-up enabled

0 = Wake-up disabled

bit 6 LPBACK: UARTx Loopback Mode Select bit

1 = Loopback mode is enabled

0 = Loopback mode is disabled

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 17.** "10-bit **Analog-to-Digital Converter (ADC)**" (DS60001104) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

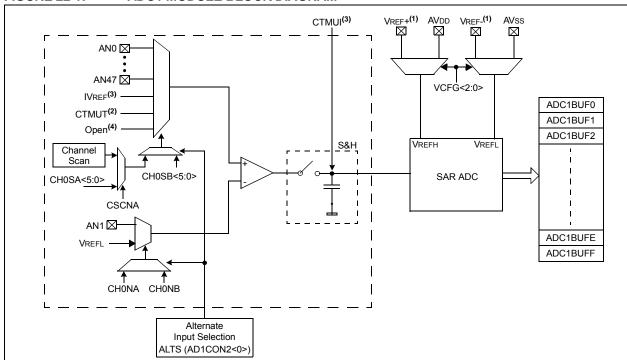

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- Up to 48 analog input pins

- · External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

- Note 1: VREF+ and VREF- inputs can be multiplexed with other analog inputs.

- 2: Connected to the CTMU temperature reference diode. See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

- 4: This selection is only used with CTMU capacitive and time measurement.

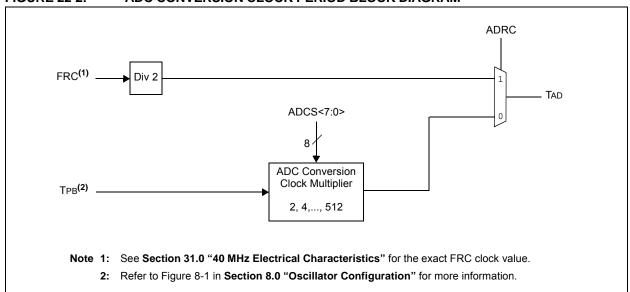

#### FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

#### REGISTER 23-1: C1CON: CAN MODULE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |  |  |

| 31.24        | _                 | _                 | _                 | _                 | ABAT              | REQOP<2:0>        |                  |                  |  |  |

| 23:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | C                 | DPMOD<2:0>        | ı                 | CANCAP            | _                 | _                 | _                | _                |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDLE             | _                 | CANBUSY           | _                 | _                | _                |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | _                 | _                 | _                 | DNCNT<4:0>        |                   |                   |                  |                  |  |  |

Legend:HC = Hardware ClearS = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-28 Unimplemented: Read as '0'

bit 27 ABAT: Abort All Pending Transmissions bit

1 = Signal all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions aborted

bit 26-24 **REQOP<2:0>:** Request Operation Mode bits

111 = Set Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Set Configuration mode

011 = Set Listen Only mode

010 = Set Loopback mode

001 = Set Disable mode

000 = Set Normal Operation mode

bit 23-21 OPMOD<2:0>: Operation Mode Status bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

1 = CANTMR value is stored on valid message reception and is stored with the message

0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

bit 19-16 Unimplemented: Read as '0'

bit 15 **ON:** CAN On bit<sup>(1)</sup>

1 = CAN module is enabled

0 = CAN module is disabled

bit 14 Unimplemented: Read as '0'

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

#### **REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN11           | MSEL1             | 1<1:0>            | FSEL11<4:0>       |                   |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN10           | MSEL1             | 0<1:0>            | FSEL10<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN9            | MSEL9<1:0>        |                   | FSEL9<4:0>        |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN8            | MSEL              | 8<1:0>            | FSEL8<4:0>        |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN11: Filter 11 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 30-29 MSEL11<1:0>: Filter 11 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL11<4:0>: FIFO Selection bits

11111 = Reserved

•

•

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

•

•

00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN10: Filter 10 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 22-21 MSEL10<1:0>: Filter 10 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             | CVR<3:0>          |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

1 = Module is enabled

Setting this bit does not affect other bits in the register.

0 = Module is disabled and does not consume current

Clearing this bit does not affect the other bits in the register.

bit 14-7 Unimplemented: Read as '0'

bit 6 CVROE: CVREFOUT Enable bit

1 = Voltage level is output on CVREFOUT pin

0 = Voltage level is disconnected from CVREFOUT pin

bit 5 CVRR: CVREF Range Selection bit

1 = 0 to 0.625 CVRSRC, with CVRSRC/24 step size

0 = 0.25 CVRSRC to 0.719 CVRSRC, with CVRSRC/32 step size

bit 4 CVRSS: CVREF Source Selection bit

1 = Comparator voltage reference source, CVRSRC = (VREF+) – (VREF-)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

When CVRR = 1:

CVREF = (CVR<3:0>/24) • (CVRSRC)

When CVRR = 0:

CVREF = 1/4 • (CVRSRC) + (CVR<3:0>/32) • (CVRSRC)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

TABLE 31-39: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)   Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |       |      |       |            |  |

|--------------------|---------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                      | Min.                                                                                                                                                                                                                                             | Тур.  | Max. | Units | Conditions |  |

| PM11               | Twr     | PMWR Pulse Width                                                    | _                                                                                                                                                                                                                                                | 1 Трв | _    | _     | _          |  |

| PM12               | TDVSU   | Data Out Valid before PMWR or PMENB goes Inactive (data setup time) | _                                                                                                                                                                                                                                                | 2 Трв |      |       | _          |  |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)       | _                                                                                                                                                                                                                                                | 1 TPB |      |       | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### **TABLE 31-40: OTG ELECTRICAL SPECIFICATIONS**

| AC CHARACTERISTICS |         |                                   | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |      |       |                                                                                   |  |

|--------------------|---------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions                                                                        |  |

| USB313             | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                            | _    | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |  |

| USB315             | VILUSB  | Input Low Voltage for USB Buffer  | _                                                                                                                                                                                                                                              | _    | 0.8  | V     | _                                                                                 |  |

| USB316             | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                            | _    | _    | V     | _                                                                                 |  |

| USB318             | VDIFS   | Differential Input Sensitivity    | _                                                                                                                                                                                                                                              | _    | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |

| USB319             | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                            | _    | 2.5  | V     | _                                                                                 |  |

| USB320             | Zout    | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                           | _    | 44.0 | Ω     | _                                                                                 |  |

| USB321             | Vol     | Voltage Output Low                | 0.0                                                                                                                                                                                                                                            | _    | 0.3  | V     | 1.425 kΩ load connected to VUSB3V3                                                |  |

| USB322             | Vон     | Voltage Output High               | 2.8                                                                                                                                                                                                                                            | _    | 3.6  | V     | 1.425 kΩ load connected to ground                                                 |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### 34.0 PACKAGING INFORMATION

### 34.1 Package Marking Information

64-Lead TQFP (10x10x1 mm)

64-Lead QFN (9x9x0.9 mm)

100-Lead TQFP (14x14x1 mm)

100-Lead TQFP (12x12x1 mm)

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3 can be found on the outer packaging for this package.

**lote:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

#### W

| WWW Address         | . 377 |

|---------------------|-------|

| WWW On-Line Support | С     |

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support