Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 28x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-QFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128ht-50i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Device Pin Tables**

### TABLE 2: PIN NAMES FOR 64-PIN GENERAL PURPOSE DEVICES

| 64·   | PIN QFN <sup>(4)</sup> AND TQFP (TOP VIEW)                                     |                   |                        |

|-------|--------------------------------------------------------------------------------|-------------------|------------------------|

|       | PIC32MX120F064H<br>PIC32MX130F128H<br>PIC32MX150F256H<br>PIC32MX170F512H<br>64 | QFN <sup>(4</sup> | 1<br>64<br><b>TQFP</b> |

| Pin # | Full Pin Name                                                                  | Pin #             | Full Pin Name          |

| 1     | AN22/RPE5/PMD5/RE5                                                             | 33                | RPF3/RF3               |

| 2     | AN23/PMD6/RE6                                                                  | 34                | RPF2/RF2               |

| 3     | AN27/PMD7/RE7                                                                  | 35                | RPF6/SCK1/INT0/RF6     |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                                  | 36                | SDA1/RG3               |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                                                       | 37                | SCL1/RG2               |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                                                       | 38                | VDD                    |

| 7     | MCLR                                                                           | 39                | OSC1/CLKI/RC12         |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                                                       | 40                | OSC2/CLKO/RC15         |

| 9     | Vss                                                                            | 41                | Vss                    |

| 10    | VDD                                                                            | 42                | RPD8/RTCC/RD8          |

| 11    | AN5/C1INA/RPB5/RB5                                                             | 43                | RPD9/RD9               |

| 12    | AN4/C1INB/RB4                                                                  | 44                | RPD10/PMA15/RD10       |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                                                       | 45                | RPD11/PMA14/RD11       |

| 14    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2                                          | 46                | RPD0/RD0               |

| 15    | PGEC1/VREF-/AN1/RPB1/CTED12/RB1                                                | 47                | SOSCI/RPC13/RC13       |

| 16    | PGED1/VREF+/AN0/RPB0/PMA6/RB0                                                  | 48                | SOSCO/RPC14/T1CK/RC14  |

| 17    | PGEC2/AN6/RPB6/RB6                                                             | 49                | AN24/RPD1/RD1          |

| 18    | PGED2/AN7/RPB7/CTED3/RB7                                                       | 50                | AN25/RPD2/RD2          |

| 19    | AVDD                                                                           | 51                | AN26/C3IND/RPD3/RD3    |

| 20    | AVss                                                                           | 52                | RPD4/PMWR/RD4          |

| 21    | AN8/RPB8/CTED10/RB8                                                            | 53                | RPD5/PMRD/RD5          |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                                                        | 54                | C3INC/RD6              |

| 23    | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                      | 55                | C3INB/RD7              |

| 24    | TDO/AN11/PMA12/RB11                                                            | 56                | VCAP                   |

| 25    | Vss                                                                            | 57                | Vdd                    |

| 26    | Vdd                                                                            | 58                | C3INA/RPF0/RF0         |

| 27    | TCK/AN12/PMA11/RB12                                                            | 59                | RPF1/RF1               |

| 28    | TDI/AN13/PMA10/RB13                                                            | 60                | PMD0/RE0               |

| 29    | AN14/RPB14/SCK3/CTED5/PMA1/RB14                                                | 61                | PMD1/RE1               |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                                | 62                | AN20/PMD2/RE2          |

| 31    | RPF4/SDA2/PMA9/RF4                                                             | 63                | RPE3/CTPLS/PMD3/RE3    |

| 32    | RPF5/SCL2/PMA8/RF5                                                             | 64                | AN21/PMD4/RE4          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

### 1.0 DEVICE OVERVIEW

Note 1: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). This document contains device-specific information for PIC32MX1XX/2XX/5XX 64/100-pin devices.

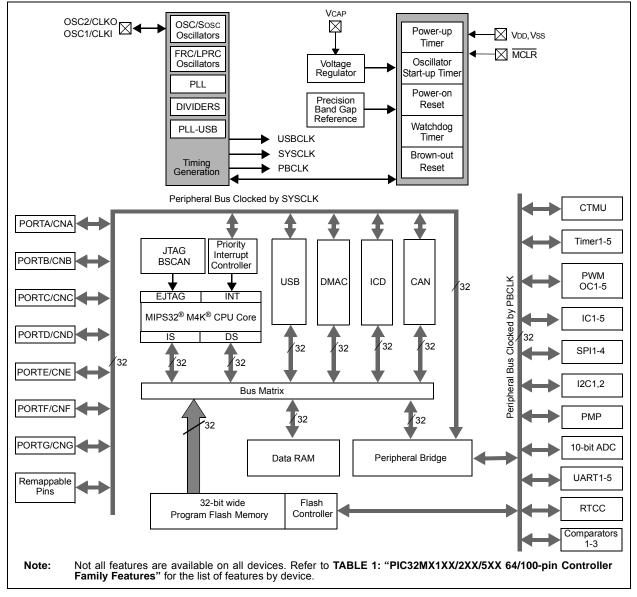

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX/ 5XX 64/100-pin family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: PIC32MX1XX/2XX/5XX 64/100-PIN BLOCK DIAGRAM

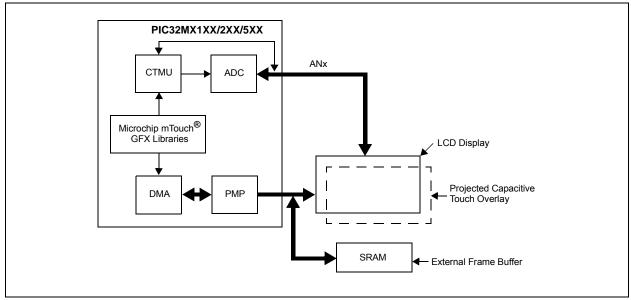

## FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

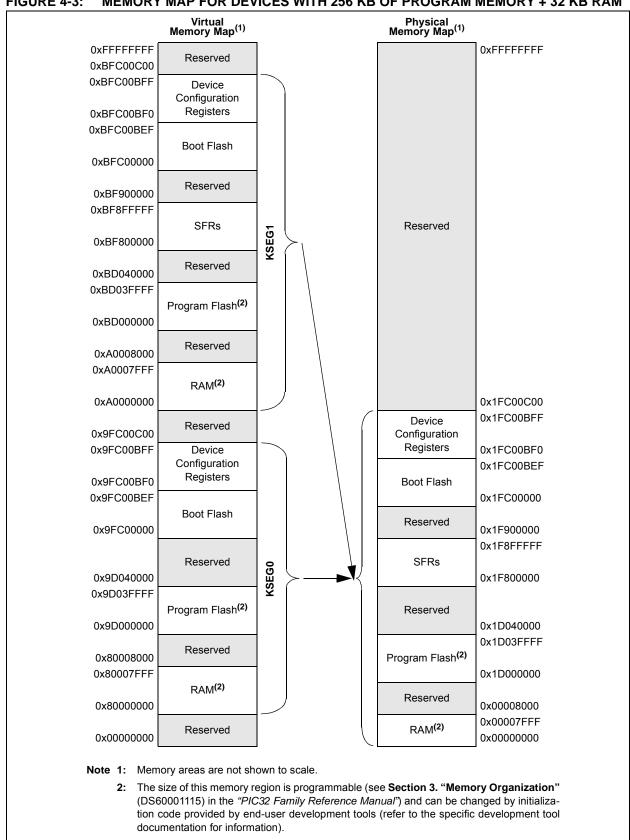

### FIGURE 4-3: MEMORY MAP FOR DEVICES WITH 256 KB OF PROGRAM MEMORY + 32 KB RAM

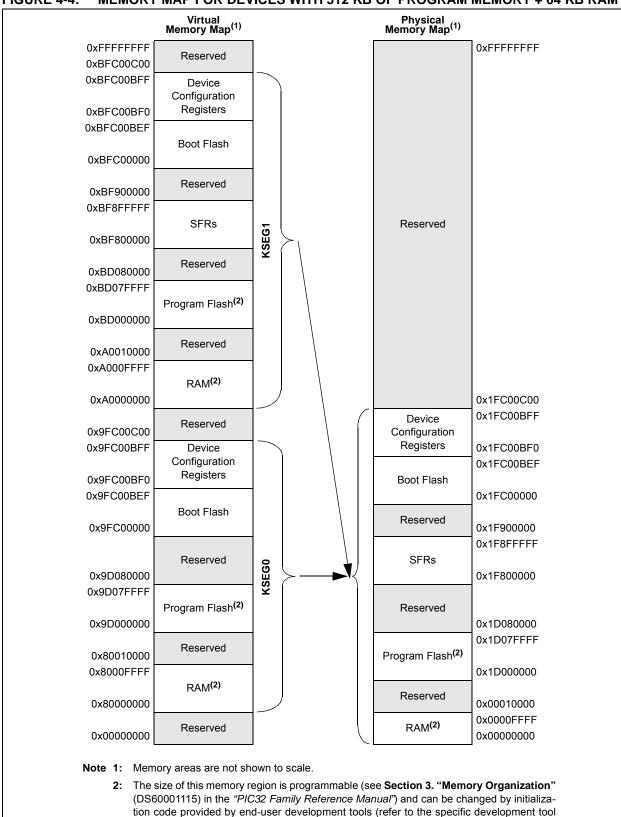

#### FIGURE 4-4: MEMORY MAP FOR DEVICES WITH 512 KB OF PROGRAM MEMORY + 64 KB RAM

© 2014-2016 Microchip Technology Inc.

documentation for information).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |  |

| 31:24        | _                 | —                    | Р                 | LLODIV<2:0>       | >                 | FRCDIV<2:0>           |                  |                  |  |

| 22.16        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |  |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI∖             | /<1:0>            | :0> PLLMULT<2:0>      |                  |                  |  |

| 15.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |  |

| 15:8         | _                 |                      | COSC<2:0>         |                   | _                 |                       | NOSC<2:0>        |                  |  |

| 7.0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

### Legend:

bit 22

#### y = Value set from Configuration bits on POR

| •                 | •                | •                         |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- SOSCRDY: Secondary Oscillator (SOSC) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### 9.1 Control Registers

### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |           |           |       |       |       |         |         |       |      | Bit      | s       |      |      |      |      |      |          |      | 6          |

|-----------------------------|-----------|-----------|-------|-------|-------|---------|---------|-------|------|----------|---------|------|------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) |           | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        |           | 31:16     | _     | _     | —     | _       | —       | _     | —    | _        | _       | _    | _    | _    | _    | _    | _        |      | 0000       |

| 3000                        | DIVIACON  | 15:0      | ON    | —     | _     | SUSPEND | DMABUSY | _     | —    | _        | —       | —    | —    | _    | —    | _    | —        | —    | 0000       |

| 2010                        | DMASTAT   | 31:16     | _     | —     | _     | _       |         | _     | —    | _        | —       | —    | —    | _    | —    | _    | —        | —    | 0000       |

| 3010                        | DIVIASTAT | 15:0      |       | -     | _     | _       | —       | _     | _    | —        | -       | —    | _    | —    | RDWR | C    | MACH<2:0 | >    | 0000       |

| 2020                        |           | 31:16     |       |       |       |         |         |       |      | DMAADD   | 7~21:05 |      |      |      |      |      |          |      | 0000       |

| 3020                        | DMAADDR   | 15:0      |       |       |       |         |         |       |      | DIVIAADD | 1.02    |      |      |      |      |      |          |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 | ¢)        | Bits  |                |       |       |       |           |      |      |          |        |        |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|-------|----------------|-------|-------|-------|-----------|------|------|----------|--------|--------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _              | BYTO  | <1:0> | WBO   | —         | _    | BITO | —        | —      | _      | _    | _    | _    | —        | _    | 0000       |

| 3030                        | DURUUUN                         | 15:0      | _     |                | —     |       |       | PLEN<4:0> |      |      | CRCEN    | CRCAPP | CRCTYP |      | _    | C    | RCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA                        | 31:16     |       |                |       |       |       |           |      |      | TA-21:05 |        |        |      |      |      |          |      | 0000       |

| 3040                        | DCRODAIA                        | 15:0      |       | DCRCDATA<31:0> |       |       |       |           |      |      |          |        |        |      |      |      |          |      |            |

| 3050                        |                                 | 31:16     |       |                |       |       |       |           |      |      | )P<31.0> |        |        |      |      |      |          |      | 0000       |

| 3030                        | 3050 DCRCXOR 15:0 DCRCXOR<31:0> |           |       |                |       |       |       |           |      |      |          | 0000   |        |      |      |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

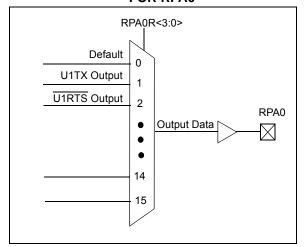

### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

## 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

### 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

### TABLE 11-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |               |       |       |       |       |       |       |      | В    | its  |      |      |      |                |       |        |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|----------------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3           | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16         |       | —     | —     | -     | -     | —     | -    | -    | -    | —    | -    | -    | —              | —     | -      |      | 0000       |

| 1 A04                       |                  | 15:0          | _     | —     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |                | INT1F | <3:0>  |      | 0000       |

| FA08                        | INT2R            | 31:16         | _     | _     |       |       | _     | _     | _    | —    | _    | _    | _    | _    | —              | _     | —      | _    | 0000       |

| 17.00                       | 1111211          | 15:0          |       |       |       |       |       |       | —    |      | _    | _    |      |      |                | INT2F | <3:0>  |      | 0000       |

| FA0C                        | INT3R            | 31:16         | _     | —     | _     |       | _     |       | _    | _    | _    | _    | _    | _    |                |       | _      |      | 0000       |

|                             |                  | 15:0          | —     | —     | —     | —     | _     | —     | —    | —    | —    | —    | —    | _    |                | INT3F | <3:0>  |      | 0000       |

| FA10                        | INT4R            | 31:16         | —     | —     | _     | —     | _     | —     | —    | —    | —    | _    | —    | _    | —              | —     | —      | —    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     | _     |       | _    | _    | _    | _    | _    | _    |                | INT4F | <3:0>  |      | 0000       |

| FA18                        | T2CKR            | 31:16         | _     |       |       |       |       |       |      |      |      |      | —    |      |                | -     | —      | _    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     |       |       |      | _    | _    | _    |      | _    |                | T2CK  | <<3:0> | _    | 0000       |

| FA1C                        | T3CKR            | 31:16         | _     | —     |       |       |       |       | _    |      |      | —    |      |      | _              | —<br> | -      | —    | 0000       |

|                             |                  | 15:0          | _     |       |       |       |       |       |      |      |      |      |      |      |                | T3CKF | <<3:0> |      | 0000       |

| FA20                        | T4CKR            | 31:16<br>15:0 |       | _     |       |       |       |       |      |      |      |      |      |      |                | T4CKF |        | —    | 0000       |

|                             |                  |               |       |       | _     |       |       |       |      |      |      | _    |      |      |                | 1400  | (<3.0> |      | 0000       |

| FA24                        | T5CKR            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      |                | T5CKF |        | _    | 0000       |

|                             |                  | 31:16         |       |       |       |       |       |       |      |      |      |      | _    |      | _              |       | (<3.0> | _    | 0000       |

| FA28                        | IC1R             | 15:0          | _     | _     |       | _     |       |       |      |      | _    | _    |      |      |                | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     |       |       |      |      |      | _    |      |      | _              | _     |        | _    | 0000       |

| FA2C                        | IC2R             | 15:0          | _     | _     | _     |       |       | _     | _    | _    | _    | _    | _    |      |                |       | <3:0>  |      | 0000       |

|                             |                  | 31:16         |       |       |       |       | _     |       |      | _    | _    |      |      | _    |                | _     | _      |      | 0000       |

| FA30                        | IC3R             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |                | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16         | _     |       | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _              |       | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |                | IC4R  | <3:0>  |      | 0000       |

| -                           | 10.55            | 31:16         | _     | —     | —     | —     | _     | —     | _    | _    | -    | _    | _    | _    | —              | —     | —      | —    | 0000       |

| FA38                        | IC5R             | 15:0          | _     | _     | _     | _     |       | _     | _    | _    | -    | _    |      |      |                | IC5R  | <3:0>  | •    | 0000       |

| FA 40                       |                  | 31:16         |       |       |       | —     |       |       |      | -    |      |      |      |      | —              | —     | —      | —    | 0000       |

| FA48                        | OCFAR            | 15:0          |       | —     | _     | —     | _     | —     |      | -    | _    | _    | -    | _    |                | OCFA  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16         | _     | _     | —     | —     | _     | —     | _    |      | _    | _    |      | -    | _              | _     | _      | _    | 0000       |

| FAGU                        | UIKAR            | 15:0          | _     | —     |       | _     |       |       | _    |      | -    | _    |      |      | 0 11 0 11 0 10 |       |        |      |            |

| FA54                        | U1CTSR           | 31:16         | _     | —     | —     | —     |       | —     |      |      |      | —    |      |      |                |       |        |      |            |

| 1704                        | UTUTUR           | 15:0          | _     | —     | —     | _     | _     | —     |      | _    | _    | —    | _    | _    |                | U1CTS | R<3:0> |      | 0000       |

| FA58                        | U2RXR            | 31:16         | _     | —     | —     | —     | _     | —     | _    | _    | _    | —    | _    | —    | —              | —     | —      | —    | 0000       |

| 1,100                       | <b>U</b> LIVIN   | 15:0          |       | —     | —     | —     |       | —     | —    | —    | —    | —    | —    | —    |                | U2RXI | R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

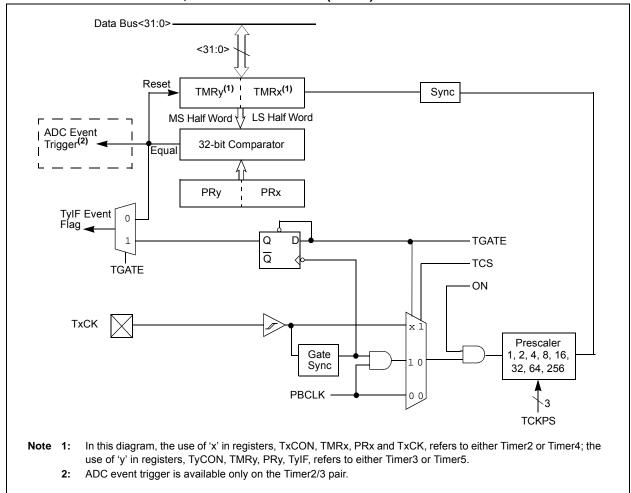

### FIGURE 13-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

NOTES:

| REGIST  | ER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                                  |

| bit 7-6 | <pre>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 =Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</pre> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                   |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                     |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                            |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                         |

| bit 1   | <b>OERR:</b> Receive Buffer Overrun Error Status bit.<br>This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.<br>1 = Receive buffer has overflowed                                                                                                                                                                                     |

|         | 0 = Receive buffer has not overflowed                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                    |

| REGISTE  | R 23-3:        | C1INT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                                 |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | 1 = A bus      | CAN Bus Activity Wake-up Interrupt Flag bit<br>s wake-up activity interrupt has occurred<br>s wake-up activity interrupt has not occurred |

| bit 13   | 1 = A CAI      | CAN Bus Error Interrupt Flag bit<br>N bus error has occurred<br>N bus error has not occurred                                              |

| bit 12   | SERRIF:        | System Error Interrupt Flag bit <sup>(1)</sup>                                                                                            |

|          |                | tem error occurred (typically an illegal address was presented to the system bus) tem error has not occurred                              |

| bit 11   | <b>RBOVIF:</b> | Receive Buffer Overflow Interrupt Flag bit                                                                                                |

|          |                | eive buffer overflow has occurred<br>eive buffer overflow has not occurred                                                                |

| bit 10-4 | Unimpler       | mented: Read as '0'                                                                                                                       |

| bit 3    | MODIF: 0       | CAN Mode Change Interrupt Flag bit                                                                                                        |

|          |                | N module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP)<br>N module mode change has not occurred                      |

| bit 2    | CTMRIF:        | CAN Timer Overflow Interrupt Flag bit                                                                                                     |

|          |                | N timer (CANTMR) overflow has occurred<br>N timer (CANTMR) overflow has not occurred                                                      |

| bit 1    | RBIF: Re       | ceive Buffer Interrupt Flag bit                                                                                                           |

|          |                | eive buffer interrupt is pending<br>eive buffer interrupt is not pending                                                                  |

| bit 0    | TBIF: Tra      | nsmit Buffer Interrupt Flag bit                                                                                                           |

|          | 1 = A tran     | nsmit buffer interrupt is pending                                                                                                         |

- 0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (C1CON<15>).

### REGISTER 23-13: C1FLTCON3: CAN FILTER CONTROL REGISTER 3 (CONTINUED) bit 20-16 FSEL14<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN13: Filter 13 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL13<1:0>: Filter 13 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL13<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN12: Filter 12 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL12<1:0>: Filter 12 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected FSEL12<4:0>: FIFO Selection bits bit 4-0 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|--|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |  |  |  |  |  |  |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | _                 | —                 |                        |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | IRNG                | <1:0>             |                   |                        |                  |  |  |  |  |  |  |

### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

### Legend:

| 8                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

### 0000 = Timer1 Event is selected

### bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------|--|--|--|--|--|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1                          | r-1              |  |  |  |  |  |

| 31:24        |                       | _                 | _                 | —                 | —                 | _                 | _                            | —                |  |  |  |  |  |

| 23:16        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                          | R/P              |  |  |  |  |  |

| 23:10        |                       | _                 |                   | —                 | —                 | FPLLODIV<2:0>     |                              |                  |  |  |  |  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                          | R/P              |  |  |  |  |  |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | —                 | —                 | UP                | UPLLIDIV<2:0> <sup>(1)</sup> |                  |  |  |  |  |  |

| 7.0          | r-1                   | R/P-1             | R/P R/P-1         |                   | r-1               | R/P R/P           |                              | R/P              |  |  |  |  |  |

| 7:0          | _                     | F                 | PLLMUL<2:0        | >                 | —                 | FPLLIDIV<2:0>     |                              |                  |  |  |  |  |  |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 28-3:**

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 6-4

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1' FPLLMUL<2:0>: PLL Multiplier bits 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is available on PIC32MX2XX/5XX devices only.

| Bit<br>31/23/15/7           | Bit<br>30/22/14/6         | Bit<br>29/21/13/5                                                                                                                           | Bit<br>28/20/12/4                                                                                                                                                                                                | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                     | Bit<br>26/18/10/2                                                                                                                                                                                         | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R                           | R                         | R                                                                                                                                           | R                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                             | VER<                      | :3:0> <sup>(1)</sup>                                                                                                                        |                                                                                                                                                                                                                  | DEVID<27:24> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| R                           | R                         | R                                                                                                                                           | R                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DEVID<23:16> <sup>(1)</sup> |                           |                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| R                           | R                         | R                                                                                                                                           | R                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DEVID<15:8> <sup>(1)</sup>  |                           |                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| R                           | R                         | R                                                                                                                                           | R                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DEVID<7:0>(1)               |                           |                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                             | 31/23/15/7<br>R<br>R<br>R | 31/23/15/7         30/22/14/6           R         R           R         R           R         R           R         R           R         R | 31/23/15/7         30/22/14/6         29/21/13/5           R         R         R           R         R         R           R         R         R           R         R         R           R         R         R | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         R           R         R         R         DEVID<2 | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3           R         R         R         R         R           VER<3:0> <sup>(1)</sup> VER<3:0> <sup>(1)</sup> VER< | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3         26/18/10/2           R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R | 31/23/15/7         30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3         26/18/10/2         25/17/9/1           R         R         R         R         R         R         R         R           VER<3:0> <sup>(1)</sup> VER<3:0> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R           R         R         R         R         R         R         R           R         R         R         R         R         R         R           R         R         R         R         R         R         R         R           R         R         R         R         R         R         R         R         R         R         R |  |  |

### REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Logonan           |                  |                                               |                    |

|-------------------|------------------|-----------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | itable bit U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                          | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

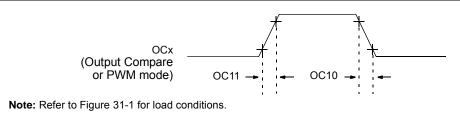

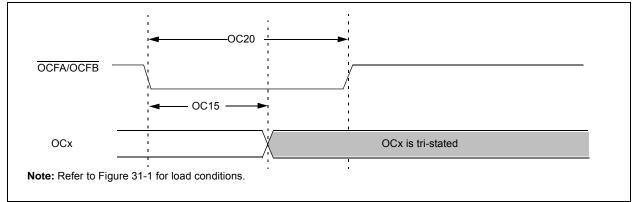

### FIGURE 31-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 31-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS