Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32 ® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 28x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128ht-50i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Number |                        |                 |             | (•             | ,                                                                                                                                                                                      |

|------------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name   | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                            |

| AN36       |                        | 47              | I           | Analog         |                                                                                                                                                                                        |

| AN37       | _                      | 48              | I           | Analog         |                                                                                                                                                                                        |

| AN38       | _                      | 52              | I           | Analog         |                                                                                                                                                                                        |

| AN39       | _                      | 53              | I           | Analog         |                                                                                                                                                                                        |

| AN40       | _                      | 79              | I           | Analog         |                                                                                                                                                                                        |

| AN41       | _                      | 80              | I           | Analog         | Analog input channels                                                                                                                                                                  |

| AN42       | _                      | 83              | I           | Analog         | Analog input channels.                                                                                                                                                                 |

| AN43       |                        | 84              | I           | Analog         |                                                                                                                                                                                        |

| AN44       | _                      | 87              | I           | Analog         |                                                                                                                                                                                        |

| AN45       | _                      | 88              | I           | Analog         |                                                                                                                                                                                        |

| AN46       | _                      | 93              | I           | Analog         |                                                                                                                                                                                        |

| AN47       | _                      | 94              | I           | Analog         |                                                                                                                                                                                        |

| CLKI       | 39                     | 63              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                 |

| CLKO       | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with the OSC2 pin function. |

| OSC1       | 39                     | 63              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                        |

| OSC2       | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                               |

| SOSCI      | 47                     | 73              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                         |

| SOSCO      | 48                     | 74              | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                        |

| IC1        | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC2        | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC3        | PPS                    | PPS             | I           | ST             | Capture Input 1-5                                                                                                                                                                      |

| IC4        | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC5        | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| OC1        | PPS                    | PPS             | 0           | ST             | Output Compare Output 1                                                                                                                                                                |

| OC2        | PPS                    | PPS             | 0           | ST             | Output Compare Output 2                                                                                                                                                                |

| OC3        | PPS                    | PPS             | 0           | ST             | Output Compare Output 3                                                                                                                                                                |

| OC4        | PPS                    | PPS             | 0           | ST             | Output Compare Output 4                                                                                                                                                                |

| OC5        | PPS                    | PPS             | 0           | ST             | Output Compare Output 5                                                                                                                                                                |

| OCFA       | PPS                    | PPS             | Ι           | ST             | Output Compare Fault A Input                                                                                                                                                           |

| OCFB       | 30                     | 44              | I           | ST             | Output Compare Fault B Input                                                                                                                                                           |

|            |                        | IOS compati     |             |                | Analog = Analog input I = Input O = Output                                                                                                                                             |

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = P

P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

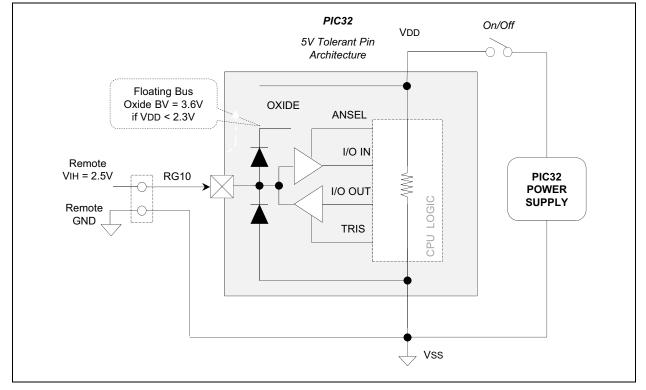

### 2.9.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

# 4.2 Special Function Register Maps

# TABLE 4-2: BUS MATRIX REGISTER MAP

| ress                        | _                       | Ð         |       |       |       | -     |       |           |      |      |      | Bits          |      | -         |           |           | -          | _        |               |

|-----------------------------|-------------------------|-----------|-------|-------|-------|-------|-------|-----------|------|------|------|---------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7 | 22/6          | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | _     |       |       | _     |       | BMXCHEDMA |      | _    |      | _             |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 041F          |

| 2000                        | BWXCON                  | 15:0      | -     | _     | _     | _     | _     | _         | _    | _    | _    | BMXWSDRM      | _    | _         | —         | В         | MXARB<2:0> |          | 0047          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | _     |       | _     | _     | -     | _         | _    | _    | -    | _             | _    | _         | _         | _         |            | _        | 0000          |

| 2010                        | DIVINDREDA              | 15:0      |       |       |       |       |       |           |      |      | BM   | XDKPBA<15:0>  |      |           |           |           |            |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _     | _     | _     |       | _     | —         | _    | —    | _    | —             | _    | —         | —         | _         | _          | —        | 0000          |

| 2020                        |                         | 15:0      |       |       |       |       |       |           |      |      | BM   | XDUDBA<15:0>  |      |           |           |           |            |          | 0000          |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | —     | —     | —     |       | —     | —         | —    | —    | —    | —             | —    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |       |       |       |       |       |           |      |      | BM   | XDUPBA<15:0>  |      |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |       |       |       |       |           |      |      | BM   | XDRMSZ<31:0>  |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |       |       |       |       |           |      |      |      |               |      |           |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —     | _     | —     |       | -     | —         | _    | -    | _    | —             | -    | —         |           | BMXPUPBA  | <19:16>    |          | 0000          |

|                             |                         | 15:0      |       |       |       |       |       |           |      |      | BM   | XPUPBA<15:0>  |      |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |       |       |       |       |       |           |      |      | BM   | XPFMSZ<31:0>  |      |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |       |       |       |       |           |      |      |      |               |      |           |           |           |            |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |       |       |       |       |       |           |      |      | BMX  | (BOOTSZ<31:0) | >    |           |           |           |            |          | 0000          |

|                             |                         | 15:0      |       |       |       |       |       |           |      |      |      |               |      |           |           |           |            |          | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 |                   | _                 |                   |                  |                  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 |                   | -                 |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 |                   | -                 |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | _                 |                   |                   | FRMH<2:0>        |                  |

### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

### Legend:

| J                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

- 0001 = OUT (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 1101 = SETUP (TX) token type transaction

- Note: All other values are reserved and must not be used.

- bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

**Note 1:** All other values are reserved and must not be used.

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection        |

|----------------|-----------------|------------------|-----------------------------------------------------------|

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPD1<br>0001 = RPG9                                |

| тзск           | T3CKR           | T3CKR<3:0>       | 0010 = RPB14<br>0011 = RPD0                               |

| IC1            | IC1R            | IC1R<3:0>        | 0100 = RPD8<br>0101 = RPB6                                |

| U3CTS          | U3CTSR          | U3CTSR<3:0>      | 0110 = RPD5<br>0111 = RPB2                                |

| U4RX           | U4RXR           | U4RXR<3:0>       | 1000 = RPF3 <sup>(4)</sup><br>1001 = RPF13 <sup>(3)</sup> |

| U5RX           | U5RXR           | U5RXR<3:0>       | 1010 = Reserved<br>1011 = RPF2 <sup>(1)</sup>             |

| SS2            | SS2R            | SS2R<3:0>        | 1100 = RPC2 <sup>(3)</sup><br>1101 = RPE8 <sup>(3)</sup>  |

| OCFA           | OCFAR           | OCFAR<3:0>       | 1110 = Reserved<br>1111 = Reserved                        |

# TABLE 11-1:INPUT PIN SELECTION (CONTINUED)

Note 1: This selection is not available on 64-pin USB devices.

- 2: This selection is only available on 100-pin General Purpose devices.

- 3: This selection is not available on 64-pin devices.

- 4: This selection is not available when USBID functionality is used on USB devices.

- 5: This selection is not available on devices without a CAN module.

- 6: This selection is not available on USB devices.

- 7: This selection is not available when VBUSON functionality is used on USB devices.

### **REGISTER 15-1:** ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     |                   | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

#### Legend:

| R = Readable bit                          | W = Writable bit | U = Unimplemented bit |                  |

|-------------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = unk | nown)            | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit <sup>(1)</sup>                                                                                                     |

|           | <ul> <li>1 = Module enabled</li> <li>0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications</li> </ul> |

| bit 14    | Unimplemented: Read as '0'                                                                                                                             |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                         |

|           | <ul><li>1 = Halt in CPU Idle mode</li><li>0 = Continue to operate in CPU Idle mode</li></ul>                                                           |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                             |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                             |

|           | <ul> <li>1 = Capture rising edge first</li> <li>0 = Capture falling edge first</li> </ul>                                                              |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                         |

|           | <ul> <li>1 = 32-bit timer resource capture</li> <li>0 = 16-bit timer resource capture</li> </ul>                                                       |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                  |

|           | <ul><li>0 = Timer3 is the counter source for capture</li><li>1 = Timer2 is the counter source for capture</li></ul>                                    |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                       |

|           | 11 = Interrupt on every fourth capture event                                                                                                           |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                  |

|           | 00 = Interrupt on every second capture event                                                                                                           |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                               |

|           | 1 = Input capture overflow occurred                                                                                                                    |

|           | 0 = No input capture overflow occurred                                                                                                                 |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                           |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>      |

|           |                                                                                                                                                        |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

© 2014-2016 Microchip Technology Inc.

# REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)('x' = 1 THROUGH 5)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 31.24        | _                    | —                 | —                 | —                 | —                        | _                 | -                | _                |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 23.10        | —                    | _                 | —                 | —                 | —                        | —                 | _                | —                |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | SPISGNEXT            | _                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR           |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0            |

| 7:0          | AUDEN <sup>(1)</sup> |                   |                   |                   | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0>(1,2)      |

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| ı' |

|----|

| ļ  |

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

#### bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame Error overflow generates error events 0 = Frame Error does not generate error events bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = Receive overflow generates error events 0 = Receive overflow does not generate error events bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun Generates Error Events 0 = Transmit Underrun Does Not Generates Error Events bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions) 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data 0 = A ROV is a critical error which stop SPI operation bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions) 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty 0 = A TUR is a critical error which stop SPI operation AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup> bit 7 1 = Audio protocol enabled 0 = Audio protocol disabled bit 6-5 Unimplemented: Read as '0' AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3 1 = Audio data is mono (Each data word is transmitted on both left and right channels) 0 = Audio data is stereo bit 2 Unimplemented: Read as '0' AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0 11 = PCM/DSP mode 10 = Right Justified mode 01 = Left Justified mode  $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

| Bit<br>Range       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24              | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 00:16              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16              | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8 DATAOUT<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|                    | DATAOUT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 20-4: PMDOUT: PARALLEL PORT OUTPUT DATA REGISTER

# Legend:

| 9                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 DATAOUT<15:0>: Port Data Output bits

This register is used for Read operations in the Enhanced Parallel Slave mode and Write operations for Dual Buffer Master mode.

In Dual Buffer Master mode, the DUALBUF bit (PMPCON<17>) = 1, a write to the MSB triggers the transaction on the PMP port. When MODE16 = 1, MSB = DATAOUT<15:8>. When MODE16 = 0, MSB = DATAOUT<7:0>.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         |                   |                   |                   | DATAIN<           | 15:8>             |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | DATAIN<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 20-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

# Legend:

| 9                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAIN<15:0>: Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode. In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port. When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note: This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

**Note:** In Master mode, a read will return the last value written to the register. In Slave mode, a read will return indeterminate results.

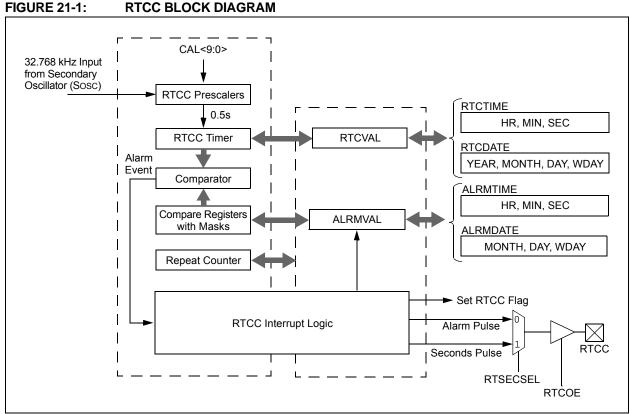

#### 21.0 **REAL-TIME CLOCK AND** CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available the Microchip web from site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are the key features of this module:

- · Time: hours. minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: Weekday, date, month and year

- · Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- · User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- · Requirements: External 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

# RTCC BLOCK DIAGRAM

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24            |                   | HR10              | <3:0>             |                   |                   | HR01              | <3:0>            |                  |  |

| 00.40            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16 MIN10<3:0> |                   |                   |                   |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8             |                   | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0              | —                 | —                 | _                 | _                 | —                 | —                 | —                | _                |  |

|                  |                   | •                 |                   |                   |                   | •                 |                  |                  |  |

| Legend:          |                   |                   |                   |                   |                   |                   |                  |                  |  |

| R = Readable bit |                   |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |

#### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

bit 31-28

HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10s place digits; contains a value from 0 to 2

bit 31-28 HR(10<3:0>: Binary-Coded Decimal Value of Hours bits, 10s place digits, contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 17-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| ILE OIOTE    | STER 21-0. AERIMDATE: AEARIM DATE VALUE REGISTER |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|--------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                                | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 04.04        | U-0                                              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                                                | _                 | _                 | —                 | _                 | _                 | _                | —                |  |

| 00.40        | R/W-x                                            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                                                  | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0         | R/W-x                                            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                                                  | DAY               | 10<1:0>           |                   | DAY01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0                                              | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          | _                                                | —                 | —                 | _                 |                   | WDAY0             | 1<3:0>           |                  |  |

# REGISTER 21-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 **DAY10<3:0>:** Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9 bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

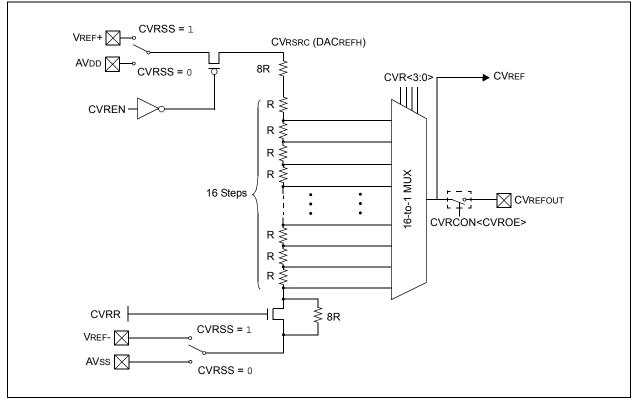

# 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

#### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | _                     | _                      | _                 | —                 | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | -                     | _                      | _                 | —                 | _                | —                |  |  |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> |                   | —                 |                  | _                |  |  |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-0             | U-0               | U-0              | R/W-1            |  |  |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            | _                 | _                | TDOEN            |  |  |

# REGISTER 28-5: CFGCON: CONFIGURATION CONTROL REGISTER

### Legend:

| Logona.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed

- bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2-1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# 30.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### 30.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 30.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 30.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

### TABLE 31-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS                                |       |                                                                     | (unless of | herwise | ture -40°C | $\leq$ Ta $\leq$ + | -85°C fo   |                                      |

|---------------------------------------------------|-------|---------------------------------------------------------------------|------------|---------|------------|--------------------|------------|--------------------------------------|

| Param.<br>No. Symbol Characteristics <sup>(</sup> |       | cs <sup>(1)</sup>                                                   | Min.       | Typical | Max.       | Units              | Conditions |                                      |

| OS50                                              | Fplli | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |            | 3.92    | _          | 5                  | MHz        | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51                                              | Fsys  | On-Chip VCO System<br>Frequency                                     |            | 60      | —          | 120                | MHz        | _                                    |

| OS52                                              | TLOCK | PLL Start-up Time (Lock Time)                                       |            | _       | _          | 2                  | ms         | —                                    |

| OS53                                              | DCLK  | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      |            | -0.25   | —          | +0.25              | %          | Measured over 100 ms<br>period       |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### TABLE 31-19: INTERNAL FRC ACCURACY

| АС СНА        | RACTERISTICS           | (unless          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                          |  |  |

|---------------|------------------------|------------------|------------------------------------------------------|------|-------|------------------------------------------|--|--|

| Param.<br>No. | Characteristics        |                  | Typical                                              | Max. | Units | Conditions                               |  |  |

| Internal      | FRC Accuracy @ 8.00 MH | z <sup>(1)</sup> |                                                      |      |       |                                          |  |  |

| F20a          | FRC                    | -0.9             | —                                                    | +0.9 | %     | $-40^{\circ}C \leq TA \leq +85^{\circ}C$ |  |  |

| F20b          | FRC                    | -2 — +2          |                                                      | +2   | %     | $-40^{\circ}C \le TA \le +105^{\circ}C$  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 31-20: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICS              |                 | $\label{eq:standard} \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |  |  |

|---------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No.                   | Characteristics | Min.                                                                                                                                                                                                                                                                                                      | Typical | Max. | Units | Conditions |  |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |                                                                                                                                                                                                                                                                                                           |         |      |       |            |  |  |  |

| F21                             | LPRC            | -15                                                                                                                                                                                                                                                                                                       | —       | +15  | %     | —          |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

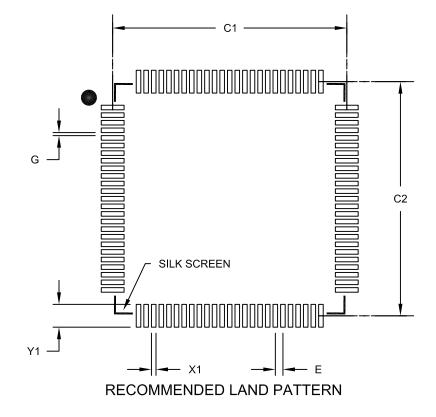

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |          |       |      |

|---------------------------|-------------|----------|-------|------|

| Dimensior                 | MIN         | NOM      | MAX   |      |

| Contact Pitch             | E           | 0.50 BSC |       |      |

| Contact Pad Spacing       | C1          |          | 15.40 |      |

| Contact Pad Spacing       | C2          |          | 15.40 |      |

| Contact Pad Width (X100)  | X1          |          |       | 0.30 |

| Contact Pad Length (X100) | Y1          |          |       | 1.50 |

| Distance Between Pads     | G           | 0.20     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B