Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin Number             |                   |             |                |                                   |

|----------|------------------------|-------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP   | Pin<br>Type | Buffer<br>Type | Description                       |

| RF0      | 58                     | 87                | I/O         | ST             |                                   |

| RF1      | 59                     | 88                | I/O         | ST             | 1                                 |

| RF2      | 34 <sup>(3)</sup>      | 52                | I/O         | ST             |                                   |

| RF3      | 33                     | 51                | I/O         | ST             | 1                                 |

| RF4      | 31                     | 49                | I/O         | ST             | 1                                 |

| RF5      | 32                     | 50                | I/O         | ST             | PORTF is a bidirectional I/O port |

| RF6      | 35 <sup>(1)</sup>      | 55 <sup>(1)</sup> | I/O         | ST             |                                   |

| RF7      |                        | 54 <b>(4)</b>     | I/O         | ST             | 1                                 |

| RF8      |                        | 53                | I/O         | ST             | 1                                 |

| RF12     |                        | 40                | I/O         | ST             |                                   |

| RF13     | _                      | 39                | I/O         | ST             |                                   |

| RG0      | _                      | 90                | I/O         | ST             |                                   |

| RG1      | _                      | 89                | I/O         | ST             |                                   |

| RG2      | 37 <sup>(1)</sup>      | 57 <sup>(1)</sup> | I/O         | ST             |                                   |

| RG3      | 36 <sup>(1)</sup>      | 56 <sup>(1)</sup> | I/O         | ST             |                                   |

| RG6      | 4                      | 10                | I/O         | ST             |                                   |

| RG7      | 5                      | 11                | I/O         | ST             | BORTC is a hidiractional I/O part |

| RG8      | 6                      | 12                | I/O         | ST             | PORTG is a bidirectional I/O port |

| RG9      | 8                      | 14                | I/O         | ST             |                                   |

| RG12     | _                      | 96                | I/O         | ST             |                                   |

| RG13     |                        | 97                | I/O         | ST             |                                   |

| RG14     |                        | 95                | I/O         | ST             |                                   |

| RG15     |                        | 1                 | I/O         | ST             |                                   |

| T1CK     | 48                     | 74                | Ι           | ST             | Timer1 External Clock Input       |

| T2CK     | PPS                    | PPS               | I           | ST             | Timer2 External Clock Input       |

| T3CK     | PPS                    | PPS               | I           | ST             | Timer3 External Clock Input       |

| T4CK     | PPS                    | PPS               | Ι           | ST             | Timer4 External Clock Input       |

| T5CK     | PPS                    | PPS               | Ι           | ST             | Timer5 External Clock Input       |

| U1CTS    | PPS                    | PPS               | Ι           | ST             | UART1 Clear to Send               |

| U1RTS    | PPS                    | PPS               | 0           |                | UART1 Ready to Send               |

| U1RX     | PPS                    | PPS               | Ι           | ST             | UART1 Receive                     |

| U1TX     | PPS                    | PPS               | 0           |                | UART1 Transmit                    |

| U2CTS    | PPS                    | PPS               | Ι           | ST             | UART2 Clear to Send               |

| U2RTS    | PPS                    | PPS               | 0           |                | UART2 Ready to Send               |

| U2RX     | PPS                    | PPS               | Ι           | ST             | UART2 Receive                     |

| U2TX     | PPS                    | PPS               | 0           | _              | UART2 Transmit                    |

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

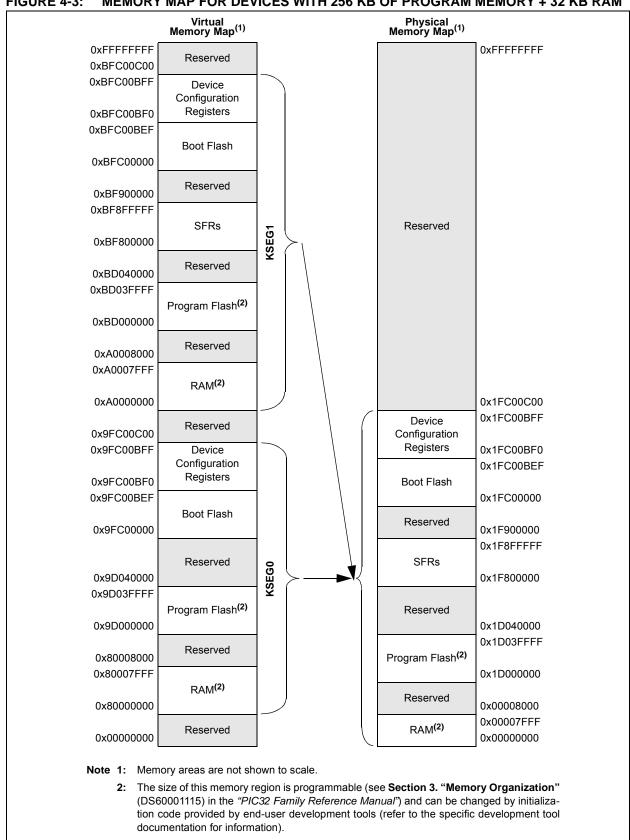

## FIGURE 4-3: MEMORY MAP FOR DEVICES WITH 256 KB OF PROGRAM MEMORY + 32 KB RAM

## REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = EOF error condition detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

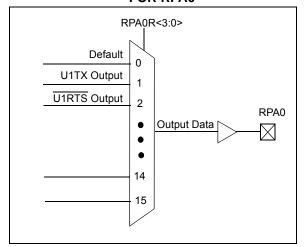

## 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

## FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

## 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

## 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

## TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

|                             |                  | 31:16     | _     | _     | _     | -     | _     | _     | _    | -    | -    | _    | -    | _    | _    | _    | -      | _    | 00         |

| FB88                        | RPC2R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2 | 2<3:0> |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FB8C                        | RPC3R            | 15:0      | _     | —     | —     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPC  | 3<3:0> |      | 00         |

| 5000                        | 00040            | 31:16     | _     | —     | —     | _     | —     | —     | _    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FB90                        | RPC4R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    |      | RPC4 | <3:0>  |      | 00         |

| 5004                        | 000400           | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBB4                        | RPC13R           | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1 | 3<3:0> |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | _    | _    | _      |      | 00         |

| FBB8                        | RPC14R           | 15:0      | _     | _     | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPC1 | 4<3:0> |      | 00         |

| 50.00                       | 00000            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBC0                        | RPD0R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      |      | RPD  | )<3:0> |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FBC4                        | RPD1R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD' | <3:0>  |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | _    | _    | _      |      | 00         |

| FBC8                        | RPD2R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD2 | 2<3:0> |      | 00         |

| 5000                        | 00000            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBCC                        | RPD3R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 3<3:0> |      | 00         |

| 5000                        | 00040            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBD0                        | RPD4R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD4 | <3:0>  |      | 00         |

|                             | 00050            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBD4                        | RPD5R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 5<3:0> |      | 00         |

|                             |                  | 31:16     | —     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —    | —      |      | 00         |

| FBE0                        | RPD8R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD8 | 3<3:0> |      | 00         |

| 5054                        | 00000            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBE4                        | RPD9R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD9 | 9<3:0> |      | 00         |

|                             |                  | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBE8                        | RPD10R           | 15:0      | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD1 | 0<3:0> |      | 00         |

|                             | 000440           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | —    | _    | _      | —    | 00         |

| FBEC                        | RPD11R           | 15:0      | —     | _     | —     | _     | —     | —     | _    | —    | _    | _    | _    | _    |      | RPD1 | 1<3:0> |      | 00         |

| FDFC                        |                  | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF0                        | RPD12R           | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | _    |      | RPD1 | 2<3:0> |      | 00         |

| EDEC                        |                  | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF8                        | RPD14R           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPD1 | 4<3:0> |      | 00         |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

## REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- • 0001 = Wait of 2 Трв

- 0000 = Wait of 1 TPB (default)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                      | _                      | _                 |                   | -                 | _                 | -                | —                |  |  |  |

| 22:16        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                      | —                      | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | WCS2 <sup>(1)</sup>    | WCS1 <sup>(3)</sup>    |                   |                   |                   | 2 < 1 2 . 0 >     |                  |                  |  |  |  |

|              | WADDR15 <sup>(2)</sup> | WADDR14 <sup>(4)</sup> |                   | WADDR<13:8>       |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | WADDR<7:0>             |                        |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 20-8: PMWADDR: PARALLEL PORT WRITE ADDRESS REGISTER

## Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 31-16 Unimplemented: Read as '0'

- bit 15 WCS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 WADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 WCS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 WADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 WADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

## REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER (CONTINUED)

```

bit 21-16 CH0SA<5:0>: Positive Input Select bits for Sample A Multiplexer Setting

For 64-pin devices:

011110 = Channel 0 positive input is Open<sup>(1)</sup>

011101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

011100 = Channel 0 positive input is IVREF<sup>(3)</sup>

011011 = Channel 0 positive input is AN27

000001 = Channel 0 positive input is AN1

000000 = Channel 0 positive input is AN0

For 100-pin devices:

110010 = Channel 0 positive input is Open<sup>(1)</sup>

110001 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

110000 = Channel 0 positive input is IVREF<sup>(3)</sup>

101111 = Channel 0 positive input is AN47

0000001 = Channel 0 positive input is AN1

0000000 = Channel 0 positive input is AN0

bit 15-0

Unimplemented: Read as '0'

```

- Note 1: This selection is only used with CTMU capacitive and time measurement.

- 2: See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

| REGISTE  | ER 23-3:       | C1INT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                             |

|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | 1 = A bus      | CAN Bus Activity Wake-up Interrupt Flag bit<br>wake-up activity interrupt has occurred<br>wake-up activity interrupt has not occurred |

| bit 13   | 1 = A CAI      | CAN Bus Error Interrupt Flag bit<br>N bus error has occurred<br>N bus error has not occurred                                          |

| bit 12   | SERRIF:        | System Error Interrupt Flag bit <sup>(1)</sup>                                                                                        |

|          |                | tem error occurred (typically an illegal address was presented to the system bus)<br>tem error has not occurred                       |

| bit 11   | <b>RBOVIF:</b> | Receive Buffer Overflow Interrupt Flag bit                                                                                            |

|          |                | eive buffer overflow has occurred<br>eive buffer overflow has not occurred                                                            |

| bit 10-4 | Unimpler       | nented: Read as '0'                                                                                                                   |

| bit 3    | MODIF: C       | CAN Mode Change Interrupt Flag bit                                                                                                    |

|          |                | N module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP)<br>N module mode change has not occurred                  |

| bit 2    | CTMRIF:        | CAN Timer Overflow Interrupt Flag bit                                                                                                 |

|          |                | N timer (CANTMR) overflow has occurred<br>N timer (CANTMR) overflow has not occurred                                                  |

| bit 1    | RBIF: Re       | ceive Buffer Interrupt Flag bit                                                                                                       |

|          |                | eive buffer interrupt is pending<br>eive buffer interrupt is not pending                                                              |

| bit 0    | TBIF: Tra      | nsmit Buffer Interrupt Flag bit                                                                                                       |

|          | 1 = A tran     | ismit buffer interrupt is pending                                                                                                     |

- 0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (C1CON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | _                 | —                | -                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

## REGISTER 23-7: C1RXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RXOVF<15:0>: FIFOx Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

## REGISTER 23-8: C1TMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 51.24        |                   | CANTS<15:8>       |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | CANTS<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | CANTSPRE<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CANTSPF           | RE<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (C1CON<20>) is set.

## bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits 1111 1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks . . 0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** C1TMR will be paused when CANCAP = 0.

2: The C1TMR prescaler count will be reset on any write to C1TMR (CANTSPRE will be unaffected).

## REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 20-16 FSEL10<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN9: Filter 9 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

## REGISTER 23-16: C1FIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0 THROUGH 15) (CONTINUED)

- bit 7 TXEN: TX/RX Buffer Selection bit 1 = FIFO is a Transmit FIFO 0 = FIFO is a Receive FIFO TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully TXLARB: Message Lost Arbitration bit<sup>(3)</sup> bit 5 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received. TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority

- 01 Low Internetiate message

- 00 = Lowest message priority

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (C1CON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

|              |                   | -                 | -                 | -                 | -                 | •                 |                    |                    |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |

| 31:24        | R-x                | R-x                |  |  |

| 31.24        |                   |                   |                   | C1FIFOU/          | An<31:24>         |                   |                    |                    |  |  |

| 23:16        | R-x                | R-x                |  |  |

| 23.10        |                   |                   |                   | C1FIFOU/          | An<23:16>         |                   |                    |                    |  |  |

| 15:8         | R-x                | R-x                |  |  |

| 10.0         | C1FIFOUAn<15:8>   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |

| 7:0          | C1FIFOUAn<7:0>    |                   |                   |                   |                   |                   |                    |                    |  |  |

### REGISTER 23-18: C1FIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' ('n' = 0 THROUGH 15)

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-0 C1FIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

### REGISTER 23-19: C1FIFOCIn: CAN MODULE MESSAGE INDEX REGISTER 'n' ('n' = 0 THROUGH 15)

|              | · · · · · · · · · · · · · · · · · · · |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0                                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                                     | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 23:16        | U-0                                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                                     | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 15:8         | U-0                                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | —                                     | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 7:0          | U-0                                   | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | _                                     | _                 | _                 | C1FIFOCIn<4:0>    |                   |                   |                  |                  |  |

### Legend:

| •                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-5 Unimplemented: Read as '0'

bit 4-0 C1FIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL<1:0>        |                   | _                   | CREF              |                   |                   | CCH              | <1:0>            |

### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

## bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

## bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

## 28.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-up Timer" (DS60001114), Section 32. "Configuration" (DS60001124) and Section 33. "Programming and Diagnostics" (DS60001129) in the "PIC32 Family Reference Manual", which are available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- Flexible device configuration

- Watchdog Timer (WDT)

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

## 28.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- CFGCON: Configuration Control Register

In addition, the DEVID register (Register 28-6) provides device and revision information.

## REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-10 **PWP<9:0>:** Program Flash Write-Protect bits

| dit 19-10     | <b>PWP&lt;9:0&gt;:</b> Program Flash Write-Protect bits                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. |

|               | 1111111111 = Disabled                                                                                                                                                                            |

|               | 1111111110 = Memory below 0x0400 address is write-protected<br>1111111101 = Memory below 0x0800 address is write-protected                                                                       |

|               | 1111111100 = Memory below 0x0000 address is write-protected                                                                                                                                      |

|               | 1111111011 = Memory below 0x1000 (4K) address is write-protected                                                                                                                                 |

|               | 1111111010 = Memory below 0x1400 address is write-protected                                                                                                                                      |

|               | 1111111001 = Memory below 0x1800 address is write-protected                                                                                                                                      |

|               | 1111111000 = Memory below 0x1C00 address is write-protected<br>1111110111 = Memory below 0x2000 (8K) address is write-protected                                                                  |

|               | 1111110110 = Memory below 0x2400 address is write-protected                                                                                                                                      |

|               | 1111110101 = Memory below 0x2800 address is write-protected                                                                                                                                      |

|               | 1111110100 = Memory below 0x2C00 address is write-protected                                                                                                                                      |

|               | 1111110011 = Memory below 0x3000 address is write-protected                                                                                                                                      |

|               | 1111110010 = Memory below 0x3400 address is write-protected<br>1111110001 = Memory below 0x3800 address is write-protected                                                                       |

|               | 1111110000 = Memory below 0x3C00 address is write-protected                                                                                                                                      |

|               | 1111101111 = Memory below 0x4000 (16K) address is write-protected                                                                                                                                |

|               | •                                                                                                                                                                                                |

|               | •<br>1110111111 = Memory below 0x10000 (64K) address is write-protected                                                                                                                          |

|               | •                                                                                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | 1101111111 = Memory below 0x20000 (128K) address is write-protected                                                                                                                              |

|               | •                                                                                                                                                                                                |

|               | •                                                                                                                                                                                                |

|               | 1011111111 = Memory below 0x40000 (256K) address is write-protected                                                                                                                              |

|               |                                                                                                                                                                                                  |

|               | O111111111 = Memory below 0x80000 (512K) address is write-protected                                                                                                                              |

|               | •                                                                                                                                                                                                |

|               | •                                                                                                                                                                                                |

|               | •<br>000000000 = All possible memory is write-protected                                                                                                                                          |

|               | <b>Note:</b> These bits are effective only if Boot Flash is also protected by clearing the BWP bit                                                                                               |

|               | (DEVCFG0<24>).                                                                                                                                                                                   |

| bit 9-5       | Reserved: Write '1'                                                                                                                                                                              |

| bit 4-3       | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits                                                                                                                      |

|               | 11 = PGEC1/PGED1 pair is used                                                                                                                                                                    |

|               | 10 = PGEC2/PGED2 pair is used                                                                                                                                                                    |

|               | 01 = PGEC3/PGED3 pair is used<br>00 = Reserved                                                                                                                                                   |

| <b>h</b> it 0 |                                                                                                                                                                                                  |

| bit 2         | JTAGEN: JTAG Enable bit <sup>(1)</sup><br>1 = JTAG is enabled                                                                                                                                    |

|               | 0 = JTAG is disabled                                                                                                                                                                             |

| bit 1-0       | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)                                                                                             |

|               | 1x = Debugger is disabled                                                                                                                                                                        |

|               | 0x = Debugger is enabled                                                                                                                                                                         |

|               |                                                                                                                                                                                                  |

| Note 1.       | This bit sets the value for the JTAGEN bit in the CEGCON register                                                                                                                                |

## **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

| DC CHARACTERISTICS                   |       |                                      |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |            |                                               |  |  |  |

|--------------------------------------|-------|--------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-----------------------------------------------|--|--|--|

| Param.<br>No. Symbol Characteristics |       |                                      | Min. Typical <sup>(1)</sup> |                                                                                                                                                                                                                                                                                     | Max. | Units      | Conditions                                    |  |  |  |

|                                      |       | Program Flash Memory <sup>(3)</sup>  |                             |                                                                                                                                                                                                                                                                                     |      |            |                                               |  |  |  |

| D130                                 | Eр    | Cell Endurance                       | 20,000                      | —                                                                                                                                                                                                                                                                                   | _    | E/W        | _                                             |  |  |  |

| D131                                 | Vpr   | VDD for Read                         | 2.3                         | —                                                                                                                                                                                                                                                                                   | 3.6  | V          | _                                             |  |  |  |

| D132                                 | VPEW  | VDD for Erase or Write               | 2.3                         | —                                                                                                                                                                                                                                                                                   | 3.6  | V          | _                                             |  |  |  |

| D134                                 | TRETD | Characteristic Retention             | 20                          | _                                                                                                                                                                                                                                                                                   | —    | Year       | Provided no other specifications are violated |  |  |  |

| D135                                 | IDDP  | Supply Current during<br>Programming | _                           | 10                                                                                                                                                                                                                                                                                  | —    | mA         | _                                             |  |  |  |

|                                      | Tww   | Word Write Cycle Time                | —                           | 411                                                                                                                                                                                                                                                                                 | _    | FRC Cycles | See Note 4                                    |  |  |  |

| D136                                 | Trw   | Row Write Cycle Time                 | —                           | 6675                                                                                                                                                                                                                                                                                | _    | FRC Cycles | See Note 2,4                                  |  |  |  |

| D137                                 | TPE   | Page Erase Cycle Time                | —                           | 20011                                                                                                                                                                                                                                                                               | _    | FRC Cycles | See Note 4                                    |  |  |  |

|                                      | TCE   | Chip Erase Cycle Time                | —                           | 80180                                                                                                                                                                                                                                                                               | _    | FRC Cycles | See Note 4                                    |  |  |  |

## TABLE 31-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 31-19) and FRC tuning values (See Register 8-2).

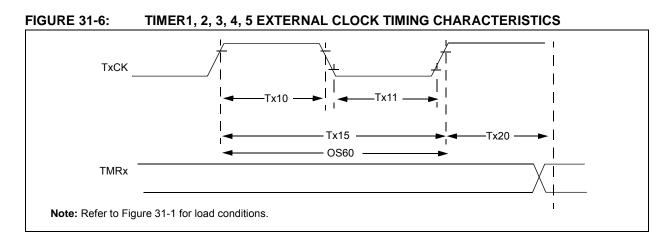

## TABLE 31-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS | TICS <sup>(1)</sup>                       |                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                            |         |                                   |       |                               |    |                               |

|---------------|-----------|-------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|-----------------------------------|-------|-------------------------------|----|-------------------------------|

| Param.<br>No. | Symbol    | Characteristics <sup>(2)</sup>            |                                                                   | Min.                                                                                                                                                                                                                                                                                  |                                            | Typical | Max.                              | Units | Conditions                    |    |                               |

| TA10          | T⊤xH      | TxCK<br>High Time                         | Synchronou<br>with presca                                         |                                                                                                                                                                                                                                                                                       | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —       | —                                 | ns    | Must also meet parameter TA15 |    |                               |

|               |           |                                           | Asynchrono<br>with presca                                         |                                                                                                                                                                                                                                                                                       | 10                                         | —       | _                                 | ns    | —                             |    |                               |

| TA11          | T⊤xL      | TxCK<br>Low Time                          | Synchronous,<br>with prescaler<br>Asynchronous,<br>with prescaler |                                                                                                                                                                                                                                                                                       | •                                          |         | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns | —     | _                             | ns | Must also meet parameter TA15 |

|               |           |                                           |                                                                   |                                                                                                                                                                                                                                                                                       | 10                                         | _       | _                                 | ns    | —                             |    |                               |

| TA15          | ΤτχΡ      | TxCK<br>Input Period                      | Synchronou with presca                                            |                                                                                                                                                                                                                                                                                       | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns | —       | —                                 | ns    | VDD > 2.7V                    |    |                               |

|               |           |                                           |                                                                   |                                                                                                                                                                                                                                                                                       | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns | -       | —                                 | ns    | VDD < 2.7V                    |    |                               |

|               |           |                                           |                                                                   |                                                                                                                                                                                                                                                                                       | Asynchronous, with prescaler               |         | 20                                | —     | —                             | ns | VDD > 2.7V<br>(Note 3)        |

|               |           |                                           |                                                                   |                                                                                                                                                                                                                                                                                       | 50                                         | -       | _                                 | ns    | VDD < 2.7V<br>(Note 3)        |    |                               |

| OS60          | FT1       |                                           |                                                                   |                                                                                                                                                                                                                                                                                       | 32                                         | —       | 100                               | kHz   | —                             |    |                               |

| TA20          | TCKEXTMRL | Delay from E<br>Clock Edge t<br>Increment |                                                                   | K                                                                                                                                                                                                                                                                                     |                                            |         | 1                                 | Трв   | —                             |    |                               |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

NOTES:

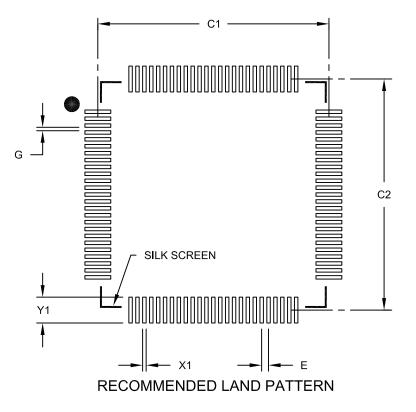

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS      |          |       |      |  |

|---------------------------|------------------|----------|-------|------|--|

| Dimension                 | Dimension Limits |          |       |      |  |

| Contact Pitch E           |                  | 0.40 BSC |       |      |  |

| Contact Pad Spacing       | C1               |          | 13.40 |      |  |

| Contact Pad Spacing       | C2               |          | 13.40 |      |  |

| Contact Pad Width (X100)  | X1               |          |       | 0.20 |  |

| Contact Pad Length (X100) | Y1               |          |       | 1.50 |  |

| Distance Between Pads     | G                | 0.20     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B