Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128ht-v-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES (CONTINUED)

| 10    | 100-PIN TQFP (TOP VIEW)                                                                                        |     |       |                           |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------|--|--|--|--|--|--|

|       | PIC32MX230F128L<br>PIC32MX530F128L<br>PIC32MX250F256L<br>PIC32MX550F256L<br>PIC32MX270F512L<br>PIC32MX570F512L |     |       | 100                       |  |  |  |  |  |  |

|       |                                                                                                                |     |       | 1                         |  |  |  |  |  |  |

| Pin # | Full Pin Name                                                                                                  |     | Pin # | Full Pin Name             |  |  |  |  |  |  |

| 71    | RPD11/PMA14/RD11                                                                                               | 1 1 | 86    | VDD                       |  |  |  |  |  |  |

| 72    | RPD0/INT0/RD0                                                                                                  | ĪĪ  | 87    | AN44/C3INA/RPF0/PMD11/RF0 |  |  |  |  |  |  |

| 73    | SOSCI/RPC13/RC13                                                                                               | ĪĪ  | 88    | AN45/RPF1/PMD10/RF1       |  |  |  |  |  |  |

| 74    | SOSCO/RPC14/T1CK/RC14                                                                                          | t t | 89    | RPG1/PMD9/RG1             |  |  |  |  |  |  |

| 75    | Vss                                                                                                            | Ī   | 90    | RPG0/PMD8/RG0             |  |  |  |  |  |  |

| 76    | AN24/RPD1/RD1                                                                                                  | 11  | 91    | RA6                       |  |  |  |  |  |  |

| 77    | AN25/RPD2/RD2                                                                                                  | 11  | 92    | CTED8/RA7                 |  |  |  |  |  |  |

| 78    | AN26/C3IND/RPD3/RD3                                                                                            | ] [ | 93    | AN46/PMD0/RE0             |  |  |  |  |  |  |

| 79    | AN40/RPD12/PMD12/RD12                                                                                          | [   | 94    | AN47/PMD1/RE1             |  |  |  |  |  |  |

| 80    | AN41/PMD13/RD13                                                                                                | [   | 95    | RG14                      |  |  |  |  |  |  |

| 81    | RPD4/PMWR/RD4                                                                                                  | [   | 96    | RG12                      |  |  |  |  |  |  |

| 82    | RPD5/PMRD/RD5                                                                                                  | [   | 97    | RG13                      |  |  |  |  |  |  |

| 83    | AN42/C3INC/PMD14/RD6                                                                                           | ] [ | 98    | AN20/PMD2/RE2             |  |  |  |  |  |  |

| 84    | AN43/C3INB/PMD15/RD7                                                                                           | [   | 99    | RPE3/CTPLS/PMD3/RE3       |  |  |  |  |  |  |

| 85    | VCAP                                                                                                           | [   | 100   | AN21/PMD4/RE4             |  |  |  |  |  |  |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

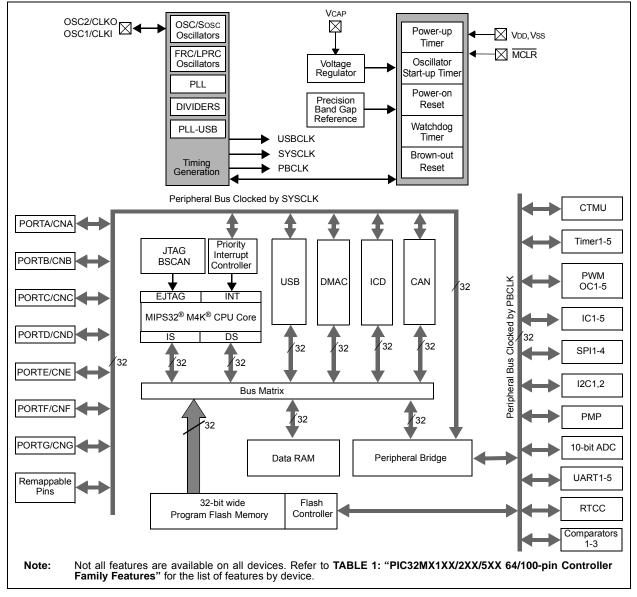

## 1.0 DEVICE OVERVIEW

Note 1: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). This document contains device-specific information for PIC32MX1XX/2XX/5XX 64/100-pin devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX/ 5XX 64/100-pin family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: PIC32MX1XX/2XX/5XX 64/100-PIN BLOCK DIAGRAM

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 3 and MPLAB REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide"* DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer or debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements

## 2.7 External Oscillator Pins

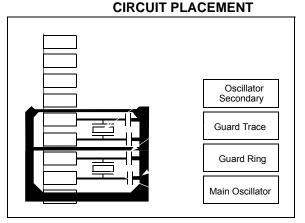

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED OSCILLATOR

<sup>© 2014-2016</sup> Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   |                   |                   | BMXPFN            | ISZ<31:24>        |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

## Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash 0x00080000 = Device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

|              |                   |                   |                   | . ,               |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   |                   |                   | BMXBOO            | TSZ<31:24>        |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         |                   |                   |                   | BMXBOC            | )TSZ<15:8>        |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00000C00 = Device has 3 KB Boot Flash

© 2014-2016 Microchip Technology Inc.

| Interment Course (1)                       | 100 # | Vector<br># |               | Interru      | pt Bit Location |              | Persistent |

|--------------------------------------------|-------|-------------|---------------|--------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>            | IRQ # |             | Flag          | Enable       | Priority        | Sub-priority | Interrupt  |

| CNA – PORTA Input Change Interrupt         | 44    | 33          | IFS1<12>      | IEC1<12>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNB – PORTB Input Change Interrupt         | 45    | 33          | IFS1<13>      | IEC1<13>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNC – PORTC Input Change Interrupt         | 46    | 33          | IFS1<14>      | IEC1<14>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CND – PORTD Input Change Interrupt         | 47    | 33          | IFS1<15>      | IEC1<15>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNE – PORTE Input Change Interrupt         | 48    | 33          | IFS1<16>      | IEC1<16>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNF – PORTF Input Change Interrupt         | 49    | 33          | IFS1<17>      | IEC1<17>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNG – PORTG Input Change Interrupt         | 50    | 33          | IFS1<18>      | IEC1<18>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| PMP – Parallel Master Port                 | 51    | 34          | IFS1<19>      | IEC1<19>     | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMPE – Parallel Master Port Error          | 52    | 34          | IFS1<20>      | IEC1<20>     | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| SPI2E – SPI2 Fault                         | 53    | 35          | IFS1<21>      | IEC1<21>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2RX – SPI2 Receive Done                 | 54    | 35          | IFS1<22>      | IEC1<22>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2TX – SPI2 Transfer Done                | 55    | 35          | IFS1<23>      | IEC1<23>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| U2E – UART2 Error                          | 56    | 36          | IFS1<24>      | IEC1<24>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2RX – UART2 Receiver                      | 57    | 36          | IFS1<25>      | IEC1<25>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2TX – UART2 Transmitter                   | 58    | 36          | IFS1<26>      | IEC1<26>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| I2C2B – I2C2 Bus Collision Event           | 59    | 37          | IFS1<27>      | IEC1<27>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2S – I2C2 Slave Event                   | 60    | 37          | IFS1<28>      | IEC1<28>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2M – I2C2 Master Event                  | 61    | 37          | IFS1<29>      | IEC1<29>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U3E – UART3 Error                          | 62    | 38          | IFS1<30>      | IEC1<30>     | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U3RX – UART3 Receiver                      | 63    | 38          | IFS1<31>      | IEC1<31>     | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U3TX – UART3 Transmitter                   | 64    | 38          | IFS2<0>       | IEC2<0>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U4E – UART4 Error                          | 65    | 39          | IFS2<1>       | IEC2<1>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U4RX – UART4 Receiver                      | 66    | 39          | IFS2<2>       | IEC2<2>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U4TX – UART4 Transmitter                   | 67    | 39          | IFS2<3>       | IEC2<3>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U5E – UART5 Error <sup>(2)</sup>           | 68    | 40          | IFS2<4>       | IEC2<4>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69    | 40          | IFS2<5>       | IEC2<5>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70    | 40          | IFS2<6>       | IEC2<6>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| CTMU – CTMU Event <sup>(2)</sup>           | 71    | 41          | IFS2<7>       | IEC2<7>      | IPC10<12:10>    | IPC10<9:8>   | Yes        |

| DMA0 – DMA Channel 0                       | 72    | 42          | IFS2<8>       | IEC2<8>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA1 – DMA Channel 1                       | 73    | 43          | IFS2<9>       | IEC2<9>      | IPC10<28:26>    | IPC10<25:24> | No         |

| DMA2 – DMA Channel 2                       | 74    | 44          | IFS2<10>      | IEC2<10>     | IPC11<4:2>      | IPC11<1:0>   | No         |

| DMA3 – DMA Channel 3                       | 75    | 45          | IFS2<11>      | IEC2<11>     | IPC11<12:10>    | IPC11<9:8>   | No         |

| CMP3 – Comparator 3 Interrupt              | 76    | 46          | IFS2<12>      | IEC2<12>     | IPC11<20:18>    | IPC11<17:16> | No         |

| CAN1 – CAN1 Event                          | 77    | 47          | IFS2<13>      | IEC2<13>     | IPC11<28:26>    | IPC11<25:24> | Yes        |

| SPI3E – SPI3 Fault                         | 78    | 48          | IFS2<14>      | IEC2<14>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI3RX – SPI3 Receive Done                 | 79    | 48          | IFS2<15>      | IEC2<15>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI3TX – SPI3 Transfer Done                | 80    | 48          | IFS2<16>      | IEC2<16>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81    | 49          | IFS2<17>      | IEC2<17>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82    | 49          | IFS2<18>      | IEC2<18>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83    | 49          | IFS2<19>      | IEC2<19>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

|                                            | •     | Lowe        | st Natural Or | der Priority |                 |              |            |

#### TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | _                | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                    |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 10.0         | —                 | _                 |                   | —                 | _                 |                   | —                | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |

## REGISTER 7-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by har | HC = Cleared by hardware |                    |  |  |  |  |

|-------------------|---------------------|--------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bi     | t, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section

6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Runge        |                   |                   |                   |                   |                   |                   |                  |                  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | <7:0>             |                   |                  |                  |

## REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| =ogona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

<u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused.

#### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | 0 IIE. 00D        |                   |                   |                   |                   |                       |                         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0                   | U-0                     |

|              |                   | _                 | _                 | _                 | _                 | _                 | _                     | —                       |

| 23:16        | U-0                   | U-0                     |

| 23.10        |                   | _                 | _                 | _                 | _                 | _                 | _                     | —                       |

| 15:8         | U-0                   | U-0                     |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                       |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          |                   | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            |                   |                   |                       | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       | 1 = STALL interrupt enabled                   |

|       | 0 = STALL interrupt disabled                  |

#### bit 6 **ATTACHIE:** ATTACH Interrupt Enable bit 1 = ATTACH interrupt enabled

0 = ATTACH interrupt disabled

#### bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt enabled

- 0 = RESUME interrupt disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt enabled

- 0 = Idle interrupt disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt enabled

- 0 = TRNIF interrupt disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt enabled

- 0 = SOFIF interrupt disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt enabled

- 0 = USB Error interrupt disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt enabled

- 0 = URSTIF interrupt disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt enabled

- 0 = DATTCHIF interrupt disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|

| 24.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 31:24        | _                 | —                 | —                        |                   | —                     | —                     | _                | —                    |  |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 23:16        | —                 | _                 | —                        | _                 | —                     | _                     | _                | —                    |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 15.0         | —                 | —                 | —                        | —                 | —                     | _                     |                  | —                    |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |

| 7:0          |                   | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |

|              | JSTATE            | 320               | TOKBUSY <sup>(1,5)</sup> | USDROI            |                       | RESUME                | FFDROI           | SOFEN <sup>(5)</sup> |  |

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER

## Legend:

| Logonal           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE detected on the USB

- 0 = No JSTATE detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single Ended Zero detected on the USB

0 = No Single Ended Zero detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability enabled

- 0 = USB host capability disabled

#### bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling activated

- 0 = RESUME signaling disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

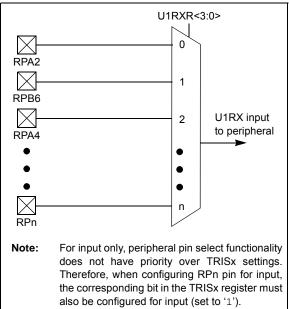

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

## FIGURE 11-2: REI

REMAPPABLE INPUT EXAMPLE FOR U1RX

#### TABLE 11-8: PORTD REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | _     | —     | _     |               | —             | —            |              | _            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0000                        | THOLLD                          | 15:0      | —     | —     | —     | —     |               |               | —            | _            | _            | —            | _            |              | ANSELD3      | ANSELD2      | ANSELD1      | —            | 000E          |

| 6310                        | TRISD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | _            |              | —            | _            |              | —            |              |              | 0000          |

| 0310                        | TRIOD                           | 15:0      | —     | —     | —     | _     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | OFFF          |

| 5320                        | PORTD                           | 31:16     | —     | _     | _     | _     | _             | _             | —            | _            | _            | _            | _            |              | _            | —            |              |              | 0000          |

| 3320                        | TORID                           | 15:0      | —     | —     | —     | _     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | —     | —     | —     | _     | —             | —             | _            | _            | _            | —            | _            | -            | —            | —            | _            | _            | 0000          |

| 0330                        | LAID                            | 15:0      | -     | _     | _     | _     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0340                        | ODCD                            | 15:0      | Ι     |       |       | -     | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 6350                        | CNPUD                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0330                        | CINFUD                          | 15:0      | -     | _     | _     | _     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 6360                        | CNPDD                           | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0300                        | CNFDD                           | 15:0      |       | _     | -     |       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 6270                        | CNCOND                          | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0370                        | CINCOIND                        | 15:0      | ON    | _     | SIDL  |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 6380                        | CNEND                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0300                        | CNEND                           | 15:0      | Ι     | -     | -     | Ι     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | _     | _             | _             | _            | _            | _            | _            | _            | _            | _            | —            |              | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | _     | _     | -     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5                  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|------------------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0                                | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                                  | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                                | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | _                 | _                                  | —                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0                              | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL                               | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0                              | R-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | - OC32 OCFLT <sup>(2)</sup> OCTSEL |                   |                   | OCM<2:0>          |                  |                  |

#### **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

## **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

#### 22.1 **Control Registers**

#### TABLE 22-1: ADC REGISTER MAP

| ess                         |                          | Ċ,            |                                     |                  |                  |                  |                  |                  |                 | Bi              | ts              |                 |                 |                 |                 |                  |                  |                  | 6          |

|-----------------------------|--------------------------|---------------|-------------------------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name         | Bit Range     | 31/15                               | 30/14            | 29/13            | 28/12            | 27/11            | 26/10            | 25/9            | 24/8            | 23/7            | 22/6            | 21/5            | 20/4            | 19/3            | 18/2             | 17/1             | 16/0             | All Resets |

|                             | AD1CON1 <sup>(1)</sup>   | 31:16         | —                                   | _                | —                | —                | _                |                  | —               | —               |                 | —               | _               | —               | _               | —                | _                | -                | 0000       |

| 3000                        | ADICONT                  | 15:0          | ON                                  | _                | SIDL             | —                | —                |                  | FORM<2:0>       | •               |                 | SSRC<2:0>       |                 | CLRASAM         | —               | ASAM             | SAMP             | DONE             | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup>   | 31:16         | —                                   | —                | —                | —                | _                | _                | —               | _               | _               | _               | —               | —               | —               | —                | —                | —                | 0000       |

|                             |                          | 15:0          | · ·                                 | VCFG<2:0>        | ><br>            | OFFCAL           |                  | CSCNA            | —               |                 | BUFS            |                 |                 | SMPI            | <3:0>           |                  | BUFM             | ALTS             | 0000       |

| 9020                        | AD1CON3(1)               | 31:16         | _                                   | _                | —                | —                | —                | _                | —               |                 | —               | —               | —               | —               | —               | —                | —                | —                | 0000       |

|                             |                          | 15:0          | ADRC                                | —                | _                |                  |                  | SAMC<4:0         | >               |                 | 0110114         |                 |                 | ADCS            |                 | = 0 (2)          |                  |                  | 0000       |

| 9040                        | AD1CHS <sup>(1)</sup>    | 31:16         | CH0NB                               |                  |                  |                  | CH0SB            | <5:0>(²)         |                 |                 | CH0NA           | _               |                 |                 | CH0SA           | <5:0>(²)         |                  |                  | 0000       |

|                             |                          | 15:0          | -                                   | —                | -                | -                | -                | -                | -               | -               | -               | -               | -               | -               | -               | -                | -                | -                | 0000       |

| 9050                        | AD1CSSL <sup>(1,3)</sup> | 31:16         | CSSL31<br>CSSL15                    | CSSL30<br>CSSL14 | CSSL29<br>CSSL13 | CSSL28<br>CSSL12 | CSSL27<br>CSSL11 | CSSL26<br>CSSL10 | CSSL25<br>CSSL9 | CSSL24<br>CSSL8 | CSSL23<br>CSSL7 | CSSL22<br>CSSL6 | CSSL21<br>CSSL5 | CSSL20<br>CSSL4 | CSSL19<br>CSSL3 | CSSL18<br>CSSL2  | CSSL17<br>CSSL1  | CSSL16<br>CSSL0  | 0000       |

|                             |                          | 15:0<br>31:16 | -                                   | C55L14           | C33L13           | -                | -                | C55L10           |                 | C33L0           | C33L7           | CSSLO           | -               |                 |                 | CSSL2<br>CSSL50  | CSSL1<br>CSSL49  | CSSL0<br>CSSL48  | 0000       |

| 9060                        | AD1CSSL2 <sup>(1)</sup>  | 15:0          | CSSL47                              | CSSL46           | CSSL45           | CSSL44           | CSSL43           | CSSL42           | CSSL41          | CSSL40          | CSSL39          | CSSL38          | CSSL37          | CSSL36          | —<br>CSSL35     | CSSL30<br>CSSL34 | CSSL49<br>CSSL33 | CSSL48<br>CSSL32 | 0000       |

|                             |                          | 31:16         | 000147                              | 000140           | 000140           | 000144           | 000140           | 000142           | 000141          | 000140          | 000109          | 000100          | 000107          | 000100          | 000100          | 000104           | 000100           | 000102           | 0000       |

| 9070                        | ADC1BUF0                 | 15:0          |                                     |                  |                  |                  |                  |                  | ADC Res         | ult Word 0      | (ADC1BUF        | 0<31:0>)        |                 |                 |                 |                  |                  |                  | 0000       |

|                             |                          | 31:16         |                                     |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  | 0000       |

| 9080                        | ADC1BUF1                 | 15:0          |                                     |                  |                  |                  |                  |                  | ADC Res         | ult Word 1      | (ADC1BUF        | 1<31:0>)        |                 |                 |                 |                  |                  |                  | 0000       |

| 9090                        | ADC1BUF2                 | 31:16         |                                     |                  |                  |                  |                  |                  |                 | ult Mard O      |                 | 0-21-05)        |                 |                 |                 |                  |                  |                  | 0000       |

| 9090                        | ADCIBUFZ                 | 15:0          |                                     |                  |                  |                  |                  |                  | ADC Res         | ult Word 2      | (ADC IBUF       | 2<31.0>)        |                 |                 |                 |                  |                  |                  | 0000       |

| 90A0                        | ADC1BUF3                 | 31:16         |                                     |                  |                  |                  |                  |                  |                 | ult Word 3      |                 | 3<31.0>)        |                 |                 |                 |                  |                  |                  | 0000       |

| 00/10                       | ABO IBOI 0               | 15:0          |                                     |                  |                  |                  |                  |                  | ABO NOS         |                 |                 | 0 10 1.04 )     |                 |                 |                 |                  |                  |                  | 0000       |

| 90B0                        | ADC1BUF4                 | 31:16         |                                     |                  |                  |                  |                  |                  | ADC Res         | ult Word 4      | (ADC1BUF        | 4<31:0>)        |                 |                 |                 |                  |                  |                  | 0000       |

|                             |                          | 15:0          |                                     |                  |                  |                  |                  |                  |                 |                 | (               | , ,             |                 |                 |                 |                  |                  |                  | 0000       |

| 90C0                        | ADC1BUF5                 | 31:16         |                                     |                  |                  |                  |                  |                  | ADC Res         | ult Word 5      | (ADC1BUF        | 5<31:0>)        |                 |                 |                 |                  |                  |                  | 0000       |

|                             |                          | 15:0          | 0000                                |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  |            |

| 90D0                        | ADC1BUF6                 | 31:16         | ADC Result Word 6 (ADC1BUF6<31:0>)  |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  |            |

|                             |                          | 15:0          |                                     |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  | 0000       |

| 90E0                        | ADC1BUF7                 | 31:16<br>15:0 |                                     |                  |                  |                  |                  |                  | ADC Res         | ult Word 7      | (ADC1BUF        | 7<31:0>)        |                 |                 |                 |                  |                  |                  | 0000       |

|                             |                          | 31:16         |                                     |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  | 0000       |

| 90F0                        | ADC1BUF8                 | 15:0          | ADC Result Word 8 (ADC1BLIE8<31:0>) |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  |            |

|                             | l                        | 10.0          | 0000                                |                  |                  |                  |                  |                  |                 |                 |                 |                 |                 |                 |                 |                  |                  |                  |            |

Legend: 3:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV registers" for details. Note 1: For 64-pin devices, the MSB of these bits is not available. 2:

For 64-pin devices, only the CSSL30:CSSL0 bits are available.

DS60001290D-page 233

Preliminary

## TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | đ             |       |                                                                                                    |  |  |  |  |         | Bi          | ts       |          |  |  |  |  | s            |

|-----------------------------|------------------|---------------|-------|----------------------------------------------------------------------------------------------------|--|--|--|--|---------|-------------|----------|----------|--|--|--|--|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 <b>Solution</b> |  |  |  |  |         |             |          |          |  |  |  |  |              |

| 9100                        | ADC1BUF9         | 31:16<br>15:0 |       |                                                                                                    |  |  |  |  | ADC Res | sult Word 9 | (ADC1BUF | 9<31:0>) |  |  |  |  | 0000<br>0000 |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |       |                                                                                                    |  |  |  |  | ADC Res | ult Word A  | (ADC1BUF | A<31:0>) |  |  |  |  | 0000<br>0000 |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       |                                                                                                    |  |  |  |  | ADC Res | ult Word B  | (ADC1BUF | B<31:0>) |  |  |  |  | 0000<br>0000 |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       |                                                                                                    |  |  |  |  | ADC Res | ult Word C  | (ADC1BUF | C<31:0>) |  |  |  |  | 0000<br>0000 |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       |                                                                                                    |  |  |  |  | ADC Res | ult Word D  | (ADC1BUF | D<31:0>) |  |  |  |  | 0000<br>0000 |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) 0000                                                            |  |  |  |  |         |             |          |          |  |  |  |  |              |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       |                                                                                                    |  |  |  |  | ADC Res | ult Word F  | (ADC1BUF | F<31:0>) |  |  |  |  | 0000<br>0000 |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for details.

2: For 64-pin devices, the MSB of these bits is not available.

3: For 64-pin devices, only the CSSL30:CSSL0 bits are available.

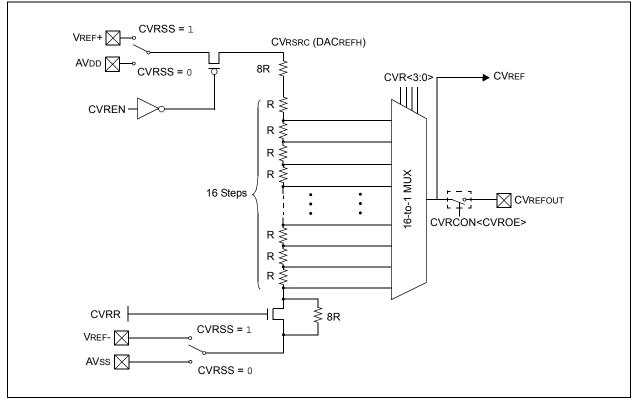

## 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

#### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

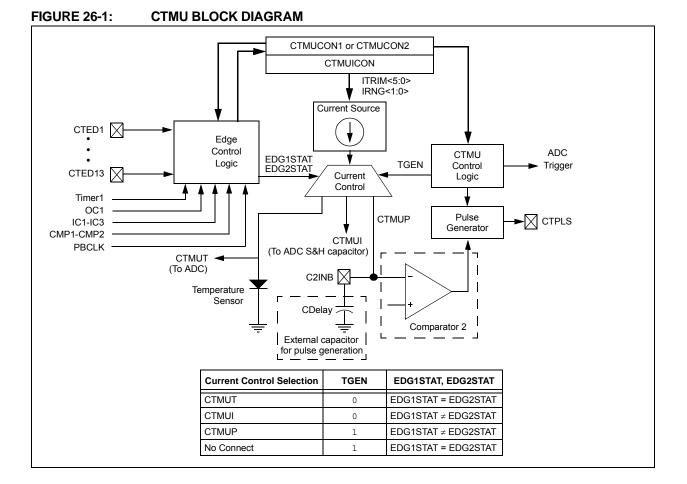

## 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167) in the "PIC32 Family Reference Manual", which is available the site from Microchip web (www.microchip.com).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The CTMU module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 26-1.

© 2014-2016 Microchip Technology Inc.

NOTES:

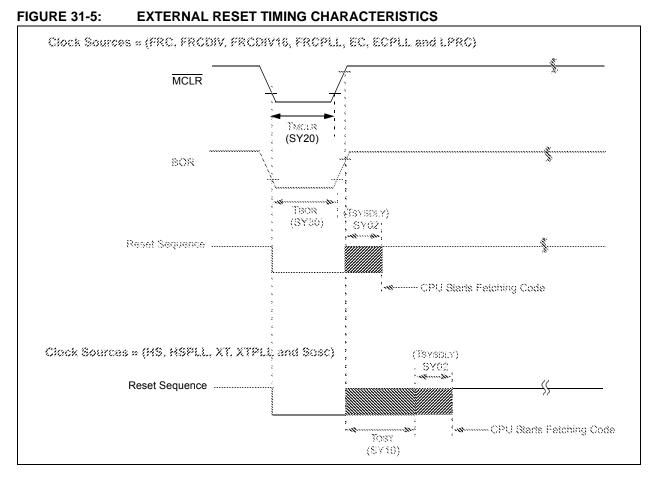

| AC CHA        | RACTERI | ISTICS                                                                                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                              |      |       |            |  |  |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|------------|--|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                                                                                             | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup>       | Max. | Units | Conditions |  |  |  |  |  |

| SY00          | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | —                                                                                                                                                                                                                                                                                     | 400                          | 600  | μS    |            |  |  |  |  |  |

| SY02          | TSYSDLY | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. |                                                                                                                                                                                                                                                                                       | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | _          |  |  |  |  |  |

| SY20          | TMCLR   | MCLR Pulse Width (low)                                                                                                                     | 2                                                                                                                                                                                                                                                                                     | _                            |      | μS    | —          |  |  |  |  |  |

| SY30          | TBOR    | BOR Pulse Width (low)                                                                                                                      | _                                                                                                                                                                                                                                                                                     | 1                            | —    | μS    | _          |  |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

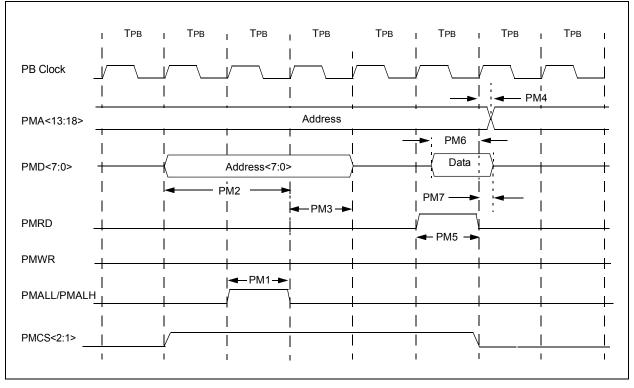

#### TABLE 31-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CH         | ARACTE       | RISTICS                                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |  |  |  |  |

|---------------|--------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|--|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions |  |  |  |  |  |