Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128l-50i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

|          | Pin Number             |                 |             |                |                                                                                           |  |  |

|----------|------------------------|-----------------|-------------|----------------|-------------------------------------------------------------------------------------------|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                               |  |  |

| RTCC     | 42                     | 68              | 0           |                | Real-Time Clock Alarm Output                                                              |  |  |

| CVREFOUT | 23                     | 34              | 0           | Analog         | Comparator Voltage Reference (Output)                                                     |  |  |

| C1INA    | 11                     | 20              | Ι           | Analog         |                                                                                           |  |  |

| C1INB    | 12                     | 21              | Ι           | Analog         |                                                                                           |  |  |

| C1INC    | 5                      | 11              | Ι           | Analog         | Comparator 1 Inputs                                                                       |  |  |

| C1IND    | 4                      | 10              | Ι           | Analog         |                                                                                           |  |  |

| C2INA    | 13                     | 22              | Ι           | Analog         |                                                                                           |  |  |

| C2INB    | 14                     | 23              | Ι           | Analog         | Comporator 2 Inputa                                                                       |  |  |

| C2INC    | 8                      | 14              | Ι           | Analog         | Comparator 2 Inputs                                                                       |  |  |

| C2IND    | 6                      | 12              | Ι           | Analog         |                                                                                           |  |  |

| C3INA    | 58                     | 87              | Ι           | Analog         |                                                                                           |  |  |

| C3INB    | 55                     | 84              | Ι           | Analog         | Comporator 2 Inputa                                                                       |  |  |

| C3INC    | 54                     | 83              | Ι           | Analog         | Comparator 3 Inputs                                                                       |  |  |

| C3IND    | 51                     | 78              | Ι           | Analog         |                                                                                           |  |  |

| C1OUT    | PPS                    | PPS             | 0           | _              | Comparator 1 Output                                                                       |  |  |

| C2OUT    | PPS                    | PPS             | 0           | _              | Comparator 2 Output                                                                       |  |  |

| C3OUT    | PPS                    | PPS             | 0           | _              | Comparator 3 Output                                                                       |  |  |

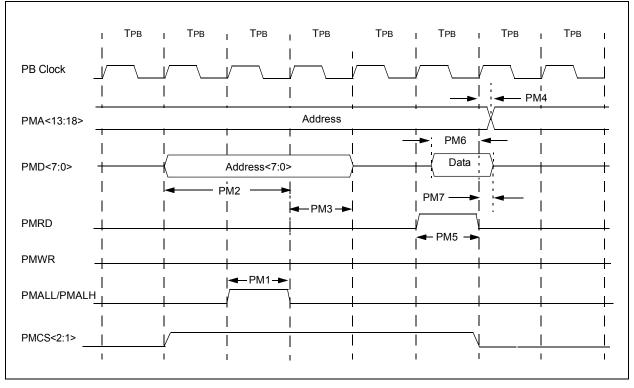

| PMALL    | 30                     | 44              | 0           | TTL/ST         | Parallel Master Port Address Latch Enable Low Byte                                        |  |  |

| PMALH    | 29                     | 43              | 0           | TTL/ST         | Parallel Master Port Address Latch Enable High Byte                                       |  |  |

| PMA0     | 30                     | 44              | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |  |  |

| PMA1     | 29                     | 43              | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |  |  |

| Legend:  | CMOS = CN              | IOS compat      | ible inpu   | it or output   | Analog = Analog input I = Input O = Output                                                |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input I = Input ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

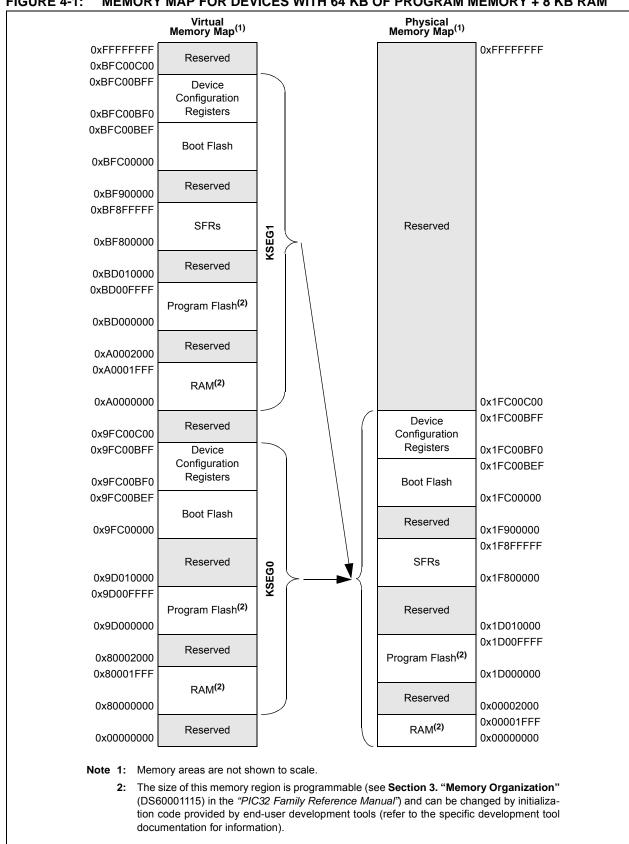

#### FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 64 KB OF PROGRAM MEMORY + 8 KB RAM

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | —                 |                   | —                 | _                 | —                 | -                | _                |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | -                 | —                 | —                 | _                 |                   |                  | —                |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   |                   |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |  |

#### REGISTER 5-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| zogonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

#### bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

|              |                   |                   |                   | -                 | -                 |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | DCRCDAT           | 4<31:24>          |                   |                  |                  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### **REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DCRCXOF           | <31:24>           |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | 5:8 DCRCXOR<15:8> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.10     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45-0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      |                   | CHSSA<15:8>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   | CHSSA<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\text{Note:}}$  This must be the physical address of the destination.

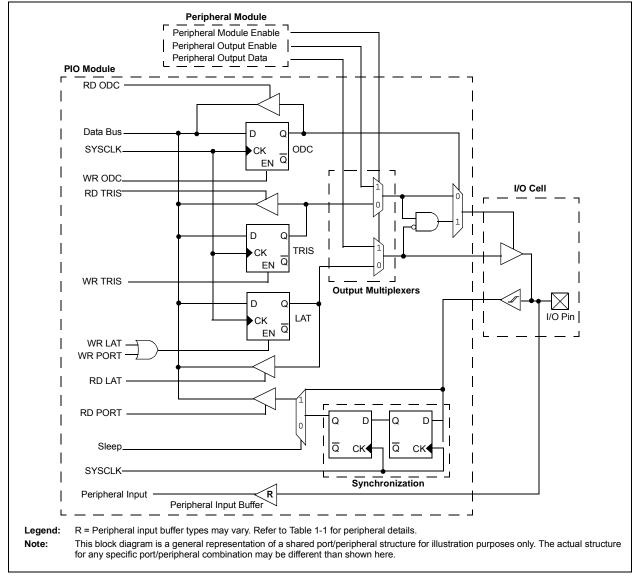

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

The following are the key features of this module:

- · Individual output pin open-drain enable or disable

- Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt

when change in pin state is detected

- Operation during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

## REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 2 **TSYNC:** Timer External Clock Input Synchronization Selection bit

- When TCS = 1:1 = External clock input is synchronized0 = External clock input is not synchronizedWhen TCS = 0:This bit is ignored.

- bit 1 **TCS:** Timer Clock Source Select bit 1 = External clock from TxCKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 4 DISSDI: Disable SDI bit

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

| REGISTE | ER 18-1: I2CxCON: I <sup>2</sup> C 'x' CONTROL REGISTER (CONTINUED)('x' = 1 AND 2)                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: General Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                             |

|         | <ul> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR<br/>(module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul>                                     |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                               |

|         | Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                                          |

| bit 5   | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                     |

|         | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                               |

|         | (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                        |

|         | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3   | <b>RCEN:</b> Receive Enable bit (when operating as $I^2C$ master)                                                                                                                                                    |

|         | 1 = Enables Receive mode for $I^2C$ . Hardware clear at end of eighth bit of master receive data byte.<br>0 = Receive sequence not in progress                                                                       |

| bit 2   | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                    |

|         | <ul><li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li><li>0 = Stop condition not in progress</li></ul>                                                       |

| bit 1   | RSEN: Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                |

|         | <ul> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of<br/>master Repeated Start sequence.</li> </ul>                                                                        |

|         | 0 = Repeated Start condition not in progress                                                                                                                                                                         |

| bit 0   | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                          |

|         | <ul> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition not in progress</li> </ul>                                                 |

|         |                                                                                                                                                                                                                      |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------------|--------------------------|--------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0                     | U-0                      | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                       | _                        | —                  | —                       | —                 |                   | _                | —                |  |  |  |

| 22:46        | U-0                     | U-0                      | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                       | _                        | —                  | —                       | —                 | _                 | —                | —                |  |  |  |

| 45.0         | R/W-0                   | R/W-0                    | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup>     | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | AMASK<3:0>(3)     |                   |                  |                  |  |  |  |

| 7.0          | R/W-0                   | R/W-0                    | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                         | ARPT<7:0> <sup>(3)</sup> |                    |                         |                   |                   |                  |                  |  |  |  |

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |

|-------------------|-------------------------------|----------------------|------------------------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

#### bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(3)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved; do not use

- 1011 = Reserved; do not use

- 11xx = Reserved; do not use

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

## **REGISTER 23-17:** C1FIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|

| 01.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24        | —                 | —                 | —                 | _                 | —                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16        | —                 | —                 | —                 | _                 | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |

| 15:8         | —                 | —                 | —                 | _                 | —                 | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |

| 7:0          | —                 | —                 | —                 | _                 | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

## bit 31-27 Unimplemented: Read as '0'

| DIL 31-21 | Unimplemented. Read as 0                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|           | 1 = Interrupt enabled for FIFO not full                                                                         |

|           | 0 = Interrupt disabled for FIFO not full                                                                        |

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit                                                      |

|           | <ul> <li>1 = Interrupt enabled for FIFO empty</li> <li>0 = Interrupt disabled for FIFO empty</li> </ul>         |

| hit 23-20 | Unimplemented: Read as '0'                                                                                      |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                         |

| DIC 13    | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

|           | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 16    | RXNEMPTYIE: Empty Interrupt Enable bit                                                                          |

|           | <ul> <li>1 = Interrupt enabled for FIFO not empty</li> <li>0 = Interrupt disabled for FIFO not empty</li> </ul> |

| hit 15 11 |                                                                                                                 |

| bit 10    | Unimplemented: Read as '0'                                                                                      |

| DICTO     | <b>TXNFULLIF:</b> Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                      |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full                                 |

|           | 0 = FIFO is full                                                                                                |

|           | TXEN = 0: (FIFO configured as a receive buffer)                                                                 |

|           | Unused, reads '0'                                                                                               |

|           |                                                                                                                 |

| Note 1:   | This bit is read-only and reflects the status of the FIFO.                                                      |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              |                   |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

NOTES:

| DC CHARACTERISTICS |        |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)                                                                                                                      |                        |            |       |                                                   |  |  |

|--------------------|--------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|--|

|                    |        |                                                         | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |       |                                                   |  |  |

| Param.<br>No.      | Symbol | Characteristics                                         | Min.                                                                                                                                                                                       | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |  |

|                    | VIL    | Input Low Voltage                                       |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

| DI10               |        | I/O Pins with PMP                                       | Vss                                                                                                                                                                                        | —                      | 0.15 Vdd   | V     |                                                   |  |  |

|                    |        | I/O Pins                                                | Vss                                                                                                                                                                                        | —                      | 0.2 Vdd    | V     |                                                   |  |  |

| DI18               |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                        | —                      | 0.3 VDD    | V     | SMBus disabled<br>(Note 4)                        |  |  |

| DI19               |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                        | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |

|                    | VIH    | Input High Voltage                                      |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

| DI20               |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                   | _                      | Vdd        | V     | (Note 4,6)                                        |  |  |

|                    |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                            | —                      | 5.5        | V     | (Note 4,6)                                        |  |  |

|                    |        | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                                                                                                                                                   | —                      | 5.5        | V     |                                                   |  |  |

| DI28               |        | SDAx, SCLx                                              | 0.65 VDD                                                                                                                                                                                   | —                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |

| DI29               |        | SDAx, SCLx                                              | 2.1                                                                                                                                                                                        | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |

| DI30               | ICNPU  | Change Notification<br>Pull-up Current                  | _                                                                                                                                                                                          | -200                   | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |

| DI31               | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup> | 50                                                                                                                                                                                         | 200                    | —          | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |

|                    | lı∟    | Input Leakage Current<br>(Note 3)                       |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

| DI50               |        | I/O Ports                                               | _                                                                                                                                                                                          | —                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |

| DI51               |        | Analog Input Pins                                       | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |

| DI55               |        | MCLR <sup>(2)</sup>                                     | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $VSS \le VPIN \le VDD$                            |  |  |

| DI56               |        | OSC1                                                    | -                                                                                                                                                                                          | —                      | <u>+</u> 1 | μΑ    | $VSS \le VPIN \le VDD,$ XT and HS modes           |  |  |

### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- **6:** The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

| AC CHA        | RACTERI       | ISTICS                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |             |            |                                              |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|----------------------------------------------|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                                   |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                                                               |                        | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)                |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                                                                     | —                      | 10          | MHz        | XT (Note 4)                                  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                                                                     | —                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                         |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                    | —                      | 25          | MHz        | HS (Note 5)                                  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                    | —                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                         |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                                                                    | 32.768                 | 100         | kHz        | Sosc (Note 4)                                |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                                                                     | _                      | _           | —          | See parameter<br>OS10 for Fosc<br>value      |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                                                                           | —                      | —           | ns         | EC (Note 4)                                  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —                                                                                                                                                                                                                                                                                     | —                      | 0.05 x Tosc | ns         | EC (Note 4)                                  |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                                                                     | 1024                   | _           | Tosc       | (Note 4)                                     |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | —                                                                                                                                                                                                                                                                                     | 2                      | —           | ms         | (Note 4)                                     |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             |                                                                                                                                                                                                                                                                                       | 12                     |             | mA/V       | VDD = 3.3V,<br>TA = +25°C<br><b>(Note 4)</b> |  |

## TABLE 31-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TcY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

**3:** PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

4: This parameter is characterized, but not tested in manufacturing.

#### TABLE 31-18: PLL CLOCK TIMING SPECIFICATIONS

|                                      |       |                                                                     | (unless of        | herwise | ture -40°C | $\leq$ Ta $\leq$ + | -85°C fo |                                      |

|--------------------------------------|-------|---------------------------------------------------------------------|-------------------|---------|------------|--------------------|----------|--------------------------------------|

| Param.<br>No. Symbol Characteristics |       |                                                                     | cs <sup>(1)</sup> | Min.    | Typical    | Max.               | Units    | Conditions                           |

| OS50                                 | Fplli | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                   | 3.92    | _          | 5                  | MHz      | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51                                 | Fsys  | On-Chip VCO System<br>Frequency                                     |                   | 60      | —          | 120                | MHz      | _                                    |

| OS52                                 | TLOCK | PLL Start-up Time (Lock Time)                                       |                   | _       | _          | 2                  | ms       | —                                    |

| OS53                                 | DCLK  | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      |                   | -0.25   | —          | +0.25              | %        | Measured over 100 ms<br>period       |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### TABLE 31-19: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS |                                                 | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                          |  |  |  |

|--------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------------------------------------|--|--|--|

| Param.<br>No.      | Characteristics                                 | Min.                                                                                                                                                                                                                                                                                 | Typical | Max. | Units | Conditions                               |  |  |  |

| Internal           | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                                      |         |      |       |                                          |  |  |  |

| F20a               | FRC                                             | -0.9                                                                                                                                                                                                                                                                                 | —       | +0.9 | %     | $-40^{\circ}C \leq TA \leq +85^{\circ}C$ |  |  |  |

| F20b               | FRC                                             | -2                                                                                                                                                                                                                                                                                   | _       | +2   | %     | $-40^{\circ}C \le TA \le +105^{\circ}C$  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 31-20: INTERNAL LPRC ACCURACY

| АС СНА                          | RACTERISTICS    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |            |  |  |

|---------------------------------|-----------------|-------------------------------------------------------|---------|------|-------|------------|--|--|

| Param.<br>No.                   | Characteristics | Min.                                                  | Typical | Max. | Units | Conditions |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |                                                       |         |      |       |            |  |  |

| F21                             | LPRC            | -15                                                   | —       | +15  | %     | —          |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

|               | AC CHAF    | ACTERISTICS                       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 5): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |      |       |                                                         |  |

|---------------|------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|

| Param.<br>No. | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                                                                                                               | Typical      | Max. | Units | Conditions                                              |  |

| ADC Ac        | curacy – N | leasurements with Inter           | nal VREF+/                                                                                                                                                                                                                                                                                         | REF-         |      |       |                                                         |  |

| AD20d         | Nr         | Resolution                        |                                                                                                                                                                                                                                                                                                    | 10 data bits | 3    | bits  | (Note 3)                                                |  |

| AD21d         | INL        | Integral Non-linearity            | > -1                                                                                                                                                                                                                                                                                               | -            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD22d         | DNL        | Differential Non-linearity        | > -1                                                                                                                                                                                                                                                                                               |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |

| AD23d         | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                                                                                               | —            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD24d         | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                                                                                               | -            | < 2  | Lsb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD25d         |            | Monotonicity                      | —                                                                                                                                                                                                                                                                                                  |              | _    | —     | Guaranteed                                              |  |

| Dynami        | c Performa | ance                              |                                                                                                                                                                                                                                                                                                    |              |      |       |                                                         |  |

| AD32b         | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                                                                                                                 | 58.5         | _    | dB    | (Notes 3,4)                                             |  |

| AD34b         | ENOB       | Effective Number of bits          | 9.0                                                                                                                                                                                                                                                                                                | 9.5          | _    | bits  | (Notes 3,4)                                             |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

**2:** With no missing codes.

3: These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.