Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128l-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

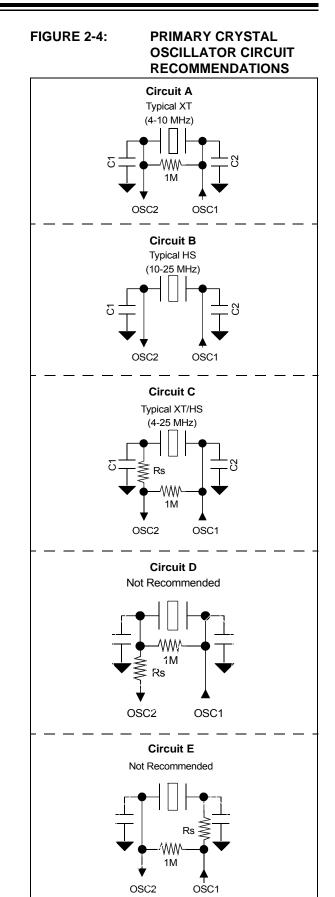

#### 2.7.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

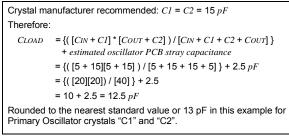

The following examples are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to  $\sim$ VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with  $\leq$  1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

2.7.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

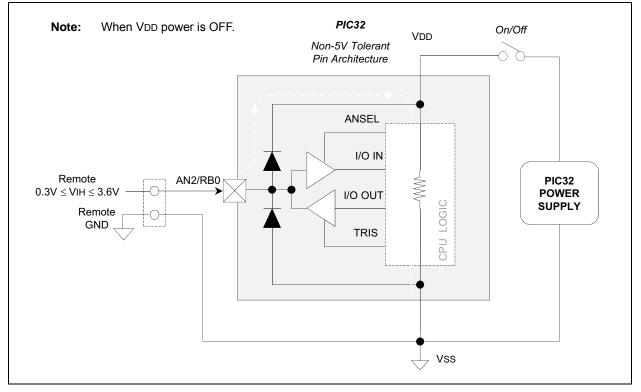

# 2.9 Considerations When Interfacing to Remotely Powered Circuits

# 2.9.1 NON-5V TOLERANT INPUT PINS

A quick review of the absolute maximum rating section in **31.0** "**40 MHz Electrical Characteristics**" will indicate that the voltage on any non-5v tolerant pin may not exceed AVDD/VDD + 0.3V. Figure 2-5 shows an example of a remote circuit using an independent power source, which is powered while connected to a PIC32 non-5V tolerant circuit that is not powered.

# FIGURE 2-5: PIC32 NON-5V TOLERANT CIRCUIT EXAMPLE

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 **Power Management**

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX-1XX/2XX/5XX 64/100-pin family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 31:24        | -                 | —                 |                   | —                 | _                 | —                 | -                | _                |  |  |  |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 23:16        | _                 | -                 | —                 | —                 | _                 |                   |                  | —                |  |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | _                 | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |  |  |  |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7.0          |                   |                   |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |  |  |  |  |  |

#### REGISTER 5-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| zogonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

#### bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

NOTES:

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 6         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |              |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3         | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _     | —        | _     | —        | _            | —      | —         |          | 0000       |

| 5260                        |                                 | 15:0      |       |       | _     |       | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>         |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | -     | _     | -     | _     | _     | _     | _    | _    | _     | —        | —     | —        | _            | -      | —         |          | 0000       |

| 5290                        | OT RMIR /                       | 15:0      | _     | —     | _     | —     | —     | —     | _    | —    | —     | —        | —     | —        | —            |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     |          | —            |        | -         | —        | 0000       |

| 5270                        | UTION                           | 15:0      | _     | —     |       | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |              | EP     | ><3:0>    |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | —        | _            | _      | —         |          | 0000       |

| 52BU                        | 0130F                           | 15:0      |       | _     |       | _     | _     | _     | _    | _    |       |          |       | CNT<7    | <b>'</b> :0> | -      | •         |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     |       | _     |       | _     | _     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     |       | _     |       | —     | —     | _    |      |       |          |       | BDTPTRH  | <23:16>      |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5200                        | OIBDIF5                         | 15:0      | _     |       | _     |       | —     | —     | _    |      |       |          |       | BDTPTRU  | <31:24>      |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 52L0                        | UICNIGI                         | 15:0      | _     |       | _     |       | —     | —     | _    |      | UTEYE | —        | _     | USBSIDL  | LSDEV        | _      | —         | UASUSPND | 0000       |

| 5300                        | U1EP0                           | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5500                        | UILFU                           | 15:0      | _     |       | _     |       | —     | —     | _    |      | LSPD  | RETRYDIS | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5510                        | UILFI                           | 15:0      | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | _     |       | _     |       | —     | —     | —    |      | _     | —        | —     | —        | —            | _      | —         |          | 0000       |

| 5520                        | UILFZ                           | 15:0      |       |       |       |       | _     | _     | _    | _    | _     | _        | —     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     | _     | —     | —     | —     | _    | —    | —     | —        | —     | —        | —            | —      | —         | _        | 0000       |

| 0000                        | 01EI 3                          | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | _     | _     | —     | —     | —    | —    | —     | —        | —     | _        | —            | —      | —         | _        | 0000       |

| 0040                        | 01214                           | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | _     | _     | —     | —     | —    | —    | —     | —        | —     | _        | —            | —      | —         | _        | 0000       |

| 5550                        | 01EI 5                          | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | _     | —     |       | —     | —     | —     | —    | —    | —     | —        | _     | _        | —            | —      | —         | —        | 0000       |

| 5500                        | 01LI 0                          | 15:0      | -     | _     | -     | —     | _     | —     | —    |      | _     | —        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | _     | —     | _     | —     | —     | —     | —    | —    | —     | -        | _     | —        | —            | —      | -         | —        | 0000       |

| 5570                        |                                 | 15:0      | -     | —     | -     | —     | _     | _     | —    | —    | —     | —        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | _     | —     | —     | —     | —    | —    | —     | —        | _     | —        | —            | —      | -         | —        | 0000       |

| 5500                        |                                 | 15:0      | -     | _     | -     | _     | —     | —     | _    | —    | _     | —        | —     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

DS60001290D-page 108

# TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit  | s    |      |          |        |        |         |        | (0         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     |       | —     | _     | _     | —    | _    |      | _    | —    | —        | _      | -      | —       |        | 0000       |

| 5390                        | UIEF9                           | 15:0      |       |       |       | _     | -     | -     | —    | _    | -    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | _     | _     |       | _     |       |       | _    |      | _    |      | _    | —        | -      |        | —       |        | 0000       |

| 55A0                        | UIEFIU                          | 15:0      | Ι     | Ι     |       | _     | -     | -     | _    | _    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | _     |       | _     | _     | —    | _    | _    | _    | —    | —        | _      | _      | —       | _      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | _     | _     |       | _     | _     | —    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | _     |       | _     | _     | —    | _    | _    | _    | —    | —        | _      | _      | —       | _      | 0000       |

| 5500                        | UIEF12                          | 15:0      | Ι     | _     | —     | _     | —     | —     | _    | —    | —    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | Ι     | _     | —     | _     | —     | —     | _    | —    | —    | _    | _    | —        | —      | —      | —       | —      | 0000       |

| 55D0                        | UIEF 13                         | 15:0      | Ι     | _     | —     | _     | —     | —     | _    | —    | —    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     |       |       | _     | _     | _    | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    |      |      | _    | _    |          | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    |      |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

#### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | 0 IIE. 00D        |                   |                   |                   |                   |                       |                         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0                   | U-0                     |

| 51.24        |                   | _                 | _                 | _                 | _                 | _                 | _                     | —                       |

| 23:16        | U-0                   | U-0                     |

| 23.10        |                   | _                 | _                 | _                 | _                 | _                 | _                     | —                       |

| 15:8         | U-0                   | U-0                     |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                       |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            |                   | SOFIE             | UERRIE''              | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       | 1 = STALL interrupt enabled                   |

|       | 0 = STALL interrupt disabled                  |

#### bit 6 **ATTACHIE:** ATTACH Interrupt Enable bit 1 = ATTACH interrupt enabled

0 = ATTACH interrupt disabled

#### bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt enabled

- 0 = RESUME interrupt disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt enabled

- 0 = Idle interrupt disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt enabled

- 0 = TRNIF interrupt disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt enabled

- 0 = SOFIF interrupt disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt enabled

- 0 = USB Error interrupt disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt enabled

- 0 = URSTIF interrupt disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt enabled

- 0 = DATTCHIF interrupt disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

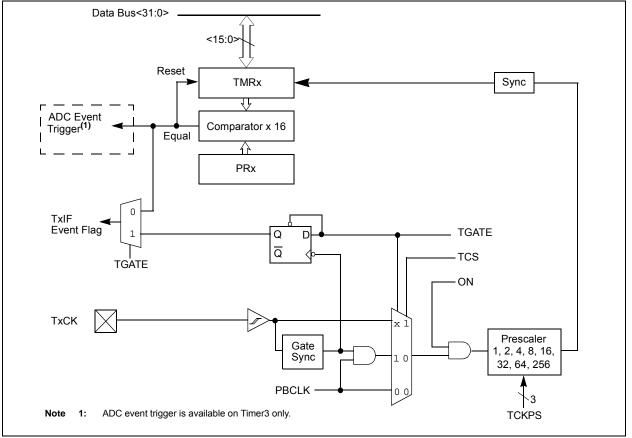

# 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

- Note: In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

# 13.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

# FIGURE 13-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | _                 | _                 | —                    | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | (                 |                   | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

# **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

# 26.1 Control Registers

# TABLE 26-1: CTMU REGISTER MAP

| ess                       |                                 | e         |         |         |          |       |         |          |          | Bits     |         |         |       |       |          |      |      |       | s         |

|---------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|-------|-------|----------|------|------|-------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5  | 20/4  | 19/3     | 18/2 | 17/1 | 16/0  | All Reset |

| 1200                      | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2S | SEL<3:0> |      |      |       | 0000      |

| A200                      | CTMUCUN                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM | <5:0> |          |      | IRNG | <1:0> | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6         | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|---------------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0                     | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |

| 51.24        | EDG1MOD           | IMOD EDG1POL EDG1SEL<3:0> |                   |                     |                   |                   | EDG2STAT               | EDG1STAT         |  |  |

| 23:16        | R/W-0             | R/W-0                     | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |  |  |

| 23.10        | EDG2MOD           | EDG2POL                   |                   | EDG2S               | EL<3:0>           |                   | _                      | —                |  |  |

| 15.0         | R/W-0             | U-0                       | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |

| 15:8         | ON                | —                         | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |  |  |

| 7:0          | R/W-0             | R/W-0                     | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |

| 7:0          | ITRIM<5:0>        |                           |                   |                     |                   |                   |                        | IRNG<1:0>        |  |  |

#### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

#### Legend:

| 8                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

#### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

# 0000 = Timer1 Event is selected

# bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Indicates the status of Edge 1 and can be written to control edge source                                                                                                                                                                                                                                         |

|           | 1 = Edge 1 has occurred                                                                                                                                                                                                                                                                                          |

|           | 0 = Edge 1 has not occurred                                                                                                                                                                                                                                                                                      |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                                                                                                                                                                                                                         |

|           | 1 = Input is edge-sensitive                                                                                                                                                                                                                                                                                      |

|           | 0 = Input is level-sensitive                                                                                                                                                                                                                                                                                     |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                                                                                                                                                                                                              |

|           | 1 = Edge 2 programmed for a positive edge response                                                                                                                                                                                                                                                               |

|           | 0 = Edge 2 programmed for a negative edge response                                                                                                                                                                                                                                                               |

| bit 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                                                                                                                                                                                                          |

|           | 1111 = IC4 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1110 = C2OUT pin is selected                                                                                                                                                                                                                                                                                     |

|           | 1101 = C1OUT pin is selected                                                                                                                                                                                                                                                                                     |

|           | 1100 = PBCLK clock is selected                                                                                                                                                                                                                                                                                   |

|           | 1011 = IC3 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1010 = IC2 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1001 = IC1 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1000 = CTED13 pin is selected<br>0111 = CTED12 pin is selected                                                                                                                                                                                                                                                   |

|           | 0110 = CTED12 pin is selected                                                                                                                                                                                                                                                                                    |

|           | 0101 = CTED10 pin is selected                                                                                                                                                                                                                                                                                    |

|           | 0100 = CTED9 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0011 = CTED1 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0010 = CTED2 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0001 = OC1 Compare Event is selected                                                                                                                                                                                                                                                                             |

|           | 0000 = Timer1 Event is selected                                                                                                                                                                                                                                                                                  |

| bit 17-16 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |

| bit 15    | ON: ON Enable bit                                                                                                                                                                                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                                                                                                                                            |

|           | 0 = Module is disabled                                                                                                                                                                                                                                                                                           |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                  |

|           | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                                                                                                                    |

|           | 0 = Continue module operation in Idle mode                                                                                                                                                                                                                                                                       |

| bit 12    | TGEN: Time Generation Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                  |

|           | 1 = Enables edge delay generation                                                                                                                                                                                                                                                                                |

|           | 0 = Disables edge delay generation                                                                                                                                                                                                                                                                               |

| bit 11    | EDGEN: Edge Enable bit                                                                                                                                                                                                                                                                                           |

|           | 1 = Edges are not blocked                                                                                                                                                                                                                                                                                        |

|           | 0 = Edges are blocked                                                                                                                                                                                                                                                                                            |

| Note 1:   | When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.                                                                                                                                                                                                    |

| 2:        | The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion                                                                                                                                                                                                               |

| -         | cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor |

|           | array.                                                                                                                                                                                                                                                                                                           |

| -         |                                                                                                                                                                                                                                                                                                                  |

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

|              | -                 |                   |                   |                   | -                 |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |  |

| 31:24        | —                 | —                 | —                 | -                 | —                 | _                 | FWDTWINSZ<1:0>   |                  |  |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | —                 |                   |                   | WDTPS<4:0>        |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM<1:0>        |                   | FPBDIV<1:0>       |                   | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO              | —                 | FSOSCEN           |                   |                   | FNOSC<2:0>        |                  |                  |  |

#### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | d bit P = Programmable bit         |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-26 Reserved: Write '1'

bit 25-24 **FWDTWINSZ:** Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

#### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

#### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

- bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| ~ |                                                              |

|---|--------------------------------------------------------------|

|   | 10100 <b>= 1:1048576</b>                                     |

|   | 10011 <b>= 1:524288</b>                                      |

|   | 10010 <b>= 1:262144</b>                                      |

|   | 10001 <b>= 1:131072</b>                                      |

|   | 10000 <b>= 1:65536</b>                                       |

|   | 01111 <b>= 1:32768</b>                                       |

|   | 01110 <b>= 1:16384</b>                                       |

|   | 01101 <b>= 1:8192</b>                                        |

|   | 01100 <b>= 1:4096</b>                                        |

|   | 01011 <b>= 1:2048</b>                                        |

|   | 01010 <b>= 1:1024</b>                                        |

|   | 01001 <b>= 1:512</b>                                         |

|   | 01000 <b>= 1:256</b>                                         |

|   | 00111 <b>= 1:128</b>                                         |

|   | 00110 <b>= 1:64</b>                                          |

|   | 00101 <b>= 1:32</b>                                          |

|   | 00100 = 1:16                                                 |

|   | 00011 <b>= 1</b> :8                                          |

|   | 00010 = 1:4                                                  |

|   | 00001 <b>= 1:2</b>                                           |

|   | 00000 = 1:1                                                  |

|   | All other combinations not shown result in operation = 10100 |

|   | · ·                                                          |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

# 30.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### 30.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 30.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 30.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 31.1 DC Characteristics

#### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                | Voo Bango                              | Temp. Range     | Max. Frequency                          |

|----------------|----------------------------------------|-----------------|-----------------------------------------|

| Characteristic | VDD Range<br>(in Volts) <sup>(1)</sup> | (in °C)         | PIC32MX1XX/2XX/5XX 64/100-pin<br>Family |

| DC5            | VBOR-3.6V                              | -40°C to +105°C | 40 MHz                                  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

#### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol | Min.          | Typical | Max. | Unit |

|--------------------------------------------------------------------------------------|--------|---------------|---------|------|------|

| Industrial Temperature Devices                                                       |        |               |         |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40           | —       | +125 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40           | —       | +85  | °C   |

| V-temp Temperature Devices                                                           |        |               |         |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40           | —       | +140 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40           | —       | +105 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD – S IOH) | PD     | PINT + PI/O   |         | W    |      |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOH} x IOH) + S (VOL x IOL))          |        |               |         |      |      |

| Maximum Allowed Power Dissipation                                                    | PDMAX  | (TJ — TA)/θJA |         |      | W    |

#### TABLE 31-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                                         | Symbol | Typical | Max. | Unit | Notes |

|---------------------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 64-pin QFN                  | θJA    | 28      | _    | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP, 10 mm x 10 mm  | θJA    | 55      | —    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP, 12 mm x 12 mm | θJA    | 52      | _    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP, 14 mm x 14 mm | θJA    | 50      | —    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHARACTERISTICS |         |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |   |                    |       |                                                                  |  |  |

|--------------------|---------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------|-------|------------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics                                              | Min. Typ. Ma                                                                                                                                                                                                                                                                          |   | Max.               | Units | Comments                                                         |  |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                                                     | _ | 10                 | μs    | See Note 1                                                       |  |  |

| D313               | DACREFH | CVREF Input Voltage                                          | AVss                                                                                                                                                                                                                                                                                  | _ | AVDD               | V     | CVRSRC with CVRSS = 0                                            |  |  |

|                    |         | Reference Range                                              | VREF-                                                                                                                                                                                                                                                                                 |   | VREF+              | V     | CVRSRC with CVRSS = 1                                            |  |  |

| D314               | DVREF   | CVREF Programmable<br>Output Range                           | 0                                                                                                                                                                                                                                                                                     | _ | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                  |  |  |

|                    |         |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                     | _ | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/<br>32 step size |  |  |

| D315               | DACRES  | Resolution                                                   | _                                                                                                                                                                                                                                                                                     | _ | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                         |  |  |

|                    |         |                                                              | _                                                                                                                                                                                                                                                                                     |   | DACREFH/32         |       | CVRCON <cvrr> = 0</cvrr>                                         |  |  |

| D316               | DACACC  | Absolute Accuracy <sup>(2)</sup>                             | —                                                                                                                                                                                                                                                                                     | _ | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                          |  |  |

|                    |         |                                                              | —                                                                                                                                                                                                                                                                                     | _ | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                          |  |  |

# TABLE 31-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

### TABLE 31-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                                            |

|--------------------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------------------------------------------------------------------------------------------------------|