Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

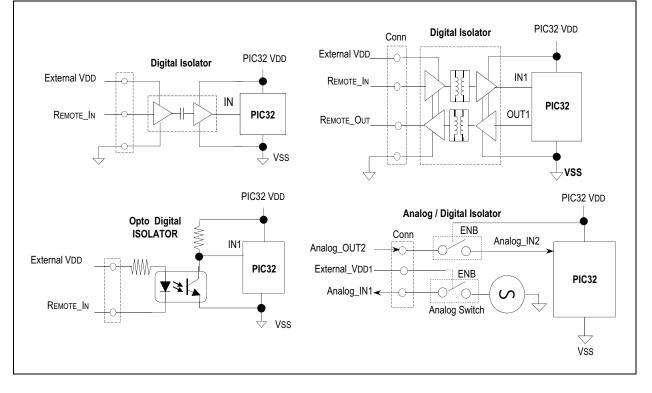

Without proper signal isolation, on non-5V tolerant pins, the remote signal can power the PIC32 device through the high side ESD protection diodes. Besides violating the absolute maximum rating specification when VDD of the PIC32 device is restored and ramping up or ramping down, it can also negatively affect the internal Power-on Reset (POR) and Brown-out Reset (BOR) circuits, which can lead to improper initialization of internal PIC32 logic circuits. In these cases, it is recommended to implement digital or analog signal isolation as depicted in Figure 2-6, as appropriate. This is indicative of all industry microcontrollers and not just Microchip products.

#### TABLE 2-1: EXAMPLES OF DIGITAL/ ANALOG ISOLATORS WITH OPTIONAL LEVEL TRANSLATION

| Example Digital/Analog<br>Signal Isolation Circuits |   | Capacitive Coupling | Opto Coupling | Analog/Digital Switch |

|-----------------------------------------------------|---|---------------------|---------------|-----------------------|

| ADuM7241 / 40 ARZ (1 Mbps)                          | Х |                     | _             |                       |

| ADuM7241 / 40 CRZ (25 Mbps)                         | Х |                     |               | _                     |

| IS0721                                              |   | Х                   |               | _                     |

| LTV-829S (2 Channel)                                | _ |                     | Х             | _                     |

| LTV-849S (4 Channel)                                | _ |                     | Х             | _                     |

| FSA266 / NC7WB66                                    | _ |                     |               | Х                     |

#### FIGURE 2-6: DIGITAL/ANALOG SIGNAL ISOLATION CIRCUITS

#### TABLE 4-1: SFR MEMORY MAP

| Devinheral             | Virtual | Address      |

|------------------------|---------|--------------|

| Peripheral             | Base    | Offset Start |

| Interrupt Controller   |         | 0x1000       |

| Bus Matrix             |         | 0x2000       |

| DMA                    | 0       | 0x3000       |

| USB                    | 0xBF88  | 0x5000       |

| PORTA-PORTG            |         | 0x6000       |

| CAN1                   |         | 0xB000       |

| Watchdog Timer         |         | 0x0000       |

| RTCC                   |         | 0x0200       |

| Timer1-Timer5          |         | 0x0600       |

| IC1-IC5                |         | 0x2000       |

| OC1-OC5                |         | 0x3000       |

| I2C1-I2C2              |         | 0x5000       |

| SPI1-SPI4              |         | 0x5800       |

| UART1-UART5            | 0xBF80  | 0x6000       |

| PMP                    | UXBF80  | 0x7000       |

| ADC1                   |         | 0x9000       |

| DAC                    |         | 0x9800       |

| Comparator 1, 2, 3     |         | 0xA000       |

| Oscillator             |         | 0xF000       |

| Device and Revision ID |         | 0xF200       |

| Flash Controller       |         | 0xF400       |

| PPS                    |         | 0xFA00       |

| Configuration          | 0xBFC0  | 0x0BF0       |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRIN            | √<8:1>            |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 |                   | —                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 |                  | —                |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

**Note:** While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | _                 | _                 | _                 | _                | _                |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### **REGISTER 9-9:** DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31-24<br>bit 23 | Unimplemented: Read as '0'<br>CHSDIE: Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                    |     |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| bit 22              | CHSHIE: Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                            |     |

| bit 21              | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                      |     |

| bit 20              | <b>CHDHIE:</b> Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                 |     |

| bit 19              | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                               |     |

| bit 18              | <b>CHCCIE:</b> Channel Cell Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                |     |

| bit 17              | CHTAIE: Channel Transfer Abort Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                               |     |

| bit 16              | CHERIE: Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                |     |

| bit 15-8            | Unimplemented: Read as '0'                                                                                                                                                 |     |

| bit 7               | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                                                             |     |

|                     | <ul><li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li><li>0 = No interrupt is pending</li></ul>                                               |     |

| bit 6               | <b>CHSHIF:</b> Channel Source Half Empty Interrupt Flag bit<br>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2<br>0 = No interrupt is pending | )   |

| bit 5               | <b>CHDDIF:</b> Channel Destination Done Interrupt Flag bit<br>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDS<br>0 = No interrupt is pending | IZ) |

| © 2014-201          | 6 Microchip Technology Inc. Preliminary                                                                                                                                    | DS  |

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected</li> <li>Either the source or the destination address is invalid.</li> </ul>                                                        |

0 = No interrupt is pending

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | -                 | _                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | _                 | _                 | -                 | _                 | -                 | -                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | CHSPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                   |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|-------------------|------------------|------------------------------------|--------------------|--|--|--|

|                                   | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | _                 | _                 | _                 | —                 |                   | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   | _                 | _                 | _                 | —                 |                   | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | CHDPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

#### 11.4 Control Registers

#### TABLE 11-3: PORTA REGISTER MAP 100-PIN DEVICES ONLY

| -                           |                                 |           |               |               |       |       | -     |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ress<br>)                   | <b>N</b> .                      | Ð         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                          | 31:16     | _             | _             | _     | _     | —     | —             | —            | _    | —            | —            | —            |              | —            |              | I            | —            | 0000          |

| 0000                        | ANGELA                          | 15:0      | _             | —             | _     | —     | —     | ANSELA10      | ANSELA9      | —    | —            | _            | _            |              | _            | _            |              | _            | 0060          |

| 6010                        | TRISA                           | 31:16     | _             | —             | _     | —     | —     | —             | —            | —    | —            | _            | _            |              | _            | _            |              | _            | 0000          |

| 0010                        | INISA                           | 15:0      | TRISA15       | TRISA14       | —     | —     | —     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | C6FF          |

| 6020                        | PORTA                           | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0020                        | FURIA                           | 15:0      | RA15          | RA14          | —     | —     | —     | RA10          | RA9          | —    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                            | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0030                        | LAIA                            | 15:0      | LATA15        | LATA14        | —     | —     | —     | LATA10        | LATA9        | —    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                            | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0040                        | ODCA                            | 15:0      | ODCA15        | ODCA14        | —     | —     | —     | ODCA10        | ODCA9        | —    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | 0000          |

| 6050                        | CNPUA                           | 31:16     | _             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | -            | —            | _            | _            | —            | 0000          |

| 0000                        |                                 | 15:0      | CNPUA15       | CNPUA14       | —     | —     | _     | CNPUA10       | CNPUA9       | —    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | 0000          |

| 6060                        | CNPDA                           | 31:16     | _             | —             | _     | _     | _     | _             | —            | _    | —            |              |              | _            |              | _            |              |              | 0000          |

| 0000                        |                                 | 15:0      | CNPDA15       | CNPDA14       | _     | _     | _     | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       | 0000          |

| 6070                        | CNCONA                          | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | _            | —            | 0000          |

| 0010                        |                                 | 15:0      | ON            | —             | SIDL  | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 6080                        | CNENA                           | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0000                        | ONEN                            | 15:0      | CNIEA15       | CNIEA14       | _     | _     | _     | CNIEA10       | CNIEA9       | _    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | 0000          |

|                             |                                 | 31:16     | _             | —             | _     | —     | —     | —             | —            | _    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 6090                        | CNSTATA                         | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | _     | _     | CN<br>STATA10 | CN<br>STATA9 | _    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### TABLE 11-6: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |         |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|---------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | —         | —         | _       | —     | -     |      |      | _    | —    | _    |      | —       |         | —       | —    | 0000          |

| 0200 / 110220               | /                               | 15:0      | —         | —         | —         | —       | —     | —     | —    | _    | —    | _    | —    | _    | ANSELC3 | ANSELC2 | ANSELC1 | —    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | —         | —         | —       | _     | _     | _    |      | _    |      | —    | _    | _       | _       | —       | _    | 0000          |

| 02.0                        |                                 | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12 | —     | —     | —    | _    | —    | _    | —    | _    | —       | —       | —       | —    | F000          |

| 6220                        | PORTC                           | 31:16     | —         | —         | —         | —       | —     | _     | _    | _    | —    | _    | —    | _    | —       | _       | —       |      | 0000          |

| 0220                        | 1 on to                         | 15:0      | RC15      | RC14      | RC13      | RC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | xxxx          |

| 6230 LATO                   | LATC                            | 31:16     |           | —         | —         | —       | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 0200                        | EAIO                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12  | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | xxxx          |

| 6240                        | ODCC                            | 31:16     |           | —         | —         | —       | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 02.10                       | 0200                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12  | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 6250                        | CNPUC                           | 31:16     |           | —         | —         | —       | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 0200                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12 | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 6260                        | CNPDC                           | 31:16     |           | —         | —         | —       | —     | _     | _    | _    | —    | —    | —    |      | —       | _       | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12 | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 6270                        | CNCONC                          | 31:16     |           |           |           | _       |       |       | _    |      | —    | _    | —    | _    | —       |         | —       |      | 0000          |

| 0270                        | oncono                          | 15:0      | ON        |           | SIDL      |         |       |       | _    |      | —    | _    | —    | _    | —       |         | —       |      | 0000          |

| 6280                        | CNENC                           | 31:16     |           | —         |           |         |       |       | _    |      | —    | _    | —    | _    | —       |         | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12 | —     | _     | _    |      | —    |      | —    | _    | —       |         | —       | _    | 0000          |

| 6200                        | CNSTATC                         | 31:16     | _         | —         | —         | _       | _     |       |      |      | -    | —    | -    |      | —       |         | —       | —    | 0000          |

| 6290 CNSTATC                | 15:0                            | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _       |       |       |      | -    | _    |      |      | _    |         | —       | _       | 0000 |               |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### TABLE 11-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| ss                          |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |        |                   |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|--------|-------------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1              | 16/0 | All Resets |

|                             |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | —    | _    | _    | —      | _                 | _    | 000        |

| FA5C                        | U2CTSR           | 15:0      | _     | —     | l —   | —     | —     | —     | _    | _    |      | _    | —    | —    |      | U2CTS  | R<3:0>            |      | 000        |

| <b>FA00</b>                 |                  | 31:16     | —     | —     | —     | —     | _     | —     | _    | _    | _    |      | —    | —    | —    | —      | —                 | —    | 000        |

| FA60                        | U3RXR            | 15:0      | —     | —     | —     | —     |       | —     |      |      |      |      |      | —    |      | U3RX   | R<3:0>            | •    | 000        |

| 5404                        | U3CTSR           | 31:16     | —     | —     | —     | —     | —     | —     | _    |      |      | _    | _    | —    | —    | —      | —                 | —    | 000        |

| FA64                        | U3CISR           | 15:0      | —     | —     | —     | —     |       | —     |      |      |      |      |      | —    |      | U3CTS  | SR<3:0>           | •    | 000        |

|                             | U4RXR            | 31:16     | —     | —     | —     | —     |       | —     |      |      |      |      |      | —    | —    | —      | —                 | —    | 000        |

| FA68                        | U4RXR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | U4RX   | R<3:0>            |      | 000        |

| FA00                        |                  | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —      | —                 | —    | 000        |

| FA6C                        | U4CTSR           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | U4CTS  | SR<3:0>           |      | 000        |

| EA 70                       |                  | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —      | —                 | —    | 000        |

| FA70                        | U5RXR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | U5RX   | R<3:0>            |      | 000        |

|                             | USOTOD           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —      | —                 | —    | 000        |

| FA74                        | U5CTSR           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | U5CTS  | SR<3:0>           |      | 000        |

| FA84                        | SDI1R            | 31:16     | _     | —     | —     | —     | _     | —     | _    | _    | _    | _    | _    | —    | _    | —      | —                 | —    | 000        |

| FA04                        | SDIIK            | 15:0      | _     | —     | —     | —     | _     | —     | _    | _    | _    | _    | _    | —    |      | SDI1F  | R<3:0>            |      | 000        |

| FA88                        | 0010             | 31:16     | _     | —     | —     | —     | _     | —     | _    | -    |      | _    | —    | —    | _    | —      | —                 | —    | 000        |

| FA00                        | SS1R             | 15:0      | —     | —     | —     | —     | —     | —     | —    |      |      | —    | —    | —    |      | SS1F   | R<3:0>            |      | 000        |

| FA90                        | SDI2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    |      |      | —    | —    | —    | —    | —      | —                 | —    | 000        |

| FA90                        | SDIZK            | 15:0      | —     | —     | —     | —     | —     | —     | —    |      |      | —    | —    | —    |      | SDI2F  | R<3:0>            |      | 000        |

| EA04                        | SS2R             | 31:16     | —     | —     | —     | —     | —     | —     | _    |      |      | —    | _    | —    | —    | —      | —                 | —    | 000        |

| FA94                        | 332R             | 15:0      | —     | —     | —     | —     | —     | —     | _    |      |      | —    | _    | —    |      | SS2F   | R<3:0>            |      | 000        |

| FA9C                        | SDI3R            | 31:16     | —     | —     | —     | —     | —     | —     | _    | -    | -    | —    | _    | —    | —    | —      | —                 | —    | 000        |

| TASC                        | SDISK            | 15:0      | —     | —     | —     | —     | —     | —     | _    | -    | -    | —    | _    | —    |      | SD13F  | R<3:0>            |      | 000        |

| FAA0                        | SS3R             | 31:16     | —     | —     | —     | —     | —     | —     | _    |      |      | —    | _    | —    | —    | —      | —                 | —    | 000        |

| FAAU                        | 333K             | 15:0      | —     | —     | —     | —     | —     | —     | _    | -    | -    | —    | _    | —    |      | SS3F   | R<3:0>            |      | 000        |

| FAA8                        | SDI4R            | 31:16     | —     | —     | —     | —     | —     | —     | _    | -    | -    | —    | _    | —    | —    | —      | —                 | —    | 000        |

| FAAo                        | 3DI4K            | 15:0      | —     | —     | —     | —     | —     | —     | _    | -    | -    | —    | _    | —    |      | SDI4F  | R<3:0>            |      | 000        |

| FAAC                        | SS4R             | 31:16     | —     | —     | —     | —     | —     | —     | _    | -    | -    | —    | _    | —    | —    | —      | —                 | —    | 000        |

| IAAU                        | 334K             | 15:0      | _     | —     | —     | —     | —     | —     | _    | -    | -    | _    | —    | —    |      | SS4F   | R<3:0>            |      | 000        |

| FAC8                        | C1RXR            | 31:16     | _     | —     | —     | —     | —     | —     | _    | -    | -    | _    | —    | —    | —    | -      | —                 | —    | 000        |

|                             | UIKAR            | 15:0      | _     | —     | —     | —     | —     | —     | _    | _    | —    | _    | —    | —    |      | C1RX   | R<3:0>            |      | 000        |

| FAD0                        | REFCLKIR         | 31:16     |       | —     | —     | _     | —     | —     | _    | _    | -    | —    |      | _    | —    | -      | —                 | _    | 000        |

| FAD0                        | NEFULNIK         | 15:0      | —     | -     | —     | -     | —     | -     | —    | —    | -    | —    | —    | -    |      | REFCLI | <ir<3:0></ir<3:0> |      | 0000       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 |                   | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   |                   | _                 | _                 | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | —                 | _                | _                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

| 011 31-10 | Unimplemented: Read as 0                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

|           | 1 = Timer is enabled                                                                                                                                                           |

|           | 0 = Timer is disabled                                                                                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                    |

|           | 1 = Discontinue operation when device enters Idle mode                                                                                                                         |

|           | 0 = Continue operation even in Idle mode                                                                                                                                       |

| bit 12    | TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

|           | <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| bit 11    | TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

|           | In Asynchronous Timer mode:                                                                                                                                                    |

|           | 1 = Asynchronous write to TMR1 register in progress                                                                                                                            |

|           | 0 = Asynchronous write to TMR1 register complete                                                                                                                               |

|           | In Synchronous Timer mode:<br>This bit is read as '0'.                                                                                                                         |

| bit 10-8  | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 7     | TGATE: Timer Gated Time Accumulation Enable bit                                                                                                                                |

|           | When TCS = 1:                                                                                                                                                                  |

|           | This bit is ignored.                                                                                                                                                           |

|           | When TCS = 0:<br>1 = Gated time accumulation is enabled                                                                                                                        |

|           | 0 = Gated time accumulation is enabled                                                                                                                                         |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 5-4   | TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

|           | 11 = 1:256 prescale value                                                                                                                                                      |

|           | 10 = 1:64 prescale value                                                                                                                                                       |

|           | 01 = 1:8 prescale value<br>00 = 1:1 prescale value                                                                                                                             |

| bit 3     | Unimplemented: Read as '0'                                                                                                                                                     |

| DIL J     | ommplemented. Read as 0                                                                                                                                                        |

|           |                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |  |

#### REGISTER 19-1: UxMODE: UARTx MODE REGISTER

#### Legend:

| Legend.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |  |  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--|--|

| 21.24        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                      |  |  |

| 31:24        | _                 | _                    |                   | _                 | _                 |                   | —                | —                        |  |  |

| 22:16        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                      |  |  |

| 23:16        | _                 | _                    | _                 | _                 | _                 | -                 | _                | —                        |  |  |

| 45.0         | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                    |  |  |

| 15:8         | PTEN<1            | 5:14> <sup>(1)</sup> | PTEN<13:8>        |                   |                   |                   |                  |                          |  |  |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                    |  |  |

| 7:0          | PTEN<7:2>         |                      |                   |                   |                   |                   |                  | PTEN<1:0> <sup>(2)</sup> |  |  |

#### REGISTER 20-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

### Legend:

| Legend.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-14 **PTEN<15:14>:** PMCSx Address Port Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

#### 23.1 **Control Registers**

#### TABLE 23-1: CAN1 REGISTER SUMMARY

| ess                         |                                 |               |              |                                |              |                                                                 |              |              |             | Bit         | 5       |             |             |              |             |           |           |         |            |

|-----------------------------|---------------------------------|---------------|--------------|--------------------------------|--------------|-----------------------------------------------------------------|--------------|--------------|-------------|-------------|---------|-------------|-------------|--------------|-------------|-----------|-----------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14                          | 29/13        | 28/12                                                           | 27/11        | 26/10        | 25/9        | 24/8        | 23/7    | 22/6        | 21/5        | 20/4         | 19/3        | 18/2      | 17/1      | 16/0    | All Resets |

|                             | 01001                           | 31:16         |              | _                              | _            | _                                                               | ABAT         | F            | REQOP<2:0   | >           | C       | OPMOD<2:0   | >           | CANCAP       | _           | _         | _         | _       | 0480       |

| B000                        | C1CON                           | 15:0          | ON           | -                              | SIDLE        |                                                                 | CANBUSY      | —            | _           | _           |         | _           | _           |              | D           | NCNT<4:0> | •         |         | 0000       |

| B010                        | C1CFG                           | 31:16         | _            |                                | _            |                                                                 | _            | _            | -           |             | -       | WAKFIL      | _           | _            | -           | S         | EG2PH<2:0 | >       | 0000       |

| вото                        | CICFG                           | 15:0          | SEG2PHTS     | SAM                            | S            | EG1PH<2:0                                                       | )>           | ŀ            | PRSEG<2:0   | >           | SJW     | <1:0>       |             |              | BRP<        | :5:0>     |           |         | 0000       |

| B020                        | C1INT                           | 31:16         | IVRIE        | WAKIE                          | CERRIE       | SERRIE                                                          | RBOVIE       |              | _           |             | _       | _           | _           | _            | MODIE       | CTMRIE    | RBIE      | TBIE    | 0000       |

| 0020                        | 01111                           | 15:0          | IVRIF        | WAKIF                          | CERRIF       | SERRIF                                                          | RBOVIF       | —            | —           | —           | —       | —           | —           | —            | MODIF       | CTMRIF    | RBIF      | TBIF    | 0000       |

| B030                        | C1VEC                           | 31:16         | —            | _                              | —            | —                                                               | —            | _            | —           | —           | _       | —           | —           | —            | —           | —         | —         | —       | 0000       |

| 2000                        |                                 | 15:0          | —            |                                | _            |                                                                 |              | FILHIT<4:0>  | >           |             |         |             |             | r            | CODE<6:0>   |           |           |         | 0040       |

| B040                        | C1TREC                          | 31:16         | _            | —                              | _            | —                                                               | _            | _            | —           | —           | _       | _           | TXBO        | TXBP         | RXBP        | TXWARN    | RXWARN    | EWARN   | 0000       |

|                             |                                 | 15:0          |              |                                |              | TERRC                                                           | NT<7:0>      |              |             |             |         |             |             | RERRCNT<7:0> |             |           |           |         | 0000       |

| B050                        | C1FSTAT                         | 31:16         | -            | -                              | -            | -                                                               | -            | -            | -           | -           | -       | -           | -           | -            | -           | -         | -         | -       | 0000       |

|                             |                                 | 15:0          | FIFOIP15     | FIFOIP14                       | FIFOIP13     | FIFOIP12                                                        | FIFOIP11     | FIFOIP10     | FIFOIP9     | FIFOIP8     | FIFOIP7 | FIFOIP6     | FIFOIP5     | FIFOIP4      | FIFOIP3     | FIFOIP2   | FIFOIP1   | FIFOIP0 | 0000       |

| B060                        | C1RXOVF                         | 31:16<br>15:0 | —<br>RXOVF15 | —<br>RXOVF14                   | –<br>RXOVF13 |                                                                 | –<br>RXOVF11 | –<br>RXOVF10 | –<br>RXOVF9 | –<br>RXOVF8 | RXOVF7  | –<br>RXOVF6 | –<br>RXOVF5 | —<br>RXOVF4  | –<br>RXOVF3 | RXOVF2    | RXOVF1    | RXOVF0  | 0000       |

|                             |                                 | 31:16         | RAUVE 15     | KAUVF14                        | RAUVEIS      | RAUVE 12                                                        | RAUVEII      | RAUVEIU      | KAUVF9      | CANTS<      |         | RAUVEO      | RAUVFS      | KAUVF4       | RAUVES      | RAUVF2    | RAUVEI    | RAUVFU  | 0000       |

| B070                        | C1TMR                           | 15:0          |              |                                |              |                                                                 |              |              | CA          | NTSPRE<15   |         |             |             |              |             |           |           |         | 0000       |

|                             |                                 | 31:16         |              |                                |              |                                                                 |              | SID<10:0>    | 0A          |             | 05      |             |             |              | MIDE        | _         | EID<1     | 7.16>   | xxxx       |

| B080                        | C1RXM0                          | 15:0          |              |                                |              |                                                                 |              | 0.0 10.0     |             | EID<1       | 5.0>    |             |             |              |             |           | 2.0       |         | XXXX       |

|                             |                                 | 31:16         |              |                                |              |                                                                 |              | SID<10:0>    |             |             |         |             |             |              | MIDE        |           | EID<1     | 7.16>   | xxxx       |

| B090                        | C1RXM1                          | 15:0          |              |                                |              |                                                                 |              | 0.0 10.0     |             | EID<1       | 5.0>    |             |             |              |             |           | 2.0       |         | XXXX       |

|                             |                                 | 31:16         |              |                                |              |                                                                 |              | SID<10:0>    |             | 210 11      |         |             |             |              | MIDE        | _         | EID<1     | 7.16>   | xxxx       |

| B0A0                        | C1RXM2                          | 15:0          |              |                                |              |                                                                 |              | 0.0 10.0     |             | EID<1       | 5:0>    |             |             |              |             |           | 2.0       |         | XXXX       |

|                             |                                 | 31:16         |              |                                |              |                                                                 |              |              |             | xxxx        |         |             |             |              |             |           |           |         |            |

| B0B0                        | C1RXM3                          | 15:0          |              |                                |              |                                                                 |              |              |             | EID<1       | 5:0>    |             |             |              |             |           | ļ         |         | xxxx       |

|                             |                                 | 31:16         | FLTEN3       |                                |              |                                                                 |              | 0000         |             |             |         |             |             |              |             |           |           |         |            |

| B0C0                        | C1FLTCON0                       | 15:0          | FLTEN1       | MSEL                           | 1<1:0>       |                                                                 |              | FSEL1<4:0>   | >           |             | FLTEN0  | MSEL        | MSEL0<1:0>  |              | FSEL0<4:0>  |           |           |         | 0000       |

|                             | 0.151 700114                    | 31:16         | FLTEN7       | MSEL                           | 7<1:0>       |                                                                 |              |              |             |             |         | 0000        |             |              |             |           |           |         |            |

| B0D0                        | C1FLTCON1                       | 15:0          | FLTEN5       | MSEL                           | 5<1:0>       | FSEL5<4:0>         FLTEN4         MSEL4<1:0>         FSEL4<4:0> |              |              |             |             | 0000    |             |             |              |             |           |           |         |            |

|                             |                                 | 31:16         | FLTEN11      | MSEL'                          | 11<1:0>      |                                                                 |              |              |             |             | 0000    |             |             |              |             |           |           |         |            |

| B0E0                        | C1FLTCON2                       | 15:0          | FLTEN9       | MSEL                           | 9<1:0>       |                                                                 |              |              |             | 0000        |         |             |             |              |             |           |           |         |            |

| B0F0                        | C1FLTCON3                       | 31:16         | FLTEN15      |                                |              |                                                                 |              |              | 0000        |             |         |             |             |              |             |           |           |         |            |

| BUFU                        | GIFLI CONS                      | 15:0          | FLTEN13      |                                |              |                                                                 |              |              | 0000        |             |         |             |             |              |             |           |           |         |            |

| B140                        | Onoan                           | 31:16         |              | SID<10:0> EXID EID<17:16> xxxx |              |                                                                 |              |              | xxxx        |             |         |             |             |              |             |           |           |         |            |

| 0+10                        | (n = 0-15)                      | 15:0          |              | EID<15:0> xxxx                 |              |                                                                 |              |              |             |             |         |             |             |              |             |           |           |         |            |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | FLTEN11 MSEL11<1:0> |                   |                   | FSEL11<4:0>       |                   |                   |                  |                  |  |

| 22:16        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN10 MSEL10<     |                   | 0<1:0>            | FSEL10<4:0>       |                   |                   |                  |                  |  |

| 15.0         | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN9              | MSEL              | 9<1:0>            |                   | F                 | SEL9<4:0>         |                  |                  |  |

| 7:0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN8 MSEL8<1:0>   |                   | FSEL8<4:0>        |                   |                   |                   |                  |                  |  |

#### REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN11: Filter 11 Enable bit                                      |

|-----------|--------------------------------------------------------------------|

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                            |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| h:+ 00 04 |                                                                    |

| bit 28-24 |                                                                    |

|           | 11111 = Reserved                                                   |

|           | •                                                                  |

|           | •                                                                  |

|           | 10000 = Reserved                                                   |

|           | 01111 = Message matching filter is stored in FIFO buffer 15        |

|           | •                                                                  |

|           |                                                                    |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 23    | FLTEN10: Filter 10 Enable bit                                      |

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                            |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected                                    |

|           | 00 = Acceptance Mask 0 selected                                    |

|           |                                                                    |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### 27.4 Peripheral Module Disable