Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f128lt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

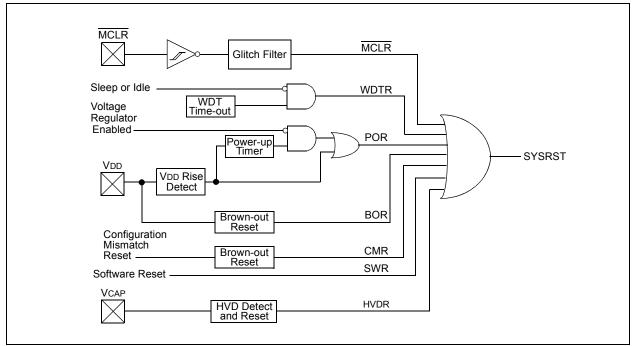

## 7.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 7-1.

#### FIGURE 7-1: SYSTEM RESET BLOCK DIAGRAM

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The PIC32MX1XX/2XX/5XX 64/100-pin oscillator system has the following modules and features:

- A Total of four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

|              |                   |                   | -                 | -                 |                   |                   |                       |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

| 24.24        | U-0                   | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | -                 | —                     | —                |

| 23:16        | U-0                   | U-0              |

| 23.10        | —                 | _                 | —                 | —                 |                   |                   |                       | —                |

| 15:8         | U-0                   | U-0              |

| 10.0         | _                 | _                 | _                 | _                 | _                 | _                 | _                     | —                |

|              | R/W-0                 | R/W-0            |

| 7:0          | DTOFF             |                   |                   | DTOFE             | DENIGEE           | 0001055           | CRC5EE <sup>(1)</sup> | DIDEE            |

|              | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |

|              |                   |                   |                   |                   |                   |                   |                       |                  |

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

- 1 = BTSEF interrupt enabled

- 0 = BTSEF interrupt disabled

- bit 6 **BMXEE:** Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt enabled

- 0 = BMXEF interrupt disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt enabled

- 0 = DMAEF interrupt disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt enabled

- 0 = BTOEF interrupt disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt enabled

- 0 = DFN8EF interrupt disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt enabled

- 0 = CRC16EF interrupt disabled

- bit 1 **CRC5EE:** CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt enabled

- 0 = CRC5EF interrupt disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt enabled

- 0 = EOF interrupt disabled

- bit 0 **PIDEE:** PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt enabled

- 0 = PIDEF interrupt disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   |                   | —                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   | —                 |                   |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | _                 |                   |                   | —                 |                   | _                | —                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  | —                |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last BD Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 PPBI: Ping-Pong BD Pointer Indicator bit

- 1 = The last transaction was to the ODD BD bank

- 0 = The last transaction was to the EVEN BD bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 7:0          | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | _                 | _                 | USBSIDL           | USBSIDL           |                   | _                | UASUSPND         |

#### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test enabled

- 0 = Eve-Pattern Test disabled

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3 LSDEV: Low-Speed Device Enable bit

- 1 = USB module operates in Low-Speed Device mode only

- 0 = USB module operates in OTG, Host, or Full-Speed Device mode

- bit 2-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock

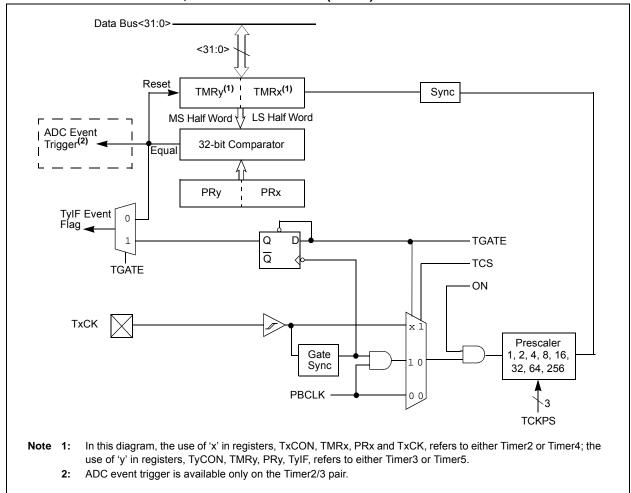

#### FIGURE 13-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

## TABLE 14-1: WATCHDOG TIMER REGISTER MAP

| ess                        |                                 | e         |       | Bits  |       |       |       |       |      |      |      | s    |      |           |      |      |          |        |           |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|----------|--------|-----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1     | 16/0   | All Reset |

| 0000                       | WDTCON                          | 31:16     | —     | —     | —     | —     |       | —     | —    | —    | —    | —    | —    | —         | —    | —    | -        | —      | 0000      |

| 0000                       | WDICON                          | 15:0      | ON    | —     | —     | —     | —     | —     | _    | —    | _    |      | SV   | VDTPS<4:0 | )>   |      | WDTWINEN | WDTCLR | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

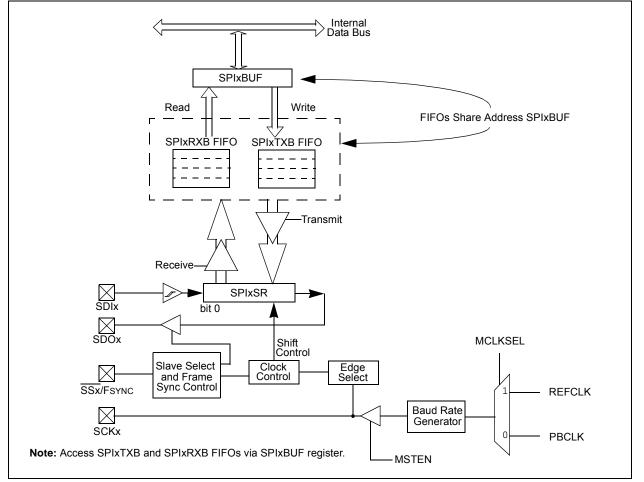

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- Master and Slave modes support

- Four different clock formats

- · Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

SUFO buffers act as 4/8/10 local data FIFO

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

#### FIGURE 17-1: SPI MODULE BLOCK DIAGRAM

| REGIST  | ER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                                  |

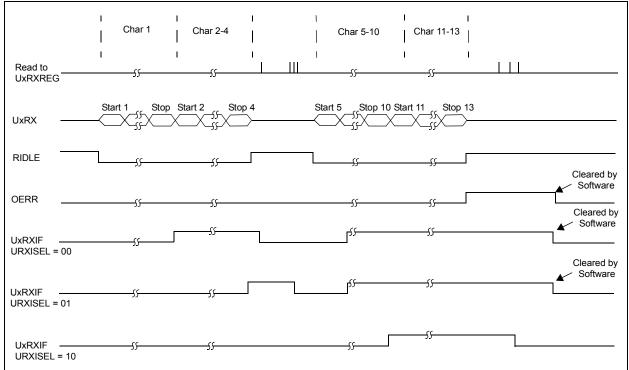

| bit 7-6 | <pre>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 =Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</pre> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                   |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                     |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                            |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                         |

| bit 1   | <b>OERR:</b> Receive Buffer Overrun Error Status bit.<br>This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.<br>1 = Receive buffer has overflowed                                                                                                                                                                                     |

|         | 0 = Receive buffer has not overflowed                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                    |

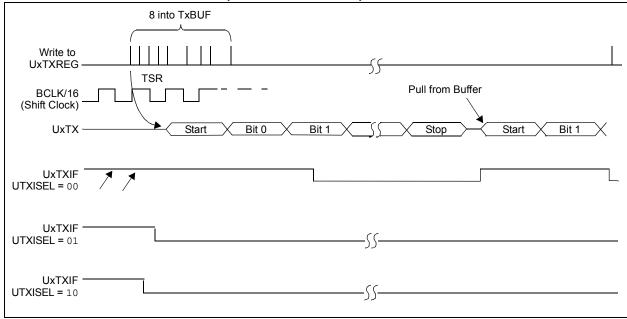

#### 19.2 Timing Diagrams

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

#### FIGURE 19-2: UART RECEPTION

#### FIGURE 19-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

U-0

U-0

\_\_\_\_

R/W-0

SMPI<3:0>

U-0

R/W-0

CSCNA

R/W-0

Bit

25/17/9/1

U-0

U-0

U-0

\_\_\_\_

R/W-0

BUFM

Bit

24/16/8/0

U-0

U-0

U-0

R/W-0

ALTS

| REGISTE      | GISTER 22-2. ADTCONZ. ADC CONTROL REGISTER Z |                   |                   |                   |                   |                   |  |  |  |

|--------------|----------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 |  |  |  |

| 31:24        | U-0                                          | U-0               | U-0               | U-0               | U-0               | U-0               |  |  |  |

| 31.24        |                                              |                   |                   |                   |                   |                   |  |  |  |

U-0

R/W-0

R/W-0

#### DECISTED 22 2. AD1CON2: ADC CONTROL REGISTER 2

U-0

R/W-0

U-0

\_

VCFG<2:0>

## Legend:

23:16

15:8

7:0

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

U-0

R/W-0

OFFCAL

R/W-0

#### bit 31-16 Unimplemented: Read as '0'

U-0

R/W-0

R-0

BUFS

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 OFFCAL: Input Offset Calibration Mode Select bit

- 1 = Enable Offset Calibration mode

- Positive and negative inputs of the sample and hold amplifier are connected to VREFL

- 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

#### bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each  $16^{th}$  sample/convert sequence 1110 = Interrupts at the completion of conversion for each  $15^{th}$  sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

#### TABLE 23-1: CAN1 REGISTER SUMMARY (CONTINUED)

| ess                         |            |               |       |        |       |       |       |           |          | Bits      | ;      |        |        |       |          |           |          |                |            |

|-----------------------------|------------|---------------|-------|--------|-------|-------|-------|-----------|----------|-----------|--------|--------|--------|-------|----------|-----------|----------|----------------|------------|

| Virtual Address<br>(BF88_#) |            |               | 31/15 | 30/14  | 29/13 | 28/12 | 27/11 | 26/10     | 25/9     | 24/8      | 23/7   | 22/6   | 21/5   | 20/4  | 19/3     | 18/2      | 17/1     | 16/0           | All Resets |

| B340                        | C1FIFOBA   | 31:16<br>15:0 |       |        |       |       |       |           |          | C1FIFOBA  | <31:0> |        |        |       |          |           |          |                | 0000       |

| B350                        | C1FIFOCONn | 31:16         |       | _      |       | _     | _     | _         | _        | _         | —      | _      | _      |       | ŀ        | SIZE<4:0> |          |                | 0000       |

| D330                        | (n = 0-15) | 15:0          | _     | FRESET | UINC  | DONLY | _     | —         | —        | —         | TXEN   | TXABAT | TXLARB | TXERR | TXREQ    | RTREN     | TXPRI    | <1:0>          | 0000       |

| B360                        | C1FIFOINTn | 31:16         | _     | -      | -     | —     | —     | TXNFULLIE | TXHALFIE | TXEMPTYIE | —      | —      | —      | —     | RXOVFLIE | RXFULLIE  | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| B300                        | (n = 0-15) | 15:0          | _     | -      | Ι     | -     | _     | TXNFULLIF | TXHALFIF | TXEMPTYIF | _      | —      | _      | —     | RXOVFLIF | RXFULLIF  | RXHALFIF | RXN<br>EMPTYIF | 0000       |

| B370                        | C1FIFOUAn  | 31:16         |       |        |       |       |       |           |          | C1FIFOUA  | <21.0> |        |        |       |          |           |          |                | 0000       |

| 6370                        | (n = 0-15) | 15:0          |       |        |       |       |       |           |          | CIFIFUUA  | ×31.0> |        |        |       |          |           |          |                | 0000       |

| B380                        | C1FIFOCIn  | 31:16         |       | _      | _     | _     |       | —         |          | _         | —      | —      | -      |       | _        | _         | _        |                | 0000       |

| 5300                        | (n = 0-15) | 15:0          | -     |        |       |       |       |           |          |           |        |        |        |       |          |           |          |                |            |

Legend: Note 1 x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 51.24        |                   | —                 | _                 | _                 | _                 |                   | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | —                 | —                 | TXBO              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | TERRCNT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | RERRCNT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 23-5: C1TREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT ≥ 128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

bit 17 **RXWARN:** Receiver in Error State Warning (128 > RERRCNT  $\ge$  96)

bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

#### REGISTER 23-6: C1FSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 |                   | _                 | _                 | _                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | —                 | —                 | _                 | _                | _                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | FIFOIP15          | FIFOIP14          | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | FIFOIP7           | FIFOIP6           | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 FIFOIP<15:0>: FIFOx Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

#### 24.1 Control Registers

## TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         |                                 |           |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON                          | 31:16     | _     | _     | —     | —     | —     | _     | —    | —    | -    | —      | —    | —    | _    | —     | —     | _     | 0000       |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4010                        | CM2CON                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4020                        | CM3CON                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A000                        | CIVISTAT                        | 15:0      | —     | _     | SIDL  | _     | _     |       |      | _    | —    |        | —    | —    | —    | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### TABLE 31-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CH4        | ARACTERIS | TICS                                                      |                        | (unless                | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |   |       |                                     |                       |  |  |

|---------------|-----------|-----------------------------------------------------------|------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-------------------------------------|-----------------------|--|--|

| Param.<br>No. | Symbol    | Cha                                                       | racteristic            | cs <sup>(1)</sup> Min. |                                                                                                                                                                                                                                                                                        |   | Units | Conditions                          |                       |  |  |

| TB10          | ТтхН      | TxCK<br>High Time                                         | Synchron<br>prescaler  | ous, with              | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns                                                                                                                                                                                                                                                      | — | ns    | Must also meet<br>parameter<br>TB15 | value<br>(1, 2, 4, 8, |  |  |

| TB11          | ΤτχL      | TxCK<br>Low Time                                          | Synchron<br>prescaler  | ous, with              | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns                                                                                                                                                                                                                                                      | _ | ns    | Must also meet<br>parameter<br>TB15 | 16, 32, 64,<br>256)   |  |  |

| TB15          | ΤτχΡ      | TxCK<br>Input                                             | Synchrono<br>prescaler | ous, with              | [(Greater of [(25 ns or<br>2 Трв)/N] + 30 ns                                                                                                                                                                                                                                           | _ | ns    | VDD > 2.7V                          |                       |  |  |

|               |           | Period                                                    |                        |                        | [(Greater of [(25 ns or<br>2 Трв)/N] + 50 ns                                                                                                                                                                                                                                           |   | ns    | VDD < 2.7V                          |                       |  |  |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                        |                        | —                                                                                                                                                                                                                                                                                      | 1 | Трв   |                                     |                       |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

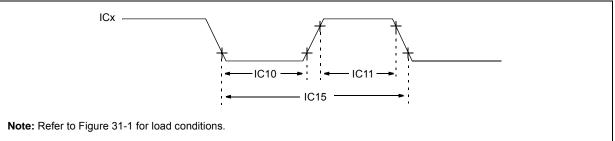

#### FIGURE 31-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 31-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHA                     | RACTERI | STICS     | (unless oth              | perating Conditions: 2.3V<br>erwise stated)<br>emperature $-40^{\circ}C \le TA \le +$<br>$-40^{\circ}C \le TA \le +$ | ·85°C foi |       |                                         |                                  |  |

|----------------------------|---------|-----------|--------------------------|----------------------------------------------------------------------------------------------------------------------|-----------|-------|-----------------------------------------|----------------------------------|--|

| Param.<br>No. Symbol Chara |         |           | teristics <sup>(1)</sup> | Min.                                                                                                                 | Max.      | Units | Conditions                              |                                  |  |

| IC10                       | TccL    | ICx Input | Low Time                 | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                    | _         | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |  |

| IC11                       | ТссН    | ICx Input | t High Time              | Гіте [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                               |           | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |  |

| IC15                       | TCCP    | ICx Input | Period                   | [(25 ns or 2 Трв)/N]<br>+ 50 ns                                                                                      | —         | ns    | —                                       |                                  |  |

| Note 1: | These parameters are | characterized, but not | t tested in manufacturing. |

|---------|----------------------|------------------------|----------------------------|

|         |                      |                        |                            |

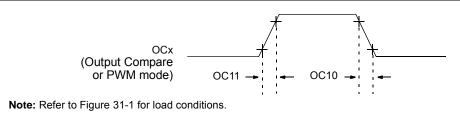

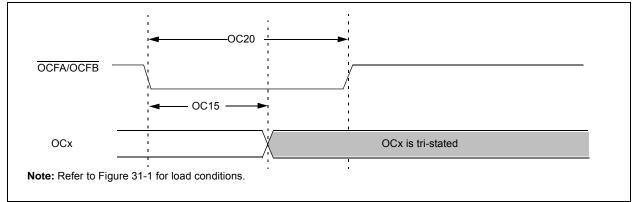

#### FIGURE 31-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 31-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| АС СНА        | AC CHARACTERISTICS |                                |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                    |  |  |  |

|---------------|--------------------|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol             | Characteristics <sup>(1)</sup> | Min. | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                              | Max. | Units | Conditions         |  |  |  |

| OC10          | TccF               | OCx Output Fall Time           | —    | —                                                                                                                                                                                                                                                                                   | _    | ns    | See parameter DO32 |  |  |  |

| OC11          | TccR               | OCx Output Rise Time           | —    | —                                                                                                                                                                                                                                                                                   | —    | ns    | See parameter DO31 |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### FIGURE 31-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 31-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHAF      | RACTERIST | rics                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                        |     |       |            |  |  |  |

|--------------|-----------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|--|--|

| Param<br>No. | Symbol    | bol Characteristics <sup>(1)</sup> |                                                                                                                                                                                                                                                                                   | Typical <sup>(2)</sup> | Max | Units | Conditions |  |  |  |

| OC15         | Tfd       | Fault Input to PWM I/O Change      | —                                                                                                                                                                                                                                                                                 | —                      | 50  | ns    | _          |  |  |  |

| OC20         | TFLT      | Fault Input Pulse Width            | 50                                                                                                                                                                                                                                                                                | —                      |     | ns    | —          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

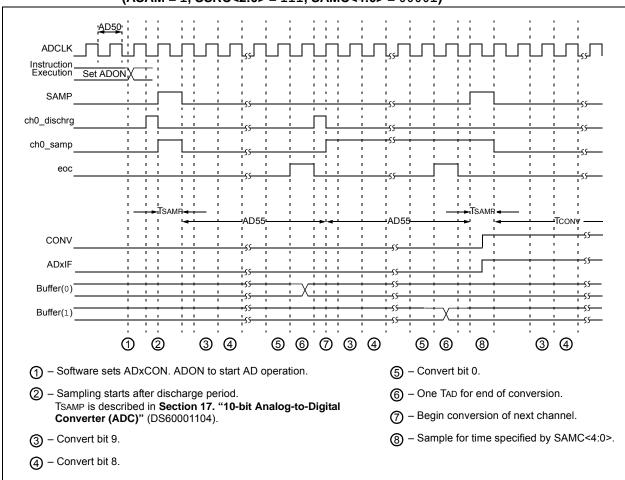

| AC CHA        | ARACTER   | ISTICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 4): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |         |       |                                                           |  |  |  |

|---------------|-----------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|-------|-----------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol    | Characteristics                                                      | Min.                                                                                                                                                                                                                                                                                               | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                |  |  |  |

| Clock P       | arameter  | S                                                                    | •                                                                                                                                                                                                                                                                                                  | •                      |         |       | ·                                                         |  |  |  |

| AD50          | Tad       | ADC Clock Period <sup>(2)</sup>                                      | 65                                                                                                                                                                                                                                                                                                 | —                      | —       | ns    | See Table 31-35                                           |  |  |  |

| Convers       | sion Rate | •                                                                    | •                                                                                                                                                                                                                                                                                                  |                        |         |       |                                                           |  |  |  |

| AD55          | TCONV     | Conversion Time                                                      | _                                                                                                                                                                                                                                                                                                  | 12 Tad                 | _       |       | —                                                         |  |  |  |

| AD56          | FCNV      | Throughput Rate                                                      | _                                                                                                                                                                                                                                                                                                  | _                      | 1000    | ksps  | AVDD = 3.0V to 3.6V                                       |  |  |  |

|               |           | (Sampling Speed)                                                     | _                                                                                                                                                                                                                                                                                                  | —                      | 400     | ksps  | AVDD = 2.5V to 3.6V                                       |  |  |  |

| AD57          | TSAMP     | Sample Time                                                          | 1 Tad                                                                                                                                                                                                                                                                                              | —                      | —       | _     | TSAMP must be $\geq$ 132 ns                               |  |  |  |

| Timing        | Paramete  | rs                                                                   |                                                                                                                                                                                                                                                                                                    |                        |         |       |                                                           |  |  |  |

| AD60          | TPCS      | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               |                                                                                                                                                                                                                                                                                                    | 1.0 Tad                | _       | —     | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |  |  |  |

| AD61          | TPSS      | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 Tad                                                                                                                                                                                                                                                                                            |                        | 1.5 Tad |       | _                                                         |  |  |  |

| AD62          | TCSS      | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | _                                                                                                                                                                                                                                                                                                  | 0.5 Tad                | —       | _     | _                                                         |  |  |  |

| AD63          | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _                                                                                                                                                                                                                                                                                                  |                        | 2       | μS    | _                                                         |  |  |  |

#### TABLE 31-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

#### FIGURE 31-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

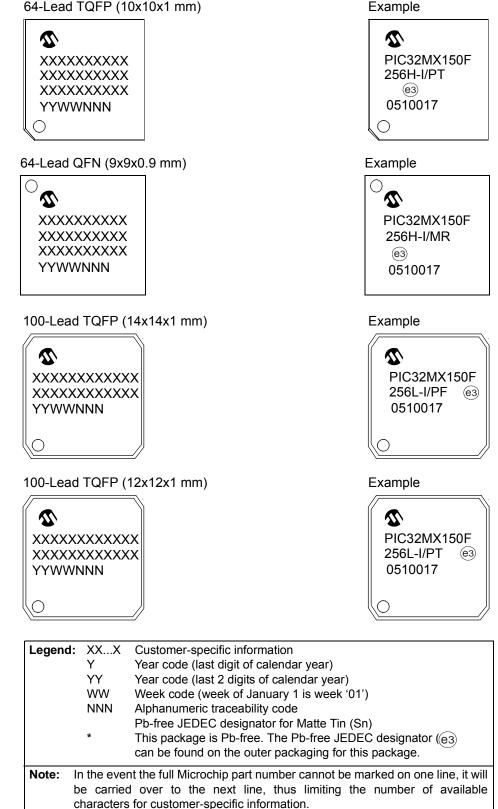

#### 34.0 **PACKAGING INFORMATION**

#### 34.1 **Package Marking Information**

64-Lead TQFP (10x10x1 mm)