Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

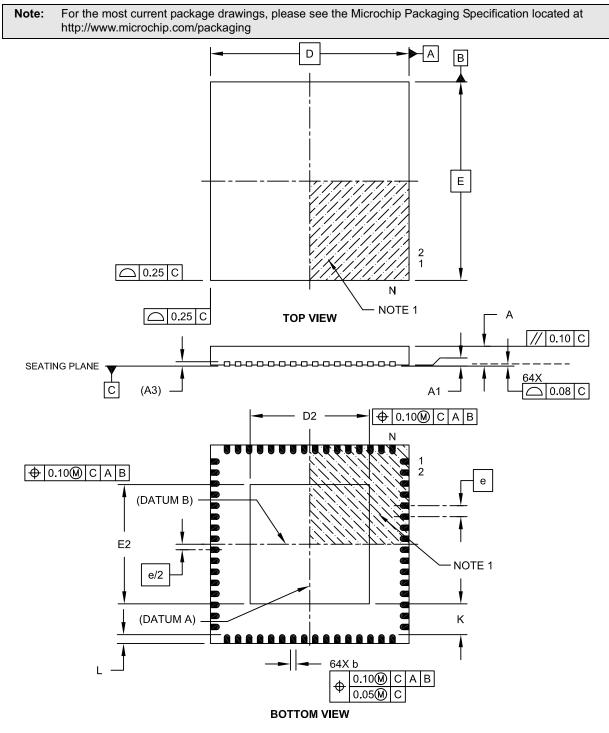

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES

# **100-PIN TQFP (TOP VIEW)**

# PIC32MX130F128L PIC32MX150F256L PIC32MX170F512L

100

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                   |

|-------|---------------------------------------|-------|---------------------------------|

| 1     | AN28/RG15                             | 36    | Vss                             |

| 2     | Vdd                                   | 37    | VDD                             |

| 3     | AN22/RPE5/PMD5/RE5                    | 38    | TCK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 39    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 40    | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 41    | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 42    | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 45    | Vss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 46    | VDD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 47    | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 48    | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 49    | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 50    | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 51    | RPF3/RF3                        |

| 17    | TMS/CTED1/RA0                         | 52    | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 53    | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 54    | RPF7/RF7                        |

| 20    | AN5/C1INA/RPB5/RB5                    | 55    | RPF6/SCK1/INT0/RF6              |

| 21    | AN4/C1INB/RB4                         | 56    | SDA1/RG3                        |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 57    | SCL1/RG2                        |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 58    | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 59    | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 60    | TDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 61    | TDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 62    | VDD                             |

| 28    | VREF-/PMA7/RA9                        | 63    | OSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 64    | OSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 65    | Vss                             |

| 31    | AVss                                  | 66    | RPA14/RA14                      |

| 32    | AN8/RPB8/CTED10/RB8                   | 67    | RPA15/RA15                      |

| 33    | AN9/RPB9/CTED4/RB9                    | 68    | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 69    | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 70    | RPD10/PMA15/RD10                |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS |            |

|------------|-------------------------|------------|

| IADLE I-I. | FINUUT I/U DESCRIFTIONS | CONTINUED) |

|           | 04-0111                               |                                       |             |                |                                                                                   |  |  |  |  |  |  |

|-----------|---------------------------------------|---------------------------------------|-------------|----------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name  |                                       |                                       | Pin<br>Type | Buffer<br>Type | Description                                                                       |  |  |  |  |  |  |

| INT0      | 35 <sup>(1)</sup> , 46 <sup>(2)</sup> | 55 <sup>(1)</sup> , 72 <sup>(2)</sup> | I           | ST             | External Interrupt 0                                                              |  |  |  |  |  |  |

| INT1      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 1                                                              |  |  |  |  |  |  |

| INT2      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 2                                                              |  |  |  |  |  |  |

| INT3      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 3                                                              |  |  |  |  |  |  |

| INT4      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 4                                                              |  |  |  |  |  |  |

| RA0       | _                                     | 17                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA1       | _                                     | 38                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA2       | —                                     | 58                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA3       | —                                     | 59                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RA4       | _                                     | 60                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RA5       | _                                     | 61                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA6       | _                                     | 91                                    | I/O         | ST             | PORTA is a bidirectional I/O port                                                 |  |  |  |  |  |  |

| RA7       | _                                     | 92                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA9       | _                                     | 28                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RA10      | _                                     | 29                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA14      | _                                     | 66                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RA15      |                                       | 67                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB0       | 16                                    | 25                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB1       | 15                                    | 24                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB2       | 14                                    | 23                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB3       | 13                                    | 22                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB4       | 12                                    | 21                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB5       | 11                                    | 20                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB6       | 17                                    | 26                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB7       | 18                                    | 27                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |  |

| RB8       | 21                                    | 32                                    | I/O         | ST             | PORTB is a bidirectional I/O port                                                 |  |  |  |  |  |  |

| RB9       | 22                                    | 33                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB10      | 23                                    | 34                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB11      | 24                                    | 35                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB12      | 27                                    | 41                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB13      | 28                                    | 42                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB14      | 29                                    | 43                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| RB15      | 30                                    | 44                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |  |

| Legend: ( | CMOS = CN                             | IOS compati<br>t Trigger inpl         | ble inpu    | it or output   | Analog = Analog input I = Input O = Output<br>Is TTL = TTL input buffer P = Power |  |  |  |  |  |  |

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

|          | Pin Number                                                                            |           |   |                |                                                                                           |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------|-----------|---|----------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP                                                                | QFN/ TOEP |   | Buffer<br>Type | Description                                                                               |  |  |  |  |  |

| RTCC     | 42                                                                                    | 68        | 0 |                | Real-Time Clock Alarm Output                                                              |  |  |  |  |  |

| CVREFOUT | 23                                                                                    | 34        | 0 | Analog         | Comparator Voltage Reference (Output)                                                     |  |  |  |  |  |

| C1INA    | 11                                                                                    | 20        | Ι | Analog         |                                                                                           |  |  |  |  |  |

| C1INB    | 12                                                                                    | 21        | Ι | Analog         | Comparator 1 Inputa                                                                       |  |  |  |  |  |

| C1INC    | 5                                                                                     | 11        | Ι | Analog         | Comparator 1 Inputs                                                                       |  |  |  |  |  |

| C1IND    | 4                                                                                     | 10        | Ι | Analog         |                                                                                           |  |  |  |  |  |

| C2INA    | 13                                                                                    | 22        | Ι | Analog         |                                                                                           |  |  |  |  |  |

| C2INB    | 14                                                                                    | 23        | Ι | Analog         | Comporator 2 Inputa                                                                       |  |  |  |  |  |

| C2INC    | 8                                                                                     | 14        | Ι | Analog         | Comparator 2 Inputs                                                                       |  |  |  |  |  |

| C2IND    | 6                                                                                     | 12        | Ι | Analog         | 7                                                                                         |  |  |  |  |  |

| C3INA    | 58                                                                                    | 87        | Ι | Analog         |                                                                                           |  |  |  |  |  |

| C3INB    | 55                                                                                    | 84        | Ι | Analog         | Comporator 2 Inputa                                                                       |  |  |  |  |  |

| C3INC    | 54                                                                                    | 83        | Ι | Analog         | Comparator 3 Inputs                                                                       |  |  |  |  |  |

| C3IND    | 51                                                                                    | 78        | Ι | Analog         |                                                                                           |  |  |  |  |  |

| C1OUT    | PPS                                                                                   | PPS       | 0 | _              | Comparator 1 Output                                                                       |  |  |  |  |  |

| C2OUT    | PPS                                                                                   | PPS       | 0 | _              | Comparator 2 Output                                                                       |  |  |  |  |  |

| C3OUT    | PPS                                                                                   | PPS       | 0 | _              | Comparator 3 Output                                                                       |  |  |  |  |  |

| PMALL    | 30                                                                                    | 44        | 0 | TTL/ST         | Parallel Master Port Address Latch Enable Low Byte                                        |  |  |  |  |  |

| PMALH    | 29                                                                                    | 43        | 0 | TTL/ST         | Parallel Master Port Address Latch Enable High Byte                                       |  |  |  |  |  |

| PMA0     | 30                                                                                    | 44        | 0 | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |  |  |  |  |  |

| PMA1     | 29                                                                                    | 43        | 0 | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |  |  |  |  |  |

| Legend:  | egend: CMOS = CMOS compatible input or output Analog = Analog input I = Input O = Out |           |   |                |                                                                                           |  |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input I = Input ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

| Interment Course (1)                       |       | Vector<br># |               | Persistent   |              |              |           |

|--------------------------------------------|-------|-------------|---------------|--------------|--------------|--------------|-----------|

| Interrupt Source <sup>(1)</sup>            | IRQ # |             | Flag          | Enable       | Priority     | Sub-priority | Interrupt |

| CNA – PORTA Input Change Interrupt         | 44    | 33          | IFS1<12>      | IEC1<12>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNB – PORTB Input Change Interrupt         | 45    | 33          | IFS1<13>      | IEC1<13>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNC – PORTC Input Change Interrupt         | 46    | 33          | IFS1<14>      | IEC1<14>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CND – PORTD Input Change Interrupt         | 47    | 33          | IFS1<15>      | IEC1<15>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNE – PORTE Input Change Interrupt         | 48    | 33          | IFS1<16>      | IEC1<16>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNF – PORTF Input Change Interrupt         | 49    | 33          | IFS1<17>      | IEC1<17>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNG – PORTG Input Change Interrupt         | 50    | 33          | IFS1<18>      | IEC1<18>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| PMP – Parallel Master Port                 | 51    | 34          | IFS1<19>      | IEC1<19>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |

| PMPE – Parallel Master Port Error          | 52    | 34          | IFS1<20>      | IEC1<20>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |

| SPI2E – SPI2 Fault                         | 53    | 35          | IFS1<21>      | IEC1<21>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| SPI2RX – SPI2 Receive Done                 | 54    | 35          | IFS1<22>      | IEC1<22>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| SPI2TX – SPI2 Transfer Done                | 55    | 35          | IFS1<23>      | IEC1<23>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| U2E – UART2 Error                          | 56    | 36          | IFS1<24>      | IEC1<24>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| U2RX – UART2 Receiver                      | 57    | 36          | IFS1<25>      | IEC1<25>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| U2TX – UART2 Transmitter                   | 58    | 36          | IFS1<26>      | IEC1<26>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| I2C2B – I2C2 Bus Collision Event           | 59    | 37          | IFS1<27>      | IEC1<27>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| I2C2S – I2C2 Slave Event                   | 60    | 37          | IFS1<28>      | IEC1<28>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| I2C2M – I2C2 Master Event                  | 61    | 37          | IFS1<29>      | IEC1<29>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| U3E – UART3 Error                          | 62    | 38          | IFS1<30>      | IEC1<30>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U3RX – UART3 Receiver                      | 63    | 38          | IFS1<31>      | IEC1<31>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U3TX – UART3 Transmitter                   | 64    | 38          | IFS2<0>       | IEC2<0>      | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U4E – UART4 Error                          | 65    | 39          | IFS2<1>       | IEC2<1>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U4RX – UART4 Receiver                      | 66    | 39          | IFS2<2>       | IEC2<2>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U4TX – UART4 Transmitter                   | 67    | 39          | IFS2<3>       | IEC2<3>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U5E – UART5 Error <sup>(2)</sup>           | 68    | 40          | IFS2<4>       | IEC2<4>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69    | 40          | IFS2<5>       | IEC2<5>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70    | 40          | IFS2<6>       | IEC2<6>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| CTMU – CTMU Event <sup>(2)</sup>           | 71    | 41          | IFS2<7>       | IEC2<7>      | IPC10<12:10> | IPC10<9:8>   | Yes       |

| DMA0 – DMA Channel 0                       | 72    | 42          | IFS2<8>       | IEC2<8>      | IPC10<20:18> | IPC10<17:16> | No        |

| DMA1 – DMA Channel 1                       | 73    | 43          | IFS2<9>       | IEC2<9>      | IPC10<28:26> | IPC10<25:24> | No        |

| DMA2 – DMA Channel 2                       | 74    | 44          | IFS2<10>      | IEC2<10>     | IPC11<4:2>   | IPC11<1:0>   | No        |

| DMA3 – DMA Channel 3                       | 75    | 45          | IFS2<11>      | IEC2<11>     | IPC11<12:10> | IPC11<9:8>   | No        |

| CMP3 – Comparator 3 Interrupt              | 76    | 46          | IFS2<12>      | IEC2<12>     | IPC11<20:18> | IPC11<17:16> | No        |

| CAN1 – CAN1 Event                          | 77    | 47          | IFS2<13>      | IEC2<13>     | IPC11<28:26> | IPC11<25:24> | Yes       |

| SPI3E – SPI3 Fault                         | 78    | 48          | IFS2<14>      | IEC2<14>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |

| SPI3RX – SPI3 Receive Done                 | 79    | 48          | IFS2<15>      | IEC2<15>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |

| SPI3TX – SPI3 Transfer Done                | 80    | 48          | IFS2<16>      | IEC2<16>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81    | 49          | IFS2<17>      | IEC2<17>     | IPC12<12:10> | IPC12<9:8>   | Yes       |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82    | 49          | IFS2<18>      | IEC2<18>     | IPC12<12:10> | IPC12<9:8>   | Yes       |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83    | 49          | IFS2<19>      | IEC2<19>     | IPC12<12:10> | IPC12<9:8>   | Yes       |

|                                            | •     | Lowe        | st Natural Or | der Priority |              | 1            |           |

# TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 | —                 | _                 | IP3<2:0>          |                   |                   | IS3<1:0>         |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 | —                 | _                 | IP2<2:0>          |                   |                   | IS2<             | 1:0>             |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | —                 | —                 | —                 |                   | IP1<2:0>          |                   | IS1<1:0>         |                  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | _                 | _                 | IP0<2:0>          |                   |                   | IS0<             | :1:0>            |  |

# REGISTER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

000 = Interrupt is disabled

bit 25-24 **IS3<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

```

111 = Interrupt priority is 7

```

```

•

•

• • • •

```

- 010 = Interrupt priority is 2

- 001 = Interrupt priority is 1 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

Note: This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions.

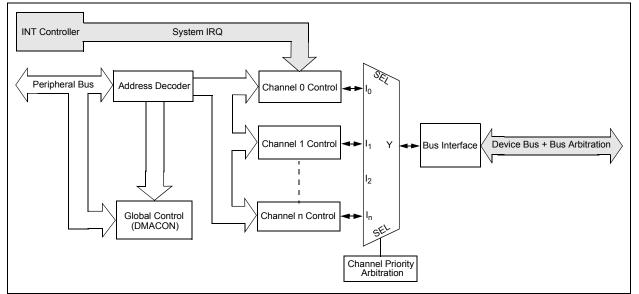

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

The following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

# FIGURE 9-1: DMA BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | _                 | —                | _                |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | _                 | _                 |                   | —                | -                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | —                | _                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | _                 | —                 | _                 | _                 | RDWR              | [                 | DMACH<2:0>       |                  |  |

# REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

# Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

# bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

# REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 0.61         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   | -                 |                   |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | -                 | -                 | _                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

# REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

# Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 **LSPDEN:** Low Speed Enable Indicator bit

1 = Next token command to be executed at Low Speed

0 = Next token command to be executed at Full Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | -                 | -                 | -                 | _                 | -                | -                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | _                 | _                 | _                 | —                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | -                 | -                 | -                 | —                 |                  | —                |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | .<7:0>            |                   |                  |                  |

# REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

# 11.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

# 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin, regardless of the output function including PPS remapped output functions to act as an open-drain output. The only exception is the  $l^2C$  pins that are open drain by default.

The open-drain feature allows the presence of outputs higher than  $V_{DD}$  (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default. The ANSELx register bit, when cleared, disables the corresponding digital input buffer pin(s).

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module. The TRISx bits only control the corresponding digital output buffer pin(s).

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level; i.e., when ANSELx = 1; TRISx = x).

Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be an NOP.

# 11.1.4 INPUT CHANGE NOTIFICATION

The input Change Notification (CN) function of the I/O ports allows the PIC32MX1XX/2XX/5XX 64/100-pin devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

# 11.1.5 INTERNALLY SELECTABLE PULL-UPS AND PULL-DOWNS

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it, which are independent of any other I/O pin functionality (i.e., PPS, Open Drain, or CN). The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

An additional control register (CNCONx) is shown in Register 11-3.

# 11.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

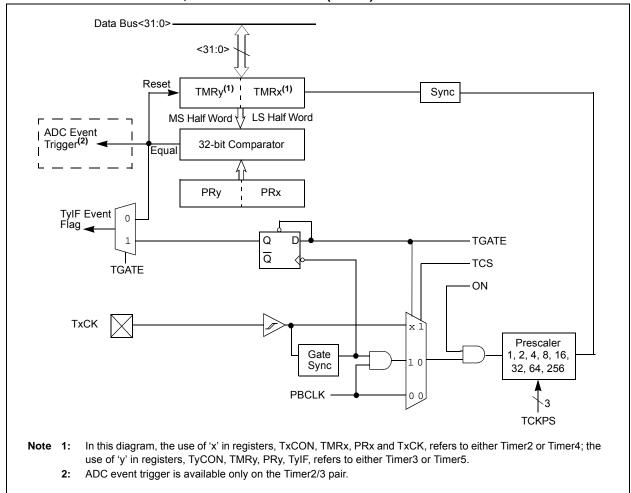

# FIGURE 13-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                  | —                   | —                   | —                 | —                | —                |

| 22.16        | R/W-0, HC         | U-0               | U-0                | U-0                 | U-0                 | U-0               | R/W-0            | U-0              |

| 23:16        | RDSTART           | —                 | _                  | _                   | _                   | _                 | DUALBUF          | _                |

| 45.0         | R/W-0             | U-0               | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL               | ADRMU               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <b>(2)</b>   | ALP <sup>(2)</sup> | CS2P <sup>(2)</sup> | CS1P <sup>(2)</sup> | _                 | WRSP             | RDSP             |

### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

| Legend:           | HC = Hardware cleared | HC = Hardware cleared              |                    |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-24 Unimplemented: Read as '0'

- bit 23 RDSTART: Start a Read on the PMP Bus bit<sup>(3)</sup>

- 1 = Start a read cycle on the PMP bus

- 0 = No effect

This bit is cleared by hardware at the end of the read cycle when the BUSY bit (PMMODE<15>) = 0.

bit 22-18 Unimplemented: Read as '0'

### bit 17 **DUALBUF:** Parallel Master Port Dual Read/Write Buffer Enable bit

- This bit is only valid in Master mode.

- PMP uses separate registers for reads and writes Reads: PMRADDR and PMRDIN Writes: PMRWADDR and PMDOUT

- 0 = PMP uses legacy registers for reads and writes Reads/Writes: PMADDR and PMRDIN

- bit 16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP enabled

- 0 = PMP disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

bit 10

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

# bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 PTWREN: Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port enabled

- 0 = PMWR/PMENB port disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- **2:** These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|---------------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | -                 | _                 | _                         | _                 | _                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                 |                   | _                         | _                 |                   | _                | —                |  |

| 45.0         | R-0               | R/W-0             | R/W-0             | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | BUSY              | IRQM              | <1:0>             | INCM                      | <1:0>             | MODE16            | MODE             | =<1:0>           |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | WAITB             | <1:0> <b>(1)</b>  |                   | WAITM<3:0> <sup>(1)</sup> |                   |                   | WAITE<1:0>(1)    |                  |  |

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER

# Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

### bit 14-13 **IRQM<1:0>:** Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

- bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 **MODE16:** 8/16-bit Mode bit

- 1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

- 0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS and PMD<7:0>)

# bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- 3: These pins are active when MODE16 = 1 (16-bit mode).

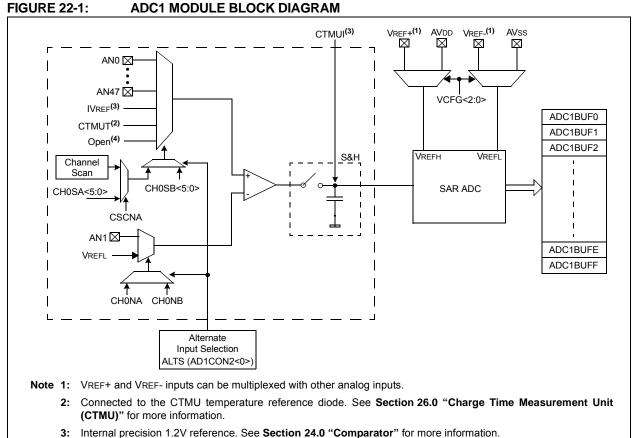

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- Up to 48 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

4: This selection is only used with CTMU capacitive and time measurement.

# REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

- bit 10-8 **PRSEG<2:0>:** Propagation Time Segment bits<sup>(4)</sup> 111 = Length is  $8 \times TQ$  $000 = \text{Length is } 1 \times TQ$ SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup> bit 7-6 11 = Length is  $4 \times TQ$  $10 = \text{Length is } 3 \times TQ$ 01 = Length is 2 x TQ  $00 = \text{Length is } 1 \times TQ$ bit 5-0 BRP<5:0>: Baud Rate Prescaler bits 111111 = Tq = (2 x 64)/SYSCLK 111110 = TQ = (2 x 63)/SYSCLK • 000001 = TQ = (2 x 2)/SYSCLK  $000000 = TQ = (2 \times 1)/SYSCLK$ Note 1: SEG2PH  $\leq$  SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. 2: 3 Time bit sampling is not allowed for BRP < 2.

- **3:** SJW  $\leq$  SEG2PH.

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

# 31.1 DC Characteristics

# TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                | Voo Bango                              | Temp. Range     | Max. Frequency                          |

|----------------|----------------------------------------|-----------------|-----------------------------------------|

| Characteristic | VDD Range<br>(in Volts) <sup>(1)</sup> | (in °C)         | PIC32MX1XX/2XX/5XX 64/100-pin<br>Family |

| DC5            | VBOR-3.6V                              | -40°C to +105°C | 40 MHz                                  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

# TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol | Min.        | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                       |        |             |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40         | —           | +85  | °C   |

| V-temp Temperature Devices                                                           |        |             |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40         | —           | +105 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD – S IOH) | PD     | PINT + PI/O |             | W    |      |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOH} x IOH) + S (VOL x IOL))          |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                    | PDMAX  | (           | TJ — TA)/θJ | A    | W    |

# TABLE 31-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                                         | Symbol | Typical | Max. | Unit | Notes |

|---------------------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 64-pin QFN                  | θJA    | 28      | _    | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP, 10 mm x 10 mm  | θJA    | 55      | _    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP, 12 mm x 12 mm | θJA    | 52      | _    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP, 14 mm x 14 mm | θJA    | 50      |      | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHARACTERISTICS |       |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)                                                                                                                  |                        |            |       |                                                   |  |

|--------------------|-------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|

|                    |       |                                                         | $\begin{array}{ll} \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                        |            |       |                                                   |  |

| Param.<br>No.      |       | Characteristics                                         | Min.                                                                                                                                                                                   | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |

|                    | VIL   | Input Low Voltage                                       |                                                                                                                                                                                        |                        |            |       |                                                   |  |

| DI10               |       | I/O Pins with PMP                                       | Vss                                                                                                                                                                                    | —                      | 0.15 Vdd   | V     |                                                   |  |

|                    |       | I/O Pins                                                | Vss                                                                                                                                                                                    | —                      | 0.2 Vdd    | V     |                                                   |  |

| DI18               |       | SDAx, SCLx                                              | Vss                                                                                                                                                                                    | —                      | 0.3 VDD    | V     | SMBus disabled<br>(Note 4)                        |  |

| DI19               |       | SDAx, SCLx                                              | Vss                                                                                                                                                                                    | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |

|                    | VIH   | Input High Voltage                                      |                                                                                                                                                                                        |                        |            |       |                                                   |  |

| DI20               |       | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                               | _                      | Vdd        | V     | (Note 4,6)                                        |  |

|                    |       | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                        | —                      | 5.5        | V     | (Note 4,6)                                        |  |

|                    |       | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                                                                                                                                               | —                      | 5.5        | V     |                                                   |  |

| DI28               |       | SDAx, SCLx                                              | 0.65 VDD                                                                                                                                                                               | —                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |

| DI29               |       | SDAx, SCLx                                              | 2.1                                                                                                                                                                                    | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |

| DI30               | ICNPU | Change Notification<br>Pull-up Current                  | _                                                                                                                                                                                      | -200                   | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |

| DI31               | ICNPD | Change Notification<br>Pull-down Current <sup>(4)</sup> | 50                                                                                                                                                                                     | 200                    | —          | μA    | VDD = 3.3V, VPIN = VDD                            |  |

|                    | lı∟   | Input Leakage Current<br>(Note 3)                       |                                                                                                                                                                                        |                        |            |       |                                                   |  |

| DI50               |       | I/O Ports                                               | _                                                                                                                                                                                      | —                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |

| DI51               |       | Analog Input Pins                                       | _                                                                                                                                                                                      | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |

| DI55               |       | MCLR <sup>(2)</sup>                                     | _                                                                                                                                                                                      | _                      | <u>+</u> 1 | μA    | $VSS \le VPIN \le VDD$                            |  |

| DI56               |       | OSC1                                                    | -                                                                                                                                                                                      | —                      | <u>+</u> 1 | μΑ    | $VSS \le VPIN \le VDD,$ XT and HS modes           |  |

# TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- **6:** The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

# 32.1 DC Characteristics

# TABLE 32-1: OPERATING MIPS VS. VOLTAGE

|      | VDD Range Temp. Range                  |                | Max. Frequency                          |  |  |

|------|----------------------------------------|----------------|-----------------------------------------|--|--|

|      | VDD Range<br>(in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX/5XX 64/100-pin<br>Family |  |  |

| MDC5 | VBOR-3.6V                              | -40°C to +85°C | 50 MHz                                  |  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

### TABLE 32-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |                  | rwise stated) |  |  |  |

|-------------------------------------|-------------------------------------------------------|------|------------------|---------------|--|--|--|

| Parameter<br>No.                    | Typical <sup>(3)</sup>                                | Max. | Units Conditions |               |  |  |  |

| Operating Current (IDD) (Note 1, 2) |                                                       |      |                  |               |  |  |  |

| MDC24                               | 25                                                    | 40   | mA 50 MHz        |               |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- **3:** RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

# TABLE 32-3: DC CHARACTERISTICS: IDLE CURRENT (lidle)

| DC CHARACT                                                     | C CHARACTERISTICS      |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |  |

|----------------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                |  |  |  |