Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

|                           | A sales as                                                                     |

| Product Status            | Active                                                                         |

| Core Processor            | MIPS32® M4K™                                                                   |

| Core Size                 | 32-Bit Single-Core                                                             |

| peed                      | 40MHz                                                                          |

| connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| Number of I/O             | 53                                                                             |

| rogram Memory Size        | 256KB (256K x 8)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AAM Size                  | 32K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 28x10b                                                                     |

| Scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| lounting Type             | Surface Mount                                                                  |

| ackage / Case             | 64-VFQFN Exposed Pad                                                           |

| upplier Device Package    | 64-QFN (9x9)                                                                   |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256h-v-mr |

### **Device Pin Tables**

#### TABLE 2: PIN NAMES FOR 64-PIN GENERAL PURPOSE DEVICES

64-PIN QFN<sup>(4)</sup> AND TQFP (TOP VIEW)

PIC32MX120F064H PIC32MX130F128H PIC32MX150F256H PIC32MX170F512H

64 1 64 **TQFP**

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 1    | AN22/RPE5/PMD5/RE5                        |

| 2    | AN23/PMD6/RE6                             |

| 3    | AN27/PMD7/RE7                             |

| 4    | AN16/C1IND/RPG6/SCK2/PMA5/RG6             |

| 5    | AN17/C1INC/RPG7/PMA4/RG7                  |

| 6    | AN18/C2IND/RPG8/PMA3/RG8                  |

| 7    | MCLR                                      |

| 8    | AN19/C2INC/RPG9/PMA2/RG9                  |

| 9    | Vss                                       |

| 10   | VDD                                       |

| 11   | AN5/C1INA/RPB5/RB5                        |

| 12   | AN4/C1INB/RB4                             |

| 13   | PGED3/AN3/C2INA/RPB3/RB3                  |

| 14   | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2     |

| 15   | PGEC1/VREF-/AN1/RPB1/CTED12/RB1           |

| 16   | PGED1/VREF+/AN0/RPB0/PMA6/RB0             |

| 17   | PGEC2/AN6/RPB6/RB6                        |

| 18   | PGED2/AN7/RPB7/CTED3/RB7                  |

| 19   | AVDD                                      |

| 20   | AVss                                      |

| 21   | AN8/RPB8/CTED10/RB8                       |

| 22   | AN9/RPB9/CTED4/PMA7/RB9                   |

| 23   | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| 24   | TDO/AN11/PMA12/RB11                       |

| 25   | Vss                                       |

| 26   | VDD                                       |

| 27   | TCK/AN12/PMA11/RB12                       |

| 28   | TDI/AN13/PMA10/RB13                       |

| 29   | AN14/RPB14/SCK3/CTED5/PMA1/RB14           |

| 30   | AN15/RPB15/OCFB/CTED6/PMA0/RB15           |

| 31   | RPF4/SDA2/PMA9/RF4                        |

| 32   | RPF5/SCL2/PMA8/RF5                        |

|      |                                           |

| Pin# | Full Pin Name         |

|------|-----------------------|

| 33   | RPF3/RF3              |

| 34   | RPF2/RF2              |

| 35   | RPF6/SCK1/INT0/RF6    |

| 36   | SDA1/RG3              |

| 37   | SCL1/RG2              |

| 38   | VDD                   |

| 39   | OSC1/CLKI/RC12        |

|      |                       |

| 40   | OSC2/CLKO/RC15        |

| 41   | VSS                   |

| 42   | RPD8/RTCC/RD8         |

| 43   | RPD9/RD9              |

| 44   | RPD10/PMA15/RD10      |

| 45   | RPD11/PMA14/RD11      |

| 46   | RPD0/RD0              |

| 47   | SOSCI/RPC13/RC13      |

| 48   | SOSCO/RPC14/T1CK/RC14 |

| 49   | AN24/RPD1/RD1         |

| 50   | AN25/RPD2/RD2         |

| 51   | AN26/C3IND/RPD3/RD3   |

| 52   | RPD4/PMWR/RD4         |

| 53   | RPD5/PMRD/RD5         |

| 54   | C3INC/RD6             |

| 55   | C3INB/RD7             |

| 56   | VCAP                  |

| 57   | VDD                   |

| 58   | C3INA/RPF0/RF0        |

| 59   | RPF1/RF1              |

| 60   | PMD0/RE0              |

| 61   | PMD1/RE1              |

| 62   | AN20/PMD2/RE2         |

| 63   | RPE3/CTPLS/PMD3/RE3   |

| 64   | AN21/PMD4/RE4         |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

- 4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin N                                 | umber                                 |             |                |                                                |

|----------|---------------------------------------|---------------------------------------|-------------|----------------|------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP                       | Pin<br>Type | Buffer<br>Type | Description                                    |

| U3CTS    | PPS                                   | PPS                                   | I           | ST             | UART3 Clear to Send                            |

| U3RTS    | PPS                                   | PPS                                   | 0           | _              | UART3 Ready to Send                            |

| U3RX     | PPS                                   | PPS                                   | 1           | ST             | UART3 Receive                                  |

| U3TX     | PPS                                   | PPS                                   | 0           | _              | UART3 Transmit                                 |

| U4CTS    | PPS                                   | PPS                                   | I           | ST             | UART4 Clear to Send                            |

| U4RTS    | PPS                                   | PPS                                   | 0           | _              | UART4 Ready to Send                            |

| U4RX     | PPS                                   | PPS                                   | I           | ST             | UART4 Receive                                  |

| U4TX     | PPS                                   | PPS                                   | 0           | _              | UART4 Transmit                                 |

| U5CTS    |                                       | PPS                                   | I           | ST             | UART5 Clear to Send                            |

| U5RTS    | _                                     | PPS                                   | 0           | _              | UART5 Ready to Send                            |

| U5RX     |                                       | PPS                                   | I           | ST             | UART5 Receive                                  |

| U5TX     | _                                     | PPS                                   | 0           | _              | UART5 Transmit                                 |

| SCK1     | 35 <sup>(1)</sup> , 50 <sup>(2)</sup> | 55 <sup>(1)</sup> , 70 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI1 |

| SDI1     | PPS                                   | PPS                                   | - 1         | _              | SPI1 Data In                                   |

| SDO1     | PPS                                   | PPS                                   | 0           | ST             | SPI1 Data Out                                  |

| SS1      | PPS                                   | PPS                                   | I/O         | _              | SPI1 Slave Synchronization for Frame Pulse I/O |

| SCK2     | 4                                     | 10                                    | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI2 |

| SDI2     | PPS                                   | PPS                                   | -           | _              | SPI2 Data In                                   |

| SDO2     | PPS                                   | PPS                                   | 0           | ST             | SPI2 Data Out                                  |

| SS2      | PPS                                   | PPS                                   | I/O         | _              | SPI2 Slave Synchronization for Frame Pulse I/O |

| SCK3     | 29                                    | 39                                    | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI3 |

| SDI3     | PPS                                   | PPS                                   | I           | _              | SPI3 Data In                                   |

| SDO3     | PPS                                   | PPS                                   | 0           | ST             | SPI3 Data Out                                  |

| SS3      | PPS                                   | PPS                                   | I/O         | _              | SPI3 Slave Synchronization for Frame Pulse I/O |

| SCK4     | _                                     | 48                                    | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI4 |

| SDI4     | _                                     | PPS                                   | ı           | _              | SPI4 Data In                                   |

| SDO4     | _                                     | PPS                                   | 0           | ST             | SPI4 Data Out                                  |

| SS4      | _                                     | PPS                                   | I/O         | _              | SPI4 Slave Synchronization for Frame Pulse I/O |

| SCL1     | 37 <sup>(1)</sup> , 44 <sup>(2)</sup> | 57 <sup>(1)</sup> , 66 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Clock Input/Output for I2C1 |

| SDA1     | 36 <sup>(1)</sup> , 43 <sup>(2)</sup> | 56 <sup>(1)</sup> , 67 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Data Input/Output for I2C1  |

| SCL2     | 32                                    | 58                                    | I/O         | ST             | Synchronous Serial Clock Input/Output for I2C2 |

| SDA2     | 31                                    | 59                                    | I/O         | ST             | Synchronous Serial Data Input/Output for I2C2  |

| TMS      | 23                                    | 17                                    | I           | ST             | JTAG Test Mode Select Pin                      |

| TCK      | 27                                    | 38                                    | I           | ST             | JTAG Test Clock Input Pin                      |

| TDI      | 28                                    | 60                                    | I           | _              | JTAG Test Clock Input Pin                      |

| TDO      | 24                                    | 61                                    | 0           | _              | JTAG Test Clock Output Pin                     |

| I        | 01400 014                             | IOS compati                           | la La Casas | .4             | Analog = Analog input $I = Input O = Output$   |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levelsAnalog = Analog input<br/>TTL = TTL input bufferI = Input<br/>P = Power

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices with a USB module.

- **4:** This pin is only available on 100-pin devices without a USB module.

### 4.0 MEMORY ORGANIZATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "**Memory Organization**" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX/5XX 64/100-pin devices to execute from data memory.

The key features include:

- · 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

### 4.1 Memory Layout

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX/5XX 64/ 100-pin devices are illustrated in Figure 4-1 through Figure 4-4.

TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | 100 " | Vector |               | Interru      | upt Bit Location |              | Persistent |

|-------------------------------------|-------|--------|---------------|--------------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>     | IRQ#  | #      | Flag          | Enable       | Priority         | Sub-priority | Interrupt  |

|                                     | •     | Highe  | st Natural Or | der Priority | <u> </u>         | <u> </u>     |            |

| CT – Core Timer Interrupt           | 0     | 0      | IFS0<0>       | IEC0<0>      | IPC0<4:2>        | IPC0<1:0>    | No         |

| CS0 – Core Software Interrupt 0     | 1     | 1      | IFS0<1>       | IEC0<1>      | IPC0<12:10>      | IPC0<9:8>    | No         |

| CS1 – Core Software Interrupt 1     | 2     | 2      | IFS0<2>       | IEC0<2>      | IPC0<20:18>      | IPC0<17:16>  | No         |

| INT0 – External Interrupt           | 3     | 3      | IFS0<3>       | IEC0<3>      | IPC0<28:26>      | IPC0<25:24>  | No         |

| T1 – Timer1                         | 4     | 4      | IFS0<4>       | IEC0<4>      | IPC1<4:2>        | IPC1<1:0>    | No         |

| IC1E – Input Capture 1 Error        | 5     | 5      | IFS0<5>       | IEC0<5>      | IPC1<12:10>      | IPC1<9:8>    | Yes        |

| IC1 – Input Capture 1               | 6     | 5      | IFS0<6>       | IEC0<6>      | IPC1<12:10>      | IPC1<9:8>    | Yes        |

| OC1 – Output Compare 1              | 7     | 6      | IFS0<7>       | IEC0<7>      | IPC1<20:18>      | IPC1<17:16>  | No         |

| INT1 – External Interrupt 1         | 8     | 7      | IFS0<8>       | IEC0<8>      | IPC1<28:26>      | IPC1<25:24>  | No         |

| T2 – Timer2                         | 9     | 8      | IFS0<9>       | IEC0<9>      | IPC2<4:2>        | IPC2<1:0>    | No         |

| IC2E – Input Capture 2              | 10    | 9      | IFS0<10>      | IEC0<10>     | IPC2<12:10>      | IPC2<9:8>    | Yes        |

| IC2 – Input Capture 2               | 11    | 9      | IFS0<11>      | IEC0<11>     | IPC2<12:10>      | IPC2<9:8>    | Yes        |

| OC2 – Output Compare 2              | 12    | 10     | IFS0<12>      | IEC0<12>     | IPC2<20:18>      | IPC2<17:16>  | No         |

| INT2 – External Interrupt 2         | 13    | 11     | IFS0<13>      | IEC0<13>     | IPC2<28:26>      | IPC2<25:24>  | No         |

| T3 – Timer3                         | 14    | 12     | IFS0<14>      | IEC0<14>     | IPC3<4:2>        | IPC3<1:0>    | No         |

| IC3E – Input Capture 3              | 15    | 13     | IFS0<15>      | IEC0<15>     | IPC3<12:10>      | IPC3<9:8>    | Yes        |

| IC3 – Input Capture 3               | 16    | 13     | IFS0<16>      | IEC0<16>     | IPC3<12:10>      | IPC3<9:8>    | Yes        |

| OC3 – Output Compare 3              | 17    | 14     | IFS0<17>      | IEC0<17>     | IPC3<20:18>      | IPC3<17:16>  | No         |

| INT3 – External Interrupt 3         | 18    | 15     | IFS0<18>      | IEC0<18>     | IPC3<28:26>      | IPC3<25:24>  | No         |

| T4 – Timer4                         | 19    | 16     | IFS0<19>      | IEC0<19>     | IPC4<4:2>        | IPC4<1:0>    | No         |

| IC4E – Input Capture 4 Error        | 20    | 17     | IFS0<20>      | IEC0<20>     | IPC4<12:10>      | IPC4<9:8>    | Yes        |

| IC4 – Input Capture 4               | 21    | 17     | IFS0<21>      | IEC0<21>     | IPC4<12:10>      | IPC4<9:8>    | Yes        |

| OC4 – Output Compare 4              | 22    | 18     | IFS0<22>      | IEC0<22>     | IPC4<20:18>      | IPC4<17:16>  | No         |

| INT4 – External Interrupt 4         | 23    | 19     | IFS0<23>      | IEC0<23>     | IPC4<28:26>      | IPC4<25:24>  | No         |

| T5 – Timer5                         | 24    | 20     | IFS0<24>      | IEC0<24>     | IPC5<4:2>        | IPC5<1:0>    | No         |

| IC5E – Input Capture 5 Error        | 25    | 21     | IFS0<25>      | IEC0<25>     | IPC5<12:10>      | IPC5<9:8>    | Yes        |

| IC5 – Input Capture 5               | 26    | 21     | IFS0<26>      | IEC0<26>     | IPC5<12:10>      | IPC5<9:8>    | Yes        |

| OC5 – Output Compare 5              | 27    | 22     | IFS0<27>      | IEC0<27>     | IPC5<20:18>      | IPC5<17:16>  | No         |

| AD1 – ADC1 Convert done             | 28    | 23     | IFS0<28>      | IEC0<28>     | IPC5<28:26>      | IPC5<25:24>  | Yes        |

| FSCM – Fail-Safe Clock Monitor      | 29    | 24     | IFS0<29>      | IEC0<29>     | IPC6<4:2>        | IPC6<1:0>    | No         |

| RTCC – Real-Time Clock and Calendar | 30    | 25     | IFS0<30>      | IEC0<30>     | IPC6<12:10>      | IPC6<9:8>    | No         |

| FCE – Flash Control Event           | 31    | 26     | IFS0<31>      | IEC0<31>     | IPC6<20:18>      | IPC6<17:16>  | No         |

| CMP1 – Comparator Interrupt         | 32    | 27     | IFS1<0>       | IEC1<0>      | IPC6<28:26>      | IPC6<25:24>  | No         |

| CMP2 – Comparator Interrupt         | 33    | 28     | IFS1<1>       | IEC1<1>      | IPC7<4:2>        | IPC7<1:0>    | No         |

| USB – USB Interrupts                | 34    | 29     | IFS1<2>       | IEC1<2>      | IPC7<12:10>      | IPC7<9:8>    | Yes        |

| SPI1E – SPI1 Fault                  | 35    | 30     | IFS1<3>       | IEC1<3>      | IPC7<20:18>      | IPC7<17:16>  | Yes        |

| SPI1RX – SPI1 Receive Done          | 36    | 30     | IFS1<4>       | IEC1<4>      | IPC7<20:18>      | IPC7<17:16>  | Yes        |

| SPI1TX – SPI1 Transfer Done         | 37    | 30     | IFS1<5>       | IEC1<5>      | IPC7<20:18>      | IPC7<17:16>  | Yes        |

| U1E – UART1 Fault                   | 38    | 31     | IFS1<6>       | IEC1<6>      | IPC7<28:26>      | IPC7<25:24>  | Yes        |

| U1RX – UART1 Receive Done           | 39    | 31     | IFS1<7>       | IEC1<7>      | IPC7<28:26>      | IPC7<25:24>  | Yes        |

| U1TX – UART1 Transfer Done          | 40    | 31     | IFS1<8>       | IEC1<8>      | IPC7<28:26>      | IPC7<25:24>  | Yes        |

| I2C1B – I2C1 Bus Collision Event    | 41    | 32     | IFS1<9>       | IEC1<9>      | IPC8<4:2>        | IPC8<1:0>    | Yes        |

| I2C1S – I2C1 Slave Event            | 42    | 32     | IFS1<10>      | IEC1<10>     | IPC8<4:2>        | IPC8<1:0>    | Yes        |

| I2C1M – I2C1 Master Event           | 43    | 32     | IFS1<11>      | IEC1<11>     | IPC8<4:2>        | IPC8<1:0>    | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

<sup>2:</sup> This interrupt source is not available on 64-pin devices.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED) bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits 111 = Clock is multiplied by 24 110 = Clock is multiplied by 21 101 = Clock is multiplied by 20 100 = Clock is multiplied by 19 011 = Clock is multiplied by 18 010 = Clock is multiplied by 17 001 = Clock is multiplied by 16 000 = Clock is multiplied by 15 bit 15 Unimplemented: Read as '0' bit 14-12 COSC<2:0>: Current Oscillator Selection bits 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits 110 = Internal Fast RC (FRC) Oscillator divided by 16 101 = Internal Low-Power RC (LPRC) Oscillator 100 = Secondary Oscillator (Sosc) 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL) 010 = Primary Oscillator (Posc) (XT, HS or EC) 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL) 000 = Internal Fast RC (FRC) Oscillator bit 11 Unimplemented: Read as '0' bit 10-8 NOSC<2:0>: New Oscillator Selection bits 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits 110 = Internal Fast RC Oscillator (FRC) divided by 16 101 = Internal Low-Power RC (LPRC) Oscillator 100 = Secondary Oscillator (Sosc) 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL) 010 = Primary Oscillator (XT, HS or EC) 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL) 000 = Internal Fast Internal RC Oscillator (FRC) On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>). bit 7 **CLKLOCK:** Clock Selection Lock Enable bit If clock switching and monitoring is disabled (FCKSM<1:0> = 1x): 1 = Clock and PLL selections are locked 0 = Clock and PLL selections are not locked and may be modified If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified. **ULOCK:** USB PLL Lock Status bit (1) bit 6 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled bit 5 **SLOCK: PLL Lock Status bit** 1 = PLL module is in lock or PLL module start-up timer is satisfied 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled bit 4 SLPEN: Sleep Mode Enable bit 1 = Device will enter Sleep mode when a WAIT instruction is executed 0 = Device will enter Idle mode when a WAIT instruction is executed bit 3 CF: Clock Fail Detect bit 1 = FSCM has detected a clock failure 0 = No clock failure has been detected Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

**TABLE 11-2: OUTPUT PIN SELECTION**

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection      |

|----------------------|----------|-------------|--------------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                          |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = <u>U3TX</u>                         |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved            |

| RPD10                | RPD10R   | RPD10R<3:0> | 0111 = Reserved                            |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                            |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                                |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved         |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 - Reserved                            |

| RPB5 <sup>(7)</sup>  | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                            |

| RPC1 <sup>(3)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 = OC3                                 |

| RPD14 <sup>(3)</sup> | RPD14R   | RPD14R<3:0> | 1100 = C1TX <sup>(5)</sup><br>1101 = C2OUT |

| RPG1 <sup>(3)</sup>  | RPG1R    | RPG1R<3:0>  | 11101 = C2001<br>1110 = SDO3               |

| RPA14 <sup>(3)</sup> | RPA14R   | RPA14R<3:0> | 1111 = SDO4 <sup>(3)</sup>                 |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                          |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                                |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                            |

| RPD11                | RPD11R   | RPD11R<3:0> | 0011 = U1TX<br>0100 = U5RTS <sup>(3)</sup> |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = 05RTS(*)<br>0101 = Reserved         |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = NCSCIVED                            |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                            |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 = SDO1                                |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                            |

| RPF3 <sup>(4)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                            |

| RPC4 <sup>(3)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved              |

| RPD15 <sup>(3)</sup> | RPD15R   | RPD15R<3:0> | 1100 = Reserved<br>1101 = C3OUT            |

| RPG0 <sup>(3)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = SDO3                                |

| RPA15 <sup>(3)</sup> | RPA15R   | RPA15R<3:0> | 1111 = SDO4 <sup>(3)</sup>                 |

Note 1: This selection is not available on 64-pin USB devices.

<sup>2:</sup> This selection is only available on 100-pin General Purpose devices.

<sup>3:</sup> This selection is not available on 64-pin devices.

<sup>4:</sup> This selection is not available when USBID functionality is used on USB devices.

<sup>5:</sup> This selection is not available on devices without a CAN module.

<sup>6:</sup> This selection is not available on USB devices.

<sup>7:</sup> This selection is not available when VBUSON functionality is used on USB devices.

#### REGISTER 13-1: TxCON: TYPE B TIMER 'x' CONTROL REGISTER ('x' = 2 THROUGH 5)

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        | _                    | _                 | -                   | _                 |                    | -                 | -                  | _                |

| 23:16        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23.10        | _                    | _                 | _                   | _                 | _                  | -                 | _                  | _                |

| 15:0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | _                  | _                 | _                  | _                |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit(1,3)

1 = Module is enabled 0 = Module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit(4)

1 = Discontinue operation when device enters Idle mode

0 = Continue operation even in Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled0 = Gated time accumulation is disabled

bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

111 = 1:256 prescale value

110 = 1:64 prescale value

101 = 1:32 prescale value

100 = 1:16 prescale value

011 = 1:8 prescale value

010 = 1:4 prescale value

001 = 1:2 prescale value

000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY |  |  |  |  |  |  |  |  |  |

|--------------------------------------|--|--|--|--|--|--|--|--|--|

| IOTES:                               |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |

TABLE 14-1: WATCHDOG TIMER REGISTER MAP

| ess                        |                                 | 9         |       |       | Bits  |       |       |       |      |      |      |      |      |           | 8    |      |          |        |           |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|----------|--------|-----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1     | 16/0   | All Reset |

| 0000                       | WDTCON                          | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _         | _    | _    | _        | _      | 0000      |

| 0000                       | WDTCON                          | 15:0      | ON    | _     | _     |       | _     | _     | _    | _    | _    |      | SV   | VDTPS<4:0 | )>   |      | WDTWINEN | WDTCLR | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | -                 | _                 | _                 | _                 | _                |                  |

| 00:40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTPS<4:0         | >                 |                   | WDTWINEN         | WDTCLR           |

Legend:y = Values set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

1 = Enables the WDT if it is not enabled by the device configuration

0 = Disable the WDT if it was enabled in software

bit 14-7 Unimplemented: Read as '0'

bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

bit 1 WDTWINEN: Watchdog Timer Window Enable bit

1 = Enable windowed Watchdog Timer0 = Disable windowed Watchdog Timer

bit 0 WDTCLR: Watchdog Timer Reset bit

1 = Writing a '1' will clear the WDT

0 = Software cannot force this bit to a '0'

**Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 17-1: SPIXCON: SPI CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | )>               |                       |

| 22:16        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | _                  | _                 | _                 | _                 | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | _                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FRMEN: Framed SPI Support bit

1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

bit 30 FRMSYNC: Frame Sync Pulse Direction Control on SSx pin bit (Framed SPI mode only)

1 = Frame sync pulse input (Slave mode)

0 = Frame sync pulse output (Master mode)

bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

1 = Frame pulse is active-high

0 = Frame pulse is active-low

bit 28 MSSEN: Master Mode Slave Select Enable bit

1 = Slave select SPI support enabled. The  $\overline{SS}$  pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

0 = Slave select SPI support is disabled.

bit 27 FRMSYPW: Frame Sync Pulse Width bit

1 = Frame sync pulse is one character wide

0 = Frame sync pulse is one clock wide

bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED SYNC mode.

111 = Reserved: do not use

110 = Reserved; do not use

101 = Generate a frame sync pulse on every 32 data characters

100 = Generate a frame sync pulse on every 16 data characters

011 = Generate a frame sync pulse on every 8 data characters

010 = Generate a frame sync pulse on every 4 data characters

001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

1 = REFCLK is used by the Baud Rate Generator

0 = PBCLK is used by the Baud Rate Generator

#### bit 22-18 Unimplemented: Read as '0'

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit can only be written when the ON bit = 0.

3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

**4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

### REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 | _                 | -                 | -                 | _                 | -                | -                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | _                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

Legend:HS = Set in hardwareHSC = Hardware set/clearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedC = Clearable bit

bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

bit 14 TRSTAT: Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

bit 13-11 Unimplemented: Read as '0'

bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2$ C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

## 21.1 Control Registers

### TABLE 21-1: RTCC REGISTER MAP

| ess                         | Register<br>Name <sup>(1)</sup> | •         |                         | Bits  |         |          |             |       |              |           |            |          |              |            |              |         |         |       |            |

|-----------------------------|---------------------------------|-----------|-------------------------|-------|---------|----------|-------------|-------|--------------|-----------|------------|----------|--------------|------------|--------------|---------|---------|-------|------------|

| Virtual Address<br>(BF80_#) |                                 | Bit Range | 31/15                   | 30/14 | 29/13   | 28/12    | 27/11       | 26/10 | 25/9         | 24/8      | 23/7       | 22/6     | 21/5         | 20/4       | 19/3         | 18/2    | 17/1    | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | I:16 — — — — — CAL<9:03 |       |         |          |             |       |              |           | 9:0>       |          |              |            |              |         |         |       |            |

| 0200                        |                                 | 15:0      | ON                      | _     | SIDL    | _        | _           | _     | _            | _         | RTSECSEL   | RTCCLKON | _            | _          | RTCWREN      | RTCSYNC | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _                       | _     | _       | _        | _           | -     | _            | _         | _          | _        | _            | _          | _            | _       | _       | _     | 0000       |

| 0210                        |                                 | 15:0      | ALRMEN                  | CHIME | PIV     | ALRMSYNC | AMASK<3:0>  |       |              | ARPT<7:0> |            |          |              |            |              |         | 0000    |       |            |

| 0220                        | RTCTIME                         | 31:16     |                         | HR1   | 0<3:0>  |          | HR01<3:0>   |       |              |           | MIN10<     | 3:0>     |              | MIN01<3:0> |              |         |         | xxxx  |            |

| 0220                        | RICIIME                         | 15:0      |                         | SEC1  | 10<3:0> |          | SEC01<3:0>  |       |              |           |            | _        | -            | _          | _            | _       | _       | _     | xx00       |

| 0230                        | RTCDATE                         | 31:16     |                         | YEAR  | 10<3:0> |          | YEAR01<3:0> |       |              |           |            | MONTH10  | )<3:0>       |            | MONTH01<3:0> |         |         |       | xxxx       |

| 0230                        | KICDAIL                         | 15:0      |                         | DAY1  | 0<3:0>  |          | DAY01<3:0>  |       |              |           |            | _        | -            | _          |              | WDAY0   | 1<3:0>  |       | xx00       |

| 0240                        | ALRMTIME                        | 31:16     |                         | HR1   | 0<3:0>  |          | HR01<3:0>   |       |              |           | MIN10<3:0> |          |              | MIN01<3:0> |              |         |         | xxxx  |            |

| 0240                        |                                 | 15:0      |                         | SEC1  | 0<3:0>  |          |             | SEC0  | 1<3:0>       |           | _          | _        | _            | _          | _            | _       | _       | _     | xx00       |

| 0250                        | ALRMDATE                        | 31:16     |                         |       |         |          |             |       | MONTH10<3:0> |           |            |          | MONTH01<3:0> |            |              |         | 00xx    |       |            |

|                             | ALKIVIDATE                      | 15:0      |                         | DAY1  | 0<3:0>  |          |             | DAY0  | 1<3:0>       |           | _          | _        | _            | _          |              | WDAY0   | 1<3:0>  |       | xx0x       |

.egend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information

### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

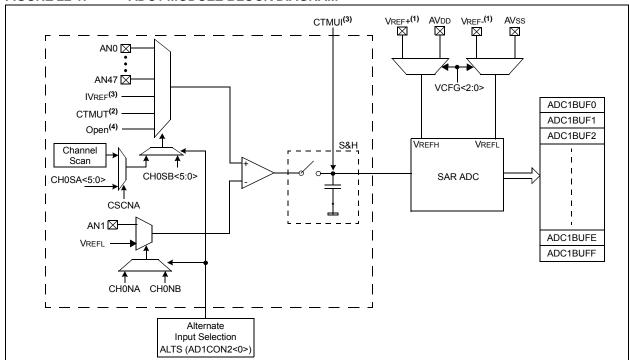

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 17.** "10-bit **Analog-to-Digital Converter (ADC)**" (DS60001104) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- Up to 48 analog input pins

- · External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

- Note 1: VREF+ and VREF- inputs can be multiplexed with other analog inputs.

- 2: Connected to the CTMU temperature reference diode. See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

- 4: This selection is only used with CTMU capacitive and time measurement.

TABLE 23-1: CAN1 REGISTER SUMMARY (CONTINUED)

| ess                         | Register<br>Name <sup>(1)</sup> | 0             |                          | Bits   |       |       |       |           |          |           |        |        |        |            |          |            | ·s       |                |           |

|-----------------------------|---------------------------------|---------------|--------------------------|--------|-------|-------|-------|-----------|----------|-----------|--------|--------|--------|------------|----------|------------|----------|----------------|-----------|

| Virtual Address<br>(BF88_#) |                                 | Bit Range     | 31/15                    | 30/14  | 29/13 | 28/12 | 27/11 | 26/10     | 25/9     | 24/8      | 23/7   | 22/6   | 21/5   | 20/4       | 19/3     | 18/2       | 17/1     | 16/0           | All Reset |

| B340                        |                                 | 31:16<br>15:0 | C1FIFOBA<31:0> 0000 0000 |        |       |       |       |           |          |           |        |        |        |            |          |            |          |                |           |

| P250                        | C1FIFOCONn<br>(n = 0-15)        | 31:16         | _                        | _      | _     | _     | -     | _         | _        | _         | -      | _      | _      | FSIZE<4:0> |          |            |          |                | 0000      |

| B330                        |                                 | 15:0          | _                        | FRESET | UINC  | DONLY | -     | _         | _        | _         | TXEN   | TXABAT | TXLARB | TXERR      | TXREQ    | RTREN      | TXPRI    | <1:0>          | 0000      |

| B360                        | C1FIFOINTn<br>(n = 0-15)        | 31:16         | _                        | _      | _     | _     | -     | TXNFULLIE | TXHALFIE | TXEMPTYIE | _      | _      | _      | _          | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000      |

| D300                        |                                 | 15:0          | _                        | -      | _     | -     | _     | TXNFULLIF | TXHALFIF | TXEMPTYIF | _      | _      | -      | _          | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000      |

| B370                        | C1FIFOUAn<br>(n = 0-15)         | 31:16<br>15:0 |                          |        |       |       |       |           |          | C1FIFOUA  | <31:0> |        |        |            |          |            |          |                | 0000      |

| B380                        | C1FIFOCIn                       | 31:16         | _                        | _      | _     | _     | 1     | _         | _        | _         | _      | _      | _      | _          | _        | _          | _        | 1              | 0000      |

| B380                        | (n = 0-15)                      | 15:0          | _                        | _      |       | _     | _     | _         | _        | _         | _      | _      | _      |            | C1       | FIFOCIn<4: | 0>       |                | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

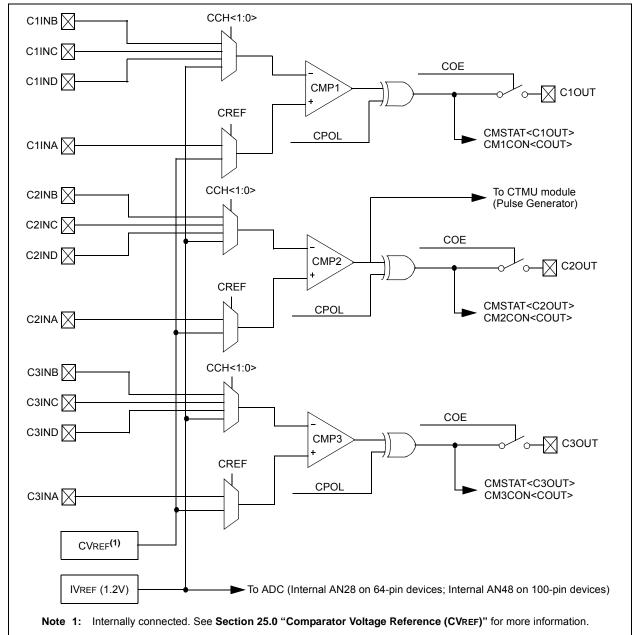

### 24.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Comparator" (DS60001110) in the "PIC32 Family Reference Manual", which is available from the Microchip web site

(www.microchip.com/PIC32).

The Analog Comparator module contains three comparators that can be configured in a variety of ways.

The following are the key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be inverted

- · Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### FIGURE 24-1: COMPARATOR BLOCK DIAGRAM

**TABLE 31-41: CTMU CURRENT SOURCE SPECIFICATIONS**

|              | DC CHAI   | RACTERISTICS                                       | Standard Operating Conditions (see Note 3):2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |       |      |       |                                  |  |  |

|--------------|-----------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----------------------------------|--|--|

| Param<br>No. | Symbol    | Characteristic                                     | Min.                                                                                                                                                                                                                                                       | Тур.  | Max. | Units | Conditions                       |  |  |

| CTMU CUR     | RENT SOUR | CE                                                 |                                                                                                                                                                                                                                                            |       |      |       |                                  |  |  |

| CTMUI1       | IOUT1     | Base Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                          | 0.55  | _    | μA    | CTMUCON<9:8> = 01                |  |  |

| CTMUI2       | IOUT2     | 10x Range <sup>(1)</sup>                           | _                                                                                                                                                                                                                                                          | 5.5   | _    | μA    | CTMUCON<9:8> = 10                |  |  |

| CTMUI3       | Іоит3     | 100x Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                          | 55    | _    | μA    | CTMUCON<9:8> = 11                |  |  |

| CTMUI4       | Iout4     | 1000x Range <sup>(1)</sup>                         | _                                                                                                                                                                                                                                                          | 550   | _    | μΑ    | CTMUCON<9:8> = 00                |  |  |

| CTMUFV1      | VF        | Temperature Diode Forward Voltage <sup>(1,2)</sup> | _                                                                                                                                                                                                                                                          | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |  |  |

|              |           |                                                    | _                                                                                                                                                                                                                                                          | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |  |  |

|              |           |                                                    | _                                                                                                                                                                                                                                                          | 0.721 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |  |  |

| CTMUFV2      | VFVR      | Temperature Diode Rate of                          | _                                                                                                                                                                                                                                                          | -1.92 | _    | mV/°C | CTMUCON<9:8> = 01                |  |  |

|              |           | Change <sup>(1,2)</sup>                            | _                                                                                                                                                                                                                                                          | -1.74 | _    | mV/°C | CTMUCON<9:8> = 10                |  |  |

|              |           |                                                    |                                                                                                                                                                                                                                                            | -1.56 |      | mV/°C | CTMUCON<9:8> = 11                |  |  |

- **Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

- 2: Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

### 32.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX/5XX 64/100-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 31.0 "40 MHz Electrical Characteristics"**, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 31.0** "**40 MHz Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX/5XX 64/100-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                              | 40°C to +85°C            |

|-----------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                         | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                          | 0.3V to +4.0V            |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)    | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 2.3V (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3) | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to Vusb3v3                             | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                         | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                           | 300 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                    | 300 mA                   |

| Maximum output current sunk by any I/O pin                                  | 15 mA                    |

| Maximum output current sourced by any I/O pin                               | 15 mA                    |

| Maximum current sunk by all ports                                           | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                               | 200 mA                   |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.