Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 28x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256ht-50i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

|          | Pin N                  | umber                    |             |                |                                                                              |  |  |  |  |  |  |

|----------|------------------------|--------------------------|-------------|----------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | Pin<br>Type | Buffer<br>Type | Description                                                                  |  |  |  |  |  |  |

| MCLR     | 7                      | 13                       | I           | ST             | Master Clear (Reset) input. This pin is an active-low Rese the device.       |  |  |  |  |  |  |

| AVDD     | 19                     | 30                       | Ρ           | Р              | Positive supply for analog modules. This pin must be connected at all times. |  |  |  |  |  |  |

| AVss     | 20                     | 31                       | Р           | Р              | Ground reference for analog modules                                          |  |  |  |  |  |  |

| Vdd      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | Ρ           | —              | Positive supply for peripheral logic and I/O pins                            |  |  |  |  |  |  |

| VCAP     | 56                     | 85                       | Р           | _              | Capacitor for Internal Voltage Regulator                                     |  |  |  |  |  |  |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | Ρ           | _              | Ground reference for logic and I/O pins                                      |  |  |  |  |  |  |

| VREF+    | 16                     | 29                       | Р           | Analog         | Analog Voltage Reference (High) Input                                        |  |  |  |  |  |  |

| VREF-    | 15                     | 28                       | Р           | Analog         | Analog Voltage Reference (Low) Input                                         |  |  |  |  |  |  |

| Legend:  | CMOS = CN              | IOS compati              | ble inpu    | it or output   | Analog = Analog input I = Input O = Output                                   |  |  |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input I = Input ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

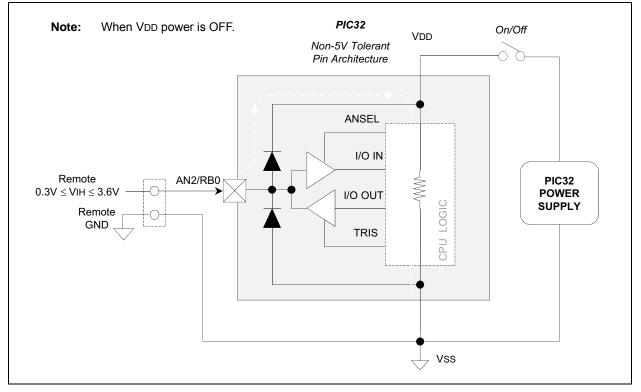

# 2.9 Considerations When Interfacing to Remotely Powered Circuits

## 2.9.1 NON-5V TOLERANT INPUT PINS

A quick review of the absolute maximum rating section in **31.0** "**40 MHz Electrical Characteristics**" will indicate that the voltage on any non-5v tolerant pin may not exceed AVDD/VDD + 0.3V. Figure 2-5 shows an example of a remote circuit using an independent power source, which is powered while connected to a PIC32 non-5V tolerant circuit that is not powered.

## FIGURE 2-5: PIC32 NON-5V TOLERANT CIRCUIT EXAMPLE

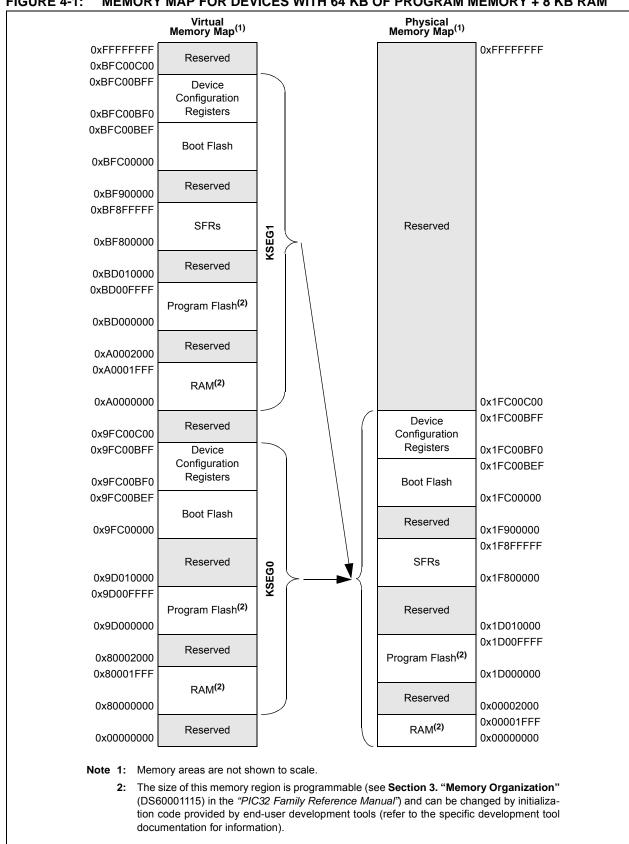

## FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 64 KB OF PROGRAM MEMORY + 8 KB RAM

## 6.1 Control Registers

## TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a     |       |                                                                                          |       |       |       |       |      | Bi        | ts      |      |      |      |      |      |      |      | 6          |

|-----------------------------|------------------------|-------|-------|------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-----------|---------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) |                        |       | 31/15 | 30/14                                                                                    | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| E400                        |                        | 31:16 | _     | —                                                                                        | —     | —     | _     |       | —    |           | —       | —    | —    | —    |      |      | —    | —    | 0000       |

| 1400                        |                        | 15:0  | WR    | WREN     WRERR     LVDERR     LVDSTAT     —     —     —     —     —     —     NVMOP<3:0> |       |       |       |       |      |           |         |      |      |      | 0000 |      |      |      |            |

| F410                        | NVMKEY                 | 31:16 |       |                                                                                          |       |       |       |       |      | NVMKE     | /<31.0> |      |      |      |      |      |      |      | 0000       |

|                             |                        | 15:0  |       |                                                                                          |       |       |       |       |      |           | 1501.02 |      |      |      |      |      |      |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16 |       |                                                                                          |       |       |       |       |      | NVMADE    | P<31.05 |      |      |      |      |      |      |      | 0000       |

| 1 420                       | NVINADDR               | 15:0  |       |                                                                                          |       |       |       |       |      | INVIVIADE | K~51.02 |      |      |      |      |      |      |      | 0000       |

| F430                        | NVMDATA                | 31:16 |       |                                                                                          |       |       |       |       |      |           | A-31.0> |      |      |      |      |      |      |      | 0000       |

| 1430                        | NVINDAIA               | 15:0  |       | NVMDATA<31:0>                                                                            |       |       |       |       |      |           |         |      |      |      | 0000 |      |      |      |            |

| F440                        | NVMSRC                 | 31:16 |       | NUMERCADDR-21105 0000                                                                    |       |       |       |       |      |           |         |      |      | 0000 |      |      |      |      |            |

| F440                        | ADDR                   | 15:0  |       | NVMSRCADDR<31:0>                                                                         |       |       |       |       |      |           |         |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

NOTES:

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | _                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | —                 | —                 | _                 | _                 |                   | —                | -                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | —                 | _                 | _                 | RDWR              | [                 | DMACH<2:0>       | •                |

## REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

## Legend:

| 0                 |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

## bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

## REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 23:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 23:10        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 0.61         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          | DMAADDR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

| TABLE 11-2: | OUTPUT PIN SELECTION |

|-------------|----------------------|

|-------------|----------------------|

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |  |  |

|----------------------|----------|-------------|----------------------------------------------|--|--|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                            |  |  |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                                  |  |  |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved              |  |  |

| RPD10                | RPD10R   | RPD10R<3:0> | 0100 = Reserved                              |  |  |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                              |  |  |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                                  |  |  |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved                              |  |  |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 - Reserved                              |  |  |

| RPB5 <sup>(7)</sup>  | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                              |  |  |

| RPC1 <sup>(3)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 = OC3                                   |  |  |

| RPD14 <sup>(3)</sup> | RPD14R   | RPD14R<3:0> | - 1100 = C1TX <sup>(5)</sup><br>1101 = C2OUT |  |  |

| RPG1 <sup>(3)</sup>  | RPG1R    | RPG1R<3:0>  | 1110 = SDO3                                  |  |  |

| RPA14 <sup>(3)</sup> | RPA14R   | RPA14R<3:0> | 1111 = SDO4 <sup>(3)</sup>                   |  |  |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                            |  |  |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                                  |  |  |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                              |  |  |

| RPD11                | RPD11R   | RPD11R<3:0> |                                              |  |  |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0101 = Reserved                              |  |  |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                                  |  |  |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                              |  |  |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 <b>= SDO1</b>                           |  |  |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                              |  |  |

| RPF3 <sup>(4)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved<br>1011 = OC4                |  |  |

| RPC4 <sup>(3)</sup>  | RPC4R    | RPC4R<3:0>  | 1100 = Reserved                              |  |  |

| RPD15 <sup>(3)</sup> | RPD15R   | RPD15R<3:0> | 1101 = C3OUT                                 |  |  |

| RPG0 <sup>(3)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 <b>=</b> SDO3                           |  |  |

| RPA15 <sup>(3)</sup> | RPA15R   | RPA15R<3:0> | 1111 = SDO4 <sup>(3)</sup>                   |  |  |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

## TABLE 11-6: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | —         | —         | _         | —     | -     |      |      | _    | —    | _    |      | —       |         | —       | —    | 0000          |

| 0200                        | /                               | 15:0      | —         | —         | —         | —         | —     | —     | —    | _    | —    | _    | —    | _    | ANSELC3 | ANSELC2 | ANSELC1 | —    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | —         | —         | —         | _     | _     | _    |      | _    |      | —    | _    | _       | _       | —       | _    | 0000          |

| 02.0                        |                                 | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | _    | —    | _    | —    | _    | —       | —       | —       | —    | F000          |

| 6220                        | PORTC                           | 31:16     | —         | —         | —         | —         | _     | _     | _    | _    | —    | _    | —    | _    | —       | _       | —       |      | 0000          |

| 0220                        | 1 on to                         | 15:0      | RC15      | RC14      | RC13      | RC12      | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | xxxx          |

| 6230                        | LATC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 0200                        | Ento                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | xxxx          |

| 6240                        | ODCC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 02.10                       | 0200                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 6250                        | CNPUC                           | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 6260                        | CNPDC                           | 31:16     |           | —         | —         | —         | —     | _     | _    | _    | —    | —    | —    |      | —       | _       | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 6270                        | CNCONC                          | 31:16     |           |           |           | _         |       |       |      |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 0270                        | oncono                          | 15:0      | ON        |           | SIDL      |           |       |       |      |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 6280                        | CNENC                           | 31:16     |           | —         |           |           |       |       |      |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | —     | _     | _    |      | —    |      | —    | _    | —       |         | —       | _    | 0000          |

| 6200                        | CNSTATC                         | 31:16     | _         | —         | —         | _         | _     |       |      |      | -    | —    | -    |      | —       |         | —       | —    | 0000          |

| 0290                        | GNOTAIC                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     |       |      |      | -    | _    |      |      | _       |         | —       | _    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

| ess                         |                                 |           |       |       |               |               |       |       |      | Bits         | 5            |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6500                        | ANSELF                          | 31:16     | _     | -     | —             | —             | _     | —     | —    | _            | -            | —            | —            | —            | —            | —            | -            | -            | 0000          |

| 0000                        | ANOLLI                          | 15:0      | —     | _     | ANSELE13      | ANSELE12      | —     | _     | _    | ANSELE8      |              | —            | _            |              |              | ANSELE2      | ANSELE1      | ANSELE0      | 3107          |

| 6510                        | TRISF                           | 31:16     | —     | _     | —             | —             | —     | —     | _    | —            | _            | —            | —            | _            |              |              | _            | _            | 0000          |

| 0010                        | TRIO                            | 15:0      | _     | -     | TRISF13       | TRISF12       | _     | —     | —    | TRISF8       | TRISF7       | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 31FF          |

| 6520                        | PORTF                           | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | _            | 0000          |

| 0020                        | 1 OKII                          | 15:0      | _     | -     | RF13          | RF12          | _     | —     | —    | RF8          | RF7          | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATE                            | 31:16     | _     | -     | —             | —             | _     | —     | _    | —            | -            | —            | —            | —            | —            | —            | _            | _            | 0000          |

| 0000                        | LAII                            | 15:0      | _     | -     | LATF13        | LATF12        | _     | —     | _    | LATF8        | LATF7        | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     | -     | —             | —             | _     | —     | _    | —            | -            | —            | —            | —            | —            | —            | _            | _            | 0000          |

| 0340                        | ODCI                            | 15:0      | _     |       | ODCF13        | ODCF12        | -     | _     | —    | ODCF8        | ODCF7        | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0330                        | CINFUI                          | 15:0      | _     |       | CNPUF13       | CNPUF12       | -     | _     | —    | CNPUF8       | CNPUF7       | CNPUF6       | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | 0000          |

| 6560                        | CNPDF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0300                        | CINF DI                         | 15:0      | _     |       | CNPDF13       | CNPDF12       | -     | _     | —    | CNPDF8       | CNPDF7       | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | —             | —             | —     | _     | _    | —            | _            | —            | _            | _            | —            | _            | -            | -            | 0000          |

| 0370                        | CINCOIN                         | 15:0      | ON    |       | SIDL          | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 6580                        | CNENF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0380                        | CINLINI                         | 15:0      | _     |       | CNIEF13       | CNIEF12       | -     | _     | —    | CNIEF8       | CNIEF7       | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | _     | _     | —             | —             | —     | _     | —    | _            |              | _            | _            | —            | _            | —            |              |              | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | _     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | _    | CN<br>STATF8 | CN<br>STATF7 | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

## TABLE 11-11: PORTF REGISTER MAP FOR PIC32MX130F128L, PIC32MX150F256L, AND PIC32MX170F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 31.24        | _                    | —                 | —                 |                   |                          | _                 | _                | _                |

| 23:16        | U-0 U-0              |                   | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 23.10        | —                    | _                 | —                 | —                 | —                        | —                 | _                | —                |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | SPISGNEXT            | _                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR           |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0            |

| 7:0          | AUDEN <sup>(1)</sup> |                   |                   |                   | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0>(1,2)      |

### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| ı' |

|----|

| ļ  |

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

## bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame Error overflow generates error events 0 = Frame Error does not generate error events bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = Receive overflow generates error events 0 = Receive overflow does not generate error events bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun Generates Error Events 0 = Transmit Underrun Does Not Generates Error Events bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions) 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data 0 = A ROV is a critical error which stop SPI operation bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions) 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty 0 = A TUR is a critical error which stop SPI operation AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup> bit 7 1 = Audio protocol enabled 0 = Audio protocol disabled bit 6-5 Unimplemented: Read as '0' AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3 1 = Audio data is mono (Each data word is transmitted on both left and right channels) 0 = Audio data is stereo bit 2 Unimplemented: Read as '0' AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0 11 = PCM/DSP mode 10 = Right Justified mode 01 = Left Justified mode  $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

U-0

U-0

\_\_\_\_

R/W-0

SMPI<3:0>

U-0

R/W-0

CSCNA

R/W-0

Bit

25/17/9/1

U-0

U-0

U-0

\_\_\_\_

R/W-0

BUFM

Bit

24/16/8/0

U-0

U-0

U-0

R/W-0

ALTS

| REGISTE      | ER 22-2. A        | DICONZ. AI        |                   |                   |                   |                   |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               |  |

| 31.24        |                   |                   |                   |                   |                   |                   |  |

U-0

R/W-0

R/W-0

#### DECISTED 22 2. AD1CON2: ADC CONTROL REGISTER 2

U-0

R/W-0

U-0

\_

VCFG<2:0>

## Legend:

23:16

15:8

7:0

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

U-0

R/W-0

OFFCAL

R/W-0

### bit 31-16 Unimplemented: Read as '0'

U-0

R/W-0

R-0

BUFS

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

- 1 = Enable Offset Calibration mode

- Positive and negative inputs of the sample and hold amplifier are connected to VREFL

- 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

#### bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each  $16^{th}$  sample/convert sequence 1110 = Interrupts at the completion of conversion for each  $15^{th}$  sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | CSSL31 <sup>(2)</sup> | CSSL30 <sup>(1)</sup> | CSSL29 <sup>(1)</sup> | CSSL28 <sup>(1)</sup> | CSSL27            | CSSL26            | CSSL25           | CSSL24           |

| 23:16        | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | CSSL23                | CSSL21                | CSSL21                | CSSL20                | CSSL19            | CSSL18            | CSSL17           | CSSL16           |

| 15.0         | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15                | CSSL14                | CSSL13                | CSSL12                | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7                 | CSSL6                 | CSSL5                 | CSSL4                 | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

## REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

## Legend:

| 0                 |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-0 CSSL<31:0>: ADC Input Pin Scan Selection bits

- 1 = Select ANx for input scan; CSSLx = ANx, where 'x' = 0-31

- 0 = Skip ANx for input scan; CSSLx = ANx, where 'x' = 0-31

- Note 1: For devices with 64 pins, CSSL28 selects IVREF (Band Gap) for scan; CSSL29 selects CTMU temperature diode for scan; and CSSL30 selects CTMU input for scan

- 2: On devices with less than 32 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

|              | REGISTER 22-0. ADTOUGE2. ADD INT OT GOAN DELEGT REGISTER 2 |                   |                   |                   |                   |                       |                       |                       |

|--------------|------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

| 31:24        | U-0                                                        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                   | U-0                   |

| 31.24        | —                                                          | —                 | —                 | —                 | —                 | —                     | —                     | —                     |

| 22:16        | U-0                                                        | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |

| 23:16        | _                                                          | —                 | _                 | _                 | —                 | CSSL50 <sup>(1)</sup> | CSSL49 <sup>(1)</sup> | CSSL48 <sup>(1)</sup> |

| 15.0         | R/W-0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                 | R/W-0                 |

| 15:8         | CSSL47                                                     | CSSL46            | CSSL45            | CSSL44            | CSSL43            | CSSL42                | CSSL41                | CSSL40                |

| 7:0          | R/W-0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                 | R/W-0                 |

| 7:0          | CSSL39                                                     | CSSL38            | CSSL37            | CSSL36            | CSSL35            | CSSL34                | CSSL33                | CSSL32                |

## REGISTER 22-6: AD1CSSL2: ADC INPUT SCAN SELECT REGISTER 2

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-19 Unimplemented: Read as '0'

- bit 18-0 CSSL<50:32>: ADC Input Pin Scan Selection bits

- 1 = Select ANx for input scan; CSSLx = ANx, where 'x' = 32-50

- 0 =Skip ANx for input scan; CSSLx = ANx, where 'x' = 32-50

- Note 1: For devices with 100 or more pins, CSSL48 selects IVREF (Band Gap) for scan; CSSL49 selects CTMU temperature diode for scan; and CSSL50 selects CTMU input for scan

**Note:** The ANx inputs in this register only support devices with 100 or more pins.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | FLTEN7            | MSEL7<1:0>        |                   |                   | FSEL7<4:0>        |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN6            | MSEL6<1:0>        |                   | FSEL6<4:0>        |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN5            | MSEL              | 5<1:0>            |                   | F                 | SEL5<4:0>         |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            | FSEL4<4:0>        |                   |                   |                  |                  |  |

## **REGISTER 23-11: C1FLTCON1: CAN FILTER CONTROL REGISTER 1**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | <b>FLTEN7:</b> Filter 7 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits<br>11111 = Reserved<br>10000 = Reserved<br>01111 = Message matching filter is stored in FIFO buffer 15<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN6: Filter 6 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

| bit 22-21 | <b>MSEL6&lt;1:0&gt;:</b> Filter 6 Mask Select bits<br>11 = Acceptance Mask 3 selected                                                                                                                |

- - 10 = Acceptance Mask 2 selected

- 01 = Acceptance Mask 1 selected

- 00 = Acceptance Mask 0 selected

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 20-16 FSEL10<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN9: Filter 9 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |  |  |  |

| 31.24        | C1FIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |  |  |  |

| 23.10        | C1FIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |  |  |  |

| 10.0         | C1FIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |  |  |

| 7:0          |                   |                   |                   | C1FIFO            | BA<7:0>           |                   |                    |                    |  |  |  |  |  |

## REGISTER 23-15: C1FIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

## Legend:

| Logonal           |                                   |                      |                    |

|-------------------|-----------------------------------|----------------------|--------------------|

| R = Readable bit  | R = Readable bit W = Writable bit |                      | read as '0'        |

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 C1FIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

## 25.1 Control Registers

## TABLE 25-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                       |                                 | Ð         |       |       |       |       |       |       |      | Bits |      |       |      |       |      |      |      |      | Ś         |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                      |                                 | 31:16     | —     | _     | _     | _     | _     | —     | —    | -    |      | _     | _    | _     | -    | _    | _    | _    | 0000      |

| 9000                      | 9800 CVRCON                     |           | ON    | _     | _     | —     |       |       | —    | _    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

## 26.1 Control Registers

## TABLE 26-1: CTMU REGISTER MAP

| ess                      |                                 | 6         |         |         |          |       |         |          |          | Bits     |         |         |                      |       |          |      |      |      | s         |

|--------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|----------------------|-------|----------|------|------|------|-----------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5                 | 20/4  | 19/3     | 18/2 | 17/1 | 16/0 | All Reset |

| 1 200                    | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |                      | EDG25 | SEL<3:0> |      |      |      | 0000      |

| A200                     | CINUCON                         | 15:0      | ON      | -       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM<5:0> IRNG<1:0> |       |          |      |      |      |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

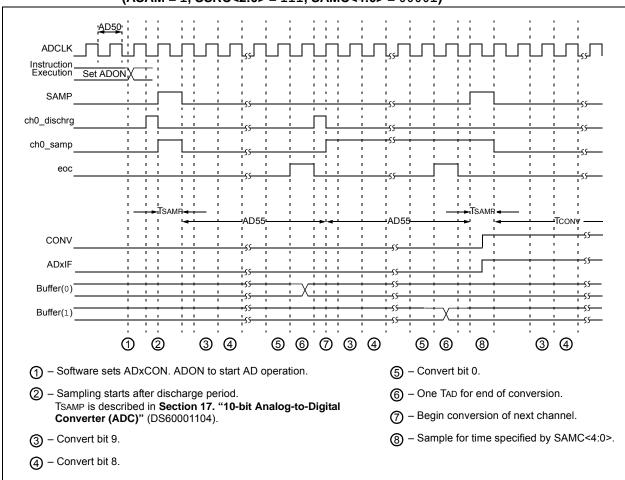

## FIGURE 31-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

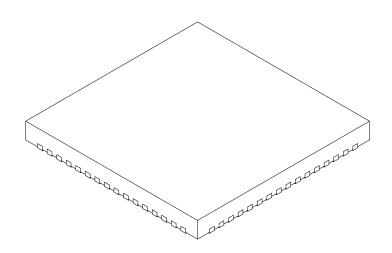

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | Ν    | <b>ILLIMETER</b> | S    |  |  |  |  |

|------------------------|--------|------|------------------|------|--|--|--|--|

| Dimension              | Limits | MIN  | NOM              | MAX  |  |  |  |  |

| Number of Pins         | Ν      |      | 64               |      |  |  |  |  |

| Pitch                  | е      |      | 0.50 BSC         |      |  |  |  |  |

| Overall Height         | Α      | 0.80 | 0.90             | 1.00 |  |  |  |  |

| Standoff               | A1     | 0.00 | 0.02             | 0.05 |  |  |  |  |

| Contact Thickness      | A3     |      | 0.20 REF         |      |  |  |  |  |

| Overall Width          | Е      |      | 9.00 BSC         |      |  |  |  |  |

| Exposed Pad Width      | E2     | 5.30 | 5.40             | 5.50 |  |  |  |  |

| Overall Length         | D      |      | 9.00 BSC         |      |  |  |  |  |

| Exposed Pad Length     | D2     | 5.30 | 5.40             | 5.50 |  |  |  |  |

| Contact Width          | b      | 0.20 | 0.25             | 0.30 |  |  |  |  |

| Contact Length         | L      | 0.30 | 0.40             | 0.50 |  |  |  |  |

| Contact-to-Exposed Pad | K      | 0.20 | -                | -    |  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2