Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32 ® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: |        | ess the docume  |            |          |

|-------|--------|-----------------|------------|----------|

|       | browse | to the docume   | ntation se | ction of |

|       | the    | Microchip       | web        | site     |

|       | (www.n | nicrochip.com). |            |          |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- · Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001123)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX/5XX 64/ 100-pin family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

# 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/<br/>DIVIDE UNIT LATENCIES AND REPEAT RATES

| Op code                 | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |  |  |  |  |  |  |  |  |

|-------------------------|--------------------------------|---------|-------------|--|--|--|--|--|--|--|--|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |  |  |  |  |  |  |  |  |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |  |  |  |  |  |  |  |  |

| MUL                     | 16 bits                        | 2       | 1           |  |  |  |  |  |  |  |  |

|                         | 32 bits                        | 3       | 2           |  |  |  |  |  |  |  |  |

| DIV/DIVU                | 8 bits                         | 12      | 11          |  |  |  |  |  |  |  |  |

|                         | 16 bits                        | 19      | 18          |  |  |  |  |  |  |  |  |

|                         | 24 bits                        | 26      | 25          |  |  |  |  |  |  |  |  |

|                         | 32 bits                        | 33      | 32          |  |  |  |  |  |  |  |  |

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX/5XX 64/100-pin devices to execute from data memory.

The key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

# 4.1 Memory Layout

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX/5XX 64/ 100-pin devices are illustrated in Figure 4-1 through Figure 4-4.

### 5.1 Interrupts Control Registers

#### TABLE 5-2: INTERRUPT REGISTER MAP

| sse                         |                                 |               |                 | Bits           |                   |                  |                  |                                            |                |                 |                   |                                   |                       |                      |                         |                         |                |                 |               |

|-----------------------------|---------------------------------|---------------|-----------------|----------------|-------------------|------------------|------------------|--------------------------------------------|----------------|-----------------|-------------------|-----------------------------------|-----------------------|----------------------|-------------------------|-------------------------|----------------|-----------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(3)</sup> | Bit Range     | 31/15           | 30/14          | 29/13             | 28/12            | 27/11            | 26/10                                      | 25/9           | 24/8            | 23/7              | 22/6                              | 21/5                  | 20/4                 | 19/3                    | 18/2                    | 17/1           | 16/0            | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _               |                | _                 | —                | _                |                                            | —              | _               | —                 | —                                 | —                     | -                    | -                       | -                       | -              | -               | 0000          |

|                             |                                 | 15:0          |                 |                | —                 | MVEC             | —                |                                            | TPC<2:0>       |                 | _                 | INT4EP INT3EP INT2EP INT1EP INT0E |                       |                      |                         | INT0EP                  | 0000           |                 |               |

| 1010                        | INTSTAT <sup>(4)</sup>          | 31:16<br>15:0 |                 |                |                   |                  | _                |                                            |                |                 |                   |                                   | _                     | _                    | <br>VEC<                | 5:0>                    | _              | _               | 0000          |

|                             |                                 | 31:16         |                 |                |                   |                  |                  |                                            |                |                 |                   |                                   |                       |                      | VLOV                    | 0.0-                    |                |                 | 0000          |

| 1020                        | IPTMR                           | 15:0          |                 |                |                   |                  |                  |                                            |                | I               | PTMR<31:0>        | >                                 |                       |                      |                         |                         |                |                 | 0000          |

| 1030                        | IFS0                            | 31:16         | FCEIF           | RTCCIF         | FSCMIF            | AD1IF            | OC5IF            | IC5IF                                      | IC5EIF         | T5IF            | INT4IF            | OC4IF                             | IC4IF                 | IC4EIF               | T4IF                    | INT3IF                  | OC3IF          | IC3IF           | 0000          |

| 1030                        | 150                             | 15:0          | IC3EIF          | T3IF           | INT2IF            | OC2IF            | IC2IF            | IC2EIF                                     | T2IF           | INT1IF          | OC1IF             | IC1IF                             | IC1EIF                | T1IF                 | INT0IF                  | CS1IF                   | CS0IF          | CTIF            | 0000          |

| 1040                        | IFS1                            | 31:16         | <b>U3RXIF</b>   | U3EIF          | I2C2MIF           | I2C2SIF          | I2C2BIF          | U2TXIF                                     | U2RXIF         | U2EIF           | SPI2TXIF          | SPI2RXIF                          | SPI2EIF               | PMPEIF               | PMPIF                   | CNGIF                   | CNFIF          | CNEIF           | 0000          |

| 1010                        |                                 | 15:0          | CNDIF           | CNCIF          | CNBIF             | CNAIF            | I2C1MIF          | I2C1SIF                                    | I2C1BIF        | U1TXIF          | U1RXIF            | U1EIF                             | SPI1TXIF              | SPI1RXIF             | SPI1EIF                 | USBIF <sup>(2)</sup>    | CMP2IF         | CMP1IF          | 0000          |

| 1050                        | IFS2                            | 31:16         | —               | —              | —                 |                  | —                | —                                          | —              | —               | _                 | (1)                               | (1)                   | —                    | SPI4TXIF <sup>(1)</sup> | SPI4RXIF <sup>(1)</sup> | -              | <b>SPI3TXIF</b> |               |

|                             |                                 | 15:0          | SPI3RXIF        | SPI3EIF        | CANIF             | CMP3IF           | DMA3IF           | DMA2IF                                     | DMA1IF         | DMA0IF          | CTMUIF            | U5TXIF <sup>(1)</sup>             | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF                  | U4RXIF                  | U4EIF          | U3TXIF          | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE<br>IC3EIE | RTCCIE<br>T3IE | FSCMIE<br>INT2IE  | AD1IE            | OC5IE            | IC5IE<br>IC2EIE                            | IC5EIE<br>T2IE | T5IE            | INT4IE            | OC4IE                             | IC4IE                 | IC4EIE<br>T1IE       | T4IE<br>INT0IE          | INT3IE                  | OC3IE          | IC3IE<br>CTIE   | 0000          |

|                             |                                 | 15:0<br>31:16 | U3RXIE          | U3EIE          | INTZIE<br>I2C2MIE | OC2IE<br>I2C2SIE | IC2IE<br>I2C2BIE | U2TXIE                                     | U2RXIE         | INT1IE<br>U2EIE | OC1IE<br>SPI2TXIE | IC1IE<br>SPI2RXIE                 | SPI2EIE               | PMPEIE               | PMPIE                   | CS1IE<br>CNGIE          | CS0IE<br>CNFIE | CITE            | 0000          |

| 1070                        | IEC1                            | 15:0          | CNDIE           | CNCIE          | CNBIE             | CNAIE            | I2C2BIE          | I2C1SIE                                    | I2C1BIE        | U1TXIE          | U1RXIE            | U1EIE                             | SPIZEIE               | SPI1RXIE             | SPI1EIE                 | USBIE <sup>(2)</sup>    | CMP2IE         | CMP1IE          | 0000          |

|                             |                                 | 31:16         | _               |                |                   |                  |                  | -                                          |                | _               |                   | _                                 |                       |                      |                         |                         | _              |                 | 0000          |

| 1080                        | IEC2                            | 15:0          | _               | _              | _                 | _                | DMA3IE           | DMA2IE                                     | DMA1IE         | DMA0IE          | CTMUIE            | U5TXIE <sup>(1)</sup>             | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE                  | U4RXIE                  | U4EIE          | U3TXIE          | 0000          |

|                             |                                 | 31:16         | _               | _              | _                 | IN               | T0IP<2:0>        |                                            | INTOIS         |                 | _                 | _                                 | _                     |                      | CS1IP<2:0>              | ,                       | CS1IS          | 6<1:0>          | 0000          |

| 1090                        | IPC0                            | 15:0          | _               | _              | _                 | CS               | S0IP<2:0>        |                                            | CSOIS          | <1:0>           |                   | _                                 | _                     |                      | CTIP<2:0>               |                         | CTIS           | <1:0>           | 0000          |

| 10A0                        | IPC1                            | 31:16         | _               | —              | —                 | IN               | T1IP<2:0>        |                                            | INT1IS         | 6<1:0>          | _                 | _                                 | _                     |                      | OC1IP<2:0>              | >                       | OC1IS          | 6<1:0>          | 0000          |

| IUAU                        | IPCT                            | 15:0          | _               | _              | —                 | IC               | 1IP<2:0>         |                                            | IC1IS          | <1:0>           | _                 | _                                 | _                     |                      | T1IP<2:0>               |                         | T1IS           | <1:0>           | 0000          |

| 10B0                        | IPC2                            | 31:16         |                 |                | —                 | IN               | T2IP<2:0>        | INT2IS<1:0> OC2IP<2:0> OC2IS<1:0>          |                |                 |                   |                                   |                       | 0000                 |                         |                         |                |                 |               |

| IUBU                        | 1602                            | 15:0          | _               | _              | —                 | IC               | 2IP<2:0>         |                                            |                |                 |                   |                                   | <1:0>                 | 0000                 |                         |                         |                |                 |               |

| 10C0                        | IPC3                            | 31:16         | _               | —              | —                 |                  | T3IP<2:0>        |                                            |                |                 |                   |                                   | 0000                  |                      |                         |                         |                |                 |               |

| 1000                        | " 00                            | 15:0          | _               |                | —                 |                  | 3IP<2:0>         | <2:0> IC3IS<1:0> — — — T3IP<2:0> T3IS<1:0> |                |                 |                   | -                                 | 0000                  |                      |                         |                         |                |                 |               |

| 10D0                        | IPC4                            | 31:16         | —               | —              | —                 |                  | T4IP<2:0>        |                                            | INT4IS         | -               | _                 | —                                 | _                     |                      | OC4IP<2:0>              | >                       | OC4IS          |                 | 0000          |

| Logor                       |                                 | 15:0          | 0 <u> </u>      |                |                   |                  |                  |                                            |                | 0000            |                   |                                   |                       |                      |                         |                         |                |                 |               |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

3: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

4: This register does not have associated CLR, SET, and INV registers.

5: This bit is only implemented on devices with a CAN module.

### 8.1 Control Registers

| TAB                         | LE 8-1:                         | : OSCILLATOR CONFIGURATION REGISTER MAP |       |                                                                                                                                                                              |         |       |         |       |          |      |         |       |       |       |                     |                       |        |       |            |

|-----------------------------|---------------------------------|-----------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|---------|-------|----------|------|---------|-------|-------|-------|---------------------|-----------------------|--------|-------|------------|

| ess                         |                                 | 0                                       |       |                                                                                                                                                                              |         |       |         |       |          |      | Bits    |       |       |       |                     |                       |        |       | s          |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range                               | 31/15 | 30/14                                                                                                                                                                        | 29/13   | 28/12 | 27/11   | 26/10 | 25/9     | 24/8 | 23/7    | 22/6  | 21/5  | 20/4  | 19/3                | 18/2                  | 17/1   | 16/0  | All Resets |

| F000                        | OSCCON                          | 31:16                                   | _     | —                                                                                                                                                                            | PI      |       |         |       |          |      |         |       |       |       | x1xx <sup>(2)</sup> |                       |        |       |            |

| F000                        | USCCON .                        | 15:0                                    | —     |                                                                                                                                                                              | COSC<2: | 0>    | —       |       | NOSC<2:0 | >    | CLKLOCK | ULOCK | SLOCK | SLPEN | CF                  | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx(2)    |

| F010                        | OSCTUN                          | 31:16                                   | _     | _                                                                                                                                                                            | _       | —     | _       | _     | —        | _    | —       | —     | _     | _     |                     | —                     | _      | —     | 0000       |

| 1010                        | 030101                          | 15:0                                    | —     |                                                                                                                                                                              |         | _     | —       | _     | —        | —    | _       | _     |       |       | TUT                 | N<5:0>                |        |       | 0000       |

| 5000                        | REFOCON                         | 31:16                                   | —     |                                                                                                                                                                              |         |       |         |       |          |      | RODIV<  | 14:0> |       |       |                     |                       |        |       | 0000       |

| F020                        | REFUCUN                         | 15:0                                    | ON    | ON         —         SIDL         OE         RSLP         —         DIVSWEN         ACTIVE         —         —         —         —         P         ROSEL<3:0>         0000 |         |       |         |       |          |      |         |       |       |       |                     |                       |        |       |            |

| 5000                        | REFOTRIM                        | 31:16                                   |       |                                                                                                                                                                              |         |       | ROTRIM< | 8:0>  |          |      |         | -     | _     | _     | —                   | —                     | —      | —     | 0000       |

| F030                        |                                 | 15:0                                    | _     | _                                                                                                                                                                            | -       | _     | —       | _     | _        | _    | —       | _     | _     | _     | _                   | —                     | _      | —     | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on devices with a USB module.

.....

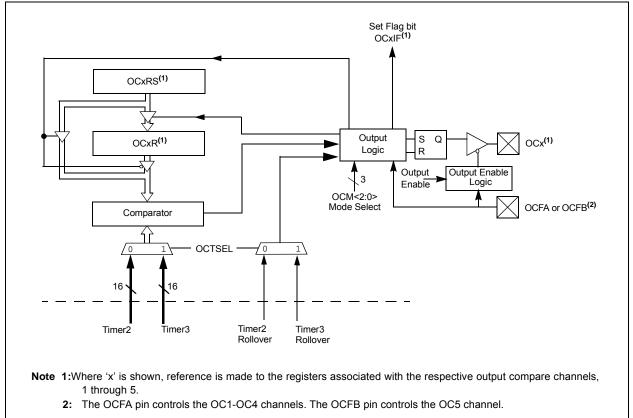

### 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are the key features of this module:

- · Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

#### FIGURE 16-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| REGIST  | ER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                                  |

| bit 7-6 | <pre>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 =Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</pre> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                   |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                     |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                            |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                         |

| bit 1   | <b>OERR:</b> Receive Buffer Overrun Error Status bit.<br>This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.<br>1 = Receive buffer has overflowed                                                                                                                                                                                     |

|         | 0 = Receive buffer has not overflowed                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                    |

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                      | _                      | _                 |                   | -                 | _                 | -                | —                |

| 22:16        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                      | —                      | _                 | _                 | _                 | _                 | _                | —                |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | WCS2 <sup>(1)</sup>    | WCS1 <sup>(3)</sup>    |                   |                   |                   | 2 < 1 2 . 0 >     |                  |                  |

|              | WADDR15 <sup>(2)</sup> | WADDR14 <sup>(4)</sup> |                   |                   | WADDF             | <<13:8>           |                  |                  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                        |                        |                   | WADDR<            | 7:0>              |                   |                  |                  |

#### REGISTER 20-8: PMWADDR: PARALLEL PORT WRITE ADDRESS REGISTER

#### Legend:

| Logonal           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

- bit 31-16 Unimplemented: Read as '0'

- bit 15 WCS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 WADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 WCS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 WADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 WADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

### 23.1 Control Registers

#### TABLE 23-1: CAN1 REGISTER SUMMARY

| ess                         |                                 |               |              |                                                                      |              |                                             |          |              |           | Bit       | 5       |                   |             |                 |          |            |         |         |            |  |

|-----------------------------|---------------------------------|---------------|--------------|----------------------------------------------------------------------|--------------|---------------------------------------------|----------|--------------|-----------|-----------|---------|-------------------|-------------|-----------------|----------|------------|---------|---------|------------|--|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14                                                                | 29/13        | 28/12                                       | 27/11    | 26/10        | 25/9      | 24/8      | 23/7    | 22/6              | 21/5        | 20/4            | 19/3     | 18/2       | 17/1    | 16/0    | All Resets |  |

|                             | 01001                           | 31:16         | _            | _                                                                    | _            | _                                           | ABAT     | F            | REQOP<2:0 | >         | (       | OPMOD<2:0         | >           | CANCAP          | _        | _          | _       | _       | 0480       |  |

| B000                        | C1CON                           | 15:0          | ON           | _                                                                    | SIDLE        |                                             | CANBUSY  | —            | _         | _         | -       | _                 | _           |                 | D        | DNCNT<4:0> |         |         | 0000       |  |

| B010                        | C1CFG                           | 31:16         | _            | _                                                                    |              |                                             |          |              |           |           |         |                   |             | — — SEG2PH<2:0> |          |            |         | 0000    |            |  |

| 8010                        | CICFG                           | 15:0          | SEG2PHTS     |                                                                      |              |                                             |          |              |           |           |         |                   |             |                 | BRP<5:0> |            |         |         | 0000       |  |

| B020                        | C1INT                           | 31:16         | IVRIE        | RIE WAKIE CERRIE SERRIE RBOVIE — — — — — — MODIE CTMRIE RBIE TBIE 00 |              |                                             |          |              |           |           |         |                   |             | 0000            |          |            |         |         |            |  |

| 0020                        | 01111                           | 15:0          | IVRIF        | RIF WAKIF CERRIF SERRIF RBOVIF — — — — — — — —                       |              |                                             |          |              |           |           |         |                   | MODIF       | CTMRIF          | RBIF     | TBIF       | 0000    |         |            |  |

| B030                        | C1VEC                           | 31:16         | —            | —                                                                    | —            | —                                           | —        | _            | —         | —         | _       | —                 | —           | —               | —        | —          | —       | —       | 0000       |  |

| 2000                        |                                 | 15:0          | —            |                                                                      |              |                                             |          |              |           |           |         |                   |             | 0040            |          |            |         |         |            |  |

| B040                        | C1TREC                          | 31:16         | —            | _                                                                    | _            | —                                           | _        | _            | —         | —         | —       | _                 | TXBO        | TXBP            | RXBP     | TXWARN     | RXWARN  | EWARN   | 0000       |  |

|                             |                                 | 15:0          |              |                                                                      |              |                                             |          |              |           |           |         |                   |             | 0000            |          |            |         |         |            |  |

| B050                        | C1FSTAT                         | 31:16         | -            | -                                                                    | -            | -                                           | -        | -            | -         | -         | -       | -                 | -           | -               | -        | -          | -       | -       | 0000       |  |

|                             |                                 | 15:0          | FIFOIP15     | FIFOIP14                                                             | FIFOIP13     | FIFOIP12                                    | FIFOIP11 | FIFOIP10     | FIFOIP9   | FIFOIP8   | FIFOIP7 | FIFOIP6           | FIFOIP5     | FIFOIP4         | FIFOIP3  | FIFOIP2    | FIFOIP1 | FIFOIP0 | 0000       |  |

| B060                        | C1RXOVF                         | 31:16<br>15:0 | —<br>RXOVF15 | —<br>RXOVF14                                                         | –<br>RXOVF13 |                                             |          |              |           |           |         |                   | —<br>RXOVF4 | –<br>RXOVF3     | RXOVF2   | RXOVF1     | RXOVF0  | 0000    |            |  |

|                             |                                 | 31:16         | KAUVE 15     | KAUVF14                                                              | RAUVEIS      | RAUVE 12                                    | RXOVF11  | RXOVF10      | RXOVF9    | CANTS<    |         | RXOVF6            | RXOVF5      | KAUVF4          | RAUVES   | RAUVEZ     | RAUVEI  | RAUVFU  | 0000       |  |

| B070                        | C1TMR                           | 15:0          |              |                                                                      |              |                                             |          |              | CA        | NTSPRE<15 |         |                   |             |                 |          |            |         |         |            |  |

|                             |                                 | 31:16         |              |                                                                      |              |                                             |          | SID<10:0>    | 0A        |           | 05      |                   |             |                 | MIDE     | _          | EID<1   | 7.16>   | 0000       |  |

| B080                        | C1RXM0                          | 15:0          |              |                                                                      |              |                                             |          | 012 110.0    |           | EID<1     | 5.0>    |                   |             |                 | MIDE     |            |         | 7.10    | XXXX       |  |

|                             |                                 | 31:16         |              |                                                                      |              |                                             |          | SID<10:0>    |           |           | 5.0     |                   |             |                 | MIDE     |            | EID<1   | 7.16>   | xxxx       |  |

| B090                        | C1RXM1                          | 15:0          |              |                                                                      |              |                                             |          | 0.0 10.0     |           | EID<1     | 5.0>    |                   |             |                 |          |            | 2.0     |         | XXXX       |  |

|                             |                                 | 31:16         |              |                                                                      |              |                                             |          | SID<10:0>    |           | 210 11    |         |                   |             |                 | MIDE     | _          | EID<1   | 7.16>   | xxxx       |  |

| B0A0                        | C1RXM2                          | 15:0          |              |                                                                      |              |                                             |          | 0.0 10.0     |           | EID<1     | 5:0>    |                   |             |                 |          |            | 2.0     |         | XXXX       |  |

|                             |                                 | 31:16         |              |                                                                      |              |                                             |          | SID<10:0>    |           |           |         |                   |             |                 | MIDE     | _          | EID<1   | 7:16>   | xxxx       |  |

| B0B0                        | C1RXM3                          | 15:0          |              |                                                                      |              |                                             |          |              |           | EID<1     | 5:0>    |                   |             |                 |          |            | ļ       |         | xxxx       |  |

|                             |                                 | 31:16         | FLTEN3       | MSEL                                                                 | 3<1:0>       |                                             |          | FSEL3<4:0>   | >         |           | FLTEN2  | MSEL              | 2<1:0>      |                 | F        | SEL2<4:0>  |         |         | 0000       |  |

| B0C0                        | C1FLTCON0                       | 15:0          | FLTEN1       | MSEL                                                                 | 1<1:0>       |                                             |          | FSEL1<4:0>   | >         |           | FLTEN0  | MSEL              | 0<1:0>      |                 | F        | SEL0<4:0>  |         |         | 0000       |  |

|                             | 0.151 700114                    | 31:16         | FLTEN7       | MSEL                                                                 |              |                                             |          |              |           |           |         |                   | 0000        |                 |          |            |         |         |            |  |

| B0D0                        | C1FLTCON1                       | 15:0          | FLTEN5       | MSEL                                                                 | 5<1:0>       | :0> FSEL5<4:0> FLTEN4 MSEL4<1:0> FSEL4<4:0> |          |              |           |           |         |                   |             |                 | 0000     |            |         |         |            |  |

| DOFO                        |                                 | 31:16         | FLTEN11      | MSEL <sup>2</sup>                                                    | 11<1:0>      |                                             |          | FSEL11<4:0   | >         |           | FLTEN10 | MSEL <sup>2</sup> | 10<1:0>     |                 | F        | SEL10<4:0> | •       |         | 0000       |  |

| B0E0                        | C1FLTCON2                       | 15:0          | FLTEN9       | MSEL                                                                 | 9<1:0>       |                                             |          | FSEL9<4:0>   | <b>`</b>  |           | FLTEN8  | MSEL              | 8<1:0>      |                 | F        | SEL8<4:0>  |         |         | 0000       |  |

| B0F0                        | C1FLTCON3                       | 31:16         | FLTEN15      | MSEL1                                                                | 15<1:0>      |                                             |          | FSEL15<4:0   | >         |           | FLTEN14 | MSEL'             | 14<1:0>     |                 | F        | SEL14<4:0> | •       |         | 0000       |  |

| BUFU                        | GIFLI CONS                      | 15:0          | FLTEN13      | MSEL1                                                                | 13<1:0>      |                                             |          | FSEL13<4:0   | >         |           | FLTEN12 | MSEL'             | 12<1:0>     |                 | F        | SEL12<4:0> | ·       |         | 0000       |  |

| B140                        | Onoan                           | 31:16         |              |                                                                      |              |                                             |          | SID<10:0>    |           |           |         |                   |             |                 | EXID     |            | EID<1   | 7:16>   | xxxx       |  |

| 040                         | (n = 0-15)                      | 15:0          |              |                                                                      |              |                                             |          | aa ara ahawr |           | EID<1     | 5:0>    |                   |             |                 |          |            |         |         | xxxx       |  |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### 25.1 Control Registers

# TABLE 25-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                       |                                 | a         |       | Bits  |       |       |       |       |      |      |      |       |      |       |      | s    |      |      |           |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                      | CVRCON                          | 31:16     |       | -     | _     | —     | _     | -     | _    | _    |      | _     | -    | —     | -    | -    | -    | -    | 0000      |

| 9000                      | CVRCON                          | 15:0      | ON    | —     | _     | —     | —     | _     |      | _    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

# 28.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-up Timer" (DS60001114), Section 32. "Configuration" (DS60001124) and Section 33. "Programming and Diagnostics" (DS60001129) in the "PIC32 Family Reference Manual", which are available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- Flexible device configuration

- Watchdog Timer (WDT)

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

### 28.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- CFGCON: Configuration Control Register

In addition, the DEVID register (Register 28-6) provides device and revision information.

#### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 **FCKSM<1:0>:** Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator disabled

- 10 = HS Oscillator mode selected

- 01 = XT Oscillator mode selected

- 00 = External Clock mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |  |  |  |

| 31:24        |                       | _                 | _                 | —                 | —                 | _                 | _                | —                |  |  |  |  |  |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |  |  |  |

| 23:16        |                       | _                 |                   | —                 | —                 | FF                | PLLODIV<2:0      | )>               |  |  |  |  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |  |  |  |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | —                 | —                 | UPLLIDIV<2:0>(1)  |                  |                  |  |  |  |  |  |

| 7.0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |  |  |  |  |  |

| 7:0          | _                     | F                 | PLLMUL<2:0        | >                 | —                 | F                 | PLLIDIV<2:0      | >                |  |  |  |  |  |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 28-3:**

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 6-4

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1' FPLLMUL<2:0>: PLL Multiplier bits 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is available on PIC32MX2XX/5XX devices only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |

|              | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 | _                 | _                 | -                 | _                 | -                | _                |

| 15:8         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

|              | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

|              | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |

#### REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bi  | it                 |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Unimplemented: Read as '0'

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| AC CHARACTERISTICS |                                                     |                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |       |      |       |            |

|--------------------|-----------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | <sup>n.</sup> Symbol Characteristics <sup>(1)</sup> |                                                                      | Min.                                                                                                                                                                                                                                                                              | Тур.  | Max. | Units | Conditions |

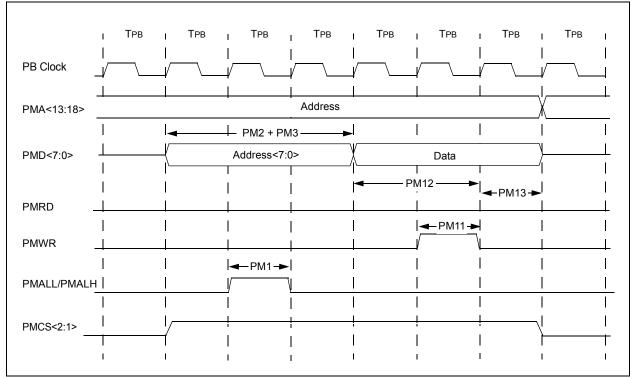

| PM1                | TLAT                                                | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                                                   | 1 Трв |      | _     | _          |

| PM2                | Tadsu                                               | Address Out Valid to PMALL/<br>PMALH Invalid (address setup time)    | _                                                                                                                                                                                                                                                                                 | 2 Трв | _    | —     | _          |

| PM3                | Tadhold                                             | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                                 | 1 Трв | _    | —     |            |

| PM4                | Tahold                                              | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                                 | _     | _    | ns    | _          |

| PM5                | Trd                                                 | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                                 | 1 Трв | _    | _     | _          |

| PM6                | TDSU                                                | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                                | —     | _    | ns    | _          |

| PM7                | TDHOLD                                              | PMRD or PMENB Inactive to<br>Data In Invalid (data hold time)        | —                                                                                                                                                                                                                                                                                 | 80    | _    | ns    | _          |

#### TABLE 31-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

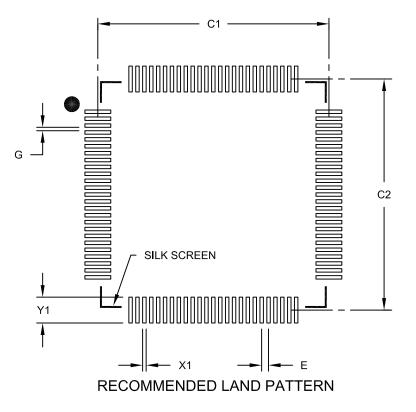

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |

|---------------------------|-------------|------|----------|------|

| Dimension                 | MIN         | NOM  | MAX      |      |

| Contact Pitch             | E           |      | 0.40 BSC |      |

| Contact Pad Spacing       | C1          |      | 13.40    |      |

| Contact Pad Spacing       | C2          |      | 13.40    |      |

| Contact Pad Width (X100)  | X1          |      |          | 0.20 |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |

| Distance Between Pads     | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

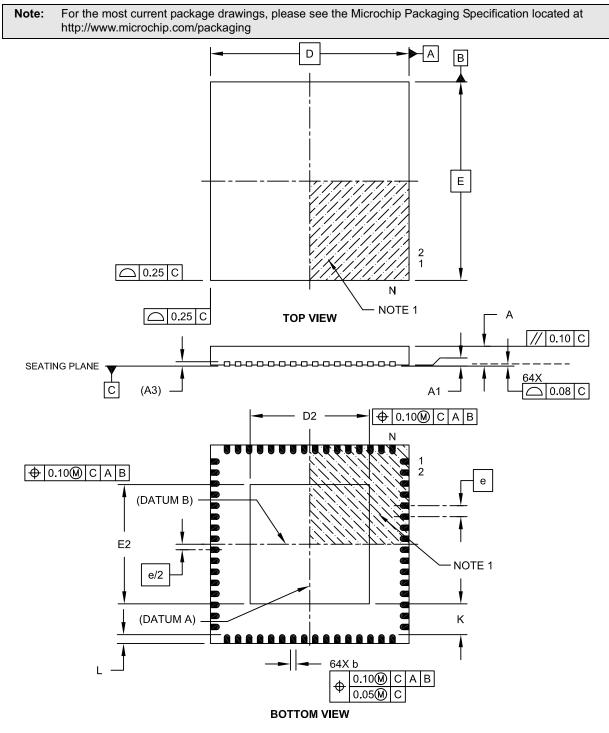

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE