Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256ht-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

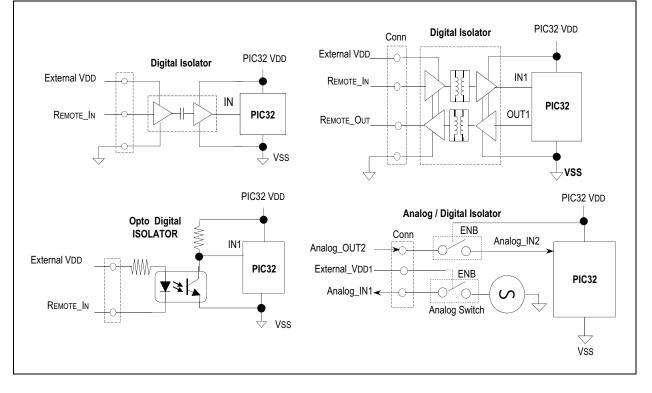

Without proper signal isolation, on non-5V tolerant pins, the remote signal can power the PIC32 device through the high side ESD protection diodes. Besides violating the absolute maximum rating specification when VDD of the PIC32 device is restored and ramping up or ramping down, it can also negatively affect the internal Power-on Reset (POR) and Brown-out Reset (BOR) circuits, which can lead to improper initialization of internal PIC32 logic circuits. In these cases, it is recommended to implement digital or analog signal isolation as depicted in Figure 2-6, as appropriate. This is indicative of all industry microcontrollers and not just Microchip products.

# TABLE 2-1: EXAMPLES OF DIGITAL/ ANALOG ISOLATORS WITH OPTIONAL LEVEL TRANSLATION

| Example Digital/Analog<br>Signal Isolation Circuits | Inductive Coupling | Capacitive Coupling | Opto Coupling | Analog/Digital Switch |

|-----------------------------------------------------|--------------------|---------------------|---------------|-----------------------|

| ADuM7241 / 40 ARZ (1 Mbps)                          | Х                  |                     | _             |                       |

| ADuM7241 / 40 CRZ (25 Mbps)                         | Х                  |                     |               | _                     |

| IS0721                                              |                    | Х                   |               | _                     |

| LTV-829S (2 Channel)                                | _                  |                     | Х             | _                     |

| LTV-849S (4 Channel)                                | _                  |                     | Х             | _                     |

| FSA266 / NC7WB66                                    | _                  |                     |               | Х                     |

# FIGURE 2-6: DIGITAL/ANALOG SIGNAL ISOLATION CIRCUITS

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Name        | Function                                                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| HWREna                  | Enables access via the RDHWR instruction to selected hardware registers.                                                                                              |

| BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.                                                                                                    |

| Count <sup>(1)</sup>    | Processor cycle count.                                                                                                                                                |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Compare <sup>(1)</sup>  | Timer interrupt control.                                                                                                                                              |

| Status <sup>(1)</sup>   | Processor status and control.                                                                                                                                         |

| IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                                                                                                                  |

| Cause <sup>(1)</sup>    | Cause of last general exception.                                                                                                                                      |

| EPC <sup>(1)</sup>      | Program counter at last exception.                                                                                                                                    |

| PRId                    | Processor identification and revision.                                                                                                                                |

| EBASE                   | Exception vector base register.                                                                                                                                       |

| Config                  | Configuration register.                                                                                                                                               |

| Config1                 | Configuration register 1.                                                                                                                                             |

| Config2                 | Configuration register 2.                                                                                                                                             |

| Config3                 | Configuration register 3.                                                                                                                                             |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Debug <sup>(2)</sup>    | Debug control and exception status.                                                                                                                                   |

| DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                                                                                                              |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| ErrorEPC <sup>(1)</sup> | Program counter at last error.                                                                                                                                        |

| DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                                                                                                                    |

|                         | NameReservedHWREnaBadVAddr(1)Count(1)ReservedCompare(1)Status(1)IntCtl(1)Cause(1)EPC(1)PRIdEBASEConfigConfig1Config2Config3ReservedDebug(2)DEPC(2)ReservedErrorEPC(1) |

| TABLE 3-2. COPROCESSOR UREGISTERS | <b>TABLE 3-2:</b> | <b>COPROCESSOR 0 REGISTERS</b> |

|-----------------------------------|-------------------|--------------------------------|

|-----------------------------------|-------------------|--------------------------------|

Note 1: Registers used in exception processing.

**2:** Registers used during debug.

# 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX1XX/2XX/5XX 64/100-pin devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX1XX/2XX/5XX 64/100-pin devices, the Flash page size is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| ess                         |                                 |               |        |       |       |       |        |       |      | Bi     | ts      |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                        | DCH0CON                         | 31:16<br>15:0 |        | —     | —     | _     | —      | —     | —    |        |         |        |        |        | —       |        |        | -      | 00         |

|                             |                                 | 31:16         |        |       |       |       |        |       |      |        |         |        | 00     |        |         |        |        |        |            |

| 3070                        | DCH0ECON                        | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN |         |        | _      | _      | FF         |

|                             |                                 | 31:16         | _      | _     | —     | _     | _      | _     | _    | _      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 00         |

| 3080                        | DCH0INT                         | 15:0          | _      | _     | _     | _     | _      | _     |      |        | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 00         |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        | •       |        |        |        | 00         |

| 30A0                        | DCH0DSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 00         |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _       | _      | _      | _      | 00         |

| 30B0                        | DCH0SSIZ                        | 15:0          |        |       |       |       |        |       |      | CHSSIZ | Z<15:0> |        |        |        |         |        |        |        | 0.0        |

| 2000                        | DCH0DSIZ                        | 31:16         | _      | —     | _     | —     | _      | _     |      | _      | _       | _      | _      | _      | _       | _      | —      | _      | 00         |

| 5000                        | DCHUD3IZ                        | 15:0          |        |       |       |       |        |       |      | CHDSIZ | Z<15:0> |        |        |        |         |        |        |        | 00         |

| 3000                        | DCH0SPTR                        | 31:16         | —      | _     |       | —     | _      | _     | —    | -      | _       | —      |        |        | _       | —      | _      |        | 00         |

| 0000                        | Donioor III                     | 15:0          |        |       |       |       |        |       |      | CHSPTI | R<15:0> |        |        |        |         |        |        |        | 00         |

| 30E0                        | DCH0DPTR                        | 31:16         | —      | _     | —     | —     | —      | —     | —    |        | _       | —      |        | —      | —       | —      | _      | _      | 00         |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHDPTI | R<15:0> |        |        |        |         |        |        |        | 00         |

| 30F0                        | DCH0CSIZ                        | 31:16         | —      |       | —     | —     | —      | —     |      |        | -       |        | —      | —      |         | —      | _      | _      | 00         |

|                             |                                 | 15:0          |        |       |       |       | _      |       |      | CHCSIZ | 2<15:0> | _      |        | _      |         |        |        |        | 00         |

| 3100                        | DCH0CPTR                        | 31:16<br>15:0 | —      |       |       |       | _      |       |      | CHCPTI |         |        |        |        | _       | —      | _      |        | 00         |

|                             |                                 | 31:16         |        | _     | _     | _     | _      | _     | _    |        |         | _      | _      |        |         | _      | _      | _      | 00         |

| 3110                        | DCH0DAT                         | 15:0          | _      | _     | _     | _     | _      | _     | _    | _      |         |        |        |        | AT<7:0> |        |        |        | 00         |

|                             |                                 | 31:16         | _      | _     | _     |       | _      | _     |      | _      | _       | —      | —      | _      | _       | _      | _      | _      | 00         |

| 3120                        | DCH1CON                         | 15:0          | CHBUSY | _     | _     | _     | _      | _     | _    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | <1:0>  | 00         |

| 0400                        | DOLUEDON                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | -      |         |        |        | CHAIR  | Q<7:0>  |        |        |        | 00         |

| 3130                        | DCH1ECON                        | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | _      | —      | —      | FF         |

| 3140                        | DCH1INT                         | 31:16         |        | _     |       | _     | _      |       |      | _      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 00         |

| 5140                        | DCHIINI                         | 15:0          | —      |       | —     | _     | _      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 00         |

| 3150                        | DCH1SSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |         |        |        |        | 00         |

| 3160                        | DCH1DSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 00         |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

# REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

|              |                           |                   | -                 |                   |                   |                   |                  |                       |

|--------------|---------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

| 04.04        | U-0                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        | —                         | —                 | —                 | _                 | —                 | _                 | _                | _                     |

| 00.40        | U-0                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                         | —                 | —                 | _                 | —                 | —                 | _                | —                     |

| 45.0         | R/W-0                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY                    | _                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> CHAED |                   | CHCHN             | CHAEN             | —                 | CHEDET            | CHPF             | RI<1:0>               |

# REGISTER 9-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

# Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

# bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

# bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

## bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

# bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

# TABLE 11-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(3)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0101 = Reserved                              |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 <b>= SDO1</b>                           |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(3)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(3)</sup> | RPD12R   | RPD12R<3:0> | 1011 = OC5<br>1100 = Reserved                |

| RPF8 <sup>(3)</sup>  | RPF8R    | RPF8R<3:0>  | 1101 = C1OUT                                 |

| RPC3 <sup>(3)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 <b>=</b> <del>SS3</del>                 |

| RPE9 <sup>(3)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = SS4 <sup>(3)</sup>                    |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(3)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(1)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(2)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(3)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(3)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(3)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(1)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

# REGISTER 13-1: TxCON: TYPE B TIMER 'x' CONTROL REGISTER (CONTINUED)('x' = 2 THROUGH 5)

- bit 3 **T32:** 32-Bit Timer Mode Select bit<sup>(2)</sup> 1 = Odd numbered and even numbered timers form a 32-bit timer 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:10        | —                 | _                 | _                 | —                    | _                 | _                 | _                | —                |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | —                |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            | OCM<2:0>          |                  |                  |  |  |

# **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

# bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

# **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

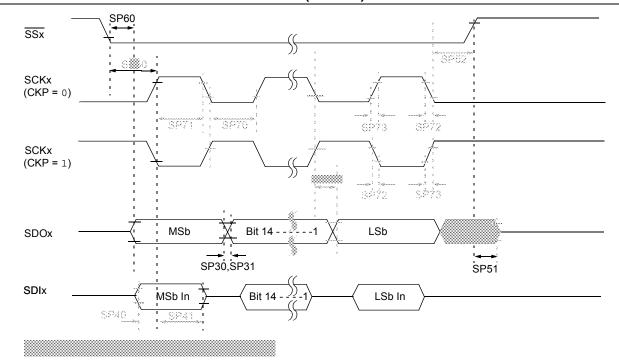

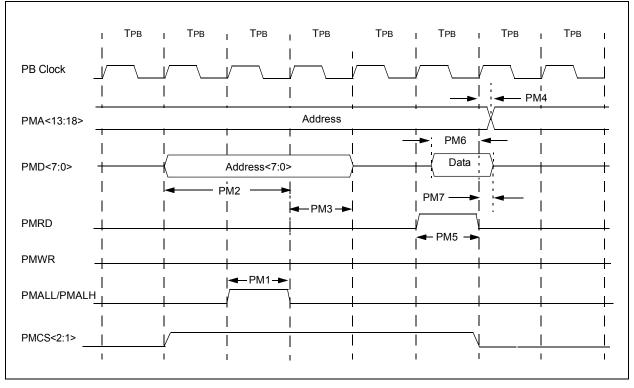

#### **Control Registers** 17.1

# TABLE 17-1: SPI1 THROUGH SPI4 REGISTER MAP

| ess                         |                                 | <i>a</i>      |               |              |           |              |                |              |             | Bi         | ts      |        |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|---------------|---------------|--------------|-----------|--------------|----------------|--------------|-------------|------------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14        | 29/13     | 28/12        | 27/11          | 26/10        | 25/9        | 24/8       | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16         | FRMEN         | FRMSYNC      | FRMPOL    | MSSEN        | FRMSYPW        | FF           | RMCNT<2:0   | )>         | MCLKSEL | —      | —      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5000                        | SITICON                         | 15:0          | ON            | —            | SIDL      | DISSDO       | MODE32         | MODE16       | SMP         | CKE        | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5810                        | SPI1STAT                        | 31:16         | _             | —            | —         |              |                | UFELM<4:     | 0>          |            | —       | —      | —      |          |             | BUFELM<4 |        |         | 0000       |

| 3010                        | 011101/1                        | 15:0          |               | —            | —         | FRMERR       | SPIBUSY        |              | —           | SPITUR     | SRMT    | SPIROV | SPIRBE | —        | SPITBE      |          | SPITBF | SPIRBF  | 19EB       |

| 5820                        | SPI1BUF                         | 31:16<br>15:0 |               | DATA<31:0>   |           |              |                |              |             |            |         |        |        |          | 0000        |          |        |         |            |

| 5830                        | SPI1BRG                         | 31:16         | _             | _            | —         | —            | —              | —            | —           | —          | —       | —      | —      | —        | —           | —        | —      | _       | 0000       |

| 5630                        | SFIIDKG                         | 15:0          |               | -            | _         | _            | —              | _            | -           |            |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |               | —            | —         |              | —              |              |             |            | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5840                        | SPI1CON2                        | 15:0          | SPI<br>SGNEXT | —            | _         | FRM<br>ERREN | SPI<br>ROVEN   | SPI<br>TUREN | IGNROV      | IGNTUR     | AUDEN   | —      | _      | _        | AUD<br>MONO | -        | AUDMO  | )D<1:0> | 0000       |

| 5A00                        | SPI2CON                         | 31:16         | FRMEN         | FRMSYNC      | FRMPOL    | MSSEN        | FRMSYPW        | FF           | RMCNT<2:0   | )>         | MCLKSEL | _      | _      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 0112001                         | 15:0          | ON            | —            | SIDL      | DISSDO       | MODE32         | MODE16       | SMP         | CKE        | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5A10                        | SPI2STAT                        | 31:16         |               | —            | —         |              |                | UFELM<4:     | 0>          |            | —       | —      | —      |          | TX          | BUFELM<4 |        | -       | 0000       |

| 5410                        | 01 120 17 11                    | 15:0          | _             | —            | —         | FRMERR       | SPIBUSY        | —            | —           | SPITUR     | SRMT    | SPIROV | SPIRBE | _        | SPITBE      | —        | SPITBF | SPIRBF  | 19EB       |

| 5A20                        | SPI2BUF                         | 31:16<br>15:0 |               |              |           |              |                |              |             | DATA<      | 31:0>   |        |        |          |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16         |               | —            | —         |              | —              |              |             |            | _       | —      | _      |          |             |          | _      | _       | 0000       |

| 5A30                        |                                 | 15:0          | -             | —            | —         | -            | —              | —            | _           |            |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |               | —            | —         |              | —              |              |             |            | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0          | SPI<br>SGNEXT | —            | _         | FRM<br>ERREN | SPI<br>ROVEN   | SPI<br>TUREN | IGNROV      | IGNTUR     | AUDEN   | —      | _      | _        | AUD<br>MONO | -        | AUDMO  | )D<1:0> | 0000       |

| 5000                        | SPI3CON                         | 31:16         | FRMEN         | FRMSYNC      | FRMPOL    | MSSEN        | FRMSYPW        | FF           | RMCNT<2:(   | )>         | MCLKSEL | —      | _      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5C00                        | SPISCON                         | 15:0          | ON            | —            | SIDL      | DISSDO       | MODE32         | MODE16       | SMP         | CKE        | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5010                        | SPI3STAT                        | 31:16         |               | -            | _         |              | RXB            | UFELM<4:     | 0>          |            | —       | _      | —      |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5C10                        | 3F 133 IAI                      | 15:0          | -             | —            | —         | FRMERR       | SPIBUSY        |              | -           | SPITUR     | SRMT    | SPIROV | SPIRBE | -        | SPITBE      |          | SPITBF | SPIRBF  | 19EB       |

| 5C20                        | SPI3BUF                         | 31:16<br>15:0 |               |              |           |              |                |              |             | DATA<      | 31:0>   |        |        |          |             |          |        |         | 0000       |

|                             |                                 | 31:16         | _             | —            | —         | _            | —              | —            | —           | —          | —       | —      | —      | —        | —           | _        | —      | _       | 0000       |

| 5C30                        | SPI3BRG                         | 15:0          | _             | _            | —         | _            | _              | _            | _           |            |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

| Legen                       | <b>d:</b> x = un                | known         | value on F    | Reset; — = ı | unimpleme | nted, read a | s '0'. Reset v | alues are s  | shown in he | xadecimal. |         |        |        |          |             |          |        |         | •          |

All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Note 1: Registers" for more information.

2: This register is only available on 100-pin devices.

|              |                                                                                                                                               | PIxCON: SF                                                                                                                                                      |                                                                                                                |                                                                                                   |                                                                                  | D:/               | <b>D</b> **      | D:"                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                             | Bit<br>30/22/14/6                                                                                                                                               | Bit<br>29/21/13/5                                                                                              | Bit<br>28/20/12/4                                                                                 | Bit<br>27/19/11/3                                                                | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 31.24        | FRMEN                                                                                                                                         | FRMSYNC                                                                                                                                                         | FRMPOL                                                                                                         | MSSEN                                                                                             | FRMSYPW                                                                          | F                 | RMCNT<2:0        | )>                   |

| 23:16        | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | U-0                                                                                                            | U-0                                                                                               | U-0                                                                              | U-0               | R/W-0            | R/W-0                |

| 23.10        | MCLKSEL <sup>(2)</sup>                                                                                                                        | _                                                                                                                                                               | _                                                                                                              | —                                                                                                 | _                                                                                | —                 | SPIFE            | ENHBUF <sup>(2</sup> |

| 15:8         | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 15.0         | ON <sup>(1)</sup>                                                                                                                             | _                                                                                                                                                               | SIDL                                                                                                           | DISSDO                                                                                            | MODE32                                                                           | MODE16            | SMP              | CKE <sup>(3)</sup>   |

| 7.0          | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 7:0          | SSEN                                                                                                                                          | CKP <sup>(4)</sup>                                                                                                                                              | MSTEN                                                                                                          | DISSDI                                                                                            | STXISE                                                                           | L<1:0>            | SRXIS            | EL<1:0>              |

| Legend:      |                                                                                                                                               |                                                                                                                                                                 |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |

| R = Read     | lable hit                                                                                                                                     |                                                                                                                                                                 | W = Writable                                                                                                   | a hit                                                                                             |                                                                                  | mented bit, rea   | ad as '0'        |                      |

| -n = Valu    |                                                                                                                                               |                                                                                                                                                                 | '1' = Bit is se                                                                                                |                                                                                                   | '0' = Bit is cle                                                                 |                   | x = Bit is un    | known                |

|              | e al POR                                                                                                                                      |                                                                                                                                                                 |                                                                                                                | ÷l                                                                                                |                                                                                  | areu              | x = bit is un    | IKHOWH               |

| bit 31       | 0 = Framed S                                                                                                                                  | SPI support is<br>SPI support is                                                                                                                                | enabled (SS<br>disabled                                                                                        | _                                                                                                 | S FSYNC input                                                                    |                   |                  |                      |

| bit 30       | FRMSYNC: F<br>1 = Frame sy<br>0 = Frame sy                                                                                                    | nc pulse inpu                                                                                                                                                   | it (Slave mod                                                                                                  | e)                                                                                                | SSx pin bit (Fra                                                                 | amed SPI mo       | de only)         |                      |

| bit 29       | <b>FRMPOL:</b> Fra<br>1 = Frame pu<br>0 = Frame pu                                                                                            | ame Sync Po<br>Ilse is active-                                                                                                                                  | larity bit (Frar<br>high                                                                                       |                                                                                                   | e only)                                                                          |                   |                  |                      |

| bit 28       | MSSEN: Mas<br>1 = Slave sele                                                                                                                  | ter Mode Sla<br>ect SPI suppo<br>ode. Polarity i                                                                                                                | ve Select Ena<br>ort enabled. T<br>s determined                                                                | he <u>SS</u> pin is a by the FRMF                                                                 | automatically o<br>POL bit.                                                      | driven during t   | transmission     | in                   |

| bit 27       | <b>FRMSYPW:</b> F                                                                                                                             | Frame Sync F                                                                                                                                                    | ulse Width b                                                                                                   | it                                                                                                |                                                                                  |                   |                  |                      |

|              | 0 = Frame sy                                                                                                                                  |                                                                                                                                                                 |                                                                                                                | viac                                                                                              |                                                                                  |                   |                  |                      |

| bit 26-24    | FRMCNT<2:0<br>pulse. This bit<br>111 = Reserv<br>110 = Reserv<br>101 = Genera<br>010 = Genera<br>010 = Genera<br>010 = Genera<br>001 = Genera | t is only valid<br>red; do not us<br>red; do not us<br>ate a frame sy<br>ate a frame sy | in FRAMED_<br>e<br>e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e | SYNC mode<br>every 32 data<br>every 16 data<br>every 8 data o<br>every 4 data o<br>every 2 data o | characters<br>characters<br>characters<br>characters<br>characters<br>characters | nber of data c    | characters tra   | ansmitted pe         |

| bit 23       | <b>MCLKSEL:</b> M<br>1 = REFCLK<br>0 = PBCLK is                                                                                               | is used by the                                                                                                                                                  | e Baud Rate                                                                                                    |                                                                                                   |                                                                                  |                   |                  |                      |

| bit 22-18    | Unimplemen                                                                                                                                    | ted: Read as                                                                                                                                                    | '0'                                                                                                            |                                                                                                   |                                                                                  |                   |                  |                      |

| Note 1:      | SYSCLK cyc                                                                                                                                    | le immediatel                                                                                                                                                   | y following th                                                                                                 | e instruction                                                                                     | e should not re<br>that clears the                                               |                   |                  | SFRs in the          |

| 2:           | This bit can c                                                                                                                                | •                                                                                                                                                               |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |

| 3:           | This bit is not mode (FRME                                                                                                                    |                                                                                                                                                                 | Framed SPI n                                                                                                   | node. The use                                                                                     | er should prog                                                                   | ram this bit to   | 0 '0' for the F  | ramed SPI            |

| 4:           | When AUDE                                                                                                                                     | N = 1, the SP                                                                                                                                                   | I module fund                                                                                                  | tions as if the                                                                                   | e CKP bit is eq                                                                  | ual to '1', rega  | ardless of the   | actual value         |

####

of CKP.

# REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | -                 | -                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | -                 | —                 |                   | _                | —                |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | _                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | HSC = Hardware set/clear  | ed                |

|-------------------|----------------------|---------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'        |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | C = Clearable bit |

# bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy 0 = No collision

- Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 **I2COV:** Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 |                   | —                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 |                   | —                 | _                 | —                | -                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

# REGISTER 23-7: C1RXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RXOVF<15:0>: FIFOx Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

# REGISTER 23-8: C1TMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 51.24        | CANTS<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        |                   |                   |                   | CANTS             | i<7:0>            |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         |                   |                   |                   | CANTSPR           | E<15:8>           |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | CANTSPF           | RE<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (C1CON<20>) is set.

# bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits 1111 1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks . . 0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** C1TMR will be paused when CANCAP = 0.

2: The C1TMR prescaler count will be reset on any write to C1TMR (CANTSPRE will be unaffected).

# 24.1 Control Registers

# TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         |                                 |           |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON                          | 31:16     | _     | _     | —     | —     | —     | _     | —    | —    | _    | —      | —    | —    | _    | —     | —     | _     | 0000       |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4010                        | CM2CON                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4020                        | CM3CON                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A000                        | CIVISTAT                        | 15:0      | —     | _     | SIDL  | —     | _     |       |      | _    | —    |        | _    | —    | —    | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

|              |                   | 101 00. DE        |                   | 100IIA IIOI       |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 | —                 | —                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | _                 | _                 | _                 | -                 | _                 | -                | _                |  |

| 15:8         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 10.0         |                   |                   |                   | USERID<1          | 15:8>             |                   |                  |                  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

# REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bi  | it                 |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit