Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

|                           |                                                                                 |

| Product Status            | Active                                                                          |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| Speed                     | 40MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O             | 53                                                                              |

| Program Memory Size       | 256KB (256K x 8)                                                                |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 32K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ata Converters            | A/D 28x10b                                                                      |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

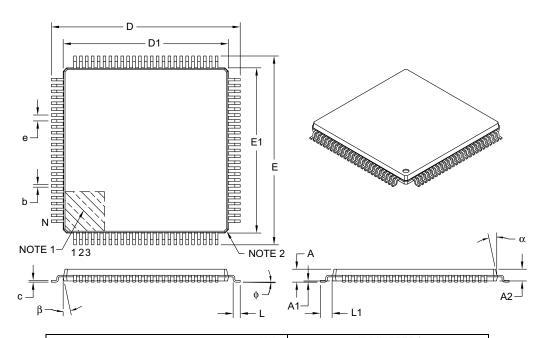

| Mounting Type             | Surface Mount                                                                   |

| ackage / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package   | 64-QFN (9x9)                                                                    |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256ht-v-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES

100-PIN TQFP (TOP VIEW)

PIC32MX130F128L PIC32MX150F256L PIC32MX170F512L

100

1

| Pin #         Full Pin Name           1         AN28/RG15           2         VDD           3         AN22/RPE5/PMD5/RE5           4         AN23/PMD6/RE6           5         AN27/PMD7/RE7           6         AN29/RPC1/RC1           7         AN30/RPC2/RC2           8         AN31/RPC3/RC3           9         RPC4/CTED7/RC4           10         AN16/C1IND/RPG6/SCK2/PMA5/RG6           11         AN17/C1INC/RPG7/PMA4/RG7           12         AN18/C2IND/RPG8/PMA3/RG8           13         MCLR           14         AN19/C2INC/RPG9/PMA2/RG9           15         Vss           16         VDD           17         TMS/CTED1/RA0           18         AN32/RPE8/RE8           19         AN33/RPE9/RE9           20         AN5/C1INA/RPB5/RB5           21         AN4/C1INB/RB4           22         PGED3/AN3/C2INA/RPB3/RB3           23         PGEC1/AN1/RPB1/CTED12/RB1           25         PGED1/AN0/RPB0/RB0           26         PGEC2/AN6/RPB6/RB6           27         PGED2/AN7/RPB7/CTED3/RB7           28         Vref-/PMA7/RA9           29 |      |                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------|

| 2 VDD 3 AN22/RPE5/PMD5/RE5 4 AN23/PMD6/RE6 5 AN27/PMD7/RE7 6 AN29/RPC1/RC1 7 AN30/RPC2/RC2 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 VSS 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                | Pin# | Full Pin Name                         |

| 3 AN22/RPE5/PMD5/RE5 4 AN23/PMD6/RE6 5 AN27/PMD7/RE7 6 AN29/RPC1/RC1 7 AN30/RPC2/RC2 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1    | AN28/RG15                             |

| 4 AN23/PMD6/RE6 5 AN27/PMD7/RE7 6 AN29/RPC1/RC1 7 AN30/RPC2/RC2 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2    | VDD                                   |

| 5 AN27/PMD7/RE7 6 AN29/RPC1/RC1 7 AN30/RPC2/RC2 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3    | AN22/RPE5/PMD5/RE5                    |

| 6 AN29/RPC1/RC1 7 AN30/RPC2/RC2 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4    | AN23/PMD6/RE6                         |

| 7 AN30/RPC2/RC2 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5    | AN27/PMD7/RE7                         |

| 8 AN31/RPC3/RC3 9 RPC4/CTED7/RC4 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6    | AN29/RPC1/RC1                         |

| 9 RPC4/CTED7/RC4  10 AN16/C1IND/RPG6/SCK2/PMA5/RG6  11 AN17/C1INC/RPG7/PMA4/RG7  12 AN18/C2IND/RPG8/PMA3/RG8  13 MCLR  14 AN19/C2INC/RPG9/PMA2/RG9  15 Vss  16 VDD  17 TMS/CTED1/RA0  18 AN32/RPE8/RE8  19 AN33/RPE9/RE9  20 AN5/C1INA/RPB5/RB5  21 AN4/C1INB/RB4  22 PGED3/AN3/C2INA/RPB3/RB3  23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2  24 PGEC1/AN1/RPB1/CTED12/RB1  25 PGED1/AN0/RPB0/RB0  26 PGEC2/AN6/RPB6/RB6  27 PGED2/AN7/RPB7/CTED3/RB7  28 VREF-/PMA7/RA9  29 VREF+/PMA6/RA10  30 AVDD  31 AVSS  32 AN8/RPB8/CTED10/RB8  33 AN9/RPB9/CTED4/RB9  34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7    | AN30/RPC2/RC2                         |

| 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8    | AN31/RPC3/RC3                         |

| 11 AN17/C1INC/RPG7/PMA4/RG7 12 AN18/C2IND/RPG8/PMA3/RG8 13 MCLR 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9    | RPC4/CTED7/RC4                        |

| 12 AN18/C2IND/RPG8/PMA3/RG8  13 MCLR  14 AN19/C2INC/RPG9/PMA2/RG9  15 Vss  16 VDD  17 TMS/CTED1/RA0  18 AN32/RPE8/RE8  19 AN33/RPE9/RE9  20 AN5/C1INA/RPB5/RB5  21 AN4/C1INB/RB4  22 PGED3/AN3/C2INA/RPB3/RB3  23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2  24 PGEC1/AN1/RPB1/CTED12/RB1  25 PGED1/AN0/RPB0/RB0  26 PGEC2/AN6/RPB6/RB6  27 PGED2/AN7/RPB7/CTED3/RB7  28 VREF-/PMA7/RA9  29 VREF+/PMA6/RA10  30 AVDD  31 AVSS  32 AN8/RPB8/CTED10/RB8  33 AN9/RPB9/CTED4/RB9  34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| 13 MCLR  14 AN19/C2INC/RPG9/PMA2/RG9  15 Vss  16 VDD  17 TMS/CTED1/RA0  18 AN32/RPE8/RE8  19 AN33/RPE9/RE9  20 AN5/C1INA/RPB5/RB5  21 AN4/C1INB/RB4  22 PGED3/AN3/C2INA/RPB3/RB3  23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2  24 PGEC1/AN1/RPB1/CTED12/RB1  25 PGED1/AN0/RPB0/RB0  26 PGEC2/AN6/RPB6/RB6  27 PGED2/AN7/RPB7/CTED3/RB7  28 VREF-/PMA7/RA9  29 VREF+/PMA6/RA10  30 AVDD  31 AVSS  32 AN8/RPB8/CTED10/RB8  33 AN9/RPB9/CTED4/RB9  34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11   | AN17/C1INC/RPG7/PMA4/RG7              |

| 14 AN19/C2INC/RPG9/PMA2/RG9 15 Vss 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12   | AN18/C2IND/RPG8/PMA3/RG8              |

| 15 VSS 16 VDD 17 TMS/CTED1/RA0 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13   | MCLR                                  |

| 16 VDD  17 TMS/CTED1/RA0  18 AN32/RPE8/RE8  19 AN33/RPE9/RE9  20 AN5/C1INA/RPB5/RB5  21 AN4/C1INB/RB4  22 PGED3/AN3/C2INA/RPB3/RB3  23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2  24 PGEC1/AN1/RPB1/CTED12/RB1  25 PGED1/AN0/RPB0/RB0  26 PGEC2/AN6/RPB6/RB6  27 PGED2/AN7/RPB7/CTED3/RB7  28 VREF-/PMA7/RA9  29 VREF+/PMA6/RA10  30 AVDD  31 AVSS  32 AN8/RPB8/CTED10/RB8  33 AN9/RPB9/CTED4/RB9  34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14   | AN19/C2INC/RPG9/PMA2/RG9              |

| 17 TMS/CTED1/RA0  18 AN32/RPE8/RE8  19 AN33/RPE9/RE9  20 AN5/C1INA/RPB5/RB5  21 AN4/C1INB/RB4  22 PGED3/AN3/C2INA/RPB3/RB3  23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2  24 PGEC1/AN1/RPB1/CTED12/RB1  25 PGED1/AN0/RPB0/RB0  26 PGEC2/AN6/RPB6/RB6  27 PGED2/AN7/RPB7/CTED3/RB7  28 VREF-/PMA7/RA9  29 VREF+/PMA6/RA10  30 AVDD  31 AVSS  32 AN8/RPB8/CTED10/RB8  33 AN9/RPB9/CTED4/RB9  34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15   | Vss                                   |

| 18 AN32/RPE8/RE8 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16   | VDD                                   |

| 19 AN33/RPE9/RE9 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17   | TMS/CTED1/RA0                         |

| 20 AN5/C1INA/RPB5/RB5 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18   | AN32/RPE8/RE8                         |

| 21 AN4/C1INB/RB4 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19   | AN33/RPE9/RE9                         |

| 22 PGED3/AN3/C2INA/RPB3/RB3 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20   | AN5/C1INA/RPB5/RB5                    |

| 23 PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21   | AN4/C1INB/RB4                         |

| 24 PGEC1/AN1/RPB1/CTED12/RB1 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22   | PGED3/AN3/C2INA/RPB3/RB3              |

| 25 PGED1/AN0/RPB0/RB0 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23   | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 |

| 26 PGEC2/AN6/RPB6/RB6 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24   | PGEC1/AN1/RPB1/CTED12/RB1             |

| 27 PGED2/AN7/RPB7/CTED3/RB7 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25   | PGED1/AN0/RPB0/RB0                    |

| 28 VREF-/PMA7/RA9 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26   | PGEC2/AN6/RPB6/RB6                    |

| 29 VREF+/PMA6/RA10 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27   | PGED2/AN7/RPB7/CTED3/RB7              |

| 30 AVDD 31 AVSS 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28   | VREF-/PMA7/RA9                        |

| 31 AVss 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29   | VREF+/PMA6/RA10                       |

| 32 AN8/RPB8/CTED10/RB8 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30   | AVDD                                  |

| 33 AN9/RPB9/CTED4/RB9 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31   | AVss                                  |

| 34 CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32   | AN8/RPB8/CTED10/RB8                   |

| 01 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33   | AN9/RPB9/CTED4/RB9                    |

| 35 AN11/PMA12/RB11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34   | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35   | AN11/PMA12/RB11                       |

| Pin # | Full Pin Name                   |

|-------|---------------------------------|

| 36    | Vss                             |

| 37    | VDD                             |

| 38    | TCK/CTED2/RA1                   |

| 39    | AN34/RPF13/SCK3/RF13            |

| 40    | AN35/RPF12/RF12                 |

| 41    | AN12/PMA11/RB12                 |

| 42    | AN13/PMA10/RB13                 |

| 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45    | Vss                             |

| 46    | VDD                             |

| 47    | AN36/RPD14/RD14                 |

| 48    | AN37/RPD15/SCK4/RD15            |

| 49    | RPF4/PMA9/RF4                   |

| 50    | RPF5/PMA8/RF5                   |

| 51    | RPF3/RF3                        |

| 52    | AN38/RPF2/RF2                   |

| 53    | AN39/RPF8/RF8                   |

| 54    | RPF7/RF7                        |

| 55    | RPF6/SCK1/INT0/RF6              |

| 56    | SDA1/RG3                        |

| 57    | SCL1/RG2                        |

| 58    | SCL2/RA2                        |

| 59    | SDA2/RA3                        |

| 60    | TDI/CTED9/RA4                   |

| 61    | TDO/RA5                         |

| 62    | VDD                             |

| 63    | OSC1/CLKI/RC12                  |

| 64    | OSC2/CLKO/RC15                  |

| 65    | Vss                             |

| 66    | RPA14/RA14                      |

| 67    | RPA15/RA15                      |

| 68    | RPD8/RTCC/RD8                   |

| 69    | RPD9/RD9                        |

| 70    | RPD10/PMA15/RD10                |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                        | Pin N                  | umber           |             |                |                                                                                                    |  |  |  |  |  |  |  |

|------------------------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin Name               | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                        |  |  |  |  |  |  |  |

| VUSB3V3 <sup>(2)</sup> | 35                     | 55              | Р           | _              | USB internal transceiver supply. If the USB module is not used, this pin must be connected to VDD. |  |  |  |  |  |  |  |

| VBUSON <sup>(2)</sup>  | 11                     | 20              | 0           | _              | USB Host and OTG bus power control Output                                                          |  |  |  |  |  |  |  |

| D+ <sup>(2)</sup>      | 37                     | 57              | I/O         | Analog         | USB D+                                                                                             |  |  |  |  |  |  |  |

| D- <sup>(2)</sup>      | 36                     | 56              | I/O         | Analog         | USB D-                                                                                             |  |  |  |  |  |  |  |

| USBID <sup>(2)</sup>   | 33                     | 51              | I           | ST             | USB OTG ID Detect                                                                                  |  |  |  |  |  |  |  |

| PGED1                  | 16                     | 25              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1                                     |  |  |  |  |  |  |  |

| PGEC1                  | 15                     | 24              | I           | ST             | Clock Input pin for Programming/Debugging Communication Channel 1                                  |  |  |  |  |  |  |  |

| PGED2                  | 18                     | 27              | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication Channel 2                                     |  |  |  |  |  |  |  |

| PGEC2                  | 17                     | 26              | I           | ST             | Clock Input Pin for Programming/Debugging Communication Channel 2                                  |  |  |  |  |  |  |  |

| PGED3                  | 13                     | 22              | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication Channel 3                                     |  |  |  |  |  |  |  |

| PGEC3                  | 14                     | 23              | I           | ST             | Clock Input Pin for Programming/Debugging Communication Channel 3                                  |  |  |  |  |  |  |  |

| CTED1                  | _                      | 17              | I           | ST             | CTMU External Edge Input 1                                                                         |  |  |  |  |  |  |  |

| CTED2                  | _                      | 38              | I           | ST             | CTMU External Edge Input 2                                                                         |  |  |  |  |  |  |  |

| CTED3                  | 18                     | 27              | I           | ST             | CTMU External Edge Input 3                                                                         |  |  |  |  |  |  |  |

| CTED4                  | 22                     | 33              | I           | ST             | CTMU External Edge Input 4                                                                         |  |  |  |  |  |  |  |

| CTED5                  | 29                     | 43              | I           | ST             | CTMU External Edge Input 5                                                                         |  |  |  |  |  |  |  |

| CTED6                  | 30                     | 44              | I           | ST             | CTMU External Edge Input 6                                                                         |  |  |  |  |  |  |  |

| CTED7                  | _                      | 9               | I           | ST             | CTMU External Edge Input 7                                                                         |  |  |  |  |  |  |  |

| CTED8                  | _                      | 92              | ı           | ST             | CTMU External Edge Input 8                                                                         |  |  |  |  |  |  |  |

| CTED9                  |                        | 60              | I           | ST             | CTMU External Edge Input 9                                                                         |  |  |  |  |  |  |  |

| CTED10                 | 21                     | 32              | I           | ST             | CTMU External Edge Input 10                                                                        |  |  |  |  |  |  |  |

| CTED11                 | 23                     | 34              | I           | ST             | CTMU External Edge Input 11                                                                        |  |  |  |  |  |  |  |

| CTED12                 | 15                     | 24              | I           | ST             | CTMU External Edge Input 12                                                                        |  |  |  |  |  |  |  |

| CTED13                 | 14                     | 23              | I           | ST             | CTMU External Edge Input 13                                                                        |  |  |  |  |  |  |  |

| C1RX                   | PPS                    | PPS             | I           | ST             | Enhanced CAN Receive                                                                               |  |  |  |  |  |  |  |

| C1TX                   | PPS                    | PPS             | 0           | ST             | Enhanced CAN Transmit                                                                              |  |  |  |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input I = Input O = Output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

**4:** This pin is only available on 100-pin devices without a USB module.

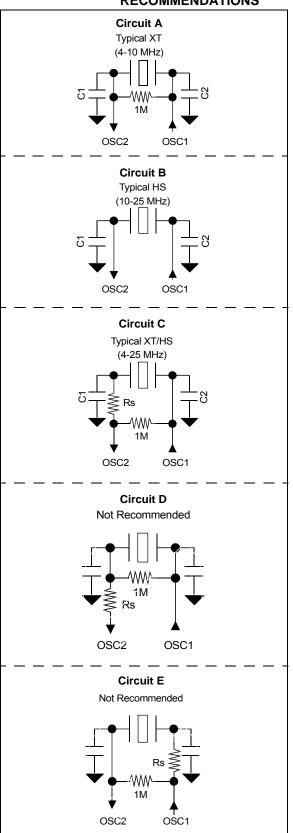

## 2.7.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following examples are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32 OSC2 Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

```

Crystal manufacturer recommended: CI = C2 = 15 pF

Therefore:

CLOAD = \{([CIN + CI] * [COUT + C2]) / [CIN + CI + C2 + COUT]\} + estimated oscillator PCB stray capacitance

= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 pF

= \{([20][20]) / [40]\} + 2.5

= 10 + 2.5 = 12.5 pF

Rounded to the nearest standard value or 13 pF in this example for Primary Oscillator crystals "C1" and "C2".

```

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator.

The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.7.1.1 Additional Microchip References

- AN588 "PICmicro® Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

# FIGURE 2-4: PRIMARY CRYSTAL OSCILLATOR CIRCUIT RECOMMENDATIONS

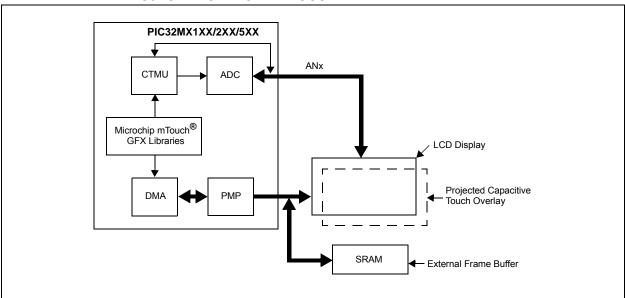

FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

#### REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|

| 24:24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | BMXDRM            | /ISZ<31:24>       |                   |                  |                  |  |  |  |  |  |  |  |  |

| 22:16        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |

| 23:16        |                   | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | BMXDRI            | MSZ<15:8>         |                   |                  |                  |  |  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |

| 7:0          |                   | BMXDRMSZ<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes:

0x00002000 = Device has 8 KB RAM 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

## REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0                   | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0              | U-0              |  |  |  |  |

| 31:24        | _                     | _                 |                   | _                 |                   |                   | _                | _                |  |  |  |  |

| 00.40        | U-0                   | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | — — — BMXPUPBA<19:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | BMXPUPBA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0                   | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | BMXPUPBA<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 BMXPUPBA<10:0>: Read-Only bits

Value is always '0', which forces 2 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

**NOTES:**

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 31:24        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31.24        |                                           | DCRCDATA<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 22:46        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | DCRCDATA<23:16>                           |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 15.0         | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         |                                           |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |  |  |  |

| 7:0          | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          |                                           |                   |                   | DCRCDA            | ΓA<7:0>           |                   |                  |                  |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 31:24        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31.24        |                                           | DCRCXOR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23.10        | DCRCXOR<23:16>                            |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         |                                           |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7:0          |                                           |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

| Bit<br>Range |       |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------|-------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 31:24        | U-0   | U-0   | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              |

| 31.24        | _     |       |                   | _                 | _                 | _                 |                       |                  |

| 23:16        | U-0   | U-0   | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              |

| 23.10        | _     | _     | _                 | _                 | _                 | _                 | _                     | _                |

| 15:8         | U-0   | U-0   | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              |

| 15.6         | _     | _     |                   | _                 | _                 | _                 | _                     |                  |

|              | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0            |

| 7:0          | DTOFF | DMVEE |                   | DTOFF             | DEMOSE            | 0004655           | CRC5EE <sup>(1)</sup> | DIDEE            |

|              | BTSEE | BMXEE | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

1 = BTSEF interrupt enabled0 = BTSEF interrupt disabled

bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

1 = BMXEF interrupt enabled0 = BMXEF interrupt disabled

bit 5 DMAEE: DMA Error Interrupt Enable bit

1 = DMAEF interrupt enabled0 = DMAEF interrupt disabled

bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

1 = BTOEF interrupt enabled0 = BTOEF interrupt disabled

bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

1 = DFN8EF interrupt enabled0 = DFN8EF interrupt disabled

bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

1 = CRC16EF interrupt enabled0 = CRC16EF interrupt disabled

bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit(1)

1 = CRC5EF interrupt enabled0 = CRC5EF interrupt disabled

**EOFEE:** EOF Error Interrupt Enable bit<sup>(2)</sup>

1 = EOF interrupt enabled0 = EOF interrupt disabled

bit 0 PIDEE: PID Check Failure Interrupt Enable bit

1 = PIDEF interrupt enabled0 = PIDEF interrupt disabled

Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

**TABLE 11-5:** PORTC REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |          |          |          |          |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | ANSLLO                          | 15:0      | _         | _         |           |           | _     | _     | _    | _    | _    | _    | _    | _        | ANSELC3  | ANSELC2  | ANSELC1  | _    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | _         |           |           | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0210                        | TKISC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | _     | _     | _    | _    | _    | _    | _    | TRISC4   | TRISC3   | TRISC2   | TRISC1   | _    | FFFF          |

| 6220                        | PORTC                           | 31:16     | 1         | _         | 1         | 1         | -     | _     | -    |      |      | _    | _    | -        | _        | _        | _        | _    | 0000          |

| 0220                        | FORTO                           | 15:0      | RC15      | RC14      | RC13      | RC12      | -     | _     | -    |      |      | _    | _    | RC4      | RC3      | RC2      | RC1      | _    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0230                        | LAIC                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    |       | _     |      |      |      | _    | _    | LATC4    | LATC3    | LATC2    | LATC1    | _    | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0240                        | 0000                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | _     | _     | _    | _    | _    | _    | _    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | _    | 0000          |

| 6250                        | CNPUC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | 0111 00                         | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | _     | _    | _    | _    | _    | _    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | _    | 0000          |

| 6260                        | CNPDC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | ON DO                           | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | _     | _     | _    | _    | _    | _    | _    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0270                        | 01100110                        | 15:0      | ON        | _         | SIDL      | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | _         |           | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | ONLINO                          | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | _     | _    | _    | _    | _    | _    | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | _    | 0000          |

| 6290                        | CNSTATC                         | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | 51,517(10                       | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     | _     | _    | _    |      | _    | _    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | _    | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

TABLE 11-15: PORTG REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 | •         |               |               |               |               |       |       |              | Bits         | 5            |              |      |      |                    |                    |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1         | 16/0         | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | _             | -             | _             | _             | _     | ı     | _            | _            | ı            | _            | ı    | _    | _                  | _                  | _            | _            | 0000          |

| 0000                        | ANOLLO                          | 15:0      | ANSELG15      | _             | _             | _             | _     | _     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | _    | _    | _                  | _                  | _            | _            | 83C0          |

| 6610                        | TRISG                           | 31:16     | _             | _             | _             | _             | _     | _     | _            | _            |              | _            |      | _    | _                  | _                  | _            | _            | 0000          |