Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

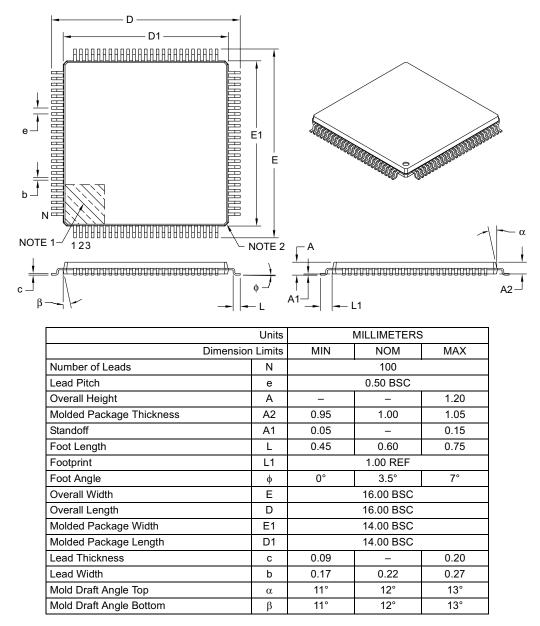

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256l-50i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IABLE 1-1 |                        | umber           |             | (•             |                                                                                                                                                                                        |

|-----------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name  | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                            |

| AN36      |                        | 47              | I           | Analog         |                                                                                                                                                                                        |

| AN37      | _                      | 48              | I           | Analog         |                                                                                                                                                                                        |

| AN38      | _                      | 52              | I           | Analog         |                                                                                                                                                                                        |

| AN39      | _                      | 53              | I           | Analog         |                                                                                                                                                                                        |

| AN40      | _                      | 79              | I           | Analog         |                                                                                                                                                                                        |

| AN41      | _                      | 80              | I           | Analog         | Analog input channels                                                                                                                                                                  |

| AN42      | _                      | 83              | Ι           | Analog         | Analog input channels.                                                                                                                                                                 |

| AN43      |                        | 84              | I           | Analog         |                                                                                                                                                                                        |

| AN44      | _                      | 87              | I           | Analog         |                                                                                                                                                                                        |

| AN45      | _                      | 88              | Ι           | Analog         |                                                                                                                                                                                        |

| AN46      | _                      | 93              | I           | Analog         |                                                                                                                                                                                        |

| AN47      | _                      | 94              | I           | Analog         |                                                                                                                                                                                        |

| CLKI      | 39                     | 63              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                 |

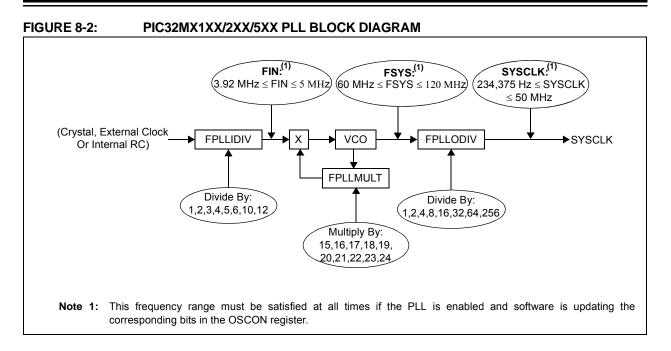

| CLKO      | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with the OSC2 pin function. |

| OSC1      | 39                     | 63              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                        |

| OSC2      | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                               |

| SOSCI     | 47                     | 73              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                         |

| SOSCO     | 48                     | 74              | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                        |

| IC1       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC2       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC3       | PPS                    | PPS             | I           | ST             | Capture Input 1-5                                                                                                                                                                      |

| IC4       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC5       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

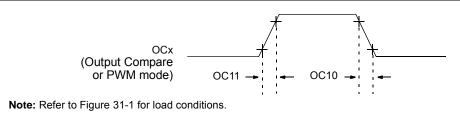

| OC1       | PPS                    | PPS             | 0           | ST             | Output Compare Output 1                                                                                                                                                                |

| OC2       | PPS                    | PPS             | 0           | ST             | Output Compare Output 2                                                                                                                                                                |

| OC3       | PPS                    | PPS             | 0           | ST             | Output Compare Output 3                                                                                                                                                                |

| OC4       | PPS                    | PPS             | 0           | ST             | Output Compare Output 4                                                                                                                                                                |

| OC5       | PPS                    | PPS             | 0           | ST             | Output Compare Output 5                                                                                                                                                                |

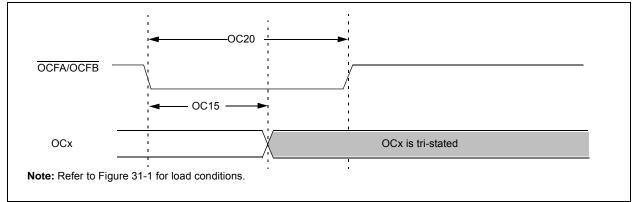

| OCFA      | PPS                    | PPS             | Ι           | ST             | Output Compare Fault A Input                                                                                                                                                           |

| OCFB      | 30                     | 44              | I           | ST             | Output Compare Fault B Input                                                                                                                                                           |

|           |                        | IOS compati     |             |                | Analog = Analog input I = Input O = Output                                                                                                                                             |

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = P

P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|---------------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0                       | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | —                       | _                 | _                 | —                         |                  | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0                       | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | —                       | —                 | —                 | —                         |                  | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0                     | U-0               | U-0               | R/W-0                     | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | _                 | —                 |                         | _                 | _                 | SRIPL<2:0> <sup>(1)</sup> |                  |                  |  |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | _                 |                   | VEC<5:0> <sup>(1)</sup> |                   |                   |                           |                  |                  |  |  |  |  |

#### REGISTER 5-2: INTSTAT: INTERRUPT STATUS REGISTER

#### Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **SRIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 **Unimplemented:** Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 |       |         |       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------|---------|-------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0 | R/W-0   | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   | •                 |                   | IPTMF | <31:24> |       |                  |                  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0 | R/W-0   | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |

|              | IPTMR<23:16>      |                   |                   |       |         |       |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0 | R/W-0   | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | IPTMR<15:8>       |                   |                   |       |         |       |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0 | R/W-0   | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | IPTM  | R<7:0>  |       |                  |                  |  |  |  |  |  |

#### REGISTER 5-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 04.04          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24<br>23:16 |                   | NVMDATA<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

|                | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8           |                   | NVMDATA<15:8>     |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0            | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0            |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |  |  |  |  |

#### **REGISTER 6-4:** NVMDATA: FLASH PROGRAM DATA REGISTER

I edend.

| Logonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

#### NVMSRCADDR: SOURCE DATA ADDRESS REGISTER **REGISTER 6-5:**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit<br>30/22/14/6 29/21/13/5 |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|----------------------------------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 21.24        | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | NVMSRCADDR<31:24> |                                  |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:10        | NVMSRCADDR<23:16> |                                  |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                                  |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                                  |       | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |  |  |  |

|-------------------|------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

### 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

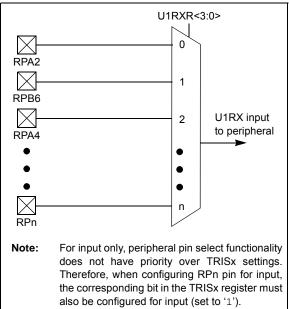

#### 11.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

### FIGURE 11-2: REI

REMAPPABLE INPUT EXAMPLE FOR U1RX

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection        |

|----------------|-----------------|------------------|-----------------------------------------------------------|

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPD1<br>0001 = RPG9                                |

| тзск           | T3CKR           | T3CKR<3:0>       | 0010 = RPB14<br>0011 = RPD0                               |

| IC1            | IC1R            | IC1R<3:0>        | 0100 = RPD8<br>0101 = RPB6                                |

| U3CTS          | U3CTSR          | U3CTSR<3:0>      | 0110 = RPD5<br>0111 = RPB2                                |

| U4RX           | U4RXR           | U4RXR<3:0>       | 1000 = RPF3 <sup>(4)</sup><br>1001 = RPF13 <sup>(3)</sup> |

| U5RX           | U5RXR           | U5RXR<3:0>       | 1010 = Reserved<br>1011 = RPF2 <sup>(1)</sup>             |

| SS2            | SS2R            | SS2R<3:0>        | 1100 = RPC2 <sup>(3)</sup><br>1101 = RPE8 <sup>(3)</sup>  |

| OCFA           | OCFAR           | OCFAR<3:0>       | 1110 = Reserved<br>1111 = Reserved                        |

#### TABLE 11-1:INPUT PIN SELECTION (CONTINUED)

Note 1: This selection is not available on 64-pin USB devices.

- 2: This selection is only available on 100-pin General Purpose devices.

- 3: This selection is not available on 64-pin devices.

- 4: This selection is not available when USBID functionality is used on USB devices.

- 5: This selection is not available on devices without a CAN module.

- 6: This selection is not available on USB devices.

- 7: This selection is not available when VBUSON functionality is used on USB devices.

#### TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                                              |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Virtual Addr<br>(BF80_#)<br>Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

|                             |                                              | 31:16     | _     | _     | _     | -     | _     | _     | _    | -    | -    | _    | -    | _    | _    | _    | -      | _    | 00         |

| FB88                        | RPC2R                                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2 | 2<3:0> |      | 00         |

|                             |                                              | 31:16     | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FB8C                        | RPC3R                                        | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPC  | 3<3:0> |      | 00         |

| 5000                        | 00040                                        | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FB90                        | RPC4R                                        | 15:0      | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    |      | RPC4 | <3:0>  |      | 00         |

| 5004                        | 000400                                       | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBB4                        | RPC13R                                       | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1 | 3<3:0> |      | 00         |

|                             |                                              | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | _    | _    | _      |      | 00         |

| FBB8                        | RPC14R                                       | 15:0      | _     | _     | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPC1 | 4<3:0> |      | 00         |

| 50.00                       | 00000                                        | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBC0                        | RPD0R                                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      |      | RPD  | )<3:0> |      | 00         |

|                             |                                              | 31:16     | _     | _     | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FBC4                        | RPD1R                                        | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD' | <3:0>  |      | 00         |

|                             |                                              | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | _    | _    | _      |      | 00         |

| FBC8                        | RPD2R                                        | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD2 | 2<3:0> |      | 00         |

| 5000                        | 00000                                        | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBCC                        | RPD3R                                        | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 3<3:0> |      | 00         |

| 5000                        | 00040                                        | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBD0                        | RPD4R                                        | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD4 | <3:0>  |      | 00         |

|                             | 00050                                        | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBD4                        | RPD5R                                        | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 5<3:0> |      | 00         |

|                             |                                              | 31:16     | —     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —    | —      |      | 00         |

| FBE0                        | RPD8R                                        | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD8 | 3<3:0> |      | 00         |

| 5054                        | 00000                                        | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBE4                        | RPD9R                                        | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD9 | 9<3:0> |      | 00         |

|                             |                                              | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBE8                        | RPD10R                                       | 15:0      | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD1 | 0<3:0> |      | 00         |

|                             | 000440                                       | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | —    | _    | _      | —    | 00         |

| FBEC                        | RPD11R                                       | 15:0      | —     | _     | —     | _     | —     | —     | _    | —    | _    | _    | _    | _    |      | RPD1 | 1<3:0> |      | 00         |

| FDFC                        |                                              | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF0                        | RPD12R                                       | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD1 | 2<3:0> |      | 00         |

| EDEC                        |                                              | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF8                        | RPD14R                                       | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPD1 | 4<3:0> |      | 00         |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | -                 | _                 | —                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | e]R<3:0>         |                  |

#### REGISTER 11-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | —                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | RPnR              | <3:0>            |                  |

#### Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

NOTES:

| IL GIOTE                           | -1\ 21-4. 1\      | ICDAIL. N                              |                   |                   |                   |                   |                  |                  |

|------------------------------------|-------------------|----------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range                       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04                              | R/W-x             | R/W-x                                  | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24                              |                   | YEAR1                                  | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |

| 00.40                              | R/W-x             | R/W-x                                  | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16                              | MONTH10<3:0>      |                                        |                   |                   | MONTH01<3:0>      |                   |                  |                  |

| 45.0                               | R/W-x             | R/W-x                                  | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8                               |                   | DAY10                                  | <3:0>             |                   | DAY01<3:0>        |                   |                  |                  |

| 7.0                                | U-0               | U-0                                    | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0                                | _                 | —                                      | _                 | —                 | WDAY01<3:0>       |                   |                  |                  |

|                                    |                   |                                        |                   |                   |                   |                   |                  |                  |

| Legend:                            |                   |                                        |                   |                   |                   |                   |                  |                  |

| R = Read                           | able bit          |                                        | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |

| -n = Value at POR '1' = Bit is set |                   | 0' = Bit is cleared x = Bit is unknown |                   |                   | known             |                   |                  |                  |

#### REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | CSSL31 <sup>(2)</sup> | CSSL30 <sup>(1)</sup> | CSSL29 <sup>(1)</sup> | CSSL28 <sup>(1)</sup> | CSSL27            | CSSL26            | CSSL25           | CSSL24           |

| 23:16        | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | CSSL23                | CSSL21                | CSSL21                | CSSL20                | CSSL19            | CSSL18            | CSSL17           | CSSL16           |

| 15.0         | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15                | CSSL14                | CSSL13                | CSSL12                | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7                 | CSSL6                 | CSSL5                 | CSSL4                 | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-0 CSSL<31:0>: ADC Input Pin Scan Selection bits

- 1 = Select ANx for input scan; CSSLx = ANx, where 'x' = 0-31

- 0 = Skip ANx for input scan; CSSLx = ANx, where 'x' = 0-31

- Note 1: For devices with 64 pins, CSSL28 selects IVREF (Band Gap) for scan; CSSL29 selects CTMU temperature diode for scan; and CSSL30 selects CTMU input for scan

- 2: On devices with less than 32 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                   | U-0                   |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                     | —                     | —                     |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |

| 23:16        | _                 | —                 | _                 | _                 | —                 | CSSL50 <sup>(1)</sup> | CSSL49 <sup>(1)</sup> | CSSL48 <sup>(1)</sup> |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                 | R/W-0                 |

| 15:8         | CSSL47            | CSSL46            | CSSL45            | CSSL44            | CSSL43            | CSSL42                | CSSL41                | CSSL40                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                 | R/W-0                 |

| 7:0          | CSSL39            | CSSL38            | CSSL37            | CSSL36            | CSSL35            | CSSL34                | CSSL33                | CSSL32                |

#### REGISTER 22-6: AD1CSSL2: ADC INPUT SCAN SELECT REGISTER 2

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-19 Unimplemented: Read as '0'

- bit 18-0 CSSL<50:32>: ADC Input Pin Scan Selection bits

- 1 = Select ANx for input scan; CSSLx = ANx, where 'x' = 32-50

- 0 =Skip ANx for input scan; CSSLx = ANx, where 'x' = 32-50

- Note 1: For devices with 100 or more pins, CSSL48 selects IVREF (Band Gap) for scan; CSSL49 selects CTMU temperature diode for scan; and CSSL50 selects CTMU input for scan

**Note:** The ANx inputs in this register only support devices with 100 or more pins.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | _                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | —                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

#### **REGISTER 23-3: C1INT: CAN INTERRUPT REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | <b>WAKIE:</b> CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by cl                                                                                          |

learing or setting the ON bit N (C1CON<15>).

| REGIST  | TER 23-17: C1FIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0 THROUGH 15)<br>(CONTINUED)                                                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9   | <b>TXHALFIF:</b> FIFO Transmit FIFO Half Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is $\leq$ half full<br>0 = FIFO is > half full<br><u>TXEN = 0:</u> (FIFO configured as a receive buffer) |

| bit 8   | Unused, reads '0'<br><b>TXEMPTYIF:</b> Transmit FIFO Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is empty<br>0 = FIFO is not empty, at least 1 message queued to be transmitted               |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                                                                                                                                      |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                       |

| bit 3   | <b>RXOVFLIF:</b> Receive FIFO Overflow Interrupt Flag bit<br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                                        |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = Overflow event has occurred<br>0 = No overflow event occured                                                                                                                                       |

| bit 2   | RXFULLIF: Receive FIFO Full Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                                    |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is full<br>0 = FIFO is not full                                                                                                                                                               |

| bit 1   | <b>RXHALFIF:</b> Receive FIFO Half Full Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                        |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is ≥ half full<br>0 = FIFO is < half full                                                                                                                                                     |

| bit 0   | RXNEMPTYIF: Receive Buffer Not Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                           |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is not empty, has at least 1 message<br>0 = FIFO is empty                                                                                                                                     |

| Note 1  | This bit is read-only and reflects the status of the FIEO                                                                                                                                                                                                        |

Note 1: This bit is read-only and reflects the status of the FIFO.

#### 24.1 Control Registers

#### TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         |                                 |           | Bits  |       |       |       |       |       |      |      |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON                          | 31:16     | _     | _     | —     | —     | —     | —     | —    | —    | _    | —      | —    | —    | _    | —     | —     | _     | 0000       |

| A000                        | CM1CON                          | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4010                        | CM2CON                          | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4020                        | CM3CON                          | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A020                        |                                 | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT                          | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| 7000                        |                                 | 15:0      | —     | _     | SIDL  | _     | _     | -     |      | _    | —    |        | —    | —    | —    | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### 27.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 27.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 27.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-10 **PWP<9:0>:** Program Flash Write-Protect bits

| DIT 19-1      | <b>PWP&lt;9:0&gt;:</b> Program Flash Write-Protect bits                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. |

|               | 111111111 = Disabled                                                                                                                                                                             |

|               | 1111111110 = Memory below 0x0400 address is write-protected<br>1111111101 = Memory below 0x0800 address is write-protected                                                                       |

|               | 1111111100 = Memory below 0x0000 address is write-protected                                                                                                                                      |

|               | 1111111011 = Memory below 0x1000 (4K) address is write-protected                                                                                                                                 |

|               | 1111111010 = Memory below 0x1400 address is write-protected                                                                                                                                      |

|               | 1111111001 = Memory below 0x1800 address is write-protected                                                                                                                                      |

|               | 1111111000 = Memory below 0x1C00 address is write-protected<br>1111110111 = Memory below 0x2000 (8K) address is write-protected                                                                  |

|               | 1111110110 = Memory below 0x2400 address is write-protected                                                                                                                                      |

|               | 1111110101 = Memory below 0x2800 address is write-protected                                                                                                                                      |

|               | 1111110100 = Memory below 0x2C00 address is write-protected                                                                                                                                      |

|               | 1111110011 = Memory below 0x3000 address is write-protected                                                                                                                                      |

|               | 1111110010 = Memory below 0x3400 address is write-protected<br>1111110001 = Memory below 0x3800 address is write-protected                                                                       |

|               | 1111110000 = Memory below 0x3C00 address is write-protected                                                                                                                                      |

|               | 1111101111 = Memory below 0x4000 (16K) address is write-protected                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | •<br>1110111111 = Memory below 0x10000 (64K) address is write-protected                                                                                                                          |

|               | •                                                                                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | 1101111111 = Memory below 0x20000 (128K) address is write-protected                                                                                                                              |

|               |                                                                                                                                                                                                  |

|               | •<br>1011111111 = Memory below 0x40000 (256K) address is write-protected                                                                                                                         |

|               | •                                                                                                                                                                                                |

|               | •                                                                                                                                                                                                |

|               | •<br>0111111111 = Memory below 0x80000 (512K) address is write-protected                                                                                                                         |

|               | •                                                                                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | 000000000 = All possible memory is write-protected                                                                                                                                               |

|               | <b>Note:</b> These bits are effective only if Boot Flash is also protected by clearing the BWP bit (DEVCFG0<24>).                                                                                |

| bit 9-5       | Reserved: Write '1'                                                                                                                                                                              |

| bit 4-3       | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits                                                                                                                      |

|               | 11 = PGEC1/PGED1 pair is used                                                                                                                                                                    |

|               | 10 = PGEC2/PGED2 pair is used                                                                                                                                                                    |

|               | 01 = PGEC3/PGED3 pair is used<br>00 = Reserved                                                                                                                                                   |

| <b>h</b> :+ 0 |                                                                                                                                                                                                  |

| bit 2         | JTAGEN: JTAG Enable bit <sup>(1)</sup><br>1 = JTAG is enabled                                                                                                                                    |

|               | 0 = JTAG is enabled                                                                                                                                                                              |

| bit 1-0       | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)                                                                                             |

|               | 1x = Debugger is disabled                                                                                                                                                                        |

|               | 0x = Debugger is disabled<br>0x = Debugger is enabled                                                                                                                                            |

|               |                                                                                                                                                                                                  |

| Note 1        | This bit sets the value for the JTAGEN bit in the CEGCON register                                                                                                                                |

#### **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

#### 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 30.12 Third-Party Development Tools