Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

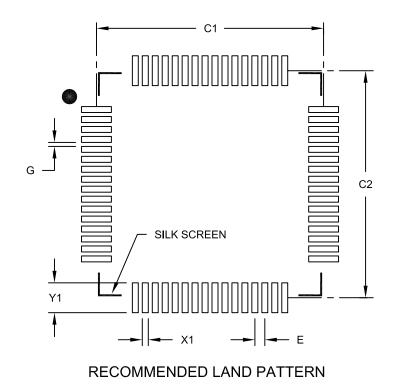

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f256lt-50i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Device Pin Tables**

#### TABLE 2: PIN NAMES FOR 64-PIN GENERAL PURPOSE DEVICES

| 64·   | PIN QFN <sup>(4)</sup> AND TQFP (TOP VIEW)                                     |                   |                        |

|-------|--------------------------------------------------------------------------------|-------------------|------------------------|

|       | PIC32MX120F064H<br>PIC32MX130F128H<br>PIC32MX150F256H<br>PIC32MX170F512H<br>64 | QFN <sup>(4</sup> | 1<br>64<br><b>TQFP</b> |

| Pin # | Full Pin Name                                                                  | Pin #             | Full Pin Name          |

| 1     | AN22/RPE5/PMD5/RE5                                                             | 33                | RPF3/RF3               |

| 2     | AN23/PMD6/RE6                                                                  | 34                | RPF2/RF2               |

| 3     | AN27/PMD7/RE7                                                                  | 35                | RPF6/SCK1/INT0/RF6     |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                                  | 36                | SDA1/RG3               |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                                                       | 37                | SCL1/RG2               |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                                                       | 38                | VDD                    |

| 7     | MCLR                                                                           | 39                | OSC1/CLKI/RC12         |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                                                       | 40                | OSC2/CLKO/RC15         |

| 9     | Vss                                                                            | 41                | Vss                    |

| 10    | VDD                                                                            | 42                | RPD8/RTCC/RD8          |

| 11    | AN5/C1INA/RPB5/RB5                                                             | 43                | RPD9/RD9               |

| 12    | AN4/C1INB/RB4                                                                  | 44                | RPD10/PMA15/RD10       |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                                                       | 45                | RPD11/PMA14/RD11       |

| 14    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2                                          | 46                | RPD0/RD0               |

| 15    | PGEC1/VREF-/AN1/RPB1/CTED12/RB1                                                | 47                | SOSCI/RPC13/RC13       |

| 16    | PGED1/VREF+/AN0/RPB0/PMA6/RB0                                                  | 48                | SOSCO/RPC14/T1CK/RC14  |

| 17    | PGEC2/AN6/RPB6/RB6                                                             | 49                | AN24/RPD1/RD1          |

| 18    | PGED2/AN7/RPB7/CTED3/RB7                                                       | 50                | AN25/RPD2/RD2          |

| 19    | AVDD                                                                           | 51                | AN26/C3IND/RPD3/RD3    |

| 20    | AVss                                                                           | 52                | RPD4/PMWR/RD4          |

| 21    | AN8/RPB8/CTED10/RB8                                                            | 53                | RPD5/PMRD/RD5          |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                                                        | 54                | C3INC/RD6              |

| 23    | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                      | 55                | C3INB/RD7              |

| 24    | TDO/AN11/PMA12/RB11                                                            | 56                | VCAP                   |

| 25    | Vss                                                                            | 57                | Vdd                    |

| 26    | Vdd                                                                            | 58                | C3INA/RPF0/RF0         |

| 27    | TCK/AN12/PMA11/RB12                                                            | 59                | RPF1/RF1               |

| 28    | TDI/AN13/PMA10/RB13                                                            | 60                | PMD0/RE0               |

| 29    | AN14/RPB14/SCK3/CTED5/PMA1/RB14                                                | 61                | PMD1/RE1               |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                                | 62                | AN20/PMD2/RE2          |

| 31    | RPF4/SDA2/PMA9/RF4                                                             | 63                | RPE3/CTPLS/PMD3/RE3    |

| 32    | RPF5/SCL2/PMA8/RF5                                                             | 64                | AN21/PMD4/RE4          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

|          | Pin N                  | umber                    |             |                |                                                                              |  |  |  |  |  |  |

|----------|------------------------|--------------------------|-------------|----------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | Pin<br>Type | Buffer<br>Type | Description                                                                  |  |  |  |  |  |  |

| MCLR     | 7                      | 13                       | I           | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |  |  |  |  |  |  |

| AVDD     | 19                     | 30                       | Ρ           | Р              | Positive supply for analog modules. This pin must be connected at all times. |  |  |  |  |  |  |

| AVss     | 20                     | 31                       | Р           | Р              | Ground reference for analog modules                                          |  |  |  |  |  |  |

| Vdd      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | Ρ           | —              | Positive supply for peripheral logic and I/O pins                            |  |  |  |  |  |  |

| VCAP     | 56                     | 85                       | Р           | _              | Capacitor for Internal Voltage Regulator                                     |  |  |  |  |  |  |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | Ρ           | _              | Ground reference for logic and I/O pins                                      |  |  |  |  |  |  |

| VREF+    | 16                     | 29                       | Р           | Analog         | Analog Voltage Reference (High) Input                                        |  |  |  |  |  |  |

| VREF-    | 15                     | 28                       | Р           | Analog         | Analog Voltage Reference (Low) Input                                         |  |  |  |  |  |  |

| Legend:  | CMOS = CN              | IOS compati              | ble inpu    | it or output   | Analog = Analog input I = Input O = Output                                   |  |  |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input I = Input ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

| Bit<br>Range |                |       |       |       |          |       |     |     |  |  |  |  |  |

|--------------|----------------|-------|-------|-------|----------|-------|-----|-----|--|--|--|--|--|

| 04.04        | U-0            | U-0   | U-0   | U-0   | U-0      | U-0   | U-0 | U-0 |  |  |  |  |  |

| 31:24        | _              | —     | _     | _     | _        | —     | _   | —   |  |  |  |  |  |

| 00.40        | U-0            | U-0   | U-0   | U-0   | U-0      | U-0   | U-0 | U-0 |  |  |  |  |  |

| 23:16        | —              | —     | _     | _     | _        | —     | —   | —   |  |  |  |  |  |

| 45.0         | R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R-0 | R-0 |  |  |  |  |  |

| 15:8         | BMXDUDBA<15:8> |       |       |       |          |       |     |     |  |  |  |  |  |

| 7.0          | R-0            | R-0   | R-0   | R-0   | R-0      | R-0   | R-0 | R-0 |  |  |  |  |  |

| 7:0          |                |       |       | BMXDU | DBA<7:0> |       |     |     |  |  |  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range |     |     | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-----|-----|-------------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|--|

| 24.04        | U-0 | U-0 | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |  |  |

| 31:24        | —   | —   | —                       | _                 | _                 | —                 |                           | _                |  |  |  |  |

| 00.40        | U-0 | U-0 | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |  |  |

| 23:16        | —   | —   | —                       | —                 | —                 | —                 |                           | —                |  |  |  |  |

| 45.0         | U-0 | U-0 | U-0                     | U-0               | U-0               | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |

| 15:8         | _   | —   |                         | _                 | _                 | S                 | SRIPL<2:0> <sup>(1)</sup> |                  |  |  |  |  |

| 7.0          | U-0 | U-0 | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |

| 7:0          | _   |     | VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                           |                  |  |  |  |  |

#### REGISTER 5-2: INTSTAT: INTERRUPT STATUS REGISTER

#### Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **SRIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 **Unimplemented:** Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|----------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | IPTMR<31:24>                     |       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | IPTMR<23:16>                     |       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | IPTMR<15:8>                      |       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                                  |       |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 5-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | _                | —                    |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |

| 23:16        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                    |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |

| 10.0         | —                 | _                 |                   | —                 | _                 |                   | —                | _                    |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |  |  |  |  |

### REGISTER 7-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by har | dware                |                    |

|-------------------|---------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section

6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

### 8.1 Control Registers

| TAB                         | LE 8-1:                                                      | 08        | SCILL | ATOR  | CONFI   | GURATI     | ON RE   | GISTE | R MAP     |        |         |         |          |            |      |                       |        |                     |            |

|-----------------------------|--------------------------------------------------------------|-----------|-------|-------|---------|------------|---------|-------|-----------|--------|---------|---------|----------|------------|------|-----------------------|--------|---------------------|------------|

| ess                         |                                                              | 0         |       | Bits  |         |            |         |       |           |        |         |         |          |            | s    |                       |        |                     |            |

| Virtual Address<br>(BF80_#) | Virtual Addr<br>(BF80_#)<br>(BF80_#)<br>(BF80_#)<br>(BF80_#) | Bit Range | 31/15 | 30/14 | 29/13   | 28/12      | 27/11   | 26/10 | 25/9      | 24/8   | 23/7    | 22/6    | 21/5     | 20/4       | 19/3 | 18/2                  | 17/1   | 16/0                | All Resets |

| F000                        | OSCCON                                                       | 31:16     | _     | —     | PI      | LLODIV<2:0 | >       |       | FRCDIV<2: | 0>     | —       | SOSCRDY | PBDIVRDY | PBDIV<1:0> |      | PLLMULT<2:0>          |        | x1xx <sup>(2)</sup> |            |

| F000                        | USCCON .                                                     | 15:0      | —     |       | COSC<2: | 0>         | —       |       | NOSC<2:0  | >      | CLKLOCK | ULOCK   | SLOCK    | SLPEN      | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN               | xxxx(2)    |

| F010                        | OSCTUN                                                       | 31:16     | _     | _     | _       | —          | _       | _     | —         | _      | —       | —       | _        | _          |      | —                     | _      | —                   | 0000       |

| 1010                        | 030101                                                       | 15:0      | —     |       |         | _          | —       | _     | —         | —      | _       | _       |          |            | TUT  | N<5:0>                |        |                     | 0000       |

| 5000                        | REFOCON                                                      | 31:16     | —     |       |         |            |         |       |           |        | RODIV<  | 14:0>   |          |            |      |                       |        |                     | 0000       |

| F020                        | REFUCUN                                                      | 15:0      | ON    | —     | SIDL    | OE         | RSLP    | —     | DIVSWEN   | ACTIVE | —       | -       | —        | —          |      | ROSE                  | L<3:0> |                     | 0000       |

| 5000                        | REFOTRIM                                                     | 31:16     |       |       |         |            | ROTRIM< | 8:0>  |           |        |         | -       | _        | _          | —    | —                     | —      | —                   | 0000       |

| F030                        |                                                              | 15:0      | _     | _     | -       | _          | —       | _     | _         | _      | —       | _       | _        | _          | _    | —                     | _      | —                   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on devices with a USB module.

.....

### 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

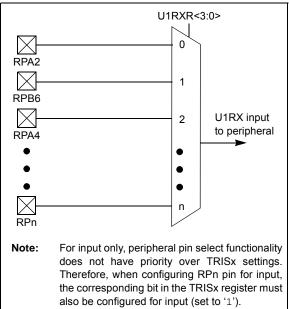

#### 11.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

# FIGURE 11-2: REI

REMAPPABLE INPUT EXAMPLE FOR U1RX

|                             | PIC32MX170F512H DEVICES ONLY    |           |       |       |       |       |       |       |      |      |      |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |       |       |       |       |       |       |      | Bi   | ts   |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510 TRISF<br>6520 PORTF    | TRISE                           | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | -    | —            |              | _            | _            | _            | —            | —            | 0000          |

|                             | INIO                            | 15:0      | —     | _     | _     | _     | _     | _     | -    | _    | -    | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 007F          |

|                             | PORTE                           | 31:16     | —     | —     | —     |       | —     | _     |      |      |      |              | —            |              | —            | —            | —            | —            | 0000          |

| 0020                        | 1 OKI                           | 15:0      | —     | —     | —     |       | —     | _     | _    |      |      | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | _     | _     | _     | _     | _     | -    | _    | -    | —            | —            | -            | —            | _            | —            | —            | 0000          |

| 0000                        | L/(II                           | 15:0      | —     | —     | —     |       | —     | _     | _    |      |      | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | —     | —     | —     | _     | —     | _     | —    |      | —    |              | —            | _            | —            | —            | —            | —            | 0000          |

| 0010                        | 0201                            | 15:0      | —     | —     | —     | _     | —     | _     | —    |      | —    | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | —     | _     | —     | —     | —     | _     | _    | —    | _    |              | —            | —            | —            | —            | —            | —            | 0000          |

| 0000                        |                                 | 15:0      | —     | _     | —     | —     | —     | _     | _    | —    | _    | CNPUF6       | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       |               |

| 6560                        | CNPDF                           | 31:16     | —     | —     | —     | _     | —     | _     | —    |      | —    |              | —            | —            | —            | —            | —            | —            | 0000          |

|                             | 0.11 51                         | 15:0      | —     | —     | —     | _     | —     | —     | -    | —    | -    | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | —     | —     | —     | _     | —     | —     | -    | —    | -    | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             | 0.10011                         | 15:0      | ON    | —     | SIDL  | _     | —     | —     | -    | —    | -    | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —     | —     | _     | —     | —     | -    | —    | -    |              | —            | —            | —            | —            | —            | —            | 0000          |

|                             | -                               | 15:0      | —     | —     | —     | _     | —     | —     | -    | —    | -    | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | —     | _     | —     | —     | —     | _     | _    | —    | _    |              | —            | —            | —            | —            | —            | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | —     | —     | —     | -     | —     | -     | -    | —    | _    | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

# TABLE 11-13: PORTF REGISTER MAP FOR PIC32MX120F064H, PIC32MX130F128H, PIC32MX150F256H, AND PIC32MX170F512H DEVICES ONLY

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### TABLE 11-16: PORTG REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |              | В            | its          |              |      |      |                    |                    |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1 | 16/0 | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | _     | _     | —     | _     | _     | —     | —            |              | —            | —            | _    | —    | —                  | —                  |      | —    | 0000          |

| 0000                        | ANOLLO                          | 15:0      | —     | —     | —     | —     | —     | —     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | —    | —    | —                  | —                  | —    | —    | 03C0          |

| 6610                        | TRISG                           | 31:16     | —     | _     | —     | —     | _     | —     | _            | —            | _            | —            | _    | _    | _                  | —                  | _    | _    | 0000          |

| 0010                        | TRIBG                           | 15:0      | _     | _     | _     | _     | _     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | —    | TRISG3             | TRISG2             | _    | —    | 03CC          |

| 6620                        | PORTG                           | 31:16     | -     |       |       | _     |       |       | _            | _            |              | —            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0020                        | FURIG                           | 15:0      | _     | _     | _     | _     | _     | _     | RG9          | RG8          | RG7          | RG6          | _    | —    | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | _    | —    | xxxx          |

| 6630                        | LATG                            | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0030                        | LAIG                            | 15:0      | Ι     | -     | -     |       |       |       | LATG9        | LATG8        | LATG7        | LATG6        | —    | —    | LATG3              | LATG2              | —    | —    | XXXX          |

| 6640                        | ODCG                            | 31:16     | Ι     | -     | -     |       |       |       | —            | —            | -            | —            | —    | —    | —                  | —                  | —    | —    | 0000          |

| 0040                        | ODCG                            | 15:0      | -     | -     | -     | -     |       |       | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | _    | _    | 0000          |

| 6650                        | CNPUG                           | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0030                        | CINFUG                          | 15:0      | -     | -     | -     | -     |       |       | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | CNPUG3             | CNPUG2             | _    | _    | 0000          |

| 6660                        | CNPDG                           | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0000                        | CINF DG                         | 15:0      | -     | -     | -     | -     |       |       | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | _    | CNPDG3             | CNPDG2             | _    | _    | 0000          |

| 6670                        | CNCONG                          | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0070                        | CINCOING                        | 15:0      | ON    | -     | SIDL  | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 6680                        | CNENG                           | 31:16     | —     | _     | _     | _     | _     |       | —            | —            |              | —            | —    | _    | —                  | —                  | —    | _    | 0000          |

| 0000                        | GNEING                          | 15:0      | —     | _     | _     | _     |       | -     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | —    | —    | CNIEG3             | CNIEG2             |      | —    | 0000          |

|                             |                                 | 31:16     | —     | _     | —     | —     | _     | _     | _            | _            | _            | —            | —    | —    | _                  | _                  | —    | —    | 0000          |

| 6690                        | CNSTATG                         | 15:0      | _     | _     | _     | _     | _     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | _    | _    | CN<br>STATG3       | CN<br>STATG2       | _    | _    | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This bit is only available on devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 |                   | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   |                   | _                 | _                 | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | —                 | _                | _                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE —           |                   | TCKPS<1:0>        |                   | _                 | TSYNC             | TCS              | _                |

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| 011 31-10 | Unimplemented: Read as 0                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

|           | 1 = Timer is enabled                                                                                                                                                           |

|           | 0 = Timer is disabled                                                                                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                    |

|           | 1 = Discontinue operation when device enters Idle mode                                                                                                                         |

|           | 0 = Continue operation even in Idle mode                                                                                                                                       |

| bit 12    | TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

|           | <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| bit 11    | TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

|           | In Asynchronous Timer mode:                                                                                                                                                    |

|           | 1 = Asynchronous write to TMR1 register in progress                                                                                                                            |

|           | 0 = Asynchronous write to TMR1 register complete                                                                                                                               |

|           | In Synchronous Timer mode:<br>This bit is read as '0'.                                                                                                                         |

| bit 10-8  | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 7     | TGATE: Timer Gated Time Accumulation Enable bit                                                                                                                                |

|           | When TCS = 1:                                                                                                                                                                  |

|           | This bit is ignored.                                                                                                                                                           |

|           | When TCS = 0:<br>1 = Gated time accumulation is enabled                                                                                                                        |

|           | 0 = Gated time accumulation is enabled                                                                                                                                         |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 5-4   | TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

|           | 11 = 1:256 prescale value                                                                                                                                                      |

|           | 10 = 1:64 prescale value                                                                                                                                                       |

|           | 01 = 1:8 prescale value<br>00 = 1:1 prescale value                                                                                                                             |

| bit 3     | Unimplemented: Read as '0'                                                                                                                                                     |

| DIL J     | ommplemented. Read as 0                                                                                                                                                        |

|           |                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

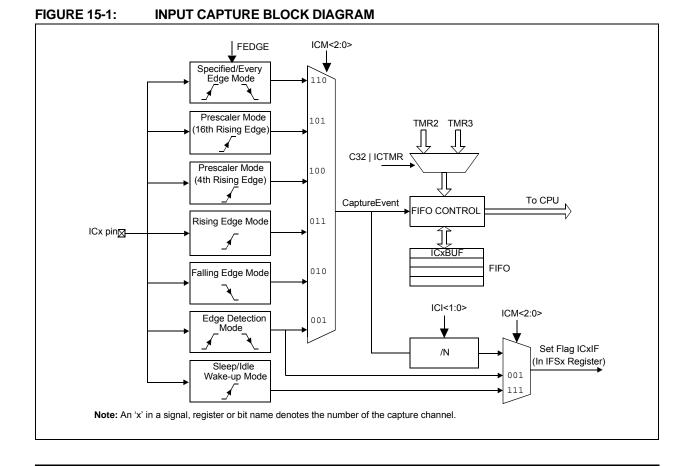

### 15.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

The other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

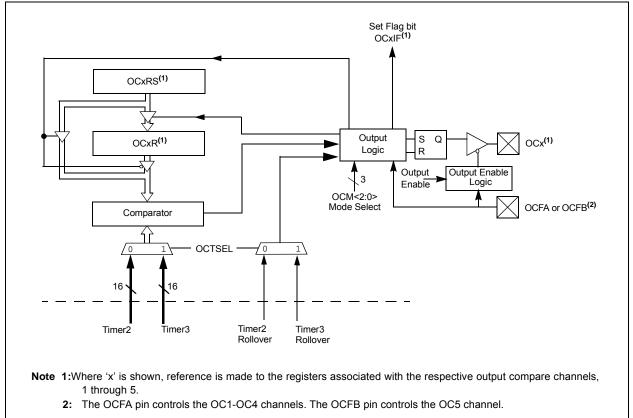

### 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are the key features of this module:

- · Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

#### FIGURE 16-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | _                 | _                 | —                    | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

# **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

NOTES:

|                                                 | LE 19-1:                 | 1: UARTI THROUGH UARTS REGISTER MAP (CONTINUED) |        |         |        |       |        |       |       |             |             |         |       |          |          |      |        |       |            |

|-------------------------------------------------|--------------------------|-------------------------------------------------|--------|---------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|------|--------|-------|------------|

| ess                                             |                          | đ                                               |        |         |        |       |        |       |       | Bi          | ts          |         |       |          |          |      |        |       | s          |

| Virtual Address<br>(BF80_#)                     | Register<br>Name         | Bit Range                                       | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6440                                            |                          | 31:16                                           | _      | —       | —      |       | —      |       | —     | —           |             | —       | _     |          | _        | _    | _      |       | 0000       |

| 0440                                            | USBRG. /                 | 15:0                                            |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 6600                                            | U4MODE <sup>(1)</sup>    | 31:16                                           | _      | _       | _      |       | _      |       | _     | _           |             | —       | _     |          | _        | _    | _      |       | 0000       |

| 0000                                            | 04IVIODL.                | 15:0                                            | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6610                                            | U4STA <sup>(1)</sup>     | 31:16                                           | _      | —       | —      | -     | —      | _     | —     | ADM_EN      |             |         |       | ADDF     | R<7:0>   |      | -      |       | 0000       |

| 0010                                            | 04017                    | 15:0                                            | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6620                                            | U4TXREG                  | 31:16                                           | —      |         | —      | _     | _      | _     |       | —           |             | —       | —     | _        | —        | —    | —      | —     | 0000       |

|                                                 | OFINICO                  | 15:0                                            | —      |         | —      | _     | _      | _     |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 6630                                            | U4RXREG                  | 31:16                                           | —      |         | —      | _     | _      | _     |       | _           |             | —       | _     | _        | _        | _    | _      | —     | 0000       |

| 0000                                            | OHIVILO                  | 15:0                                            | —      |         | —      | _     | _      | _     |       | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                                            | U4BRG <sup>(1)</sup>     | 31:16                                           | —      | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                                            | U IBIKO                  | 15:0                                            |        |         |        |       |        |       | Bau   | d Rate Gen  | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 6800                                            | U5MODE <sup>(1,2)</sup>  | 31:16                                           |        | —       | —      |       | —      | _     | —     |             |             | —       | _     |          | —        | —    | —      |       | 0000       |

|                                                 | 00111022                 | 15:0                                            | ON     | —       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                                            | U5STA <sup>(1,2)</sup>   | 31:16                                           | —      | —       | —      | —     | —      | —     | —     | ADM_EN      |             |         |       | 1        | R<7:0>   | 1    | 1      | 1     | 0000       |

|                                                 |                          | 15:0                                            | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6820                                            | U5TXREG <sup>(1,2)</sup> | 31:16                                           | _      |         | —      | _     | —      |       |       |             | _           | —       | —     | —        |          | —    |        |       | 0000       |

|                                                 |                          | 15:0                                            | _      |         | —      | _     | —      |       |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 6830 U5RXREG <sup>(1,2)</sup>                   |                          | 31:16                                           | _      |         | —      | —     | —      |       |       | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

|                                                 |                          | 1010                                            | —      |         | —      | —     | —      |       |       | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 6840                                            | U5BRG <sup>(1,2)</sup>   | 31:16                                           | —      | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —    | —      |       | 0000       |

| 15:0     Baud Rate Generator Prescaler     0000 |                          |                                                 |        |         |        |       |        |       |       |             |             |         |       |          |          |      |        |       |            |

#### TABLE 19-1: UART1 THROUGH UART5 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              |                   |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

#### 27.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### 27.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

| DC CHA                                | DC CHARACTERISTICS     |         |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                     |  |  |  |  |  |  |  |

|---------------------------------------|------------------------|---------|-------|------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units | Conditions                                           |                                                     |  |  |  |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |       |                                                      |                                                     |  |  |  |  |  |  |  |

| DC40k                                 | 33                     | 78      | μA    | -40°C                                                |                                                     |  |  |  |  |  |  |  |

| DC40I                                 | 49                     | 78      | μA    | +25°C                                                | Base Power-Down Current                             |  |  |  |  |  |  |  |

| DC40n                                 | 281                    | 450     | μA    | +85°C                                                | Base Fower-Down Current                             |  |  |  |  |  |  |  |

| DC40m                                 | 559                    | 895     | μA    | +105°C                                               |                                                     |  |  |  |  |  |  |  |

| Module                                | Differential           | Current |       |                                                      |                                                     |  |  |  |  |  |  |  |

| DC41e                                 | 10                     | 25      | μA    | 3.6V                                                 | Watchdog Timer Current: AIWDT (Note 3)              |  |  |  |  |  |  |  |

| DC42e                                 | 29                     | 50      | μA    | 3.6V                                                 | 3.6V RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3 |  |  |  |  |  |  |  |

| DC43d                                 | 1000                   | 1300    | μA    | 3.6V ADC: ∆IADC (Notes 3,4)                          |                                                     |  |  |  |  |  |  |  |

#### TABLE 31-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8