Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: |        | ess the docume  |            |          |

|-------|--------|-----------------|------------|----------|

|       | browse | to the docume   | ntation se | ction of |

|       | the    | Microchip       | web        | site     |

|       | (www.n | nicrochip.com). |            |          |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

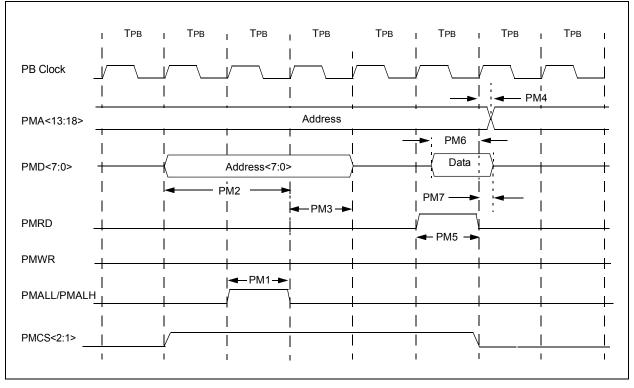

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

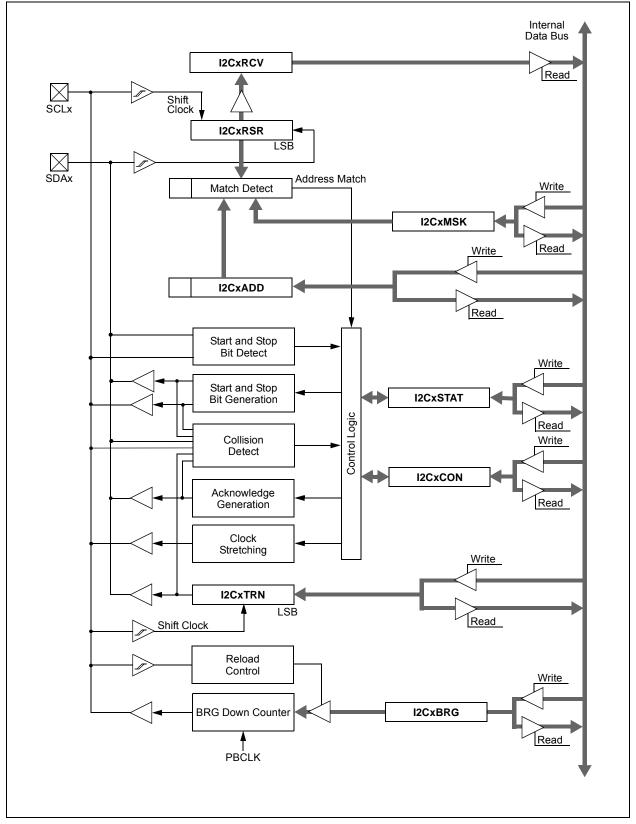

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- · Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001123)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

|          | Pin N                  | umber           |             |                |                        |

|----------|------------------------|-----------------|-------------|----------------|------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description            |

| AN0      | 16                     | 25              | Ι           | Analog         |                        |

| AN1      | 15                     | 24              | Ι           | Analog         |                        |

| AN2      | 14                     | 23              | Ι           | Analog         |                        |

| AN3      | 13                     | 22              | Ι           | Analog         |                        |

| AN4      | 12                     | 21              | Ι           | Analog         |                        |

| AN5      | 11                     | 20              | I           | Analog         |                        |

| AN6      | 17                     | 26              | Ι           | Analog         |                        |

| AN7      | 18                     | 27              | I           | Analog         |                        |

| AN8      | 21                     | 32              | I           | Analog         |                        |

| AN9      | 22                     | 33              | Ι           | Analog         |                        |

| AN10     | 23                     | 34              | Ι           | Analog         |                        |

| AN11     | 24                     | 35              | I           | Analog         |                        |

| AN12     | 27                     | 41              | Ι           | Analog         |                        |

| AN13     | 28                     | 42              | Ι           | Analog         |                        |

| AN14     | 29                     | 43              | I           | Analog         |                        |

| AN15     | 30                     | 44              | Ι           | Analog         |                        |

| AN16     | 4                      | 10              | I           | Analog         |                        |

| AN17     | 5                      | 11              | I           | Analog         |                        |

| AN18     | 6                      | 12              | Ι           | Analog         | Analog input channels. |

| AN19     | 8                      | 14              | Ι           | Analog         |                        |

| AN20     | 62                     | 98              | I           | Analog         |                        |

| AN21     | 64                     | 100             | Ι           | Analog         |                        |

| AN22     | 1                      | 3               | I           | Analog         |                        |

| AN23     | 2                      | 4               | Ι           | Analog         |                        |

| AN24     | 49                     | 76              | Ι           | Analog         |                        |

| AN25     | 50                     | 77              | Ι           | Analog         |                        |

| AN26     | 51                     | 78              | I           | Analog         |                        |

| AN27     | 3                      | 5               | I           | Analog         |                        |

| AN28     |                        | 1               | Ι           | Analog         |                        |

| AN29     | —                      | 6               | Ι           | Analog         |                        |

| AN30     | _                      | 7               | I           | Analog         |                        |

| AN31     |                        | 8               | Ι           | Analog         |                        |

| AN32     | _                      | 18              | I           | Analog         |                        |

| AN33     | _                      | 19              | Ι           | Analog         |                        |

| AN34     |                        | 39              | Ι           | Analog         |                        |

| AN35     |                        | 40              |             | Analog         | 1                      |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

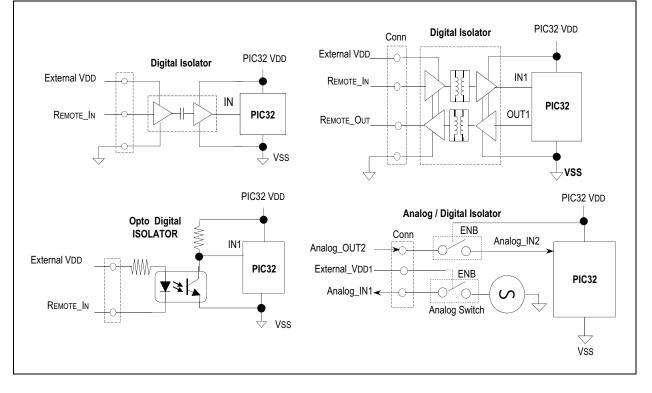

Without proper signal isolation, on non-5V tolerant pins, the remote signal can power the PIC32 device through the high side ESD protection diodes. Besides violating the absolute maximum rating specification when VDD of the PIC32 device is restored and ramping up or ramping down, it can also negatively affect the internal Power-on Reset (POR) and Brown-out Reset (BOR) circuits, which can lead to improper initialization of internal PIC32 logic circuits. In these cases, it is recommended to implement digital or analog signal isolation as depicted in Figure 2-6, as appropriate. This is indicative of all industry microcontrollers and not just Microchip products.

## TABLE 2-1: EXAMPLES OF DIGITAL/ ANALOG ISOLATORS WITH OPTIONAL LEVEL TRANSLATION

| Example Digital/Analog<br>Signal Isolation Circuits | Inductive Coupling | Capacitive Coupling | Opto Coupling | Analog/Digital Switch |

|-----------------------------------------------------|--------------------|---------------------|---------------|-----------------------|

| ADuM7241 / 40 ARZ (1 Mbps)                          | Х                  |                     | _             |                       |

| ADuM7241 / 40 CRZ (25 Mbps)                         | Х                  |                     |               | _                     |

| IS0721                                              |                    | Х                   |               | _                     |

| LTV-829S (2 Channel)                                | _                  |                     | Х             | _                     |

| LTV-849S (4 Channel)                                | _                  |                     | Х             | _                     |

| FSA266 / NC7WB66                                    | _                  |                     |               | Х                     |

## FIGURE 2-6: DIGITAL/ANALOG SIGNAL ISOLATION CIRCUITS

## 4.3 Control Registers

Register 4-1 through Register 4-8 are used for setting the RAM and Flash memory partitions for data and code.

|                                   | ER 4-1: I                                                                                    |                                                  | •••                             |                   | RATION RE                          |                         |                  |                  |  |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------|-------------------|------------------------------------|-------------------------|------------------|------------------|--|--|--|--|--|--|

| Bit<br>Range                      | Bit<br>31/23/15/7                                                                            | Bit<br>30/22/14/6                                | Bit<br>29/21/13/5               | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

| 31:24                             | U-0                                                                                          | U-0                                              | U-0                             | U-0               | U-0                                | U-0                     | U-0              | U-0              |  |  |  |  |  |  |

| 31:24                             | —                                                                                            | -                                                | —                               | —                 | —                                  | _                       | —                | _                |  |  |  |  |  |  |

|                                   | U-0                                                                                          | U-0                                              | U-0                             | R/W-1             | R/W-1                              | R/W-1                   | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 23:16                             | —                                                                                            | —                                                | —                               | BMX<br>ERRIXI     | BMX<br>ERRICD                      | BMX<br>ERRDMA           | BMX<br>ERRDS     | BMX<br>ERRIS     |  |  |  |  |  |  |

| 15:8                              | U-0                                                                                          | U-0                                              | U-0                             | U-0               | U-0                                | U-0                     | U-0              | U-0              |  |  |  |  |  |  |

|                                   | U-0                                                                                          | R/W-1                                            | U-0                             | U-0               | U-0                                | R/W-0                   | R/W-0            | R/W-1            |  |  |  |  |  |  |

| 7:0                               | BMX<br>WSDRM     -     -     BMXARB<2:0>                                                     |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

| Legend:<br>R = Reac<br>-n = Value |                                                                                              |                                                  | W = Writable<br>'1' = Bit is se |                   | U = Unimplei<br>'0' = Bit is cle   | mented bit, re<br>eared | ad as '0'        |                  |  |  |  |  |  |  |

| bit 31-21                         | Unimpleme                                                                                    | nted: Read a                                     | <b>s</b> '0'                    |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

| bit 20                            | BMXERRIXI: Enable Bus Error from IXI bit                                                     |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus  |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

| bit 19                            | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                          |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 1 = Enable bus error exceptions for unmapped address accesses initiated from ICD             |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 0 = Disable bus error exceptions for unmapped address accesses initiated from ICD            |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

| bit 18                            | BMXERRD                                                                                      | MA: Bus Error                                    | from DMA bi                     | t                 |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 1 = Enable I                                                                                 | ous error exce                                   | ptions for unr                  | mapped addre      | ess accesses i                     | nitiated from I         | DMA              |                  |  |  |  |  |  |  |

|                                   | 0 = Disable                                                                                  | bus error exce                                   | eptions for un                  | mapped addr       | ess accesses                       | initiated from          | DMA              |                  |  |  |  |  |  |  |

| bit 17                            |                                                                                              |                                                  |                                 |                   | disabled in De                     |                         |                  |                  |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ess accesses i                     |                         | CPU data acc     | ess              |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ess accesses                       |                         |                  |                  |  |  |  |  |  |  |

| bit 16                            |                                                                                              |                                                  |                                 |                   | bit (disabled i                    |                         |                  |                  |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ess accesses i                     |                         |                  | on access        |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ess accesses                       |                         |                  |                  |  |  |  |  |  |  |

| bit 15-7                          |                                                                                              | nted: Read a                                     |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

| bit 6                             | -                                                                                            |                                                  |                                 | Access from       | Data RAM Wa                        | ait State bit           |                  |                  |  |  |  |  |  |  |

|                                   | -                                                                                            |                                                  |                                 |                   | ate for address                    |                         |                  |                  |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ates for addre                     |                         |                  |                  |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

| DIT 5-3                           | -                                                                                            |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | Unimplemented: Read as '0'<br>BMXARB<2:0>: Bus Matrix Arbitration Mode bits                  |                                                  |                                 |                   |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ill produce un                     | defined behav           | vior)            |                  |  |  |  |  |  |  |

|                                   |                                                                                              |                                                  |                                 |                   | ill produce und                    | defined behav           | ior)             |                  |  |  |  |  |  |  |

| bit 2-0                           |                                                                                              |                                                  |                                 |                   | ill produce und                    | defined behav           | ior)             |                  |  |  |  |  |  |  |

| bit 5-3<br>bit 2-0                | 111 = Rese                                                                                   | rved (using th                                   | ese configura                   | tion modes w      |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 111 = Rese<br>011 = Rese                                                                     | rved (using th<br>rved (using th                 | ese configura                   | tion modes w      | ill produce und<br>ill produce und |                         |                  |                  |  |  |  |  |  |  |

|                                   | 111 = Rese                                                                                   | rved (using th<br>rved (using th<br>ation Mode 2 | ese configura<br>ese configura  | tion modes w      |                                    |                         |                  |                  |  |  |  |  |  |  |

|                                   | 111 = Rese<br><br>011 = Rese<br>010 = Arbitr<br>001 = Arbitr                                 | rved (using th<br>rved (using th                 | ese configura<br>ese configura  | tion modes w      |                                    |                         |                  |                  |  |  |  |  |  |  |

## REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

## 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX1XX/2XX/5XX 64/100-pin devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX1XX/2XX/5XX 64/100-pin devices, the Flash page size is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| REGISTER 8-2: OSCTUN: FRC TUNING REGISTER |

|-------------------------------------------|

|-------------------------------------------|

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0 U-0 U-0       |                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | -                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0 U-0           |                   | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## TABLE 9-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |              | Ô             |             |                                                          |       |       |        |       |      | Bi     | ts      |        |        |        |         |        |        |        |            |

|-----------------------------|--------------|---------------|-------------|----------------------------------------------------------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) |              | Bit Range     | 31/15       | 30/14                                                    | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR     | 31:16         | —           | _                                                        | _     | _     |        | -     | —    | _      | -       | -      | —      | _      | —       | -      | —      | —      | 0000       |

| 0200                        |              | 15:0          |             |                                                          |       |       |        |       |      | CHCPTI | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3290                        | DCH2DAT      | 31:16         | 3           |                                                          |       |       |        |       |      |        |         |        | —      | 0000   |         |        |        |        |            |

| 5290                        | DCH2DAI      | 15:0          | CHPDAT<7:0> |                                                          |       |       |        |       |      |        |         |        |        | 0000   |         |        |        |        |            |

| 3240                        | DCH3CON      | 31:16         |             |                                                          |       |       |        |       |      |        |         |        | _      | 0000   |         |        |        |        |            |

| 32AU                        | DCH3CON      | 15:0          | CHBUSY      | CHBUSY CHCHNS CHEN CHAED CHCHN CHAEN - CHEDET CHPRI<1:0> |       |       |        |       |      |        |         |        |        |        | <1:0>   | 0000   |        |        |            |

| 32B0                        | DCH3ECON     | 31:16         | —           |                                                          |       |       |        |       |      |        |         |        |        |        |         | 00FF   |        |        |            |

| 0200                        | DONOLOON     | 15:0          |             |                                                          |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | _      |        |        | FFF8       |

| 32C0                        | DCH3INT      | 31:16         | —           | —                                                        | _     | —     | _      | _     | —    |        | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | Donom        | 15:0          | —           | —                                                        | —     | —     | —      | —     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF |            |

| 32D0                        | DCH3SSA      | 31:16         |             | CHSSA<31:D>                                              |       |       |        |       |      |        |         |        |        |        |         | 0000   |        |        |            |

|                             |              | 15:0<br>31:16 |             |                                                          |       |       |        |       |      |        |         |        |        |        |         |        |        |        | 0000       |

| 32E0                        | DCH3DSA      | 15:0          |             |                                                          |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 0000       |

| 2250                        | DCH3SSIZ     | 31:16         | _           | _                                                        | _     |       | _      | _     | —    | _      | _       | _      | —      |        | —       | _      | —      | —      | 0000       |

| 32FU                        | DCH333IZ     | 15:0          |             |                                                          |       |       |        |       |      | CHSSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3300                        | DCH3DSIZ     | 31:16         | _           | _                                                        | _     |       |        |       | —    | -      |         |        | _      | _      | _       |        | —      | _      | 0000       |

| 3300                        | DCI ISD3IZ   | 15:0          |             |                                                          |       |       |        |       |      | CHDSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3310                        | DCH3SPTR     | 31:16         | —           | _                                                        | —     | _     | -      | -     | —    | _      | _       | -      | —      | _      | —       | -      | —      | —      | 0000       |

| 3310                        | Denisor IIX  | 15:0          |             |                                                          |       |       |        |       |      | CHSPT  | R<15:0> |        | -      |        |         |        |        | -      | 0000       |

| 3320                        | DCH3DPTR     | 31:16         | —           | —                                                        | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —       | —      | —      |        | 0000       |

| 0020                        | DOI 10DI 111 | 15:0          |             |                                                          |       |       |        |       |      | CHDPTI | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3330                        | DCH3CSIZ     | 31:16         | _           | _                                                        |       | _     | —      | _     | —    | —      | _       | —      | _      |        | —       | —      | —      | —      | 0000       |

|                             |              | 15:0          |             |                                                          |       |       |        |       |      | CHCSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3340                        | DCH3CPTR     | 31:16         | —           | —                                                        | —     | —     | —      | —     | —    | —      | —       | —      | —      | _      | —       | —      | —      | —      | 0000       |

|                             |              | 15:0          |             |                                                          |       |       |        |       |      | CHCPTI | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3350                        | DCH3DAT      | 31:16         | —           | —                                                        | —     | —     | _      | _     | —    | —      | —       | —      | —      | _      | —       | —      | —      | —      | 0000       |

| 2000                        | _ 5.165.11   | 15:0          |             | _                                                        |       | _     |        | —     | —    |        |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| ILCIOID L    | . N 0 4. D        | CINCCON. D            |                   |                   |                    |                   |                  |                  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | —                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                     | —                 | -                 | —                  | _                 | -                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0 R/          |                       | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | -                 | —                  | (                 | CRCCH<2:0>       |                  |

## REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

## Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(1</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

## <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

## bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

## TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                                                            |           |       |       |       |       |       |       |      |      |      | Bit  | s    |      |          |        |        |         |            | 6    |

|----------------------------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|----------|--------|--------|---------|------------|------|

| Virtual Address<br>(BF88_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3     | 18/2   | 17/1   | 16/0    | All Resets |      |

| 5390                                                           | U1EP9     | 31:16 | _     | —     |       | —     | _     | _    | —    | _    |      | _    | —    | —        | -      | -      | —       |            | 0000 |

| 5390                                                           | UIEF9     | 15:0  |       |       |       | _     | _     | _    | —    | _    | -    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

| 5240                                                           | U1EP10    | 31:16 | _     | _     |       | _     |       |      | _    |      | _    |      | _    | —        | -      |        | —       |            | 0000 |

| 53A0 U1EP10                                                    | UIEFIU    | 15:0  | Ι     | Ι     |       | _     | -     | -    | _    | _    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

| 53B0                                                           | U1EP11    | 31:16 | _     | _     | _     |       | _     | _    | —    | _    | _    | _    | —    | —        | _      | _      | —       | _          | 0000 |

| 53BU                                                           | UIEPII    | 15:0  | _     | _     | _     |       | _     | _    | —    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

| 53C0                                                           | U1EP12    | 31:16 | _     | _     | _     |       | _     | _    | —    | _    | _    | _    | —    | —        | _      | _      | —       | _          | 0000 |

| 5500                                                           | UIEF12    | 15:0  | Ι     | —     | —     | _     | —     | —    | _    | —    | —    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

| 53D0                                                           | U1EP13    | 31:16 | Ι     | —     | —     | _     | —     | —    | _    | —    | —    | _    | _    | —        | —      | —      | —       | —          | 0000 |

| 55D0                                                           | UIEF 13   | 15:0  | Ι     | —     | —     | _     | —     | —    | _    | —    | —    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

| 5050                                                           |           | 31:16 |       | _     | _     | _     | _     | _    | _    | _    | _    | _    | -    | _        | _      | _      | _       | _          | 0000 |

| 53E0                                                           | U1EP14    | 15:0  | _     | _     |       |       | _     | _    | _    | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

| 5050                                                           |           | 31:16 | _     | _     | _     | _     | _     | _    | _    |      |      | _    | _    |          | _      | _      | _       | _          | 0000 |

| 53F0                                                           | U1EP15    | 15:0  | _     | _     | _     | _     | _     | _    | _    |      |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK     | 0000 |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

## 11.0 I/O PORTS

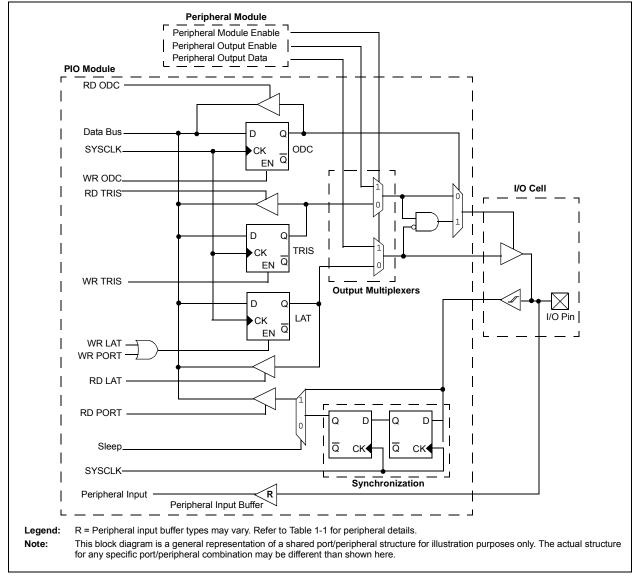

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

The following are the key features of this module:

- · Individual output pin open-drain enable or disable

- Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt

when change in pin state is detected

- Operation during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

## TABLE 11-15: PORTG REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 |           |               |               |               |               |       |       |              | Bits         | 5            |              |      |      |                    |                    |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1         | 16/0         | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     |               | -             | —             | —             | _     | _     | —            | _            |              | —            | —    |      |                    | —                  |              |              | 0000          |

| 0000                        | JUIGEEO                         | 15:0      | ANSELG15      | _             |               | —             | —     | —     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | —    | _    |                    | _                  | _            |              | 83C0          |

| 6610                        | TRISG                           | 31:16     | —             | _             | _             | —             | —     | —     | —            | —            | _            | —            | _    | _    | _                  | _                  | _            | _            | 0000          |

| 0010                        | TRISO                           | 15:0      | TRISG15       | TRISG14       | TRISG13       | TRISG12       | —     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | _    | TRISG3             | TRISG2             | TRISG1       | TRISG0       | F3CF          |

| 6620                        | PORTG                           | 31:16     |               | -             | —             | _             | -     | —     | -            |              |              | —            | —    | -    | _                  | —                  | -            | —            | 0000          |

| 0020                        | FURIG                           | 15:0      | RG15          | RG14          | RG13          | RG12          |       | _     | RG9          | RG8          | RG7          | RG6          | _    | _    | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | RG1          | RG0          | xxxx          |

| 6620                        | LATG                            | 31:16     | _             | —             | —             | _             | _     | _     | —            | —            | _            | —            | _    | _    | _                  | —                  | _            | —            | 0000          |

| 6630                        | LAIG                            | 15:0      | LATG15        | LATG14        | LATG13        | LATG12        | _     | _     | LATG9        | LATG8        | LATG7        | LATG6        | _    | _    | LATG3              | LATG2              | LATG1        | LATG0        | xxxx          |

| 0040                        | ODCG                            | 31:16     | _             | _             |               | —             | _     | _     | _            | _            | _            | —            | _    | _    | _                  | —                  | -            | —            | 0000          |

| 6640                        | ODCG                            | 15:0      | ODCG15        | ODCG14        | ODCG13        | ODCG12        | _     | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | ODCG1        | ODCG0        | 0000          |

| CCEO                        | CNPUG                           | 31:16     | _             | —             | —             | _             | _     | _     | —            | —            | _            | —            | _    | _    | _                  | —                  | _            | —            | 0000          |

| 6650                        | CNPUG                           | 15:0      | CNPUG15       | CNPUG14       | CNPUG13       | CNPUG12       | _     | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | CNPUG3             | CNPUG2             | CNPUG1       | CNPUG0       | 0000          |

| 0000                        | CNPDG                           | 31:16     | _             | _             | _             | _             | _     | _     | _            | _            | _            |              | _    | _    |                    | _                  | _            | _            | 0000          |

| 6660                        | CNPDG                           | 15:0      | CNPDG15       | CNPDG14       | CNPDG13       | CNPDG12       | _     | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | _    | CNPDG3             | CNPDG2             | CNPDG1       | CNPDG0       | 0000          |

| 0070                        |                                 | 31:16     | _             | _             | _             | _             | _     | _     | _            | _            | _            |              | _    | _    |                    | _                  | _            | _            | 0000          |

| 6670                        | CNCONG                          | 15:0      | ON            | _             | SIDL          | _             | _     | _     | _            | _            | _            | —            | _    | _    | _                  | —                  |              | _            | 0000          |

| 0000                        |                                 | 31:16     | _             | _             | _             | _             | _     | _     | _            | _            | _            | —            | _    | _    | _                  | —                  |              | _            | 0000          |

| 6680                        | CNENG                           | 15:0      | CNIEG15       | CNIEG14       | CNIEG13       | CNIEG12       | _     | —     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | _    | _    | CNIEG3             | CNIEG2             | CNIEG1       | CNIEG0       | 0000          |

|                             |                                 | 31:16     | _             | _             | —             | _             | _     | _     | _            | _            | -            | —            | _    | _    | —                  | —                  | _            | —            | 0000          |

| 6690                        | CNSTATG                         | 15:0      | CN<br>STATG15 | CN<br>STATG14 | CN<br>STATG13 | CN<br>STATG12 | —     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | _    |      | CN<br>STATG3       | CN<br>STATG2       | CN<br>STATG1 | CN<br>STATG0 | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This bit is only available on devices without a USB module.

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PIxCON: SF                       |                          |                   |                                    | <b>D</b> !/       | D:"              | D:/                  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------|-------------------|------------------------------------|-------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit<br>30/22/14/6                | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                            | R/W-0                    | R/W-0             | R/W-0                              | R/W-0             | R/W-0            | R/W-0                |

| 31.24        | FRMEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FRMSYNC                          | FRMPOL                   | MSSEN             | FRMSYPW                            | F                 | RMCNT<2:0        | >                    |

| 23:16        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                              | U-0                      | U-0               | U-0                                | U-0               | R/W-0            | R/W-0                |

| 23.10        | MCLKSEL <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                | _                        | —                 | —                                  | _                 | SPIFE            | ENHBUF <sup>(2</sup> |

| 15:8         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                              | R/W-0                    | R/W-0             | R/W-0                              | R/W-0             | R/W-0            | R/W-0                |

| 15.0         | ON <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                | SIDL                     | DISSDO            | MODE32                             | MODE16            | SMP              | CKE <sup>(3)</sup>   |

| 7.0          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                            | R/W-0                    | R/W-0             | R/W-0                              | R/W-0             | R/W-0            | R/W-0                |

| 7:0          | SSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CKP <sup>(4)</sup>               | MSTEN                    | DISSDI            | STXISE                             | L<1:0>            | SRXIS            | EL<1:0>              |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |                          |                   |                                    |                   |                  |                      |

| R = Read     | lable hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  | W = Writable             | a hit             | U = Unimpler                       | mented hit re     | ad as 'O'        |                      |