Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512h-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: |        | ess the docume  |            |          |

|-------|--------|-----------------|------------|----------|

|       | browse | to the docume   | ntation se | ction of |

|       | the    | Microchip       | web        | site     |

|       | (www.n | nicrochip.com). |            |          |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- · Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001123)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                     | Pin N                    | umber           |             |                |                                                          |  |  |  |  |  |  |

|---------------------|--------------------------|-----------------|-------------|----------------|----------------------------------------------------------|--|--|--|--|--|--|

| Pin Name            | 64-pin<br>QFN/<br>TQFP   | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                              |  |  |  |  |  |  |

| PMA2                | 8                        | 14              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA3                | 6                        | 12              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA4                | 5                        | 11              | 0           | TTL/ST         | -                                                        |  |  |  |  |  |  |

| PMA5                | 4                        | 10              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA6                | 16                       | 29              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA7                | 22                       | 28              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA8                | 32                       | 50              | 0           | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) or |  |  |  |  |  |  |

| PMA9                | 31                       | 49              | 0           | TTL/ST         | Address/Data (Multiplexed Master modes)                  |  |  |  |  |  |  |

| PMA10               | 28                       | 42              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA11               | 27                       | 41              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA12               | 24                       | 35              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA13               | 23                       | 34              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA14               | 45                       | 71              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMA15               | 44                       | 70              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMCS1               | 45                       | 71              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMCS2               | 44                       | 70              | 0           | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD0                | 60                       | 93              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD1                | 61                       | 94              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD2                | 62                       | 98              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD3                | 63                       | 99              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD4                | 64                       | 100             | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD5                | 1                        | 3               | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD6                | 2                        | 4               | I/O         | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) o  |  |  |  |  |  |  |

| PMD7                | 3                        | 5               | I/O         | TTL/ST         | Address/Data (Multiplexed Master modes)                  |  |  |  |  |  |  |

| PMD8                | —                        | 90              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD9                |                          | 89              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD10               | —                        | 88              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD11               | _                        | 87              | I/O         | TTL/ST         |                                                          |  |  |  |  |  |  |

| PMD12               | —                        | 79              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |  |  |

| PMD13               | —                        | 80              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |  |  |

| PMD14               | —                        | 83              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |  |  |

| PMD15               | —                        | 84              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |  |  |

| PMRD                | 53                       | 82              | 0           | —              | Parallel Master Port Read Strobe                         |  |  |  |  |  |  |

| PMWR                | 52                       | 81              | 0           | —              | Parallel Master Port Write Strobe                        |  |  |  |  |  |  |

| VBUS <sup>(2)</sup> | 34                       | 54              | Ι           | Analog         | USB Bus Power Monitor                                    |  |  |  |  |  |  |

| •                   | CMOS = CM<br>ST = Schmit | t Trigger inp   | ut with (   | CMOS level     | ls TTL = TTL input buffer P = Power                      |  |  |  |  |  |  |

|                     | -                        | -               |             |                | t a USB module.<br>USB module.                           |  |  |  |  |  |  |

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 |                   | —                | _                |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 |                  | —                |  |  |  |  |  |

### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

**Note:** While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

# TABLE 9-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 | Ô             |        |       |       |       |        |       |      | Bi     | ts      |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                        | 31:16         | —      | _     | _     | _     |        | -     | —    | _      | -       | -      | —      | _      | —       | -      | —      | —      | 0000       |

| 0200                        |                                 | 15:0          |        |       |       |       |        |       |      | CHCPTI | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | —      | —     | —     | _     | _      | _     | —    | —      | _       | —      | —      | _      | —       | —      | —      | —      | 0000       |

| 5290                        | DCH2DAI                         | 15:0          | _      | —     | —     | _     | _      | _     | —    | —      |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3240                        | DCH3CON                         | 31:16         | _      | _     | _     |       |        |       | _    |        |         |        | _      | _      | _       |        | _      | _      | 0000       |

| 32AU                        | DCH3CON                         | 15:0          | CHBUSY | _     | —     | _     | _      | _     | _    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  |         | CHEDET | CHPR   | l<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16         | —      | —     | —     | —     | —      | —     | —    | —      |         |        | -      | CHAIR  |         |        |        |        | 00FF       |

| 0200                        | DONOLOON                        | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | _      |        |        | FFF8       |

| 32C0                        | DCH3INT                         | 31:16         | —      | —     | _     | —     | _      | _     | —    |        | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | Donom                           | 15:0          | —      | —     | —     | —     | —      | —     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF |            |

| 32D0                        | DCH3SSA                         | 31:16         |        |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0<br>31:16 |        |       |       |       |        |       |      |        |         |        |        |        |         |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 15:0          |        |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 0000       |

| 2250                        | DCH3SSIZ                        | 31:16         | _      | _     | _     |       | _      | _     | —    | _      | _       | _      | —      |        | —       | _      | —      | —      | 0000       |

| 32FU                        | DCH333IZ                        | 15:0          |        |       |       |       |        |       |      | CHSSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3300                        | DCH3DSIZ                        | 31:16         | _      | _     | _     |       |        |       | —    | -      |         |        | _      | _      | _       |        | —      | _      | 0000       |

| 3300                        | DCI ISD3IZ                      | 15:0          |        |       |       |       |        |       |      | CHDSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16         | —      | _     | —     | _     | -      | -     | —    | _      | _       | -      | —      | _      | —       | -      | —      | —      | 0000       |

| 3310                        | Denisor IIX                     | 15:0          |        |       |       |       |        |       |      | CHSPT  | R<15:0> |        | -      |        |         |        |        | -      | 0000       |

| 3320                        | DCH3DPTR                        | 31:16         | —      | —     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —       | —      | —      |        | 0000       |

| 0020                        | DOI 10DI 111                    | 15:0          |        |       |       |       |        |       |      | CHDPTI | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3330                        | DCH3CSIZ                        | 31:16         | _      | _     |       | _     | —      | _     | —    | —      | _       | —      | _      |        | —       | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHCSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         | —      | —     | —     | —     | —      | —     | —    | —      | —       | —      | —      | _      | —       | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHCPTI | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | —      | —     | —     | —     | _      | _     | —    | —      | —       | —      | —      | _      | —       | —      | —      | —      | 0000       |

| 2000                        | _ 5.165.11                      | 15:0          |        | _     |       | _     |        | —     | —    |        |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

|              |                     |                   | -                 |                   |                   |                   |                  |                       |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        | —                   | —                 | —                 | _                 | —                 | _                 | _                | _                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | -                 | —                 | —                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | _                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | —                 | CHEDET            | CHPF             | RI<1:0>               |

#### REGISTER 9-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                                 |                      |                    |

|-------------------|---------------------------------|----------------------|--------------------|

| R = Readable bit  | = Readable bit W = Writable bit |                      | read as '0'        |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

#### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

#### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

#### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### **REGISTER 9-9:** DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

# Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-24<br>bit 23 | Unimplemented: Read as '0'<br>CHSDIE: Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                    |     |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| bit 22              | CHSHIE: Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                            |     |

| bit 21              | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                      |     |

| bit 20              | <b>CHDHIE:</b> Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                 |     |

| bit 19              | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                               |     |

| bit 18              | <b>CHCCIE:</b> Channel Cell Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                |     |

| bit 17              | CHTAIE: Channel Transfer Abort Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                               |     |

| bit 16              | CHERIE: Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                |     |

| bit 15-8            | Unimplemented: Read as '0'                                                                                                                                                 |     |

| bit 7               | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                                                             |     |

|                     | <ul><li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li><li>0 = No interrupt is pending</li></ul>                                               |     |

| bit 6               | <b>CHSHIF:</b> Channel Source Half Empty Interrupt Flag bit<br>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2<br>0 = No interrupt is pending | )   |

| bit 5               | <b>CHDDIF:</b> Channel Destination Done Interrupt Flag bit<br>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDS<br>0 = No interrupt is pending | IZ) |

| © 2014-201          | 6 Microchip Technology Inc. Preliminary                                                                                                                                    | DS  |

# 11.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin, regardless of the output function including PPS remapped output functions to act as an open-drain output. The only exception is the  $l^2C$  pins that are open drain by default.

The open-drain feature allows the presence of outputs higher than  $V_{DD}$  (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default. The ANSELx register bit, when cleared, disables the corresponding digital input buffer pin(s).

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module. The TRISx bits only control the corresponding digital output buffer pin(s).

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level; i.e., when ANSELx = 1; TRISx = x).

Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be an NOP.

### 11.1.4 INPUT CHANGE NOTIFICATION

The input Change Notification (CN) function of the I/O ports allows the PIC32MX1XX/2XX/5XX 64/100-pin devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

#### 11.1.5 INTERNALLY SELECTABLE PULL-UPS AND PULL-DOWNS

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it, which are independent of any other I/O pin functionality (i.e., PPS, Open Drain, or CN). The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

An additional control register (CNCONx) is shown in Register 11-3.

# 11.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection        |

|----------------|-----------------|------------------|-----------------------------------------------------------|

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPD1<br>0001 = RPG9                                |

| тзск           | T3CKR           | T3CKR<3:0>       | 0010 = RPB14<br>0011 = RPD0                               |

| IC1            | IC1R            | IC1R<3:0>        | 0100 = RPD8<br>0101 = RPB6                                |

| U3CTS          | U3CTSR          | U3CTSR<3:0>      | 0110 = RPD5<br>0111 = RPB2                                |

| U4RX           | U4RXR           | U4RXR<3:0>       | 1000 = RPF3 <sup>(4)</sup><br>1001 = RPF13 <sup>(3)</sup> |

| U5RX           | U5RXR           | U5RXR<3:0>       | 1010 = Reserved<br>1011 = RPF2 <sup>(1)</sup>             |

| SS2<br>OCFA    | SS2R            | SS2R<3:0>        | 1100 = RPC2 <sup>(3)</sup><br>1101 = RPE8 <sup>(3)</sup>  |

|                | OCFAR           | OCFAR<3:0>       | 1110 = Reserved<br>1111 = Reserved                        |

### TABLE 11-1:INPUT PIN SELECTION (CONTINUED)

Note 1: This selection is not available on 64-pin USB devices.

- 2: This selection is only available on 100-pin General Purpose devices.

- 3: This selection is not available on 64-pin devices.

- 4: This selection is not available when USBID functionality is used on USB devices.

- 5: This selection is not available on devices without a CAN module.

- 6: This selection is not available on USB devices.

- 7: This selection is not available when VBUSON functionality is used on USB devices.

#### TABLE 11-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(3)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0101 = Reserved                              |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 <b>= SDO1</b>                           |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(3)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(3)</sup> | RPD12R   | RPD12R<3:0> | 1011 = OC5<br>1100 = Reserved                |

| RPF8 <sup>(3)</sup>  | RPF8R    | RPF8R<3:0>  | 1101 = C1OUT                                 |

| RPC3 <sup>(3)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 <b>=</b> <del>SS3</del>                 |

| RPE9 <sup>(3)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = SS4 <sup>(3)</sup>                    |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(3)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(1)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(2)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(3)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(3)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(3)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(1)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

### TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                         |                  |           |       |       |       |       |       |       |      | Bi   | its  |      |      |      |           |      |        |      |            |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|-----------|------|--------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3      | 18/2 | 17/1   | 16/0 | All Resets |

| 5004                       | RPG1R            | 31:16     |       | _     |       |       | —     | _     | _    |      | _    |      | —    | _    |           | _    |        | —    | 0000       |

| FC04                       | RPGIR            | 15:0      | —     | —     | _     | _     | _     | —     | —    | —    | —    | _    | _    | —    | RPG1<3:0> |      |        | 0000 |            |

| 5000                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | —    | _    | _    | _    | —    | _         | _    | _      | _    | 0000       |

| FC98                       | RPG6R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    |           | RPG  | 6<3:0> |      | 0000       |

| 5000                       | 00070            | 31:16     | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    | —         | —    | _      | —    | 0000       |

| FC9C                       | RPG7R            | 15:0      | _     | —     | _     | _     | _     | —     | —    | _    | _    | _    | _    | _    |           | RPG7 | /<3:0> |      | 0000       |

| 5040                       | DDOAD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | -    |      | _    | _    | _    | _         | _    | _      | _    | 0000       |

| FCAU                       | FCA0 RPG8R 15:0  |           | _     | —     | _     | _     | _     | —     | —    |      |      | _    | _    | —    |           | RPG8 | 3<3:0> | •    | 0000       |

| 5044                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | _    | -    | _    | _    | _    | _         | _    | _      | _    | 0000       |

| FCA4                       | RPG9R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | _    | _    | —    | —    | —    |           | RPG9 | <3:0>  |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

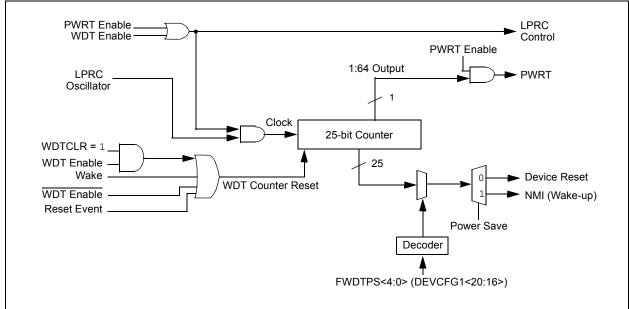

# 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Watchdog Timer (WDT), when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

### FIGURE 14-1: WATCHDOG AND POWER-UP TIMER BLOCK DIAGRAM

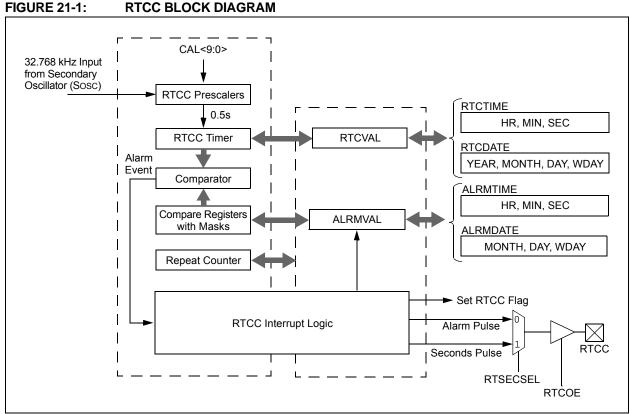

#### 21.0 **REAL-TIME CLOCK AND** CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available the Microchip web from site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are the key features of this module:

- · Time: hours. minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: Weekday, date, month and year

- · Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- · User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- · Requirements: External 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

# RTCC BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        |                   |                   |                   | SID<1             | 0:3>              |                   |                  |                  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |

| 23.10        |                   | SID<2:0>          |                   | —                 | MIDE              | — EID<17:16>      |                  |                  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          |                   |                   |                   | EID<7             | 7:0>              |                   |                  |                  |  |

#### REGISTER 23-9: C1RXMn: CAN ACCEPTANCE FILTER MASK 'n' REGISTER (n = 0, 1, 2 OR 3)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include the SIDx bit in filter comparison

- 0 = The SIDx bit is a 'don't care' in filter operation

- bit 20 Unimplemented: Read as '0'

- bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

- Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

#### bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include the EIDx bit in filter comparison

- 0 = The EIDx bit is a 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| REGISTE   | R 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0 (CONTINUED)                               |

|-----------|---------------------------------------------------------------------------------------------|

| bit 20-16 | FSEL2<4:0>: FIFO Selection bits                                                             |

|           | 11111 = Reserved                                                                            |

|           |                                                                                             |

|           |                                                                                             |

|           | 10000 = Reserved                                                                            |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| bit 15    | FLTEN1: Filter 1 Enable bit                                                                 |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                                                       |

|           | 11 = Acceptance Mask 3 selected                                                             |

|           | 10 = Acceptance Mask 2 selected                                                             |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                          |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                                             |

| DIL 12-0  | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           |                                                                                             |

|           | •<br>10000 = Reserved                                                                       |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| bit 7     | FLTEN0: Filter 0 Enable bit                                                                 |

|           | 1 = Filter is enabled                                                                       |

|           | 0 = Filter is disabled                                                                      |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                                                       |

|           | 11 = Acceptance Mask 3 selected                                                             |

|           | 10 = Acceptance Mask 2 selected                                                             |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                          |

| bit 4-0   | <b>FSEL0&lt;4:0&gt;:</b> FIFO Selection bits                                                |

|           | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           |                                                                                             |

|           | •<br>10000 = Reserved                                                                       |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| Netar     | The bits in this register can only be medified if the corresponding filter enable (ELTEN) b |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 23-16: C1FIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0 THROUGH 15) (CONTINUED)

- bit 7 TXEN: TX/RX Buffer Selection bit 1 = FIFO is a Transmit FIFO 0 = FIFO is a Receive FIFO TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully TXLARB: Message Lost Arbitration bit<sup>(3)</sup> bit 5 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received. TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority

- 01 Low Internetiate message

- 00 = Lowest message priority

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (C1CON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

# **REGISTER 23-17:** C1FIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|

| 01.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24        | —                 | —                 | —                 | _                 | —                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16        | —                 | —                 | —                 | _                 | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |

| 15:8         | —                 | —                 | —                 | _                 | —                 | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |

| 7:0          | —                 | —                 | —                 | _                 | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

### bit 31-27 Unimplemented: Read as '0'

| DIL 31-21 | Unimplemented. Read as 0                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|           | 1 = Interrupt enabled for FIFO not full                                                                         |

|           | 0 = Interrupt disabled for FIFO not full                                                                        |

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit                                                      |

|           | <ul> <li>1 = Interrupt enabled for FIFO empty</li> <li>0 = Interrupt disabled for FIFO empty</li> </ul>         |

| hit 23-20 | Unimplemented: Read as '0'                                                                                      |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                         |

| DIC 13    | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

|           | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 16    | RXNEMPTYIE: Empty Interrupt Enable bit                                                                          |

|           | <ul> <li>1 = Interrupt enabled for FIFO not empty</li> <li>0 = Interrupt disabled for FIFO not empty</li> </ul> |

| hit 15 11 |                                                                                                                 |

| bit 10    | Unimplemented: Read as '0'                                                                                      |

| DICTO     | <b>TXNFULLIF:</b> Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                      |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full                                 |

|           | 0 = FIFO is full                                                                                                |

|           | TXEN = 0: (FIFO configured as a receive buffer)                                                                 |

|           | Unused, reads '0'                                                                                               |

|           |                                                                                                                 |

| Note 1:   | This bit is read-only and reflects the status of the FIFO.                                                      |

NOTES:

#### TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| АС СНА        | RACTERIS | STICS                      |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |       |                            |  |

|---------------|----------|----------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------|--|

| Param.<br>No. | Symbol   | Charact                    | eristics                      | Min.                                                                                                                                                                                                                                                                            | Max. | Units | Conditions                 |  |

| IS34          | THD:STO  | Stop Condition             | 100 kHz mode                  | 4000                                                                                                                                                                                                                                                                            | _    | ns    | —                          |  |

|               |          | Hold Time                  | 400 kHz mode                  | 600                                                                                                                                                                                                                                                                             | —    | ns    |                            |  |

|               |          |                            | 1 MHz mode<br>(Note 1)        | 250                                                                                                                                                                                                                                                                             |      | ns    |                            |  |

| IS40          | TAA:SCL  | Output Valid from<br>Clock | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                               | 3500 | ns    | —                          |  |

|               |          |                            | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                               | 1000 | ns    |                            |  |

|               |          |                            | 1 MHz mode<br><b>(Note 1)</b> | 0                                                                                                                                                                                                                                                                               | 350  | ns    |                            |  |

| IS45          | TBF:SDA  | Bus Free Time              | 100 kHz mode                  | 4.7                                                                                                                                                                                                                                                                             | —    | μs    | The amount of time the bus |  |

|               |          |                            | 400 kHz mode                  | 1.3                                                                                                                                                                                                                                                                             | _    | μs    | must be free before a new  |  |

|               |          |                            | 1 MHz mode<br><b>(Note 1)</b> | 0.5                                                                                                                                                                                                                                                                             | _    | μS    | transmission can start     |  |

| IS50          | Св       | Bus Capacitive Lo          | ading                         |                                                                                                                                                                                                                                                                                 | 400  | pF    | —                          |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

### TABLE 32-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS | TICS                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |    |   |    |   |

|---------------|-----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|----|---|

| Param.<br>No. | Symbol    | Characteristics                 | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                    |    |   |    |   |

| MSP70         | TscL      | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                                                                                                                                                             | _  | _ | ns | _ |

| MSP71         | TscH      | SCKx Input High Time (Note 1,2) | TSCK/2                                                                                                                                                                                                                                                                             | _  | _ | ns | — |

| MSP51         | 5         | _                               | 25                                                                                                                                                                                                                                                                                 | ns |   |    |   |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

### TABLE 32-9:SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS | TICS                            | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |      |       |            |  |

|---------------|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No. | Symbol   | Characteristics                 | Min.                                                                                                                                                 | Typical | Max. | Units | Conditions |  |

| SP70          | TscL     | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                               | _       | _    | ns    | —          |  |

| SP71          | TscH     | SCKx Input High Time (Note 1,2) | Tsck/2                                                                                                                                               | _       | _    | ns    | —          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: The minimum clock period for SCKx is 40 ns.

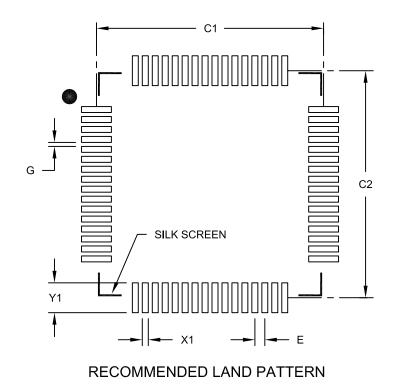

# 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |       |      |

|--------------------------|----|-------------|-------|------|

| Dimension Limits         |    | MIN         | NOM   | MAX  |

| Contact Pitch            | E  | 0.50 BSC    |       |      |

| Contact Pad Spacing      | C1 |             | 11.40 |      |

| Contact Pad Spacing      | C2 |             | 11.40 |      |

| Contact Pad Width (X64)  | X1 |             |       | 0.30 |

| Contact Pad Length (X64) | Y1 |             |       | 1.50 |

| Distance Between Pads    | G  | 0.20        |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B