Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                 |

|--------------------------|---------------------------------------------------------------------------------|

| roduct Status            | Active                                                                          |

| ore Processor            | MIPS32® M4K™                                                                    |

| ore Size                 | 32-Bit Single-Core                                                              |

| peed                     | 40MHz                                                                           |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| eripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| umber of I/O             | 53                                                                              |

| ogram Memory Size        | 512KB (512K x 8)                                                                |

| ogram Memory Type        | FLASH                                                                           |

| PROM Size                | -                                                                               |

| M Size                   | 64K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ta Converters            | A/D 28x10b                                                                      |

| cillator Type            | Internal                                                                        |

| erating Temperature      | -40°C ~ 85°C (TA)                                                               |

| unting Type              | Surface Mount                                                                   |

| ckage / Case             | 64-TQFP                                                                         |

| pplier Device Package    | 64-TQFP (10x10)                                                                 |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512ht-i-pt |

#### TABLE 3: PIN NAMES FOR 64-PIN USB DEVICES

64-PIN QFN<sup>(4)</sup> AND TQFP (TOP VIEW)

PIC32MX230F128H PIC32MX530F128H PIC32MX250F256H PIC32MX550F256H PIC32MX270F512H PIC32MX570F512H

QFN<sup>(4)</sup>

TQFP

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 1    | AN22/RPE5/PMD5/RE5                        |

| 2    | AN23/PMD6/RE6                             |

| 3    | AN27/PMD7/RE7                             |

| 4    | AN16/C1IND/RPG6/SCK2/PMA5/RG6             |

| 5    | AN17/C1INC/RPG7/PMA4/RG7                  |

| _    | A 1 1 4 2 1 2 2 1 2 1 2 1 2 2 2 2 2 2 2 2 |

| 5  | AN17/C1INC/RPG7/PMA4/RG7                  |

|----|-------------------------------------------|

| 6  | AN18/C2IND/RPG8/PMA3/RG8                  |

| 7  | MCLR                                      |

| 8  | AN19/C2INC/RPG9/PMA2/RG9                  |

| 9  | Vss                                       |

| 10 | VDD                                       |

| 11 | AN5/C1INA/RPB5/VBUSON/RB5                 |

| 12 | AN4/C1INB/RB4                             |

| 13 | PGED3/AN3/C2INA/RPB3/RB3                  |

| 14 | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2     |

| 15 | PGEC1/VREF-/AN1/RPB1/CTED12/RB1           |

| 16 | PGED1/VREF+/AN0/RPB0/PMA6/RB0             |

| 17 | PGEC2/AN6/RPB6/RB6                        |

| 18 | PGED2/AN7/RPB7/CTED3/RB7                  |

| 19 | AVDD                                      |

| 20 | AVss                                      |

| 21 | AN8/RPB8/CTED10/RB8                       |

| 22 | AN9/RPB9/CTED4/PMA7/RB9                   |

| 23 | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| Pin # | Full Pin Name         |

|-------|-----------------------|

| 33    | USBID/RPF3/RF3        |

| 34    | VBUS                  |

| 35    | Vusb3v3               |

| 36    | D-                    |

| 37    | D+                    |

| 38    | VDD                   |

| 39    | OSC1/CLKI/RC12        |

| 40    | OSC2/CLKO/RC15        |

| 41    | Vss                   |

| 42    | RPD8/RTCC/RD8         |

| 43    | RPD9/SDA1/RD9         |

| 44    | RPD10/SCL1/PMA15/RD10 |

| 45    | RPD11/PMA14/RD11      |

| 46    | RPD0/INT0/RD0         |

| 47    | SOSCI/RPC13/RC13      |

| 48    | SOSCO/RPC14/T1CK/RC14 |

| 49    | AN24/RPD1/RD1         |

| 50    | AN25/RPD2/SCK1/RD2    |

| 51    | AN26/C3IND/RPD3/RD3   |

| 52    | RPD4/PMWR/RD4         |

| 53    | RPD5/PMRD/RD5         |

| 54    | C3INC/RD6             |

| 55    | C3INB/RD7             |

| 56    | VCAP                  |

| 57    | VDD                   |

| 58    | C3INA/RPF0/RF0        |

| 59    | RPF1/RF1              |

| 60    | PMD0/RE0              |

| 61    | PMD1/RE1              |

| 62    | AN20/PMD2/RE2         |

| 63    | RPE3/CTPLS/PMD3/RE3   |

| 64    | AN21/PMD4/RE4         |

32 Note

24

25 26

27

28

30

Vss

VDD

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

AN14/RPB14/SCK3/CTED5/PMA1/RB14 AN15/RPB15/OCFB/CTED6/PMA0/RB15

TDO/AN11/PMA12/RB11

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

RPF4/SDA2/PMA9/RF4 RPF5/SCL2/PMA8/RF5

4: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES (CONTINUED)

### 100-PIN TQFP (TOP VIEW)

PIC32MX230F128L PIC32MX530F128L PIC32MX250F256L PIC32MX550F256L PIC32MX270F512L PIC32MX570F512L

100

1

| Pin# | Full Pin Name         |  |  |  |  |  |  |  |  |

|------|-----------------------|--|--|--|--|--|--|--|--|

| 71   | RPD11/PMA14/RD11      |  |  |  |  |  |  |  |  |

| 72   | RPD0/INT0/RD0         |  |  |  |  |  |  |  |  |

| 73   | SOSCI/RPC13/RC13      |  |  |  |  |  |  |  |  |

| 74   | SOSCO/RPC14/T1CK/RC14 |  |  |  |  |  |  |  |  |

| 75   | Vss                   |  |  |  |  |  |  |  |  |

| 76   | AN24/RPD1/RD1         |  |  |  |  |  |  |  |  |

| 77 . | AN25/RPD2/RD2         |  |  |  |  |  |  |  |  |

| 78   | AN26/C3IND/RPD3/RD3   |  |  |  |  |  |  |  |  |

| 79   | AN40/RPD12/PMD12/RD12 |  |  |  |  |  |  |  |  |

| 80   | AN41/PMD13/RD13       |  |  |  |  |  |  |  |  |

| 81   | RPD4/PMWR/RD4         |  |  |  |  |  |  |  |  |

| 82   | RPD5/PMRD/RD5         |  |  |  |  |  |  |  |  |

| 83   | AN42/C3INC/PMD14/RD6  |  |  |  |  |  |  |  |  |

| 84   | AN43/C3INB/PMD15/RD7  |  |  |  |  |  |  |  |  |

| 85   | VCAP                  |  |  |  |  |  |  |  |  |

|      | Į.                        |  |  |  |  |  |  |  |

|------|---------------------------|--|--|--|--|--|--|--|

| Pin# | Full Pin Name             |  |  |  |  |  |  |  |

| 86   | VDD                       |  |  |  |  |  |  |  |

| 87   | AN44/C3INA/RPF0/PMD11/RF0 |  |  |  |  |  |  |  |

| 88   | AN45/RPF1/PMD10/RF1       |  |  |  |  |  |  |  |

| 89   | RPG1/PMD9/RG1             |  |  |  |  |  |  |  |

| 90   | RPG0/PMD8/RG0             |  |  |  |  |  |  |  |

| 91   | RA6                       |  |  |  |  |  |  |  |

| 92   | CTED8/RA7                 |  |  |  |  |  |  |  |

| 93   | AN46/PMD0/RE0             |  |  |  |  |  |  |  |

| 94   | AN47/PMD1/RE1             |  |  |  |  |  |  |  |

| 95   | RG14                      |  |  |  |  |  |  |  |

| 96   | RG12                      |  |  |  |  |  |  |  |

| 97   | RG13                      |  |  |  |  |  |  |  |

| 98   | AN20/PMD2/RE2             |  |  |  |  |  |  |  |

| 99   | RPE3/CTPLS/PMD3/RE3       |  |  |  |  |  |  |  |

| 100  | AN21/PMD4/RE4             |  |  |  |  |  |  |  |

#### Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information

- 3: Shaded pins are 5V tolerant.

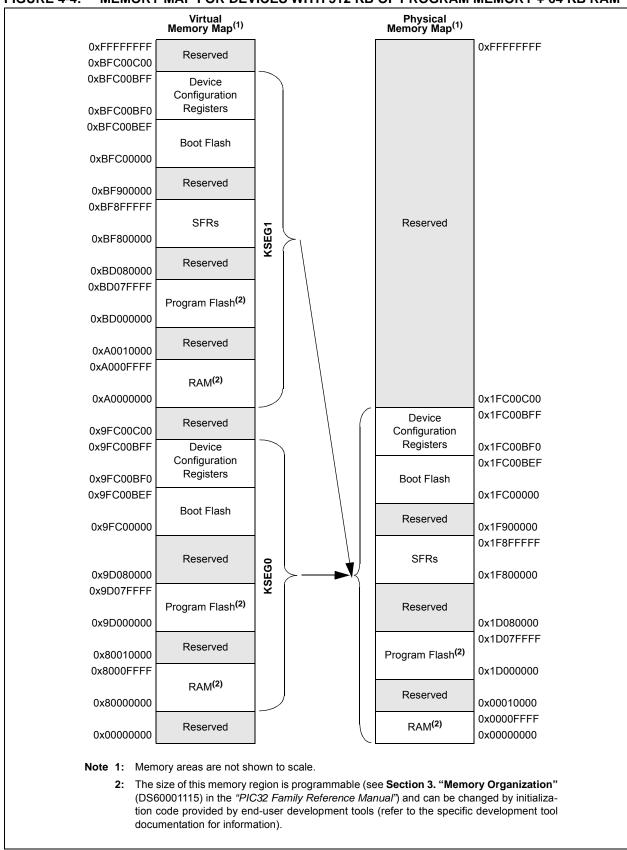

FIGURE 4-4: MEMORY MAP FOR DEVICES WITH 512 KB OF PROGRAM MEMORY + 64 KB RAM

#### REGISTER 7-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0               | U-0               | R/W-0, HS         | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31.24        | _                 | _                 | HVDR              | _                 | _                 | _                 | _                  | _                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                  | _                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | CMR                | VREGS              |

| 7:0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

**Legend:** HS = Set by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29 HVDR: High Voltage Detect Reset Flag bit

1 = High Voltage Detect (HVD) Reset has occurred, voltage on VCAP > 2.5V

0 = HVD Reset has not occurred

bit 28-10 Unimplemented: Read as '0'

bit 9 CMR: Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 **VREGS:** Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is disabled and is off during Sleep mode

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 SWR: Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset as not executed

bit 5 Unimplemented: Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 **IDLE:** Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

Note 1: User software must clear this bit to view next detection.

### 8.1 Control Registers

### TABLE 8-1: OSCILLATOR CONFIGURATION REGISTER MAP

| ess                         | Register<br>Name <sup>(1)</sup> | Φ.                   |       |       |                 |       |         |         |          |        | Bits    |              |       |       |                     |                       |        |       | w                   |

|-----------------------------|---------------------------------|----------------------|-------|-------|-----------------|-------|---------|---------|----------|--------|---------|--------------|-------|-------|---------------------|-----------------------|--------|-------|---------------------|

| Virtual Address<br>(BF80_#) |                                 | Bit Range            | 31/15 | 30/14 | 29/13           | 28/12 | 27/11   | 26/10   | 25/9     | 24/8   | 23/7    | 22/6         | 21/5  | 20/4  | 19/3                | 18/2                  | 17/1   | 16/0  | All Rese            |

| F000                        | OSCCON                          | 31:16 — PLLODIV<2:0> |       | -     | FRCDIV<2:0> — S |       |         | SOSCRDY | PBDIVRDY | PBDI\  | /<1:0>  | PLLMULT<2:0> |       |       | x1xx <sup>(2)</sup> |                       |        |       |                     |

| F000                        | OSCCON                          | 15:0                 | _     |       | COSC<2:         | 0>    | _       |         | NOSC<2:0 | >      | CLKLOCK | ULOCK        | SLOCK | SLPEN | CF                  | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx <sup>(2)</sup> |

| F010                        | OSCTUN                          | 31:16                | _     | _     | _               | _     | _       | _       | _        | _      | _       | _            | _     | _     | _                   | _                     | _      | _     | 0000                |

| F010                        | OSCIUN                          | 15:0                 | _     | _     | _               | _     | _       | _       | _        | _      | _       | _            |       |       | TUT                 | N<5:0>                |        |       | 0000                |

| F000                        | DEEOCON                         | 31:16                | _     |       |                 |       |         |         |          |        | RODIV<  | 14:0>        |       |       |                     |                       |        |       | 0000                |

| F020                        | REFOCON                         | 15:0                 | ON    | _     | SIDL            | OE    | RSLP    | -       | DIVSWEN  | ACTIVE | _       | _            | _     |       |                     | ROSE                  | L<3:0> |       | 0000                |

| F000                        | REFOTRIM                        | 31:16                |       |       |                 | ļ     | ROTRIM< | 3:0>    | )>       |        |         |              |       | _     | _                   | _                     | _      | _     | 0000                |

| F030                        |                                 | 15:0                 | _     | _     | _               | _     | _       | _       | _        | _      | _       | _            | _     | _     | _                   | _                     |        | _     | 0000                |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

lote 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on devices with a USB module.

| TABLE 9-3: [ | OMA CHANNEL | <b>0 THROUGH CHANNEL</b> | 3 REGISTER MAP | (CONTINUED) |

|--------------|-------------|--------------------------|----------------|-------------|

|--------------|-------------|--------------------------|----------------|-------------|

| ess                         |                                 |               |             |             |            |       |        |       |      | Bi     | ts       |        |        |            |          |        |        |        |            |

|-----------------------------|---------------------------------|---------------|-------------|-------------|------------|-------|--------|-------|------|--------|----------|--------|--------|------------|----------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14       | 29/13      | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4       | 19/3     | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | _           | _           | _          | _     |        |       | _    | _      |          | _      | _      | _          |          | _      |        |        | 0000       |

| 0200                        | DOTIZOT TIX                     | 15:0          |             |             |            |       |        |       |      |        |          |        |        |            |          |        |        | 0000   |            |

| 3200                        | DCH2DAT                         | 31:16         | _           |             | _          | _     | _      | _     | _    | _      | _        | _      | _      | _          | _        | _      | _      | _      | 0000       |

| 3230                        | DOMEDAI                         | 15:0          | _           |             | _          | _     | _      | _     | _    | _      |          |        |        | CHPDA      | T<7:0>   |        |        |        | 0000       |

| 3240                        | DCH3CON                         | 31:16         | _           | _           | _          | _     | _      | _     | _    | _      | _        | _      | _      | _          | _        | _      | _      | _      | 0000       |

| JZAU                        | DOMOCON                         | 15:0          | CHBUSY      |             | _          | _     | _      | _     | _    | CHCHNS | CHEN     | CHAED  | CHCHN  | CHAEN      | _        | CHEDET | CHPR   | I<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16         | _           |             | _          | _     | _      | _     | _    | _      |          | 1      | 1      | CHAIR      |          |        |        |        | 00FF       |

|                             | 20/10/2001                      | 15:0          |             |             |            | CHSIR | Q<7:0> |       |      |        | CFORCE   |        | PATEN  |            | AIRQEN   |        |        |        | FFF8       |

| 32C0                        | DCH3INT                         | 31:16         | _           |             |            | _     |        | _     | _    | _      | CHSDIE   | CHSHIE | CHDDIE | CHDHIE     | CHBCIE   | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0          | _           |             | _          | _     | _      | _     | _    | _      | CHSDIF   | CHSHIF | CHDDIF | CHDHIF     | CHBCIF   | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0 | CHSSA<31:0> |             |            |       |        |       |      |        |          |        |        |            |          | 0000   |        |        |            |

|                             |                                 | 31:16         | 000         |             |            |       |        |       |      |        |          |        |        |            |          | -      |        |        |            |

| 32E0                        | DCH3DSA                         | 15:0          |             |             |            |       |        |       |      |        |          |        |        |            |          | 0000   |        |        |            |

|                             |                                 | 31:16         | _           | _           | _          | _     | _      | _     | _    | _      | _        | _      | _      | _          | _        | _      | _      | _      | 0000       |

| 32F0                        | DCH3SSIZ                        | 15:0          |             |             |            |       |        |       |      |        |          |        |        | 0000       |          |        |        |        |            |

| 2200                        | DCH3DSIZ                        | 31:16         | _           | _           | _          | _     | _      | _     | _    | _      | _        | _      | _      | _          | _        | _      | _      | _      | 0000       |

| 3300                        | DCH3DSIZ                        | 15:0          |             |             |            |       |        |       |      | CHDSIZ | Z<15:0>  |        |        |            |          |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16         | _           |             | _          | _     | -      | -     | _    | _      | -        | _      | _      | _          | -        | _      | -      | _      | 0000       |

| 3310                        | DOI 1001 110                    | 15:0          |             |             |            |       |        |       |      | CHSPTF | R<15:0>  |        |        |            |          |        |        |        | 0000       |

| 3320                        | DCH3DPTR                        | 31:16         | _           | _           | _          | _     | _      | _     | _    | _      | _        | _      | _      | _          | _        | _      | _      | _      | 0000       |

|                             |                                 | 15:0          |             |             |            |       |        |       |      | CHDPT  | R<15:0>  |        |        |            |          |        |        |        | 0000       |

| 3330                        | DCH3CSIZ                        | 31:16         | _           |             | _          | _     | _      | _     | _    | -      | _        | _      | _      | _          | _        | _      | _      | _      | 0000       |

|                             |                                 | 15:0          |             |             |            |       |        |       |      | CHCSIZ | 2<15:0>  |        |        |            |          |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16<br>15:0 | _           | _           | _          | _     | _      | _     | _    | CHCPTF |          | _      | _      | _          | _        | _      | _      |        | 0000       |

| -                           |                                 | 31:16         | _           |             |            | _     |        |       |      |        | ₹~ IO.U≥ |        | _      |            |          |        | _      | _      | 0000       |

| 3350                        | DCH3DAT                         | 15:0          |             |             | _          |       |        |       |      |        | _        | _      | _      | —<br>CHPDA | T<7:0>   | _      | _      |        | 0000       |

| Logon                       | <u> </u>                        |               |             | <del></del> | unimplomer |       |        |       |      |        |          |        |        | CHEDA      | 11 >1.02 |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### 10.0 USB ON-THE-GO (OTG)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 27. "USB On-The-Go (OTG)"** (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- · USB Full-speed support for host and device

- · Low-speed host support

- · USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

Note:

The implementation and use of the USB specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | _                 | 1                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | 1                 | -                 | 1                 |                   | 1                 | 1                 | 1                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   | FRMH<2:0>        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2-0 FRMH<2:0>: The Upper 3 bits of the Frame Numbers bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | -                   | _                 | -                 | _                 | -                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |  |

| 15:8         | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | PID<              | 3:0> <sup>(1)</sup> |                   | EP<3:0>           |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup>

0001 = OUT (TX) token type transaction 1001 = IN (RX) token type transaction 1101 = SETUP (TX) token type transaction

**Note:** All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

TABLE 11-4: PORTB REGISTER MAP

| ess                         |                                 | 0         | Bits          |               |               |               |               |               |              |              |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6100                        | ANSELB                          | 31:16     |               | _             |               | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | _            |              | 0000          |

| 0.00                        |                                 | 15:0      | ANSELB15      | ANSELB14      | ANSELB13      | ANSELB12      | ANSELB11      | ANSELB10      | ANSELB9      | ANSELB8      | ANSELB7      | ANSELB6      | ANSELB5      | ANSELB4      | ANSELB3      | ANSELB2      | ANSELB1      | ANSELB0      | FFFF          |

| 6110                        | TRISB                           | 31:16     | -             | _             | -             | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | -            | 1            | 0000          |

|                             |                                 | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF          |

| 6120                        | PORTB                           | 31:16     | -             | _             | -             | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | -            | 1            | 0000          |

| 0.20                        |                                 | 15:0      | RB15          | RB14          | RB13          | RB12          | RB11          | RB10          | RB9          | RB8          | RB7          | RB6          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx          |

| 6130                        | LATB                            | 31:16     | -             | _             | -             | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | -            | 1            | 0000          |

| 0.00                        |                                 | 15:0      | LATB15        | LATB14        | LATB13        | LATB12        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx          |

| 6140                        | ODCB                            | 31:16     | -             | _             | -             | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | -            | 1            | 0000          |

| 00                          |                                 | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6        | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000          |

| 6150                        | CNPUB                           | 31:16     | -             | _             | -             | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | -            | 1            | 0000          |

| 0.00                        |                                 | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000          |

| 6160                        | CNPDB                           | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000          |

| 6170                        | CNCONB                          | 31:16     | _             |               | _             | _             |               |               | _            |              |              |              | _            |              | _            |              |              |              | 0000          |

| 00                          |                                 | 15:0      | ON            | _             | SIDL          | _             | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | 0000          |

| 6180                        | CNENB                           | 31:16     | -             | _             | -             | _             | _             | _             | _            | _            | _            | _            | _            | -            | _            | _            | -            | 1            | 0000          |

| 3.00                        |                                 | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB12       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000          |

|                             |                                 | 31:16     |               | _             |               | _             | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            |              | 0000          |

| 6190                        | CNSTATB                         | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | -                 | _                 | _                 | -                 | _                | -                |

| 00:40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

Legend:y = Values set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

1 = Enables the WDT if it is not enabled by the device configuration

0 = Disable the WDT if it was enabled in software

bit 14-7 Unimplemented: Read as '0'

bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

bit 1 WDTWINEN: Watchdog Timer Window Enable bit

1 = Enable windowed Watchdog Timer0 = Disable windowed Watchdog Timer

bit 0 WDTCLR: Watchdog Timer Reset bit

1 = Writing a '1' will clear the WDT

0 = Software cannot force this bit to a '0'

Note 1: A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 19-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

- bit 5 ABAUD: Auto-Baud Enable bit

- 1 = Enable baud rate measurement on the next character requires reception of Sync character (0x55); cleared by hardware upon completion

- 0 = Baud rate measurement disabled or completed

- bit 4 RXINV: Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

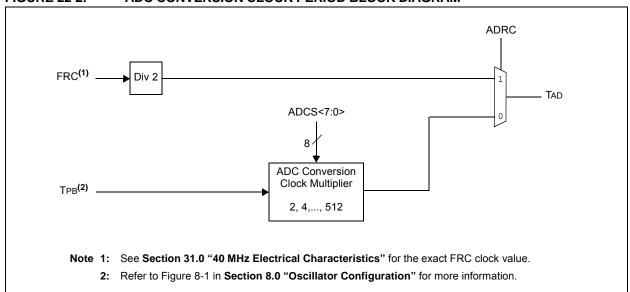

### FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# 23.0 CONTROLLER AREA NETWORK (CAN)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 34.** "**Controller Area Network (CAN)**" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

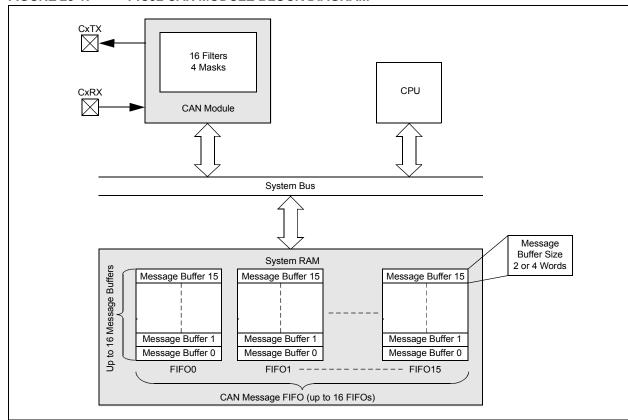

The Controller Area Network (CAN) module supports the following key features:

- · Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- · Message Reception and Transmission:

- 16 message FIFOs

- Each FIFO can have up to 16 messages for a total of 256 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 16 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet™ addressing support

- · Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 23-1 illustrates the general structure of the CAN module.

### FIGURE 23-1: PIC32 CAN MODULE BLOCK DIAGRAM

### **REGISTER 23-3: C1INT: CAN INTERRUPT REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | _                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 IVRIE: Invalid Message Received Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 30 WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 29 CERRIE: CAN Bus Error Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 28 SERRIE: System Error Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 27 RBOVIE: Receive Buffer Overflow Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 26-20 Unimplemented: Read as '0'

bit 19 MODIE: Mode Change Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 18 **CTMRIE:** CAN Timestamp Timer Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 17 RBIE: Receive Buffer Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 16 TBIE: Transmit Buffer Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 15 IVRIF: Invalid Message Received Interrupt Flag bit

1 = An invalid messages interrupt has occurred

0 = An invalid message interrupt has not occurred

Note 1: This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit

(C1CON<15>).

#### REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | 1                 | -                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | _                 |                   |                   | _                | _                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | SIDL              | _                 |                   | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 | _                 |                   | C3OUT             | C2OUT            | C1OUT            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in IDLE Control bit

1 = All Comparator modules are disabled in IDLE mode

0 = All Comparator modules continue to operate in the IDLE mode

bit 12-3 **Unimplemented:** Read as '0'

bit 2 C3OUT: Comparator Output bit

1 = Output of Comparator 3 is a '1'

0 = Output of Comparator 3 is a '0'

bit 1 C2OUT: Comparator Output bit

1 = Output of Comparator 2 is a '1'

0 = Output of Comparator 2 is a '0'

bit 0 C10UT: Comparator Output bit

1 = Output of Comparator 1 is a '1'

0 = Output of Comparator 1 is a '0'

### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

bit 24 EDG1STAT: Edge 1 Status bit

Indicates the status of Edge 1 and can be written to control edge source

- 1 = Edge 1 has occurred

- 0 = Edge 1 has not occurred

- bit 23 EDG2MOD: Edge 2 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 22 EDG2POL: Edge 2 Polarity Select bit

- 1 = Edge 2 programmed for a positive edge response

- 0 = Edge 2 programmed for a negative edge response

- bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = PBCLK clock is selected

- 1011 = IC3 Capture Event is selected

- 1010 = IC2 Capture Event is selected

- 1001 = IC1 Capture Event is selected

- 1001 101 Capture Event is select

- 1000 = CTED13 pin is selected

- 0111 = CTED12 pin is selected

- 0110 = CTED11 pin is selected

- 0101 = CTED10 pin is selected

- 0100 = CTED9 pin is selected

- 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

- 0000 = Timer1 Event is selected

- bit 17-16 Unimplemented: Read as '0'

- bit 15 ON: ON Enable bit

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **CTMUSIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 **TGEN:** Time Generation Enable bit<sup>(1)</sup>

- 1 = Enables edge delay generation

- 0 = Disables edge delay generation

- bit 11 EDGEN: Edge Enable bit

- 1 = Edges are not blocked

- 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in **Section 31.0 "40 MHz Electrical Characteristics"** for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- · On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

#### 27.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator start-up delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- · On any form of device Reset

- On a WDT time-out interrupt

## 27.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

TABLE 31-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |          |                                                                                                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |         |         |                                                                                                                                |                                                      |  |  |

|--------------------|----------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| DO 0117            | WAO I EN |                                                                                                                | Operatin                                                              | g tempe | erature | $-40^{\circ}$ C $\leq$ TA $\leq$ +85 $^{\circ}$ C for Industrial $-40^{\circ}$ C $\leq$ TA $\leq$ +105 $^{\circ}$ C for V-temp |                                                      |  |  |

| Param.             | Symbol   | Characteristic                                                                                                 | Min.                                                                  | Тур.    | Max.    | Units                                                                                                                          | Conditions                                           |  |  |

| DO10               |          | Output Low Voltage I/O Pins: 4x Sink Driver Pins - All I/O output pins not defined as 8x Sink Driver pins      | _                                                                     | _       | 0.4     | V                                                                                                                              | IoL ≤ 9 mA, VDD = 3.3V                               |  |  |

| DO 10              | Vol      | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - RB14,<br>RC15, RD2, RD10, RD15, RF6,<br>RF13, RG6     | ı                                                                     | _       | 0.4     | >                                                                                                                              | $IOL \le 15$ mA, $VDD = 3.3V$                        |  |  |

| DO20               | Vон      | Output High Voltage I/O Pins: 4x Source Driver Pins - All I/O output pins not defined as 8x Source Driver pins | 2.4                                                                   | _       | _       | >                                                                                                                              | IOH ≥ -10 mA, VDD = 3.3V                             |  |  |

| DO20               | VOH      | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - RB14,<br>RC15, RD2, RD10, RD15, RF6,<br>RF13, RG6  | 2.4                                                                   |         |         | >                                                                                                                              | IOH ≥ -15 mA, VDD = 3.3V                             |  |  |

|                    |          | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>                                                    | _       | _       |                                                                                                                                | IOH ≥ -14 mA, VDD = 3.3V                             |  |  |

|                    |          | 4x Source Driver Pins - All I/O                                                                                | 2.0 <sup>(1)</sup>                                                    | _       | _       | V                                                                                                                              | IOH $\geq$ -12 mA, VDD = 3.3V                        |  |  |

| DO20A              | Voud     | output pins not defined as 8x Sink Driver pins                                                                 | 3.0 <sup>(1)</sup>                                                    | _       | _       |                                                                                                                                | $IOH \ge -7 \text{ mA}, VDD = 3.3V$                  |  |  |

| DOZUA              | VOHI     | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>                                                    | _       | _       |                                                                                                                                | IOH ≥ -22 mA, VDD = 3.3V                             |  |  |

|                    |          | 8x Source Driver Pins - RB14,                                                                                  | 2.0 <sup>(1)</sup>                                                    | _       | _       | V                                                                                                                              | IOH ≥ -18 mA, VDD = 3.3V                             |  |  |

|                    |          | RC15, RD2, RD10, RD15, RF6,<br>RF13, RG6                                                                       | 3.0 <sup>(1)</sup>                                                    | _       | _       |                                                                                                                                | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |  |

Note 1: Parameters are characterized, but not tested.

DS60001290D-page 316

TABLE 31-12: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        |                                      |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |            |                                               |  |  |  |  |

|--------------------|--------|--------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-----------------------------------------------|--|--|--|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min.   | Typical <sup>(1)</sup>                                                                                                                                                                                                                         | Max. | Units      | Conditions                                    |  |  |  |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |        |                                                                                                                                                                                                                                                |      |            |                                               |  |  |  |  |

| D130               | EP     | Cell Endurance                       | 20,000 | _                                                                                                                                                                                                                                              | _    | E/W        | _                                             |  |  |  |  |

| D131               | VPR    | VDD for Read                         | 2.3    | _                                                                                                                                                                                                                                              | 3.6  | V          | _                                             |  |  |  |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.3    | _                                                                                                                                                                                                                                              | 3.6  | V          | _                                             |  |  |  |  |

| D134               | TRETD  | Characteristic Retention             | 20     | _                                                                                                                                                                                                                                              | _    | Year       | Provided no other specifications are violated |  |  |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | _      | 10                                                                                                                                                                                                                                             | _    | mA         | _                                             |  |  |  |  |

|                    | Tww    | Word Write Cycle Time                | _      | 411                                                                                                                                                                                                                                            | _    | FRC Cycles | See Note 4                                    |  |  |  |  |

| D136               | Trw    | Row Write Cycle Time                 | _      | 6675                                                                                                                                                                                                                                           | _    | FRC Cycles | See Note 2,4                                  |  |  |  |  |

| D137               | TPE    | Page Erase Cycle Time                | _      | 20011                                                                                                                                                                                                                                          | _    | FRC Cycles | See Note 4                                    |  |  |  |  |

|                    | TCE    | Chip Erase Cycle Time                | _      | 80180                                                                                                                                                                                                                                          | _    | FRC Cycles | See Note 4                                    |  |  |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

- 2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

- **3:** Refer to the "PIC32 Flash Programming Specification" (DS60001145) for operating conditions during programming and erase cycles.

- 4: This parameter depends on FRC accuracy (See Table 31-19) and FRC tuning values (See Register 8-2).

TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                                    |              | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |       |            |  |  |  |

|--------------------|----------------------|----------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>                     | Min.         | Typical <sup>(2)</sup>                                                                                                                                                                                                                         | Max. | Units | Conditions |  |  |  |

| SP51               | TssH2DoZ             | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4) | 5            | _                                                                                                                                                                                                                                              | 25   | ns    | _          |  |  |  |

| SP52               | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                              | Тscк +<br>20 | _                                                                                                                                                                                                                                              | _    | ns    | _          |  |  |  |

| SP60               | TssL2DoV             | SDOx Data Output Valid after SSx Edge              | _            | _                                                                                                                                                                                                                                              | 25   | ns    | _          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.