Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES

## **100-PIN TQFP (TOP VIEW)**

#### PIC32MX130F128L PIC32MX150F256L PIC32MX170F512L

100

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                   |

|-------|---------------------------------------|-------|---------------------------------|

| 1     | AN28/RG15                             | 36    | Vss                             |

| 2     | Vdd                                   | 37    | VDD                             |

| 3     | AN22/RPE5/PMD5/RE5                    | 38    | TCK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 39    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 40    | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 41    | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 42    | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 45    | Vss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 46    | VDD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 47    | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 48    | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 49    | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 50    | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 51    | RPF3/RF3                        |

| 17    | TMS/CTED1/RA0                         | 52    | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 53    | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 54    | RPF7/RF7                        |

| 20    | AN5/C1INA/RPB5/RB5                    | 55    | RPF6/SCK1/INT0/RF6              |

| 21    | AN4/C1INB/RB4                         | 56    | SDA1/RG3                        |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 57    | SCL1/RG2                        |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 58    | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 59    | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 60    | TDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 61    | TDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 62    | VDD                             |

| 28    | VREF-/PMA7/RA9                        | 63    | OSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 64    | OSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 65    | Vss                             |

| 31    | AVss                                  | 66    | RPA14/RA14                      |

| 32    | AN8/RPB8/CTED10/RB8                   | 67    | RPA15/RA15                      |

| 33    | AN9/RPB9/CTED4/RB9                    | 68    | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 69    | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 70    | RPD10/PMA15/RD10                |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

|          | Pin Number                     |     |             |                |                        |

|----------|--------------------------------|-----|-------------|----------------|------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP<br>TQFP |     | Pin<br>Type | Buffer<br>Type | Description            |

| AN0      | 16                             | 25  | Ι           | Analog         |                        |

| AN1      | 15                             | 24  | Ι           | Analog         |                        |

| AN2      | 14                             | 23  | Ι           | Analog         |                        |

| AN3      | 13                             | 22  | Ι           | Analog         |                        |

| AN4      | 12                             | 21  | Ι           | Analog         |                        |

| AN5      | 11                             | 20  | I           | Analog         |                        |

| AN6      | 17                             | 26  | Ι           | Analog         |                        |

| AN7      | 18                             | 27  | I           | Analog         |                        |

| AN8      | 21                             | 32  | I           | Analog         |                        |

| AN9      | 22                             | 33  | Ι           | Analog         |                        |

| AN10     | 23                             | 34  | Ι           | Analog         |                        |

| AN11     | 24                             | 35  | I           | Analog         |                        |

| AN12     | 27                             | 41  | Ι           | Analog         |                        |

| AN13     | 28                             | 42  | Ι           | Analog         |                        |

| AN14     | 29                             | 43  | I           | Analog         |                        |

| AN15     | 30                             | 44  | Ι           | Analog         |                        |

| AN16     | 4                              | 10  | I           | Analog         |                        |

| AN17     | 5                              | 11  | I           | Analog         |                        |

| AN18     | 6                              | 12  | Ι           | Analog         | Analog input channels. |

| AN19     | 8                              | 14  | Ι           | Analog         |                        |

| AN20     | 62                             | 98  | I           | Analog         |                        |

| AN21     | 64                             | 100 | Ι           | Analog         |                        |

| AN22     | 1                              | 3   | I           | Analog         |                        |

| AN23     | 2                              | 4   | Ι           | Analog         |                        |

| AN24     | 49                             | 76  | Ι           | Analog         |                        |

| AN25     | 50                             | 77  | Ι           | Analog         |                        |

| AN26     | 51                             | 78  | I           | Analog         |                        |

| AN27     | 3                              | 5   | I           | Analog         |                        |

| AN28     |                                | 1   | I           | Analog         |                        |

| AN29     | —                              | 6   | Ι           | Analog         |                        |

| AN30     | _                              | 7   | I           | Analog         |                        |

| AN31     |                                | 8   | Ι           | Analog         |                        |

| AN32     | _                              | 18  | I           | Analog         |                        |

| AN33     | _                              | 19  | Ι           | Analog         |                        |

| AN34     |                                | 39  | Ι           | Analog         |                        |

| AN35     |                                | 40  |             | Analog         | 1                      |

# TABLE 1-1:PINOUT I/O DESCRIPTIONS

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

|          | Pin Number             |                          |                         |              |                                                                              |  |  |  |

|----------|------------------------|--------------------------|-------------------------|--------------|------------------------------------------------------------------------------|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | Pin Buffer<br>Type Type |              | Description                                                                  |  |  |  |

| MCLR     | 7                      | 13                       | I                       | ST           | Master Clear (Reset) input. This pin is an active-low Reset t the device.    |  |  |  |

| AVDD     | 19                     | 30                       | Ρ                       | Р            | Positive supply for analog modules. This pin must be connected at all times. |  |  |  |

| AVss     | 20                     | 31                       | Р                       | Р            | Ground reference for analog modules                                          |  |  |  |

| Vdd      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | Ρ                       | —            | Positive supply for peripheral logic and I/O pins                            |  |  |  |

| VCAP     | 56                     | 85                       | Р                       | _            | Capacitor for Internal Voltage Regulator                                     |  |  |  |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | Ρ                       | _            | Ground reference for logic and I/O pins                                      |  |  |  |

| VREF+    | 16                     | 29                       | Р                       | Analog       | Analog Voltage Reference (High) Input                                        |  |  |  |

| VREF-    | 15                     | 28                       | Р                       | Analog       | Analog Voltage Reference (Low) Input                                         |  |  |  |

| Legend:  | CMOS = CN              | IOS compati              | ble inpu                | it or output | Analog = Analog input I = Input O = Output                                   |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input I = Input ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0               | U-0               | R/W-0, HS         | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31.24        | —                 | —                 | HVDR              | —                 | —                 | _                 | —                  | —                  |

| 23:16        | U-0                | U-0                |

| 23.10        | —                 | —                 | —                 | —                 | —                 | _                 | —                  | —                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

# REGISTER 7-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware | 9                    |                    |

|-------------------|----------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |

| -n - value |                                                                          |

|------------|--------------------------------------------------------------------------|

|            |                                                                          |

| bit 31-30  | Unimplemented: Read as '0'                                               |

| bit 29     | HVDR: High Voltage Detect Reset Flag bit                                 |

|            | 1 = High Voltage Detect (HVD) Reset has occurred, voltage on VCAP > 2.5V |

|            | 0 = HVD Reset has not occurred                                           |

| bit 28-10  | Unimplemented: Read as '0'                                               |

| bit 9      | CMR: Configuration Mismatch Reset Flag bit                               |

|            | 1 = Configuration mismatch Reset has occurred                            |

|            | 0 = Configuration mismatch Reset has not occurred                        |

| bit 8      | VREGS: Voltage Regulator Standby Enable bit                              |

|            | 1 = Regulator is enabled and is on during Sleep mode                     |

|            | 0 = Regulator is disabled and is off during Sleep mode                   |

| bit 7      | EXTR: External Reset (MCLR) Pin Flag bit                                 |

|            | 1 = Master Clear (pin) Reset has occurred                                |

|            | 0 = Master Clear (pin) Reset has not occurred                            |

| bit 6      | SWR: Software Reset Flag bit                                             |

|            | 1 = Software Reset was executed                                          |

|            | 0 = Software Reset as not executed                                       |

| bit 5      | Unimplemented: Read as '0'                                               |

| bit 4      | WDTO: Watchdog Timer Time-out Flag bit                                   |

|            | 1 = WDT Time-out has occurred                                            |

|            | 0 = WDT Time-out has not occurred                                        |

| bit 3      | SLEEP: Wake From Sleep Flag bit                                          |

|            | 1 = Device was in Sleep mode                                             |

|            | 0 = Device was not in Sleep mode                                         |

| bit 2      | IDLE: Wake From Idle Flag bit                                            |

|            | 1 = Device was in Idle mode                                              |

|            | 0 = Device was not in Idle mode                                          |

| bit 1      | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                             |

|            | 1 = Brown-out Reset has occurred                                         |

|            | 0 = Brown-out Reset has not occurred                                     |

| bit 0      | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                       |

|            | 1 = Power-on Reset has occurred                                          |

|            | 0 = Power-on Reset has not occurred                                      |

|            |                                                                          |

Note 1: User software must clear this bit to view next detection.

# REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| LEGISTER 3-10. DETACSIZ. DMA CHANNEL & CEEL-SIZE REGISTER |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|-----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range                                              | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 01.04                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24                                                     |                   | —                 | -                 | -                 | —                 | —                 | -                | —                |  |  |

| 22:16                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16                                                     | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8                                                      | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0                                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0                                                       |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |

# REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

## **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | -                 | _                 |                   |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                                                                  |                      |                    |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

#### Note: When in Pattern Detect mode, this register is reset on a pattern detect.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

| 24.24        | U-0                   | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | -                 | —                     | —                |  |

| 22:16        | U-0                   | U-0              |  |

| 23:16        | —                 | _                 | —                 | —                 |                   |                   |                       | —                |  |

| 15:8         | U-0                   | U-0              |  |

| 10.0         | _                 | _                 | _                 | _                 | _                 | _                 | _                     | —                |  |

|              | R/W-0                 | R/W-0            |  |

| 7:0          | DTOFF             |                   |                   | DTOFE             | DENIGEE           | 0001055           | CRC5EE <sup>(1)</sup> | DIDEE            |  |

|              | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |  |

|              |                   |                   |                   |                   |                   |                   |                       |                  |  |

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

- 1 = BTSEF interrupt enabled

- 0 = BTSEF interrupt disabled

- bit 6 **BMXEE:** Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt enabled

- 0 = BMXEF interrupt disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt enabled

- 0 = DMAEF interrupt disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt enabled

- 0 = BTOEF interrupt disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt enabled

- 0 = DFN8EF interrupt disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt enabled

- 0 = CRC16EF interrupt disabled

- bit 1 **CRC5EE:** CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt enabled

- 0 = CRC5EF interrupt disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt enabled

- 0 = EOF interrupt disabled

- bit 0 **PIDEE:** PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt enabled

- 0 = PIDEF interrupt disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

# TABLE 11-5: PORTC REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 | 0         |           |           |           |           |       |       |      | Bits |      |      |      |          |          |          |          |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | —         | —         | _         | _         | —     | —     | _    | _    | _    | —    | —    | —        | —        | —        | —        | —    | 0000          |

| 0200                        |                                 | 15:0      | —         | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —        | ANSELC3  | ANSELC2  | ANSELC1  | —    | 000E          |

| 6210                        | TRISC                           | 31:16     | —         | —         | —         | —         | —     | —     | —    | —    | _    | —    | —    | —        | —        |          | —        | —    | 0000          |

| 0210                        | 11100                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | —    | —    | —    | —    | TRISC4   | TRISC3   | TRISC2   | TRISC1   | —    | FFFF          |

| 6220                        | PORTC                           | 31:16     | —         | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —        | —        | —        | —        | —    | 0000          |

| 0220                        | TOILIO                          | 15:0      | RC15      | RC14      | RC13      | RC12      | _     | —     | _    |      | _    | —    | —    | RC4      | RC3      | RC2      | RC1      | —    | xxxx          |

| 6230                        | LATC                            | 31:16     | —         | _         |           |           | _     | —     | _    |      | _    | —    | —    | —        | —        | —        |          | —    | 0000          |

| 0200                        | LATO                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | _     | —     | _    |      | _    | —    | —    | LATC4    | LATC3    | LATC2    | LATC1    | —    | xxxx          |

| 6240                        | ODCC                            | 31:16     | —         | _         |           |           | _     | —     | _    |      | _    | —    | —    | —        | —        | —        |          | —    | 0000          |

| 0240                        | 0000                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —     | —     | —    | —    | —    | —    | —    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | —    | 0000          |

| 6250                        | CNPUC                           | 31:16     | —         | —         | _         | _         | —     | —     | —    | —    | —    | —    | —    | —        | —        | —        | —        | —    | 0000          |

| 0230                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | _     | _    | _    | _    | —    | —    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | —    | 0000          |

| 6260                        | CNPDC                           | 31:16     | —         | —         | —         | _         | —     | —     | -    | _    | -    | —    | —    | _        | —        | —        | _        | —    | 0000          |

| 0200                        | CINFDC                          | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | _     |      |      |      | _    | _    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     | _         | —         | _         | _         | —     | _     |      |      |      | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0270                        | CINCOINC                        | 15:0      | ON        | —         | SIDL      | _         | —     | _     |      |      |      | —    | —    | _        | —        | —        | -        | —    | 0000          |

| 6280                        | CNENC                           | 31:16     | —         | —         |           | _         | _     | _     | —    | —    | —    | —    | -    | _        | _        | _        | —        | _    | 0000          |

| 0200                        | CINEING                         | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     |       | —    | _    | —    | —    | _    | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | _    | 0000          |

| 6200                        | CNICTATO                        | 31:16     | —         | —         | _         | _         | _     | —     | _    | _    | -    | _    | _    | _        |          | _        | _        | —    | 0000          |

| 0290                        | CNSTATC                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     | _     | _    | _    | _    | _    | _    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | _    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### **Control Registers** 17.1

# TABLE 17-1: SPI1 THROUGH SPI4 REGISTER MAP

| ess                         |                                 | <i>a</i>      |               |              |           |              |                |              |             | Bi         | ts      |        |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|---------------|---------------|--------------|-----------|--------------|----------------|--------------|-------------|------------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14        | 29/13     | 28/12        | 27/11          | 26/10        | 25/9        | 24/8       | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16         | FRMEN         | FRMSYNC      | FRMPOL    | MSSEN        | FRMSYPW        | FF           | RMCNT<2:0   | )>         | MCLKSEL | —      | —      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5000                        | SITICON                         | 15:0          | ON            | —            | SIDL      | DISSDO       | MODE32         | MODE16       | SMP         | CKE        | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5810                        | SPI1STAT                        | 31:16         | _             | —            | —         |              |                | UFELM<4:     | 0>          |            | —       | —      | —      |          |             | BUFELM<4 |        |         | 0000       |

| 3010                        | 011101/1                        | 15:0          |               | —            | —         | FRMERR       | SPIBUSY        |              | —           | SPITUR     | SRMT    | SPIROV | SPIRBE | —        | SPITBE      |          | SPITBF | SPIRBF  | 19EB       |

| 5820                        | SPI1BUF                         | 31:16<br>15:0 |               |              |           |              |                |              |             | DATA<      | 31:0>   |        |        |          |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16         | _             | _            | _         | —            | —              | —            | —           | —          | —       | —      | —      | —        | —           | _        | —      | _       | 0000       |

| 5630                        | SFIIDKG                         | 15:0          |               | -            | _         | _            | —              | _            | -           |            |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |               | —            | —         |              | —              |              |             |            | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5840                        | SPI1CON2                        | 15:0          | SPI<br>SGNEXT | —            | _         | FRM<br>ERREN | SPI<br>ROVEN   | SPI<br>TUREN | IGNROV      | IGNTUR     | AUDEN   | —      | _      | _        | AUD<br>MONO | -        | AUDMO  | )D<1:0> | 0000       |

| 5A00                        | SPI2CON                         | 31:16         | FRMEN         | FRMSYNC      | FRMPOL    | MSSEN        | FRMSYPW        | FF           | RMCNT<2:0   | )>         | MCLKSEL | _      | _      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 0112001                         | 15:0          | ON            | —            | SIDL      | DISSDO       | MODE32         | MODE16       | SMP         | CKE        | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5A10                        | SPI2STAT                        | 31:16         |               | —            | —         |              |                | UFELM<4:     | 0>          |            | —       | —      | —      |          | TX          | BUFELM<4 |        | -       | 0000       |

| 5410                        | 01 120 17 11                    | 15:0          | _             | —            | —         | FRMERR       | SPIBUSY        | —            | —           | SPITUR     | SRMT    | SPIROV | SPIRBE | _        | SPITBE      | —        | SPITBF | SPIRBF  | 19EB       |

| 5A20                        | SPI2BUF                         | 31:16<br>15:0 |               |              |           |              |                |              |             | DATA<      | 31:0>   |        |        |          |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16         |               | —            | —         |              | —              |              |             |            | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5A30                        |                                 | 15:0          | -             | —            | —         | -            | —              | —            | _           |            |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |               | —            | —         |              | —              |              |             |            | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0          | SPI<br>SGNEXT | —            | _         | FRM<br>ERREN | SPI<br>ROVEN   | SPI<br>TUREN | IGNROV      | IGNTUR     | AUDEN   | —      | _      | _        | AUD<br>MONO | -        | AUDMO  | )D<1:0> | 0000       |

| 5000                        | SPI3CON                         | 31:16         | FRMEN         | FRMSYNC      | FRMPOL    | MSSEN        | FRMSYPW        | FF           | RMCNT<2:0   | )>         | MCLKSEL | —      | _      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5C00                        | SPISCON                         | 15:0          | ON            | —            | SIDL      | DISSDO       | MODE32         | MODE16       | SMP         | CKE        | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5010                        | SPI3STAT                        | 31:16         |               | -            | _         |              | RXB            | UFELM<4:     | 0>          |            | —       | _      | —      |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5C10                        | 3F 133 IAI                      | 15:0          | -             | —            | —         | FRMERR       | SPIBUSY        |              | -           | SPITUR     | SRMT    | SPIROV | SPIRBE | -        | SPITBE      |          | SPITBF | SPIRBF  | 19EB       |

| 5C20                        | SPI3BUF                         | 31:16<br>15:0 |               |              |           |              |                |              |             | DATA<      | 31:0>   |        |        |          |             |          |        |         | 0000       |

|                             |                                 | 31:16         | _             | —            | —         | _            | —              | —            | —           | —          | —       | —      | —      | —        | —           | _        | —      | _       | 0000       |

| 5C30                        | SPI3BRG                         | 15:0          | _             | _            | —         | _            | _              | _            | _           |            |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

| Legen                       | <b>d:</b> x = un                | known         | value on F    | Reset; — = ı | unimpleme | nted, read a | s '0'. Reset v | alues are s  | shown in he | xadecimal. |         |        |        |          |             |          |        |         | •          |

All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Note 1: Registers" for more information.

2: This register is only available on 100-pin devices.

# REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER (CONTINUED)

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

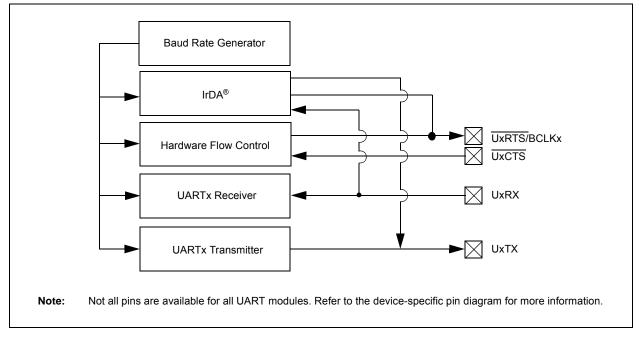

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX/5XX 64/100-pin family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9<sup>th</sup> bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

| REGISTER 21-4. REGISTER |                   |                                                                      |                   |                   |                                    |                   |                  |                  |  |  |  |  |

|-------------------------|-------------------|----------------------------------------------------------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range            | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                                                    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 04.04                   | R/W-x             | R/W-x                                                                | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24                   |                   | YEAR1                                                                | 0<3:0>            |                   |                                    | YEAR0             | 1<3:0>           |                  |  |  |  |  |

| 00.40                   | R/W-x             | R/W-x                                                                | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16                   |                   | MONTH                                                                | MONTH             | NTH01<3:0>        |                                    |                   |                  |                  |  |  |  |  |

| 45.0                    | R/W-x             | R/W-x                                                                | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8                    |                   | DAY10                                                                | <3:0>             |                   |                                    | DAY01             | <3:0>            |                  |  |  |  |  |

| 7.0                     | U-0               | U-0                                                                  | U-0               | U-0               | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0                     | _                 | —                                                                    | _                 | —                 |                                    | WDAYO             | 1<3:0>           |                  |  |  |  |  |

|                         |                   |                                                                      |                   |                   |                                    |                   |                  |                  |  |  |  |  |

| Legend:                 |                   |                                                                      |                   |                   |                                    |                   |                  |                  |  |  |  |  |

| R = Read                | able bit          |                                                                      | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |  |  |

| -n = Value              | e at POR          | $(1)^{2}$ = Bit is set $(0)^{2}$ = Bit is cleared x = Bit is unknown |                   |                   |                                    |                   |                  | known            |  |  |  |  |

# REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                              | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                                                                                                                                                                                   | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|------------------------------------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x                                          | R/W-x             | R/W-x             | R/W-x                                                                                                                                                                                                                              | R/W-x            |  |  |

| 31:24        |                   | HR10              | <3:0>             |                                                | HR01<3:0>         |                   |                                                                                                                                                                                                                                    |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x                                          | R/W-x             | R/W-x             | R/W-x                                                                                                                                                                                                                              | R/W-x            |  |  |

| 23:16        |                   | MIN10             | <3:0>             |                                                | MIN01<3:0>        |                   |                                                                                                                                                                                                                                    |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x                                          | R/W-x             | R/W-x             | R/W-x                                                                                                                                                                                                                              | R/W-x            |  |  |

| 15:8         |                   | SEC10             | <3:0>             |                                                |                   | SEC01             | 25/17/9/1         24/1           R/W-x         R           <3:0>         R/W-x           R/W-x         R           <3:0>         R           W-x         R           <3:0>         0           U-0         U           —         0 |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0                                            | U-0               | U-0               | U-0                                                                                                                                                                                                                                | U-0              |  |  |

| 7:0          | _                 | _                 | _                 | _                                              | _                 | _                 | _                                                                                                                                                                                                                                  | _                |  |  |

|              |                   |                   |                   |                                                |                   |                   |                                                                                                                                                                                                                                    |                  |  |  |

| Legend:      |                   |                   |                   |                                                |                   |                   |                                                                                                                                                                                                                                    |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | ritable bit U = Unimplemented bit, read as '0' |                   |                   |                                                                                                                                                                                                                                    |                  |  |  |

### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10s place digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10s place digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10s place digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

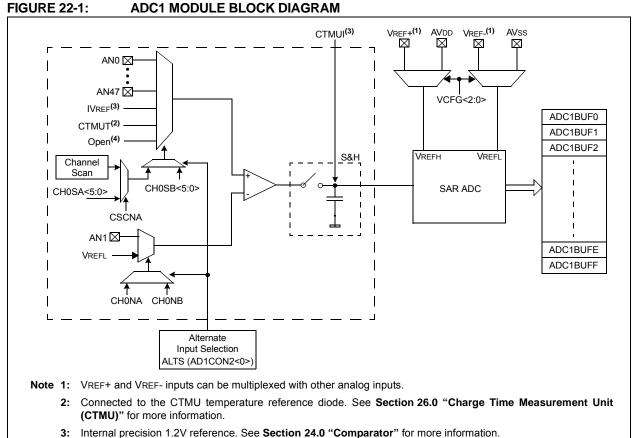

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- Up to 48 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

4: This selection is only used with CTMU capacitive and time measurement.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0                            | R/W-0            |

| 31:24        |                   |                   | —                 | —                 | ABAT              | F                 | •                                |                  |

| 22:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0                              | U-0              |

| 23:16        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | —                 | 25/17/9/1<br>R/W-0<br>REQOP<2:03 | -                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0                              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | —                 | CANBUSY           | —                 | —                                | _                |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                            | R/W-0            |

| 7.0          | _                 | _                 | _                 |                   | I                 | DNCNT<4:0>        |                                  |                  |

# **REGISTER 23-1: C1CON: CAN MODULE CONTROL REGISTER**

| Legend:           | HC = Hardware Clear | S = Settable bit          |                    |  |  |  |

|-------------------|---------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, re | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

#### bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

## bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 31.24        | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 02:16        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |  |  |  |

| 23:16        |                   | SID<2:0>          |                   | _                 | EXID              | _                 | EID<1            | 7:16>            |  |  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 7:0          | EID<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

# REGISTER 23-14: C1RXFn: CAN ACCEPTANCE FILTER 'n' REGISTER ('n' = 0 THROUGH 15)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

# 27.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 27-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМИ                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| UART3                        | U3MD                         | PMD5<2>                        |

| UART4                        | U4MD                         | PMD5<3>                        |

| UART5                        | U5MD                         | PMD5<4>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| SPI3                         | SPI3MD                       | PMD5<10>                       |

| SPI4                         | SPI4MD                       | PMD5<11>                       |

| 2C1                          | I2C1MD                       | PMD5<16>                       |

| 2C2                          | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| CAN                          | CAN1MD                       | PMD5<28>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1:

Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

# TABLE 27-2: PERIPHERAL MODULE DISABLE REGISTER SUMMARY

| ess                         |                  | e         |       |       |       |        |        |        |        | Bi                   | s    |      |      |       |       |        |        |        | £                         |

|-----------------------------|------------------|-----------|-------|-------|-------|--------|--------|--------|--------|----------------------|------|------|------|-------|-------|--------|--------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12  | 27/11  | 26/10  | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets <sup>(1)</sup> |

|                             | PMD1             | 31:16     | _     | —     | —     | —      | —      |        |        | —                    | _    | —    | _    | —     |       | —      | —      |        | 0000                      |

| F240                        | FINDT            | 15:0      |       |       | —     | CVRMD  | Ι      |        |        | CTMUMD               | Ι    | —    |      | —     |       | —      | —      | AD1MD  | 0000                      |

| 5050                        | PMD2             | 31:16     | _     | -     | —     | —      | _      | -      |        | —                    | _    | _    |      | _     | -     | _      | —      |        | 0000                      |

| F250                        | FINDZ            | 15:0      |       |       | —     | —      | Ι      |        |        | _                    | Ι    | —    |      | —     |       | CMP3MD | CMP2MD | CMP1MD | 0000                      |

| 5000                        | PMD3             | 31:16     | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000                      |

| F260                        | FINDS            | 15:0      | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000                      |

| F270                        | PMD4             | 31:16     | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | _    | _     | —     | _      | —      | _      | 0000                      |

| F270                        | FIVID4           | 15:0      | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000                      |

| 5000                        | PMD5             | 31:16     | -     |       | _     | CAN1MD | -      | —      | —      | USBMD <sup>(1)</sup> |      | _    | _    | _     | —     | _      | I2C1MD | I2C1MD | 0000                      |

| F280                        | FINDS            | 15:0      | -     |       | _     | —      | SPI4MD | SPI3MD | SPI2MD | SPI1MD               |      | _    | _    | U5MD  | U4MD  | U3MD   | U2MD   | U1MD   | 0000                      |

| 5000                        | PMD6             | 31:16     | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | _    | _     | —     | _      | —      | PMPMD  | 0000                      |

| F290                        | FIVIDO           | 15:0      | —     | _     | —     | —      | _      | _      | -      | —                    | _    | —    | _    | _     | _     | —      | REFOMD | RTCCMD | 0000                      |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on devices with a USB module.

© 2014-2016 Microchip Technology Inc.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |  |  |