Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512l-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

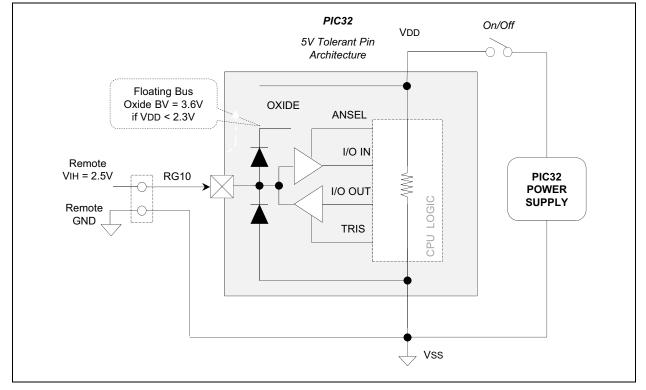

### 2.9.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

## 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/<br/>DIVIDE UNIT LATENCIES AND REPEAT RATES

| Op code                 | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

#### TABLE 4-1: SFR MEMORY MAP

| Devinheral             | Virtual | Address      |

|------------------------|---------|--------------|

| Peripheral             | Base    | Offset Start |

| Interrupt Controller   |         | 0x1000       |

| Bus Matrix             |         | 0x2000       |

| DMA                    | 0       | 0x3000       |

| USB                    | 0xBF88  | 0x5000       |

| PORTA-PORTG            |         | 0x6000       |

| CAN1                   |         | 0xB000       |

| Watchdog Timer         |         | 0x0000       |

| RTCC                   |         | 0x0200       |

| Timer1-Timer5          |         | 0x0600       |

| IC1-IC5                |         | 0x2000       |

| OC1-OC5                |         | 0x3000       |

| I2C1-I2C2              |         | 0x5000       |

| SPI1-SPI4              |         | 0x5800       |

| UART1-UART5            | 0xBF80  | 0x6000       |

| PMP                    | UXBF80  | 0x7000       |

| ADC1                   |         | 0x9000       |

| DAC                    |         | 0x9800       |

| Comparator 1, 2, 3     |         | 0xA000       |

| Oscillator             |         | 0xF000       |

| Device and Revision ID |         | 0xF200       |

| Flash Controller       |         | 0xF400       |

| PPS                    |         | 0xFA00       |

| Configuration          | 0xBFC0  | 0x0BF0       |

## 4.2 Special Function Register Maps

## TABLE 4-2: BUS MATRIX REGISTER MAP

|                             |                         |           |       |                     | 2010  |       |       |           |      |      |      |               |      |           |           |           |          |          |               |

|-----------------------------|-------------------------|-----------|-------|---------------------|-------|-------|-------|-----------|------|------|------|---------------|------|-----------|-----------|-----------|----------|----------|---------------|

| ress                        | _                       | Ð         |       |                     |       | -     |       |           |      |      |      | Bits          |      | -         |           |           | -        | _        |               |

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14               | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7 | 22/6          | 21/5 | 20/4      | 19/3      | 18/2      | 17/1     | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | _     |                     |       | _     |       | BMXCHEDMA |      | _    |      | _             |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS | BMXERRIS | 041F          |

| 2000                        | BWXCON                  | 15:0      | -     |                     |       |       |       |           |      |      |      | 0047          |      |           |           |           |          |          |               |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | _     |                     | _     | _     | -     | _         | _    | _    | -    | _             | _    | _         | _         | _         |          | _        | 0000          |

| 2010                        | DIVINDREDA              | 15:0      |       | BMXDKPBA<15:0> 0000 |       |       |       |           |      |      |      |               |      | 0000      |           |           |          |          |               |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _     | _                   | _     |       | _     | —         | _    | —    | _    | —             | _    | —         | —         | _         | _        | —        | 0000          |

| 2020                        |                         | 15:0      |       | BMXDUDBA<15:0> 000  |       |       |       |           |      |      |      |               | 0000 |           |           |           |          |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | —     | —                   | —     |       | —     | —         | —    | —    | —    | —             | —    | —         | —         | —         | —        | —        | 0000          |

| 2000                        |                         | 15:0      |       |                     |       |       |       |           |      |      | BM   | XDUPBA<15:0>  |      |           |           |           |          |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |                     |       |       |       |           |      |      | BM   | XDRMSZ<31:0>  |      |           |           |           |          |          | xxxx          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      |      |               |      |           |           |           |          |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —     | _                   | —     |       | -     | —         | _    | -    | _    | —             | -    | —         |           | BMXPUPBA  | <19:16>  |          | 0000          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      | BM   | XPUPBA<15:0>  |      |           |           |           |          |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |       |                     |       |       |       |           |      |      | BM   | XPFMSZ<31:0>  |      |           |           |           |          |          | xxxx          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      |      |               |      |           |           |           |          |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |       |                     |       |       |       |           |      |      | BMX  | (BOOTSZ<31:0) | >    |           |           |           |          |          | 0000          |

|                             |                         | 15:0      |       |                     |       |       |       |           |      |      |      |               |      |           |           |           |          |          | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

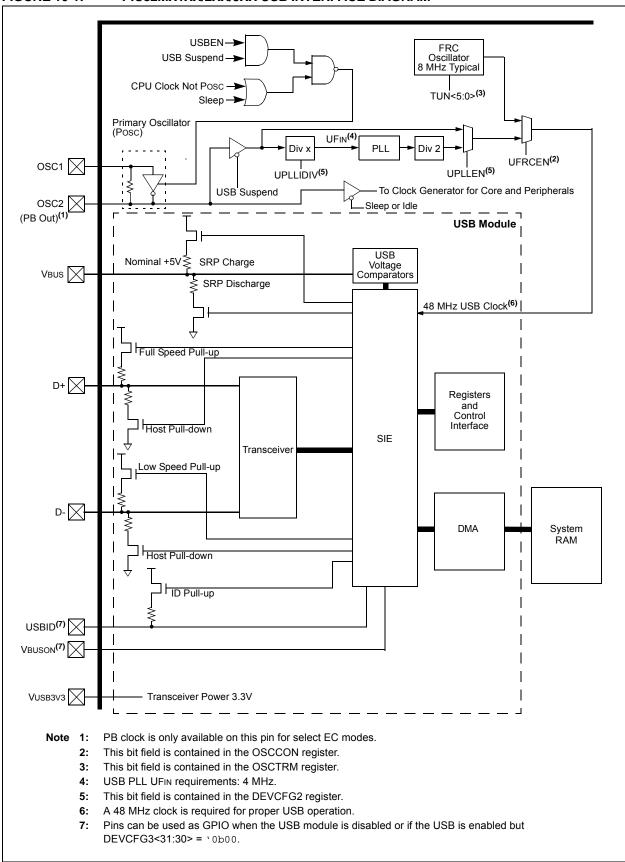

# 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | -                 | —                 | -                 | _                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | _                 | —                 | _                 | _                 | -                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | -                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

### REGISTER 10-16: U1SOF: USB SOF THRESHOLD REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CNT<7:0>:** SOF Threshold Value bits Typical values of the threshold are: 01001010 = 64-byte packet 00101010 = 32-byte packet 00011010 = 16-byte packet 00010010 =8-byte packet

#### REGISTER 10-17: U1BDTP1: USB BDT PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |       |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------|-------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0   | U-0   | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | —                 | -     | -     | —                 | —                 | -                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0   | U-0   | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | —                 |       |       | —                 | —                 |                  | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0   | U-0   | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | -                 | —                 | -     | -     | —                 | —                 | -                | —                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0            | U-0              |  |  |  |

| 7.0          | BDTPTRL<15:9>     |                   |       |       |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-1 **BDTPTRL<15:9>:** BDT Base Address bits This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory. The 32-bit BDT base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

# REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)('x' = 1 THROUGH 5)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## TABLE 17-1: SPI1 THROUGH SPI4 REGISTER MAP (CONTINUED)

| ess                                                            |                                 | 6             |               |         |        |              |              |              |           | Bit    | ts      |        |        |               |             |        |        |         | \$         |

|----------------------------------------------------------------|---------------------------------|---------------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|---------------|-------------|--------|--------|---------|------------|

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4          | 19/3        | 18/2   | 17/1   | 16/0    | All Resets |

|                                                                |                                 | 31:16         | -             | —       | _      | _            | _            | _            | —         | _      | —       | _      | —      | _             | _           | —      | —      | —       | 0000       |

| 5C40                                                           | SPI3CON2                        | 15:0          | SPI<br>SGNEXT | -       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | -      |        |               | AUD<br>MONO | -      | AUDMC  | )D<1:0> | 0000       |

|                                                                | SPI4CON <sup>(2)</sup>          | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL |        | —      | —             | —           |        | SPIFE  | ENHBUF  | 0000       |

| 5E00                                                           | SPI4COIN-                       | 15:0          | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI        | STXISE      | L<1:0> | SRXISE | L<1:0>  | 0000       |

|                                                                | SPI4STAT <sup>(2)</sup>         | 31:16         | _             | _       | _      |              | RXB          | UFELM<4:     | )>        |        | —       | —      | —      | TXBUFELM<4:0> |             |        | 0000   |         |            |

| 5E10                                                           | 5P1451A1                        | 15:0          | _             | —       | —      | FRMERR       | SPIBUSY      | —            |           | SPITUR | SRMT    | SPIROV | SPIRBE | —             | SPITBE      | —      | SPITBF | SPIRBF  | 19EB       |

| 5E20                                                           | SPI4BUF <sup>(2)</sup>          | 31:16<br>15:0 |               |         |        |              |              |              |           | DATA<  | 31:0>   |        |        |               |             |        |        |         | 0000       |

|                                                                | SPI4BRG <sup>(2)</sup>          | 31:16         | _             |         |        | —            | —            | —            | _         | —      | —       | —      | —      | —             | —           | —      | —      | —       | 0000       |

| 5E30                                                           | SPI4BRG-                        | 15:0          | _             | _       | _      | _            | _            | _            | _         |        |         |        |        | BRG<8:0>      |             |        |        |         | 0000       |

|                                                                |                                 | 31:16         |               | —       | —      | —            | —            | —            |           |        | —       | —      | —      | —             | —           | —      | —      | —       | 0000       |

| 5E40                                                           | SPI4CON2 <sup>(2)</sup>         | 15:0          | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _      | _      | _             | AUD<br>MONO | _      | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

| Bit<br>Range |                      |     | Bit Bit<br>0/22/14/6 29/21/13/5 |          | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-----|---------------------------------|----------|--------------------------|-------------------|------------------|------------------|

| 31:24        | U-0                  | U-0 | U-0                             | U-0      | U-0                      | U-0               | U-0              | U-0              |

| 31.24        | _                    | —   | —                               | —        | —                        | _                 | _                | _                |

| 23:16        | U-0                  | U-0 | U-0                             | U-0      | U-0                      | U-0               | U-0              | U-0              |

| 23.10        | —                    | _   | —                               | —        | —                        | —                 | _                | —                |

| 15:8         | R/W-0                | U-0 | U-0                             | R/W-0    | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | SPISGNEXT            | _   | —                               | FRMERREN | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR           |

| 7.0          | R/W-0 U-0 U-0 U-     |     | U-0                             | R/W-0    | U-0                      | R/W-0             | R/W-0            |                  |

| 7:0          | AUDEN <sup>(1)</sup> |     |                                 |          | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0>(1,2)      |

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| ı' |

|----|

| ļ  |

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

#### bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame Error overflow generates error events 0 = Frame Error does not generate error events bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = Receive overflow generates error events 0 = Receive overflow does not generate error events bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun Generates Error Events 0 = Transmit Underrun Does Not Generates Error Events bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions) 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data 0 = A ROV is a critical error which stop SPI operation bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions) 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty 0 = A TUR is a critical error which stop SPI operation AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup> bit 7 1 = Audio protocol enabled 0 = Audio protocol disabled bit 6-5 Unimplemented: Read as '0' AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3 1 = Audio data is mono (Each data word is transmitted on both left and right channels) 0 = Audio data is stereo bit 2 Unimplemented: Read as '0' AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0 11 = PCM/DSP mode 10 = Right Justified mode 01 = Left Justified mode  $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

## 21.1 Control Registers

## TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | 6         |            |       |         |            |             |            |                   | l            | Bits      |          |              |            |         |         |         |       | s         |

|-----------------------------|---------------------------------|-----------|------------|-------|---------|------------|-------------|------------|-------------------|--------------|-----------|----------|--------------|------------|---------|---------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15      | 30/14 | 29/13   | 28/12      | 27/11       | 26/10      | 25/9              | 24/8         | 23/7      | 22/6     | 21/5         | 20/4       | 19/3    | 18/2    | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON                          | 31:16     | _          | _     |         | —          | _           | —          |                   |              |           |          | CAL<         | 9:0>       |         |         |         |       | 0000      |

| 0200                        | RICCON                          | 15:0      | ON         | _     | SIDL    | —          | _           | —          |                   | —            | RTSECSEL  | RTCCLKON | _            | _          | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000      |

| 0210                        | RTCALRM                         | 31:16     | _          | _     |         | —          | -           | _          |                   | _            | _         | _        |              |            | _       | _       | _       | —     | 0000      |

| 0210                        | RICALKI                         | 15:0      | ALRMEN     | CHIME | PIV     | ALRMSYNC   |             | AMASI      | <b>&lt;</b> <3:0> |              | ARPT<7:0> |          |              |            |         | 0000    |         |       |           |

| 0220                        | RTCTIME                         | 31:16     |            | HR10  | 0<3:0>  |            | HR01<3:0>   |            |                   | MIN10<3:0>   |           |          |              | MIN01<3:0> |         |         |         | xxxx  |           |

| 0220                        | INTO THME                       | 15:0      | SEC10<3:0> |       |         | SEC01<3:0> |             |            | _                 | —            | _         | _        | —            | —          | —       | —       | xx00    |       |           |

| 0230                        | RTCDATE                         | 31:16     |            | YEAR  | 10<3:0> |            | YEAR01<3:0> |            |                   | MONTH10<3:0> |           |          | MONTH01<3:0> |            |         |         | xxxx    |       |           |

| 0230                        | RIODAIL                         | 15:0      |            | DAY1  | 0<3:0>  |            |             | DAY01<3:0> |                   |              | _         | —        | _            | _          |         | WDAY0   | 1<3:0>  |       | xx00      |

| 0240                        | ALRMTIME                        | 31:16     | HR10<3:0>  |       |         |            | HR01<3:0>   |            |                   |              | MIN10<    | 3:0>     |              |            | MIN01   | <3:0>   |         | xxxx  |           |

| 0240                        | 15:0                            |           |            | SEC1  | 0<3:0>  |            |             | SEC02      | 1<3:0>            |              | _         | _        |              |            | —       | -       | —       | —     | xx00      |

| 0250                        | ALRMDATE                        | 31:16     | _          | _     |         | _          | _           | _          | _                 | —            |           | MONTH10  | <3:0>        |            |         | MONTH   | 01<3:0> |       | 00xx      |

| 0200                        |                                 | 15:0      |            | DAY1  | 0<3:0>  |            |             | DAY01      | 1<3:0>            |              | —         | _        | _            |            |         | WDAY0   | 1<3:0>  |       | xx0x      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        |                   | HR10              | <3:0>             | HR01<3:0>         |                                    |                   |                  |                  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MIN10             | <3:0>             | MIN01<3:0>        |                                    |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                         |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                                | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                                  | _                 | _                | _                |  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10s place digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10s place digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10s place digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 **FCKSM<1:0>:** Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator disabled

- 10 = HS Oscillator mode selected

- 01 = XT Oscillator mode selected

- 00 = External Clock mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

## 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 31.0 40 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX/5XX 64/100-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 32.0** "**50 MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX/5XX 64/100-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | -0.3V to +3.6V           |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               |                          |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

3: See the "Device Pin Tables" section for the 5V tolerant pins.

### TABLE 31-13: COMPARATOR SPECIFICATIONS

| DC CHA        | RACTERI                | STICS                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                                                                            |  |  |

|---------------|------------------------|---------------------------------------|------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol                 | Characteristics                       | Min.                                                 | Тур. | Max. | Units | Comments                                                                   |  |  |

| D300          | VIOFF                  | Input Offset Voltage                  | —                                                    | ±7.5 | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                  |  |  |

| D301          | VICM <b>(2)</b>        | Input Common Mode Voltage             | 0                                                    | —    | Vdd  | V     | AVDD = VDD,<br>AVSS = VSS                                                  |  |  |

| D302          | CMRR <sup>(2)</sup>    | Common Mode Rejection Ratio           | 55                                                   |      | _    | dB    | Max VICM = (VDD - 1)V                                                      |  |  |

| D303          | TRESP <sup>(1,2)</sup> | Response Time                         | —                                                    | 150  | 400  | ns    | AVDD = VDD,<br>AVSS = VSS                                                  |  |  |

| D304          | ON20√ <sup>(2)</sup>   | Comparator Enabled to Output<br>Valid | —                                                    | _    | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit |  |  |

| D305          | IVREF                  | Internal Voltage Reference            | 1.14                                                 | 1.2  | 1.26 | V     | _                                                                          |  |  |

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

2: These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

4: The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

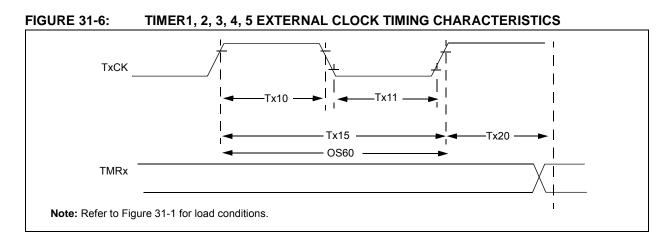

## TABLE 31-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS                      | TICS <sup>(1)</sup>                                                                                   |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                                            |         |      |       |                               |  |  |

|---------------|--------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|------|-------|-------------------------------|--|--|

| Param.<br>No. | Symbol                         | Characteristics <sup>(2)</sup>                                                                        |                             |                                                                                                                                                                                                                                                                                 | Min.                                       | Typical | Max. | Units | Conditions                    |  |  |

| TA10          | T⊤xH                           | TxCK<br>High Time                                                                                     | Synchronous, with prescaler |                                                                                                                                                                                                                                                                                 | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —       | —    | ns    | Must also meet parameter TA15 |  |  |

|               |                                |                                                                                                       | Asynchrono<br>with presca   |                                                                                                                                                                                                                                                                                 | 10                                         | —       | _    | ns    | —                             |  |  |

|               |                                | TxCKSynchronoLow Timewith presca                                                                      |                             |                                                                                                                                                                                                                                                                                 | [(12.5 ns or 1 TPB)/N] —<br>+ 25 ns        |         | —    | ns    | Must also meet parameter TA15 |  |  |

|               | Asynchronous<br>with prescaler |                                                                                                       |                             | 10                                                                                                                                                                                                                                                                              | _                                          | _       | ns   | —     |                               |  |  |

| TA15          | ΤτχΡ                           | TxCK<br>Input Period                                                                                  | Synchronou with presca      |                                                                                                                                                                                                                                                                                 | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns | —       | —    | ns    | VDD > 2.7V                    |  |  |

|               |                                |                                                                                                       |                             |                                                                                                                                                                                                                                                                                 | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns | -       | —    | ns    | VDD < 2.7V                    |  |  |

|               |                                |                                                                                                       | Asynchrono<br>with presca   |                                                                                                                                                                                                                                                                                 | 20                                         | —       | —    | ns    | VDD > 2.7V<br>(Note 3)        |  |  |

|               |                                |                                                                                                       |                             |                                                                                                                                                                                                                                                                                 | 50                                         | -       | _    | ns    | VDD < 2.7V<br>(Note 3)        |  |  |

| OS60          | FT1                            | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by set<br>the TCS (T1CON<1>) bi |                             |                                                                                                                                                                                                                                                                                 | 32                                         | —       | 100  | kHz   | —                             |  |  |

| TA20          | TCKEXTMRL                      | Delay from E<br>Clock Edge t<br>Increment                                                             |                             | K                                                                                                                                                                                                                                                                               |                                            |         | 1    | Трв   | —                             |  |  |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

### TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| АС СНА        | RACTERIS | STICS                      |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                            |  |  |

|---------------|----------|----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------|--|--|

| Param.<br>No. | Symbol   | Charact                    | eristics                      | Min.                                                                                                                                                                                                                                                                                | Max. | Units | Conditions                 |  |  |

| IS34          | THD:STO  | Stop Condition             | 100 kHz mode                  | 4000                                                                                                                                                                                                                                                                                | _    | ns    | —                          |  |  |

|               |          | Hold Time                  | 400 kHz mode                  | 600                                                                                                                                                                                                                                                                                 | —    | ns    |                            |  |  |

|               |          |                            | 1 MHz mode<br>(Note 1)        | 250                                                                                                                                                                                                                                                                                 |      | ns    |                            |  |  |

| IS40          | TAA:SCL  | Output Valid from<br>Clock | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                   | 3500 | ns    | —                          |  |  |

|               |          |                            | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                   | 1000 | ns    |                            |  |  |

|               |          |                            | 1 MHz mode<br><b>(Note 1)</b> | 0                                                                                                                                                                                                                                                                                   | 350  | ns    |                            |  |  |

| IS45          | TBF:SDA  | Bus Free Time              | 100 kHz mode                  | 4.7                                                                                                                                                                                                                                                                                 | —    | μs    | The amount of time the bus |  |  |

|               |          |                            | 400 kHz mode                  | 1.3                                                                                                                                                                                                                                                                                 | _    | μs    | must be free before a new  |  |  |

|               |          |                            | 1 MHz mode<br><b>(Note 1)</b> | 0.5                                                                                                                                                                                                                                                                                 | _    | μS    | transmission can start     |  |  |

| IS50          | Св       | Bus Capacitive Lo          |                               | 400                                                                                                                                                                                                                                                                                 | pF   | —     |                            |  |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

#### TABLE 31-34: ADC MODULE SPECIFICATIONS

|               |            | ACTERISTICS                                          | (unless oth                       | erwise sta                                           | ted)                             |          | e 5): 2.5V to 3.6V                                                                            |  |  |  |  |

|---------------|------------|------------------------------------------------------|-----------------------------------|------------------------------------------------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|--|--|

|               |            | ACTERISTICS                                          | Operating te                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                  |          |                                                                                               |  |  |  |  |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                              | Typical                                              | Max.                             | Units    | Conditions                                                                                    |  |  |  |  |

| Device        | Supply     |                                                      |                                   |                                                      |                                  |          |                                                                                               |  |  |  |  |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5 | —                                                    | Lesser of<br>VDD + 0.3 or<br>3.6 | V        | _                                                                                             |  |  |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                               | _                                                    | AVdd                             | V        | (Note 1)                                                                                      |  |  |  |  |

| Referen       | ce Inputs  |                                                      |                                   |                                                      |                                  |          |                                                                                               |  |  |  |  |

| AD05<br>AD05a | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                 | _                                                    | AVDD<br>3.6                      | V<br>V   | (Note 1)<br>VREFH = AVDD (Note 3)                                                             |  |  |  |  |

| AD06          | Vrefl      | Reference Voltage Low                                | AVss                              | —                                                    | Vrefh – 2.0                      | V        | (Note 1)                                                                                      |  |  |  |  |

| AD07          | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                               | —                                                    | AVDD                             | V        | (Note 3)                                                                                      |  |  |  |  |

| AD08<br>AD08a | IREF       | Current Drain                                        |                                   | 250<br>—                                             | 400<br>3                         | μA<br>μA | ADC operating<br>ADC off                                                                      |  |  |  |  |

| Analog        | Input      | ·                                                    |                                   |                                                      |                                  |          | ·                                                                                             |  |  |  |  |

| AD12          | VINH-VINL  | Full-Scale Input Span                                | VREFL                             | —                                                    | Vrefh                            | V        | —                                                                                             |  |  |  |  |

| AD13          | VINL       | Absolute VINL Input<br>Voltage                       | AVss – 0.3                        | —                                                    | AVDD/2                           | V        | _                                                                                             |  |  |  |  |

| AD14          | Vin        | Absolute Input Voltage                               | AVss - 0.3                        | _                                                    | AVDD + 0.3                       | V        | —                                                                                             |  |  |  |  |

| AD15          | _          | Leakage Current                                      | —                                 | ±0.001                                               | ±0.610                           | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3.3V$<br>Source Impedance = $10 \text{ k}\Omega$ |  |  |  |  |

| AD17          | RIN        | Recommended<br>Impedance of Analog<br>Voltage Source | —                                 | _                                                    | 5k                               | Ω        | (Note 1)                                                                                      |  |  |  |  |

| ADC Ac        | curacy – N | leasurements with Exte                               | rnal VREF+/V                      | REF-                                                 |                                  |          |                                                                                               |  |  |  |  |

| AD20c         | Nr         | Resolution                                           |                                   | 10 data bit                                          | S                                | bits     | _                                                                                             |  |  |  |  |

| AD21c         | INL        | Integral Non-linearity                               | > -1                              | _                                                    | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |  |  |  |  |

| AD22c         | DNL        | Differential Non-linearity                           | > -1                              | _                                                    | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                  |  |  |  |  |

| AD23c         | Gerr       | Gain Error                                           | > -1                              | _                                                    | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |  |  |  |  |

| AD24c         | Eoff       | Offset Error                                         | > -1                              | —                                                    | < 1                              | Lsb      | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                              |  |  |  |  |

| AD25c         | —          | Monotonicity                                         | _                                 | _                                                    | —                                | _        | Guaranteed                                                                                    |  |  |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |          |      |  |  |

|------------------------|-------------|----------|----------|------|--|--|

| Dimension              | MIN         | NOM      | MAX      |      |  |  |

| Number of Pins         | Ν           |          | 64       |      |  |  |

| Pitch                  | е           |          | 0.50 BSC |      |  |  |

| Overall Height         | Α           | 0.80     | 0.90     | 1.00 |  |  |

| Standoff               | A1          | 0.00     | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3          | 0.20 REF |          |      |  |  |

| Overall Width          | Е           | 9.00 BSC |          |      |  |  |

| Exposed Pad Width      | E2          | 5.30     | 5.40     | 5.50 |  |  |

| Overall Length         | D           | 9.00 BSC |          |      |  |  |

| Exposed Pad Length     | D2          | 5.30     | 5.40     | 5.50 |  |  |

| Contact Width          | b           | 0.20     | 0.25     | 0.30 |  |  |

| Contact Length         | L           | 0.30     | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | К           | 0.20     | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2