Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

|                       | Pin N                  | umber           |             |                | Description                                                                                        |  |  |  |  |

|-----------------------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name              | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type |                                                                                                    |  |  |  |  |

| VUSB3V3 <b>(2)</b>    | 35                     | 55              | Р           | —              | USB internal transceiver supply. If the USB module is not used, this pin must be connected to VDD. |  |  |  |  |

| VBUSON <sup>(2)</sup> | 11                     | 20              | 0           | —              | USB Host and OTG bus power control Output                                                          |  |  |  |  |

| D+ <sup>(2)</sup>     | 37                     | 57              | I/O         | Analog         | USB D+                                                                                             |  |  |  |  |

| D-(2)                 | 36                     | 56              | I/O         | Analog         | USB D-                                                                                             |  |  |  |  |

| USBID <sup>(2)</sup>  | 33                     | 51              | Ι           | ST             | USB OTG ID Detect                                                                                  |  |  |  |  |

| PGED1                 | 16                     | 25              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication<br>Channel 1                                  |  |  |  |  |

| PGEC1                 | 15                     | 24              | I           | ST             | Clock Input pin for Programming/Debugging Communicat<br>Channel 1                                  |  |  |  |  |

| PGED2                 | 18                     | 27              | I/O         | ST             | Data I/O Pin for Programming/Debugging Communicat<br>Channel 2                                     |  |  |  |  |

| PGEC2                 | 17                     | 26              | I           | ST             | Clock Input Pin for Programming/Debugging Communication Channel 2                                  |  |  |  |  |

| PGED3                 | 13                     | 22              | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication<br>Channel 3                                  |  |  |  |  |

| PGEC3                 | 14                     | 23              | I           | ST             | Clock Input Pin for Programming/Debugging Communication<br>Channel 3                               |  |  |  |  |

| CTED1                 | _                      | 17              | Ι           | ST             | CTMU External Edge Input 1                                                                         |  |  |  |  |

| CTED2                 |                        | 38              | I           | ST             | CTMU External Edge Input 2                                                                         |  |  |  |  |

| CTED3                 | 18                     | 27              | I           | ST             | CTMU External Edge Input 3                                                                         |  |  |  |  |

| CTED4                 | 22                     | 33              | Ι           | ST             | CTMU External Edge Input 4                                                                         |  |  |  |  |

| CTED5                 | 29                     | 43              | Ι           | ST             | CTMU External Edge Input 5                                                                         |  |  |  |  |

| CTED6                 | 30                     | 44              | Ι           | ST             | CTMU External Edge Input 6                                                                         |  |  |  |  |

| CTED7                 | _                      | 9               | Ι           | ST             | CTMU External Edge Input 7                                                                         |  |  |  |  |

| CTED8                 |                        | 92              | Ι           | ST             | CTMU External Edge Input 8                                                                         |  |  |  |  |

| CTED9                 |                        | 60              | Ι           | ST             | CTMU External Edge Input 9                                                                         |  |  |  |  |

| CTED10                | 21                     | 32              | Ι           | ST             | CTMU External Edge Input 10                                                                        |  |  |  |  |

| CTED11                | 23                     | 34              | Ι           | ST             | CTMU External Edge Input 11                                                                        |  |  |  |  |

| CTED12                | 15                     | 24              | Ι           | ST             | CTMU External Edge Input 12                                                                        |  |  |  |  |

| CTED13                | 14                     | 23              | Ι           | ST             | CTMU External Edge Input 13                                                                        |  |  |  |  |

| C1RX                  | PPS                    | PPS             | Ι           | ST             | Enhanced CAN Receive                                                                               |  |  |  |  |

| C1TX                  | PPS                    | PPS             | 0           | ST             | Enhanced CAN Transmit                                                                              |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output

P = Power

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer **Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module. 4: This pin is only available on 100-pin devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | -                 | —                 |                   | —                 | _                 | —                 | -                | _                |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | -                 | —                 | —                 | _                 |                   |                  | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | -                 | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7.0          |                   |                   |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |  |  |

### REGISTER 5-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| zogonal           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-13 Unimplemented: Read as '0'

### bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

- bit 11 Unimplemented: Read as '0'

### bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit<sup>(1)</sup>

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 **SOSCEN:** Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRIN            | √<8:1>            |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 |                   | —                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 |                  | —                |

## REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

**Note:** While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 |                       |                       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        | _                 | —                 | —                        |                   | —                     | —                     | _                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | —                 |                   |                          | _                 | —                     | _                     | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.0         | —                 | —                 | —                        | —                 | —                     | _                     |                  | —                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | 050               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JOTATE            | SE0               | TOKBUSY <sup>(1,5)</sup> | USDROI            |                       | RESUME                | FFDROI           | SOFEN <sup>(5)</sup> |

### REGISTER 10-11: U1CON: USB CONTROL REGISTER

## Legend:

| Logonal           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE detected on the USB

- 0 = No JSTATE detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single Ended Zero detected on the USB

0 = No Single Ended Zero detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability enabled

- 0 = USB host capability disabled

## bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling activated

- 0 = RESUME signaling disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL<1:0>        |                  | STSEL            |  |  |  |

### REGISTER 19-1: UxMODE: UARTx MODE REGISTER

## Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | 0             |       |                                         |       |       |       |       |         | Bi         | ts       |          |      |      |      |      |      |      | ú            |

|-----------------------------|------------------|---------------|-------|-----------------------------------------|-------|-------|-------|-------|---------|------------|----------|----------|------|------|------|------|------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                   | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8       | 23/7     | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets   |

| 9100                        | ADC1BUF9         | 31:16<br>15:0 |       | ADC Result Word 9 (ADC1BUF9<31:0>)      |       |       |       |       |         |            |          |          |      |      |      |      |      |      |              |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |       | ADC Result Word A (ADC1BUFA<31:0>) 0000 |       |       |       |       |         |            |          |          |      |      |      |      |      |      |              |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>)      |       |       |       |       |         |            |          |          |      |      |      |      |      |      |              |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       |                                         |       |       |       |       | ADC Res | ult Word C | (ADC1BUF | C<31:0>) |      |      |      |      |      |      | 0000         |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       |                                         |       |       |       |       | ADC Res | ult Word D | (ADC1BUF | D<31:0>) |      |      |      |      |      |      | 0000<br>0000 |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>)      |       |       |       |       |         |            |          |          |      |      |      |      |      |      |              |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       |                                         |       |       |       |       | ADC Res | ult Word F | (ADC1BUF | F<31:0>) |      |      |      |      |      |      | 0000<br>0000 |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for details.

2: For 64-pin devices, the MSB of these bits is not available.

3: For 64-pin devices, only the CSSL30:CSSL0 bits are available.

## REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

## REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 20-16 FSEL10<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN9: Filter 9 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN15           | MSEL1             | 5<1:0>            |                   | FSEL15<4:0>       |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | FLTEN14           | MSEL1             | 4<1:0>            | FSEL14<4:0>       |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | FLTEN13           | MSEL1             | 3<1:0>            | FSEL13<4:0>       |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | FLTEN12           | MSEL1             | 2<1:0>            | FSEL12<4:0>       |                   |                   |                  |                  |  |  |

### REGISTER 23-13: C1FLTCON3: CAN FILTER CONTROL REGISTER 3

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31<br>bit 30-29 | FLTEN15: Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled<br>MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 28-24           | FSEL15<4:0>: FIFO Selection bits<br>11111 = Reserved<br>10000 = Reserved<br>01111 = Message matching filter is stored in FIFO buffer 15<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                   |

| bit 23              | FLTEN14: Filter 14 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                        |

| bit 22-21           | MSEL14<1:0>: Filter 14 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                     |

| Note:               | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                                                                                                                  |

## REGISTER 23-16: C1FIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0 THROUGH 15) (CONTINUED)

- bit 7 TXEN: TX/RX Buffer Selection bit 1 = FIFO is a Transmit FIFO 0 = FIFO is a Receive FIFO TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully TXLARB: Message Lost Arbitration bit<sup>(3)</sup> bit 5 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received. TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority

- 00 = Lowest message priority

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (C1CON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | r-1                        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        |                            | _                 | _                 | —                 | —                 | _                 | _                | —                |  |

| 00.40        | r-1                        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 23:16        |                            | _                 |                   | —                 | —                 | FPLLODIV<2:0>     |                  |                  |  |

| 45.0         | R/P                        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | 15:8 UPLLEN <sup>(1)</sup> |                   | _                 | —                 | —                 | UP                | LLIDIV<2:0>      | .(1)             |  |

| 7.0          | r-1                        | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | _                          | FPLLMUL<2:0>      |                   |                   | —                 | F                 | PLLIDIV<2:0      | >                |  |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 28-3:**

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 6-4

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1' FPLLMUL<2:0>: PLL Multiplier bits 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is available on PIC32MX2XX/5XX devices only.

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24             | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24             | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | —                | _                |  |

| 23:16             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10             | —                 | —                 | —                 | —                 | _                 | _                 | —                | _                |  |

| 15.0              | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 15:8 USERID<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7.0               |                   |                   |                   | USERID<           | 7:0>              |                   |                  |                  |  |

#### REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bi  | it                 |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Unimplemented: Read as '0'

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

| Bit<br>31/23/15/7           | Bit<br>30/22/14/6         | Bit<br>29/21/13/5                                                                                          | Bit<br>28/20/12/4                                                                                                                                             | Bit<br>27/19/11/3                                                                                                                                                                                                                                    | Bit<br>26/18/10/2                                                                                                                                                           | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-----------------------------|---------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R                           | R                         | R                                                                                                          | R                                                                                                                                                             | R                                                                                                                                                                                                                                                    | R                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                             | VER<                      | :3:0> <sup>(1)</sup>                                                                                       |                                                                                                                                                               | DEVID<27:24> <sup>(1)</sup>                                                                                                                                                                                                                          |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| R                           | R                         | R                                                                                                          | R                                                                                                                                                             | R                                                                                                                                                                                                                                                    | R                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| DEVID<23:16> <sup>(1)</sup> |                           |                                                                                                            |                                                                                                                                                               |                                                                                                                                                                                                                                                      |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| R                           | R                         | R                                                                                                          | R                                                                                                                                                             | R                                                                                                                                                                                                                                                    | R                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| DEVID<15:8> <sup>(1)</sup>  |                           |                                                                                                            |                                                                                                                                                               |                                                                                                                                                                                                                                                      |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| R                           | R                         | R                                                                                                          | R                                                                                                                                                             | R                                                                                                                                                                                                                                                    | R                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                             |                           |                                                                                                            | DEVID<                                                                                                                                                        | 7:0>(1)                                                                                                                                                                                                                                              |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                             | 31/23/15/7<br>R<br>R<br>R | 31/23/15/7      30/22/14/6        R      R        R      R        R      R        R      R        R      R | 31/23/15/7      30/22/14/6      29/21/13/5        R      R      R        R      R      R        R      R      R        R      R      R        R      R      R | 31/23/15/7      30/22/14/6      29/21/13/5      28/20/12/4        R      R      R      R        R      R      R      R        R      R      R      R        R      R      R      R        R      R      R      R        R      R      R      DEVID<2 | 31/23/15/7      30/22/14/6      29/21/13/5      28/20/12/4      27/19/11/3        R      R      R      R      R        VER<3:0> <sup>(1)</sup> VER<3:0> <sup>(1)</sup> VER< | 31/23/15/7      30/22/14/6      29/21/13/5      28/20/12/4      27/19/11/3      26/18/10/2        R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R      R | 31/23/15/7      30/22/14/6      29/21/13/5      28/20/12/4      27/19/11/3      26/18/10/2      25/17/9/1        R      R      R      R      R      R      R      R        VER<3:0> <sup>(1)</sup> VER<3:0> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> R      R      R      R      R      R        R      R      R      R      R      R        R      R      R      R      R      R        R      R      R      R      R      R      R        R      R      R      R      R      R      R        R      R      R      R      R      R      R      R        R      R      R      R      R      R      R      R      R      R      R |  |

## REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Logonan           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

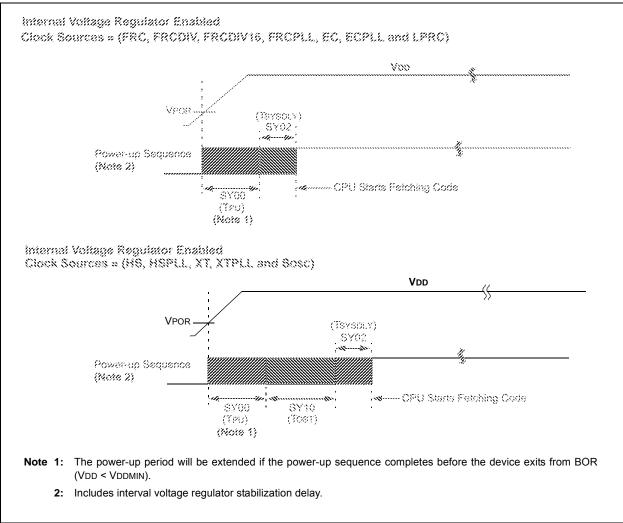

## FIGURE 31-4: POWER-ON RESET TIMING CHARACTERISTICS

#### TABLE 31-34: ADC MODULE SPECIFICATIONS

|               |            | ACTERISTICS                                          | Standard Operating Conditions (see Note 5): 2.5V to 3.6V (unless otherwise stated) |             |                                   |          |                                                                                               |  |  |

|---------------|------------|------------------------------------------------------|------------------------------------------------------------------------------------|-------------|-----------------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|

|               |            | ACTERISTICS                                          | Operating te                                                                       | emperature  | C for Industrial<br>°C for V-temp |          |                                                                                               |  |  |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                                                                               | Typical     | Max.                              | Units    | Conditions                                                                                    |  |  |

| Device        | Supply     |                                                      |                                                                                    |             |                                   |          |                                                                                               |  |  |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                  | —           | Lesser of<br>VDD + 0.3 or<br>3.6  | V        | _                                                                                             |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                                                                                | _           | AVdd                              | V        | (Note 1)                                                                                      |  |  |

| Referen       | ce Inputs  |                                                      |                                                                                    |             |                                   |          |                                                                                               |  |  |

| AD05<br>AD05a | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                                                                  | _           | AVDD<br>3.6                       | V<br>V   | (Note 1)<br>VREFH = AVDD (Note 3)                                                             |  |  |

| AD06          | Vrefl      | Reference Voltage Low                                | AVss                                                                               | —           | Vrefh – 2.0                       | V        | (Note 1)                                                                                      |  |  |

| AD07          | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                                                                                | —           | AVDD                              | V        | (Note 3)                                                                                      |  |  |

| AD08<br>AD08a | IREF       | Current Drain                                        |                                                                                    | 250<br>—    | 400<br>3                          | μA<br>μA | ADC operating<br>ADC off                                                                      |  |  |

| Analog        | Input      | ·                                                    |                                                                                    |             |                                   |          | ·                                                                                             |  |  |

| AD12          | VINH-VINL  | Full-Scale Input Span                                | VREFL                                                                              | —           | Vrefh                             | V        | —                                                                                             |  |  |

| AD13          | VINL       | Absolute VINL Input<br>Voltage                       | AVss – 0.3                                                                         | —           | AVDD/2                            | V        | _                                                                                             |  |  |

| AD14          | Vin        | Absolute Input Voltage                               | AVss - 0.3                                                                         | _           | AVDD + 0.3                        | V        | —                                                                                             |  |  |

| AD15          | _          | Leakage Current                                      | —                                                                                  | ±0.001      | ±0.610                            | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3.3V$<br>Source Impedance = $10 \text{ k}\Omega$ |  |  |

| AD17          | RIN        | Recommended<br>Impedance of Analog<br>Voltage Source | —                                                                                  | _           | 5k                                | Ω        | (Note 1)                                                                                      |  |  |

| ADC Ac        | curacy – N | leasurements with Exte                               | rnal VREF+/V                                                                       | REF-        |                                   |          |                                                                                               |  |  |

| AD20c         | Nr         | Resolution                                           |                                                                                    | 10 data bit | S                                 | bits     | _                                                                                             |  |  |

| AD21c         | INL        | Integral Non-linearity                               | > -1                                                                               | _           | < 1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |  |  |

| AD22c         | DNL        | Differential Non-linearity                           | > -1                                                                               | _           | < 1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                  |  |  |

| AD23c         | Gerr       | Gain Error                                           | > -1                                                                               | _           | < 1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |  |  |

| AD24c         | Eoff       | Offset Error                                         | > -1                                                                               | —           | < 1                               | Lsb      | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                              |  |  |

| AD25c         | —          | Monotonicity                                         | _                                                                                  | _           | —                                 | _        | Guaranteed                                                                                    |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| AC CHA        | ARACTER | ISTICS                                                               | (unless o                      | I Operating<br>otherwise st<br>g temperature | <b>ated)</b><br>e -40°C ≤ | ≤ TA ≤ +85 | <b>3.6V</b><br>°C for Industrial<br>5°C for V-temp |

|---------------|---------|----------------------------------------------------------------------|--------------------------------|----------------------------------------------|---------------------------|------------|----------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min. Typ. Max. Units Condition |                                              |                           |            |                                                    |

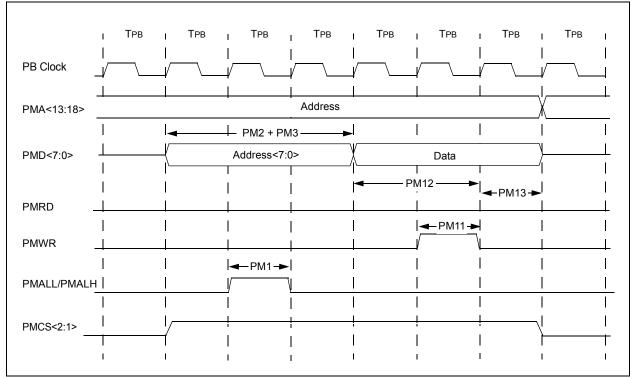

| PM1           | TLAT    | PMALL/PMALH Pulse Width                                              |                                | 1 Трв                                        |                           | _          | _                                                  |