Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512lt-v-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES

#### **100-PIN TQFP (TOP VIEW)**

PIC32MX230F128L PIC32MX530F128L PIC32MX250F256L PIC32MX550F256L PIC32MX270F512L PIC32MX570F512L

100

| Pin # | Full Pin Name                         | Div | n #  | Full Pin Name                   |

|-------|---------------------------------------|-----|------|---------------------------------|

|       |                                       |     |      |                                 |

| 1     | AN28/RG15                             |     | -    | /ss                             |

| 2     | VDD                                   | -   |      |                                 |

| 3     | AN22/RPE5/PMD5/RE5                    | 3   | .0   | ICK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 3   | -    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 4   | .0 A | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 4   | -1 A | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 4   | -2 A | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 4   | -3 A | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 4   | 4 A  | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 4   | ·5 \ | /ss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 4   | ·6 \ | /DD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 4   | ·7 A | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 4   | -8 A | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 4   | .9 F | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 5   | 60 F | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 5   | i1 L | JSBID/RPF3/RF3                  |

| 17    | TMS/CTED1/RA0                         | 5   | 2 A  | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 5   | 3 A  | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 5   | i4 \ | /BUS                            |

| 20    | AN5/C1INA/RPB5/VBUSON/RB5             | 5   | 5 \  | /USB3V3                         |

| 21    | AN4/C1INB/RB4                         | 5   | 6 E  | )-                              |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 5   | 7 E  | )+                              |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 5   | 8 5  | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 5   | 9 5  | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 6   | т 0  | IDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 6   | i1 T | IDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 6   | i2 \ | /DD                             |

| 28    | VREF-/PMA7/RA9                        | 6   | i3 ( | DSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 6   | i4 ( | DSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 6   | i5 Ν | /ss                             |

| 31    | AVss                                  | 6   | 6 F  | RPA14/SCL1/RA14                 |

| 32    | AN8/RPB8/CTED10/RB8                   | 6   | 57 F | RPA15/SDA1/RA15                 |

| 33    | AN9/RPB9/CTED4/RB9                    | 6   | i8 F | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 6   | ;9 F | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 7   | '0 F | RPD10/SCK1/PMA15/RD10           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

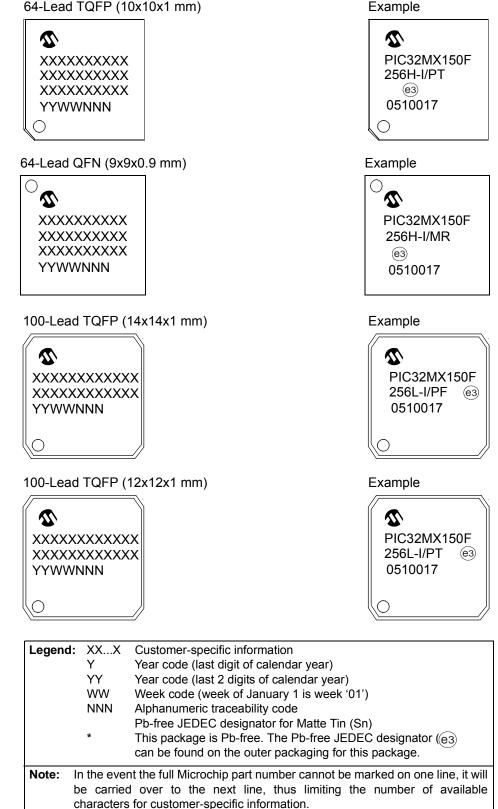

## 5.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupt Controller"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX/5XX 64/100-pin interrupt module includes the following features:

- Up to 76 interrupt sources

- Up to 46 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Software can generate any interrupt

- User-configurable interrupt vector table location

- User-configurable interrupt vector spacing

Note: The dedicated shadow register set is not available on these devices.

#### FIGURE 5-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 31:24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 15:8         |                   |                   |                   | NVMK              | EY<15:8>          |                   |                  |                  |  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 7:0          |                   | NVMKEY<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 6-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

## Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **NVMKEY<31:0>:** Unlock Register bits These bits are write-only, and read as '0' on any read.

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

#### REGISTER 6-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | NVMADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | NVMADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | NVMAE             | )DR<7:0>          |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMADDR<31:0>: Flash Address bits Bulk/Chip/PFM Erase: Address is ignored Page Erase: Address identifies the page to erase Row Program: Address identifies the row to program Word Program: Address identifies the word to program

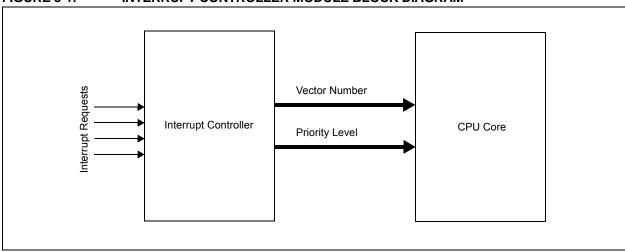

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit<sup>(1)</sup>

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 **SOSCEN:** Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

#### **TABLE 9-3:** DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |       |       |       |       |       |       |      | Bi     | ts      |         |        |         |             |        |        |         |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|--------|---------|---------|--------|---------|-------------|--------|--------|---------|------------|

| VIITUAI AGGRESS<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6    | 21/5   | 20/4    | 19/3        | 18/2   | 17/1   | 16/0    | All Resets |

|                             | DCH1SSIZ                        | 31:16         | —     |       |       | —     |       |       |      | —      | _       | —       |        |         | —           | —      | —      |         | 000        |

| ,,,,,                       | Donnool2                        | 15:0          |       |       |       |       |       |       |      | CHSSIZ | 2<15:0> | •       |        |         | i           | i      | i      | ·       | 000        |

| 3180                        | DCH1DSIZ                        | 31:16         | —     | —     | —     | —     | —     | —     | —    | —      | _       | —       | —      | —       | —           | —      | _      | —       | 000        |

| 5100                        | DOITIDOIZ                       | 15:0          |       |       |       |       |       |       |      | CHDSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

| 3190                        | DCH1SPTR                        | 31:16         | —     | _     | —     | —     |       | —     | —    | —      | —       | —       | —      | —       | —           | —      | —      | —       | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHSPT  | R<15:0> | -       |        |         |             |        |        |         | 000        |

| 31A0                        | DCH1DPTR                        | 31:16         | —     |       | —     | _     |       | _     | —    | —      | —       | —       | —      | _       | —           | —      | —      | —       | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHDPT  | R<15:0> |         |        |         |             |        |        |         | 000        |

| 31B0                        | DCH1CSIZ                        | 31:16         | —     | _     | —     | —     | _     | —     | —    | -      | —       | -       | —      | —       |             |        |        | _       | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHCSIZ | 2<15:0> | 1       |        |         |             |        |        |         | 000        |

| 31C0                        | DCH1CPTR                        | 31:16         | —     |       | _     |       |       |       |      |        | -       | —       | _      |         |             |        |        |         | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHCPTI | ≺<15:0> |         |        |         |             |        |        |         | 000        |

| 31D0                        | DCH1DAT                         | 31:16<br>15:0 | _     | _     |       |       | _     |       |      |        | _       | —       | —      |         | <br>AT<7:0> | —      | —      | _       | 000        |

|                             |                                 | 31:16         | _     |       |       |       | _     |       |      |        |         | _       | _      | CHPDF   |             | _      |        |         | 000        |

| 31E0                        | DCH2CON                         | 15:0          |       |       |       |       |       |       |      | CHCHNS | CHEN    | CHAED   | CHCHN  | CHAEN   |             | CHEDET | CHPR   |         | 000        |

|                             |                                 | 31:16         | —     |       |       | _     |       |       |      |        | CHLIN   | CHALD   | CHCHN  | CHAIR   |             | GHEDET | CHER   | .1<1.0> | 000        |

| 31F0                        | DCH2ECON                        | 15:0          |       |       |       | CHSIR |       |       |      |        | CFORCE  | CABORT  | PATEN  | SIRQEN  | AIRQEN      | _      |        | _       | FFF        |

|                             |                                 | 31:16         | _     | _     | _     |       |       | _     | _    | _      | CHSDIE  | CHSHIE  | CHDDIE | CHDHIE  | CHBCIE      | CHCCIE | CHTAIE | CHERIE  |            |

| 3200                        | DCH2INT                         | 15:0          | _     | _     |       | _     | _     | _     | _    | _      | CHSDIE  | CHSHIF  | CHDDIE | CHDHIF  | CHBCIE      | CHCCIF | CHTAIF | CHERIF  |            |

|                             |                                 | 31:16         |       |       |       |       |       |       |      |        |         | 0.10111 | 0.1551 | 0.15111 | 0112011     | 011001 | 0      | 0.12.11 | 000        |

| 3210                        | DCH2SSA                         | 15:0          |       |       |       |       |       |       |      | CHSSA  | <31:0>  |         |        |         |             |        |        |         | 000        |

|                             |                                 | 31:16         |       |       |       |       |       |       |      |        |         |         |        |         |             |        |        |         | 000        |

| 3220                        | DCH2DSA                         | 15:0          |       |       |       |       |       |       |      | CHDSA  | <31:0>  |         |        |         |             |        |        |         | 000        |

|                             | D.01100017                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _      | _       | _       | _      | _       | _           | _      | _      | _       | 000        |

| 3230                        | DCH2SSIZ                        | 15:0          |       |       |       |       |       |       |      | CHSSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

| 0040                        | DOUDDOUZ                        | 31:16         | _     | _     | —     | —     | —     | —     | —    | _      | —       | _       | —      | —       | —           | —      | _      | —       | 000        |

| 3240                        | DCH2DSIZ                        | 15:0          |       |       |       |       |       |       |      | CHDSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

| 2250                        | DCH2SPTR                        | 31:16         | —     | _     | —     | —     | —     | —     | —    | —      | —       | —       | —      | —       | —           | —      | _      | —       | 000        |

| 3230                        |                                 | 15:0          |       |       |       |       |       |       |      | CHSPT  | R<15:0> |         |        |         |             |        |        |         | 000        |

| 3260                        | DCH2DPTR                        | 31:16         | _     | _     | —     | —     | —     | —     | —    | _      | _       | —       | _      | —       |             | —      |        | —       | 000        |

| 3200                        |                                 | 15:0          |       |       |       |       |       |       |      | CHDPTI | R<15:0> |         |        |         |             |        |        |         | 000        |

| 3270                        | DCH2CSIZ                        | 31:16         | _     | _     | —     | —     |       | —     | _    | _      | _       | —       | _      | _       |             | —      |        | —       | 000        |

| 5210                        | DONZOSIZ                        | 15:0          |       |       |       |       |       |       |      | CHCSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### 15.1 Control Registers

### TABLE 15-1: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 5 REGISTER MAP

| ess                         |                       | â             |                   |              |       |       |       |       |       | Bi     | s      |      |              |      |       |      |          |      |            |

|-----------------------------|-----------------------|---------------|-------------------|--------------|-------|-------|-------|-------|-------|--------|--------|------|--------------|------|-------|------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15             | 30/14        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5         | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         |                   | —            | _     | —     | —     | _     |       |        |        | -    | _            | —    |       |      | _        |      | 0000       |

| 2000                        | 1010011               | 15:0          | ON                | —            | SIDL  | —     | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2010                        | IC1BUF                | 31:16         |                   |              |       |       |       |       |       | IC1BUF | <31:0> |      |              |      |       |      |          |      | xxxx       |

|                             |                       | 15:0          |                   |              |       |       |       |       |       |        |        |      |              | -    |       |      |          |      | xxxx       |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         | —                 |              | —     | —     | —     |       | —     |        | _      | —    | —            | —    |       |      | —        | —    | 0000       |

|                             |                       | 15:0          | ON                |              | SIDL  |       |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2210                        | IC2BUF                | 31:16<br>15:0 |                   | IC2BUF<31:0> |       |       |       |       |       |        |        |      | xxxx<br>xxxx |      |       |      |          |      |            |

|                             | (1)                   | 31:16         | _                 |              | _     |       |       | _     |       | _      | _      | _    | _            | _    | _     | _    | _        | _    | 0000       |

| 2400                        | IC3CON <sup>(1)</sup> | 15:0          | ON                | _            | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

|                             |                       | 31:16         |                   |              |       |       |       |       | 1 1   |        |        |      |              |      |       |      |          |      | xxxx       |

| 2410                        | IC3BUF                | 15:0          |                   |              |       |       |       |       |       | IC3BUF | <31:0> |      |              |      |       |      |          |      | xxxx       |

| 0000                        | 104001(1)             | 31:16         | —                 | —            | —     | —     | —     | —     | —     | _      | —      | —    | —            | _    | —     | —    | _        | —    | 0000       |

| 2600                        | IC4CON <sup>(1)</sup> | 15:0          | ON                | _            | SIDL  | _     |       |       | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 0040                        | IC4BUF                | 31:16         |                   | •            |       |       |       |       |       |        | 101.05 |      |              | •    |       |      |          |      | xxxx       |

| 2610                        | IC4BUF                | 15:0          | 15:0 IC4BUF<31:0> |              |       |       |       |       |       |        |        |      |              |      |       |      |          |      |            |

| 2000                        |                       | 31:16         | _                 | _            | _     | _     | _     | _     | —     | _      | —      | _    | _            | _    | _     | _    | —        | _    | 0000       |

| 2000                        | IC5CON <sup>(1)</sup> | 15:0          | ON                | —            | SIDL  | —     | —     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2810                        | IC5BUF                | 31:16         |                   |              |       |       |       |       |       | IC5BUF | <31.0> |      |              |      |       |      |          |      | xxxx       |

| 2010                        | ICODOF                | 15:0          |                   |              |       |       |       |       |       | IC3B0F | -01.02 |      |              |      |       |      |          |      | xxxx       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- • 0001 = Wait of 2 Трв

- 0000 = Wait of 1 TPB (default)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

| REGIST  | ER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)                                               |

|---------|--------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(3)</sup>                                              |

|         | 11111111 =Alarm will trigger 256 times                                                                 |

|         | •                                                                                                      |

|         | •                                                                                                      |

|         | •<br>00000000 =Alarm will trigger one time                                                             |

|         | The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = $00$ and CHIME = $0$ . |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.             |

| 3:      | This assumes a CPU read will execute in less than 32 PBCLKs.                                           |

| Note:   | This register is reset only on a Power-on Reset (POR).                                                 |

|         |                                                                                                        |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31.24        | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 02:16        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        |                   | SID<2:0>          |                   | _                 | EXID              | _                 | EID<1            | 7:16>            |  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          |                   |                   |                   | EID<              | :7:0>             |                   |                  |                  |  |  |  |  |

#### REGISTER 23-14: C1RXFn: CAN ACCEPTANCE FILTER 'n' REGISTER ('n' = 0 THROUGH 15)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|--|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EL<3:0>           |                   | EDG2STAT               | EDG1STAT         |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |  |  |  |  |  |  |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | _                 | —                 |                        |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   | ITRIM             | 1<5:0>              |                   |                   | IRNG                   | <1:0>            |  |  |  |  |  |  |

#### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

#### Legend:

| 8                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

#### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

## 0000 = Timer1 Event is selected

## bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

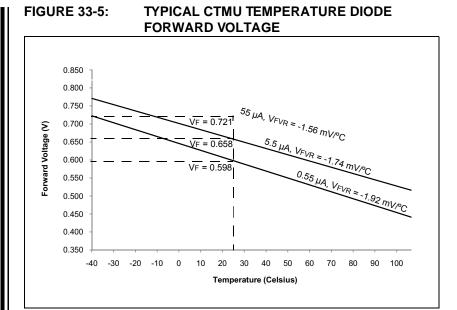

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Indicates the status of Edge 1 and can be written to control edge source                                                                                                                                                                                                                                         |

|           | 1 = Edge 1 has occurred                                                                                                                                                                                                                                                                                          |

|           | 0 = Edge 1 has not occurred                                                                                                                                                                                                                                                                                      |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                                                                                                                                                                                                                         |

|           | 1 = Input is edge-sensitive                                                                                                                                                                                                                                                                                      |

|           | 0 = Input is level-sensitive                                                                                                                                                                                                                                                                                     |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                                                                                                                                                                                                              |

|           | 1 = Edge 2 programmed for a positive edge response                                                                                                                                                                                                                                                               |

|           | 0 = Edge 2 programmed for a negative edge response                                                                                                                                                                                                                                                               |

| bit 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                                                                                                                                                                                                          |

|           | 1111 = IC4 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1110 = C2OUT pin is selected                                                                                                                                                                                                                                                                                     |

|           | 1101 = C1OUT pin is selected                                                                                                                                                                                                                                                                                     |

|           | 1100 = PBCLK clock is selected                                                                                                                                                                                                                                                                                   |

|           | 1011 = IC3 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1010 = IC2 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1001 = IC1 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1000 = CTED13 pin is selected<br>0111 = CTED12 pin is selected                                                                                                                                                                                                                                                   |

|           | 0110 = CTED12 pin is selected                                                                                                                                                                                                                                                                                    |

|           | 0101 = CTED10 pin is selected                                                                                                                                                                                                                                                                                    |

|           | 0100 = CTED9 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0011 = CTED1 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0010 = CTED2 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0001 = OC1 Compare Event is selected                                                                                                                                                                                                                                                                             |

|           | 0000 = Timer1 Event is selected                                                                                                                                                                                                                                                                                  |

| bit 17-16 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |

| bit 15    | ON: ON Enable bit                                                                                                                                                                                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                                                                                                                                            |

|           | 0 = Module is disabled                                                                                                                                                                                                                                                                                           |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                  |

|           | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                                                                                                                    |

|           | 0 = Continue module operation in Idle mode                                                                                                                                                                                                                                                                       |

| bit 12    | TGEN: Time Generation Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                  |

|           | 1 = Enables edge delay generation                                                                                                                                                                                                                                                                                |

|           | 0 = Disables edge delay generation                                                                                                                                                                                                                                                                               |

| bit 11    | EDGEN: Edge Enable bit                                                                                                                                                                                                                                                                                           |

|           | 1 = Edges are not blocked                                                                                                                                                                                                                                                                                        |

|           | 0 = Edges are blocked                                                                                                                                                                                                                                                                                            |

| Note 1:   | When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.                                                                                                                                                                                                    |

| 2:        | The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion                                                                                                                                                                                                               |

|           | cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor |

|           | array.                                                                                                                                                                                                                                                                                                           |

| -         |                                                                                                                                                                                                                                                                                                                  |

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

## 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 30.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| AC CHARACTERISTICS |               |                                  | $ \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \\ \end{array} $ |             |      |                            |                                            |  |

|--------------------|---------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|----------------------------|--------------------------------------------|--|

| Param.<br>No.      | Symbol        | Charact                          | eristics                                                                                                                                                                                                                                                                                 | Min.        | Max. | Units                      | Conditions                                 |  |

| IS10               | TLO:SCL       | Clock Low Time                   | 100 kHz mode                                                                                                                                                                                                                                                                             | 4.7         | —    | μS                         | PBCLK must operate at a minimum of 800 kHz |  |

|                    |               |                                  | 400 kHz mode                                                                                                                                                                                                                                                                             | 1.3         | —    | μs                         | PBCLK must operate at a minimum of 3.2 MHz |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 0.5         | —    | μS                         | _                                          |  |

| IS11               | THI:SCL       | Clock High Time                  | 100 kHz mode                                                                                                                                                                                                                                                                             | 4.0         | —    | μS                         | PBCLK must operate at a minimum of 800 kHz |  |

|                    |               |                                  | 400 kHz mode                                                                                                                                                                                                                                                                             | 0.6         | —    | μS                         | PBCLK must operate at a minimum of 3.2 MHz |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 0.5         | —    | μS                         | _                                          |  |

| IS20               | TF:SCL        | SDAx and SCLx                    | 100 kHz mode                                                                                                                                                                                                                                                                             | —           | 300  | ns                         | CB is specified to be from                 |  |

|                    | Fall Time     | 400 kHz mode                     | 20 + 0.1 Св                                                                                                                                                                                                                                                                              | 300         | ns   | 10 to 400 pF               |                                            |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | —           | 100  | ns                         |                                            |  |

| IS21 TR:SCL        | SDAx and SCLx | 100 kHz mode                     | —                                                                                                                                                                                                                                                                                        | 1000        | ns   | CB is specified to be from |                                            |  |

|                    |               | Rise Time                        | 400 kHz mode                                                                                                                                                                                                                                                                             | 20 + 0.1 Св | 300  | ns                         | 10 to 400 pF                               |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | _           | 300  | ns                         |                                            |  |

| IS25               | TSU:DAT       | Data Input<br>Setup Time         | 100 kHz mode                                                                                                                                                                                                                                                                             | 250         | —    | ns                         | —                                          |  |

|                    |               |                                  | 400 kHz mode                                                                                                                                                                                                                                                                             | 100         | _    | ns                         |                                            |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 100         | -    | ns                         |                                            |  |

| IS26               | THD:DAT       | Data Input                       | 100 kHz mode                                                                                                                                                                                                                                                                             | 0           | _    | ns                         | —                                          |  |

|                    |               | Hold Time                        | 400 kHz mode                                                                                                                                                                                                                                                                             | 0           | 0.9  | μS                         |                                            |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 0           | 0.3  | μS                         |                                            |  |

| IS30               | TSU:STA       | A Start Condition<br>Setup Time  | 100 kHz mode                                                                                                                                                                                                                                                                             | 4700        | —    | ns                         | Only relevant for Repeated                 |  |

|                    |               |                                  | 400 kHz mode                                                                                                                                                                                                                                                                             | 600         | —    | ns                         | Start condition                            |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 250         | —    | ns                         |                                            |  |

| IS31 Thd:sta       | THD:STA       | STA Start Condition<br>Hold Time | 100 kHz mode                                                                                                                                                                                                                                                                             | 4000        | _    | ns                         | After this period, the first               |  |

|                    |               |                                  | 400 kHz mode                                                                                                                                                                                                                                                                             | 600         | _    | ns                         | clock pulse is generated                   |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 250         | _    | ns                         |                                            |  |

| IS33               | Tsu:sto       | Stop Condition                   | 100 kHz mode                                                                                                                                                                                                                                                                             | 4000        | _    | ns                         |                                            |  |

|                    |               | Setup Time                       | 400 kHz mode                                                                                                                                                                                                                                                                             | 600         | _    | ns                         | ]                                          |  |

|                    |               |                                  | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                   | 600         | _    | ns                         |                                            |  |

### TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| AC CHARACTERISTICS |            |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 5): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |              |            |      |                                                         |  |

|--------------------|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------|---------------------------------------------------------|--|

| Param.<br>No.      | Symbol     | Characteristics                   | Min. Typical                                                                                                                                                                                                                                                                                   |              | Max. Units |      | Conditions                                              |  |

| ADC Ac             | curacy – N | leasurements with Inter           | nal VREF+/                                                                                                                                                                                                                                                                                     | REF-         |            |      |                                                         |  |

| AD20d              | Nr         | Resolution                        |                                                                                                                                                                                                                                                                                                | 10 data bits | 3          | bits | (Note 3)                                                |  |

| AD21d              | INL        | Integral Non-linearity            | > -1                                                                                                                                                                                                                                                                                           | -            | < 1        | LSb  | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD22d              | DNL        | Differential Non-linearity        | > -1                                                                                                                                                                                                                                                                                           |              | < 1        | LSb  | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |

| AD23d              | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                                                                                           | —            | < 4        | LSb  | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD24d              | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                                                                                           | -            | < 2        | Lsb  | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD25d              |            | Monotonicity                      | —                                                                                                                                                                                                                                                                                              |              | _          | —    | Guaranteed                                              |  |

| Dynami             | c Performa | ance                              |                                                                                                                                                                                                                                                                                                |              |            |      |                                                         |  |

| AD32b              | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                                                                                                             | 58.5         | _          | dB   | (Notes 3,4)                                             |  |

| AD34b              | ENOB       | Effective Number of bits          | 9.0                                                                                                                                                                                                                                                                                            | 9.5          | _          | bits | (Notes 3,4)                                             |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

**2:** With no missing codes.

3: These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| AC CHARACTERISTICS |                  |                                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |         |       |                                                           |  |

|--------------------|------------------|-------------------------------------------------------------------------|------------------------------------------------------|------------------------|---------|-------|-----------------------------------------------------------|--|

| Param.<br>No.      | Symbol           | Characteristics                                                         | Min.                                                 | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                |  |

| Clock P            | arameter         | s                                                                       | •                                                    | •                      |         |       | ·                                                         |  |